# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                         |

| Number of I/O              | 19                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 5x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0422sj020ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### X

# Introduction

This Product Specification provides detailed operating information for Z8 Encore! XP<sup>®</sup> F0822 Series devices within the Z8 Encore! XP Microcontroller (MCU) family of products. Within this document, Z8 Encore! XP<sup>®</sup> F0822 Series is referred as Z8 Encore! XP or the F0822 Series unless specifically stated otherwise.

#### About This Manual

Zilog recommends that you read and understand everything in this manual before setting up and using the product. We have designed this Product Specification to be used either as a *how to* procedural manual or a reference guide to important data.

#### Intended Audience

This document is written for Zilog customers who are experienced at working with microcontrollers, integrated circuits, or printed circuit assemblies.

#### **Manual Conventions**

The following assumptions and conventions are adopted to provide clarity and ease of use:

#### **Courier Typeface**

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various executable items are distinguished from general text by the use of the Courier typeface. Where the use of the font is not indicated, as in the Index, the name of the entity is presented in upper case.

• **Example:** FLAGS[1] is smrf.

#### **Hexadecimal Values**

Hexadecimal values are designated by uppercase *H* suffix and appear in the Courier typeface.

• **Example:** R1 is set to F8H.

#### Brackets

The square brackets [], indicate a register or bus.

• **Example:** For the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

- WDT's internal RC oscillator continues to operate.

- If enabled, the WDT continues to operate.

- All other on-chip peripherals continue to operate.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- WDT time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout reset

- External **RESET** pin assertion

To minimize current in HALT mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

| IRQ1ENL[x] | Priority                       | Description               |

|------------|--------------------------------|---------------------------|

| 0          | Disabled                       | Disabled                  |

| 1          | Level 1                        | Low                       |

| 0          | Level 2                        | Nominal                   |

| 1          | Level 3                        | High                      |

|            | IRQ1ENL[x]<br>0<br>1<br>0<br>1 | 0Disabled1Level 10Level 2 |

Table 31. IRQ1 Enable and Priority Encoding

where *x* indicates the register bits from 0 through 7.

#### Table 32. IRQ1 Enable High Bit Register (IRQ1ENH)

| BITS  | 7                                                      | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|--------------------------------------------------------|-----|---|----|----|---|---|---|--|--|--|

| FIELD | PA7ENH PA6ENH PA5ENH PA4ENH PA3ENH PA2ENH PA1ENH PA0EN |     |   |    |    |   |   |   |  |  |  |

| RESET |                                                        | 0   |   |    |    |   |   |   |  |  |  |

| R/W   |                                                        | R/W |   |    |    |   |   |   |  |  |  |

| ADDR  |                                                        |     |   | FC | 4H |   |   |   |  |  |  |

**PAxENH**—Port A Bit[*x*] Interrupt Request Enable High Bit

#### Table 33. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PA7ENL | PA6ENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |  |

| RESET |        | 0      |        |        |        |        |        |        |  |  |  |

| R/W   |        | R/W    |        |        |        |        |        |        |  |  |  |

| ADDR  |        |        |        | FC     | 5H     |        |        |        |  |  |  |

**PAxENL**—Port A Bit[*x*] Interrupt Request Enable Low Bit

#### **IRQ2 Enable High and Low Bit Registers**

Table 34 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit Registers (Table 35 and Table 36) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register.

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

# **Clear To Send Operation**

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this would be done during STOP bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

#### Multiprocessor (9-bit) Mode

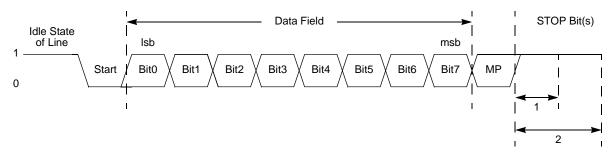

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit is transmitted following the 8-bits of data and immediately preceding the STOP bit(s) as displayed in Figure 14.

Figure 14. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 Registers provide Multiprocessor (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare Register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When multiprocessor mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software, or combination of the two depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not need to access the UART when it receives data directed to other devices on the

#### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the BRG is the system clock. The UART Baud Rate High and Low Byte Registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

#### **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data Register (Table 53). The Read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

#### Table 53. UART Receive Data Register (U0RXD)

| BITS  | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|-----|---|---|----|----|---|---|---|--|

| FIELD | RXD |   |   |    |    |   |   |   |  |

| RESET | X   |   |   |    |    |   |   |   |  |

| R/W   |     | R |   |    |    |   |   |   |  |

| ADDR  |     |   |   | F4 | 0H |   |   |   |  |

#### **RXD**—Receive Data

UART receiver data byte from the RXDx pin

#### UART Status 0 Register

The UART Status 0 and Status 1 registers (Table 54 and Table 55 on page 102) identify the current UART operating configuration and status.

#### Table 54. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6  | 5  | 4  | 3    | 2    | 1   | 0   |  |  |

|-------|-----|----|----|----|------|------|-----|-----|--|--|

| FIELD | RDA | PE | OE | FE | BRKD | TDRE | TXE | CTS |  |  |

| RESET |     |    | 0  |    | ,    | Х    |     |     |  |  |

| R/W   |     | R  |    |    |      |      |     |     |  |  |

| ADDR  |     |    |    | F4 | 1H   |      |     |     |  |  |

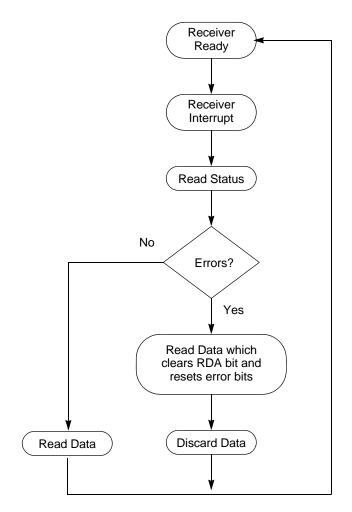

#### **RDA**—Receive Data Available

This bit indicates that the UART Receive Data Register has received data. Reading the UART Receive Data Register clears this bit.

0 = The UART Receive Data Register is empty.

1 = There is a byte in the UART Receive Data Register.

#### **PE—Parity Error**

This bit indicates that a parity error has occurred. Reading the UART Receive Data Register clears this bit.

0 = No parity error has occurred.

1 = A parity error has occurred.

#### **OE—Overrun Error**

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data Register has not been read. If the RDA bit is reset to

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

#### **SPI Signals**

The four basic SPI signals are:

- MISO (Master-In, Slave-Out)

- MOSI (Master-Out, Slave-In)

- SCK (Serial Clock)

- <u>SS</u> (Slave Select)

The following sections discuss these SPI signals. Each signal is described in both Master and Slave modes.

#### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

115

#### **SPI Status Register**

The SPI Status Register indicates the current state of the SPI. All bits revert to their reset state if the SPIEN bit in the SPICTL Register equals 0.

#### Table 65. SPI Status Register (SPISTAT)

| BITS       | 7                                                    | 6   | 5   | 4   | 3   | 2             | 1 | 0 |  |  |  |

|------------|------------------------------------------------------|-----|-----|-----|-----|---------------|---|---|--|--|--|

| FIELD      | IRQ                                                  | OVR | COL | ABT | Res | Reserved TXST |   |   |  |  |  |

| RESET      | 0 1                                                  |     |     |     |     |               |   |   |  |  |  |

| R/W        |                                                      | R/  | W*  |     |     |               | R |   |  |  |  |

| ADDR       | F62H                                                 |     |     |     |     |               |   |   |  |  |  |

| R/W* = Rea | R/W* = Read access. Write a 1 to clear the bit to 0. |     |     |     |     |               |   |   |  |  |  |

#### **IRQ—Interrupt Request**

If SPIEN = 1, this bit is set if the STR bit in the SPICTL Register is set, or upon completion of an SPI Master or Slave transaction. This bit does not set if SPIEN = 0 and the SPI Baud Rate Generator is used as a timer to generate the SPI interrupt.

- 0 =No SPI interrupt request pending.

- 1 =SPI interrupt request is pending.

#### OVR—Overrun

0 = An overrun error has not occurred.

1 = An overrun error has been detected.

#### **COL**—Collision

- 0 = A multi-master collision (mode fault) has not occurred.

- 1 = A multi-master collision (mode fault) has been detected.

#### ABT—SLAVE mode transaction abort

This bit is set if the SPI is configured in SLAVE mode, a transaction is occurring and  $\overline{SS}$  deasserts before all bits of a character have been transferred as defined by the NUMBITS field of the SPIMODE Register. The IRQ bit also sets, indicating the transaction has completed.

0 = A SLAVE mode transaction abort has not occurred.

1 = A SLAVE mode transaction abort has been detected.

#### Reserved—Must be 0

#### **TXST**—Transmit Status

- 0 = No data transmission currently in progress.

- 1 = Data transmission currently in progress.

#### **SLAS—Slave Select**

If SPI enabled as a Slave

$0 = \overline{SS}$  input pin is asserted (Low)

$1 = \overline{SS}$  input is not asserted (High).

If SPI enabled as a Master, this bit is not applicable.

Receive interrupts occur when a byte of data has been received by the  $I^2C$  Controller (Master reading data from Slave). This procedure sets the RDRF bit of the  $I^2C$  Status Register. The RDRF bit is cleared by reading the  $I^2C$  Data Register. The RDRF bit is set during the acknowledge phase. The  $I^2C$  Controller pauses after the acknowledge phase until the receive interrupt is cleared before performing any other action.

Transmit interrupts occur when the TDRE bit of the  $I^2C$  Status register sets and the TXI bit in the  $I^2C$  Control Register is set. Transmit interrupts occur under the following conditions when the Transmit Data Register is empty:

- The I<sup>2</sup>C Controller is enabled

- The first bit of the byte of an address is shifting out and the RD bit of the I<sup>2</sup>C Status register is deasserted.

- The first bit of a 10-bit address shifts out.

- The first bit of write data shifts out.

**Note:** Writing to the  $I^2C$  Data Register always clears the TRDE bit to 0. When TDRE is asserted, the  $I^2C$  Controller pauses at the beginning of the Acknowledge cycle of the byte currently shifting out until the data register is written with the next value to send or the STOP or START bits are set indicating the current byte is the last one to send.

The fourth interrupt source is the BRG. If the I<sup>2</sup>C Controller is disabled (IEN bit in the I2CCTL Register = 0) and the BIRQ bit in the I2CCTL Register = 1, an interrupt is generated when the BRG counts down to 1. This allows the I<sup>2</sup>C Baud Rate Generator to be used by software as a general purpose timer when IEN = 0.

# Software Control of I<sup>2</sup>C Transactions

Software controls I<sup>2</sup>C transactions by using the I<sup>2</sup>C Controller interrupt, by polling the I<sup>2</sup>C Status register or by DMA. Note that not all products include a DMA Controller.

To use interrupts, the  $I^2C$  interrupt must be enabled in the Interrupt Controller. The TXI bit in the  $I^2C$  Control Register must be set to enable transmit interrupts.

To control transactions by polling, the interrupt bits (TDRE, RDRF and NCKI) in the  $I^2C$  Status Register should be polled. The TDRE bit asserts regardless of the state of the TXI bit.

Either or both transmit and receive data movement can be controlled by the DMA Controller. The DMA Controller channel(s) must be initialized to select the I<sup>2</sup>C transmit and receive requests. Transmit DMA requests require that the TXI bit in the I<sup>2</sup>C Control Register be set.

**Caution:** A transmit (write) DMA operation hangs if the slave responds with a Not Acknowledge before the last byte has been sent. After receiving the Not Acknowledge, the I<sup>2</sup>C Controller sets the NCKI bit in the Status Register and pauses until either the STOP or

# I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers (Tables 73 and 73) combine to form a 16bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0]

Table 73. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|

| FIELD |   | BRH |   |    |    |   |   |   |  |  |

| RESET |   | FFH |   |    |    |   |   |   |  |  |

| R/W   |   | R/W |   |    |    |   |   |   |  |  |

| ADDR  |   |     |   | F5 | 3H |   |   |   |  |  |

# **BRH** = $I^2C$ Baud Rate High Byte

Most significant byte, BRG[15:8], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRH register returns the current value of the  $I^2C$  Baud Rate Counter[15:8].

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|

| FIELD |   | BRL |   |    |    |   |   |   |  |  |

| RESET |   | FFH |   |    |    |   |   |   |  |  |

| R/W   |   | R/W |   |    |    |   |   |   |  |  |

| ADDR  |   |     |   | F5 | 4H |   |   |   |  |  |

# **BRL** = $I^2C$ Baud Rate Low Byte

Least significant byte, BRG[7:0], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRL register returns the current value of the  $I^2C$  Baud Rate Counter [7:0].

# I<sup>2</sup>C Diagnostic State Register

The I<sup>2</sup>C Diagnostic State register (Table 75) provides observability of internal state. This is a read only register used for I<sup>2</sup>C diagnostics and manufacturing test.

162

frequency range for the device. The Flash Frequency High and Low Byte Registers must be loaded with the correct value to insure proper program and erase times.

#### Table 87. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|

| FIELD |   | FFREQH |   |    |    |   |   |   |  |  |

| RESET | 0 |        |   |    |    |   |   |   |  |  |

| R/W   |   | R/W    |   |    |    |   |   |   |  |  |

| ADDR  |   |        |   | FF | AH |   |   |   |  |  |

#### Table 88. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|

| FIELD |   | FFREQL |   |    |    |   |   |   |  |  |

| RESET |   | 0      |   |    |    |   |   |   |  |  |

| R/W   |   | R/W    |   |    |    |   |   |   |  |  |

| ADDR  |   |        |   | FF | BH |   |   |   |  |  |

#### FFREQH and FFREQL—Flash Frequency High and Low Bytes

These 2 bytes, {FFREQH[7:0], FFREQL[7:0]}, contain the 16-bit Flash Frequency value.

#### Reserved

These Option Bits are reserved for future use and must always be 1.

The following information applies only to the Flash versions of the F0822 Series devices:

#### **FWP—Flash Write Protect**

These two Option Bits combine to provide three levels of Program Memory protection:

| FWP | Description                                                                                                   |

|-----|---------------------------------------------------------------------------------------------------------------|

| 0   | Programming, Page Erase, and Mass Erase using User Code is disabled. Mass Erase is available through the OCD. |

| 1   | Programming and Page Erase are enabled for all of Flash Program Memory.                                       |

#### Flash Memory Address 0001H

#### Table 90. Options Bits at Flash Memory Address 0001H

| BITS                                            | 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------------------------------------------------|----------------------|---|---|---|---|---|---|---|--|--|--|--|

| FIELD                                           | Reserved             |   |   |   |   |   |   |   |  |  |  |  |

| RESET                                           | U                    |   |   |   |   |   |   |   |  |  |  |  |

| R/W                                             | R/W                  |   |   |   |   |   |   |   |  |  |  |  |

| ADDR                                            | Program Memory 0001H |   |   |   |   |   |   |   |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |   |   |   |   |   |   |   |  |  |  |  |

#### Reserved

These Option Bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

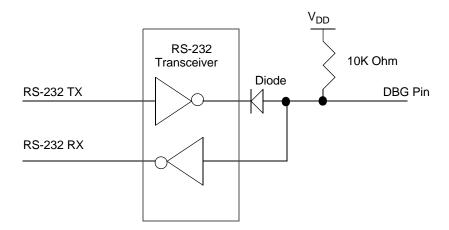

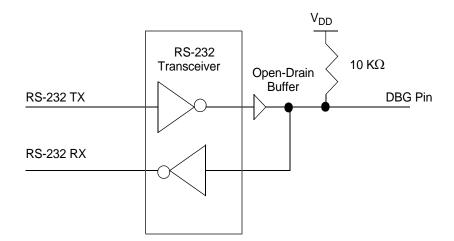

transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the Z8 Encore! XP F0822 Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 38 and Figure 39.

# **!** Caution: For operation of the OCD, all power pins $(V_{DD} \text{ and } AV_{DD})$ must be supplied with power, and all ground pins $(V_{SS} \text{ and } AV_{SS})$ must be properly grounded. The DBG pin is open-drain and must always be connected to $V_{DD}$ through an external pull-up resistor to insure proper operation.

Figure 38. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

Figure 39. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

A "reset and stop" function can be achieved by writing 81H to this register. A "reset and go" function can be achieved by writing 41H to this register. If the device is in DEBUG mode, a "run" function can be implemented by writing 40H to this register.

Table 94. OCD Control Register (OCDCTL)

| BITS  | 7 6           |     | 5      | 4       | 3     | 2      | 1        | 0   |  |  |  |  |

|-------|---------------|-----|--------|---------|-------|--------|----------|-----|--|--|--|--|

| FIELD | DBGMODE BRKEN |     | DBGACK | BRKLOOP | BRKPC | BRKZRO | Reserved | RST |  |  |  |  |

| RESET | 0             |     |        |         |       |        |          |     |  |  |  |  |

| R/W   |               | R/W |        |         | R/W   |        |          |     |  |  |  |  |

#### **DBGMODE—Debug Mode**

Setting this bit to 1 causes the device to enter DEBUG mode. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to start running again. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device, it cannot be written to 0.

0 = The Z8 Encore! XP F0822 Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F0822 Series device is in DEBUG mode.

#### **BRKEN**—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves like an NOP instruction. If this bit is set to 1 and a BRK instruction is decoded, the OCD takes action dependent upon the BRK-LOOP bit.

0 = BRK instruction is disabled.

1 = BRK instruction is enabled.

#### DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, then the OCD sends an Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled.

1 = Debug Acknowledge is enabled.

#### **BRKLOOP**—Breakpoint Loop

This bit determines what action the OCD takes when a BRK instruction is decoded if breakpoints are enabled (BRKEN is 1). If this bit is 0, then the DBGMODE bit is automatically set to 1 and the OCD enter DEBUG mode. If BRKLOOP is set to 1, then the eZ8 CPU loops on the BRK instruction.

0 = BRK instruction sets DBGMODE to 1.

1 = eZ8 CPU loops on BRK instruction.

#### **BRKPC—Break when PC == OCDCNTR**

If this bit is set to 1, then the OCDCNTR register is used as a hardware breakpoint. When the program counter matches the value in the OCDCNTR register, DBGMODE is

212

Table 116 contains additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                   |

|--------|------------------------------|

| dst    | Destination Operand          |

| src    | Source Operand               |

| @      | Indirect Address Prefix      |

| SP     | Stack Pointer                |

| PC     | Program Counter              |

| FLAGS  | Flags Register               |

| RP     | Register Pointer             |

| #      | Immediate Operand Prefix     |

| В      | Binary Number Suffix         |

| %      | Hexadecimal Number<br>Prefix |

| Н      | Hexadecimal Number<br>Suffix |

|        |                              |

#### Table 116. Additional Symbols

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

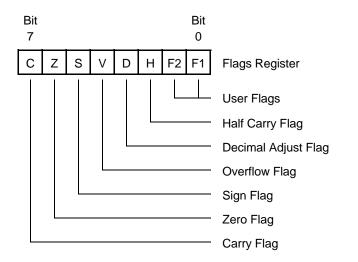

## **Flags Register**

The Flags Register contains the status information regarding the most recent arithmetic, logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits of status information that are set or cleared by CPU operations. Four of the bits (C, V, Z and S) can be tested with conditional jump instructions. Two flags (H and D) cannot be tested and are used for Binary-Coded Decimal (BCD) arithmetic.

The two remaining bits, User Flags (F1 and F2), are available as general-purpose status bits. User Flags are unaffected by arithmetic operations and must be set or cleared by instructions. The User Flags cannot be used with conditional Jumps. They are undefined at initial power-up and are unaffected by Reset. Figure 56 illustrates the flags and their bit positions in the Flags Register.

#### Figure 56. Flags Register

Interrupts, the Software Trap (TRAP) instruction, and Illegal Instruction Traps all write the value of the Flags Register to the stack. Executing an Interrupt Return (IRET) instruction restores the value saved on the stack into the Flags Register.

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

|          |                         | Lower Nibble (Hex)       |                            |                             |                            |                            |                            |                                |                               |                              |                            |                   |                           |                           |                  |                          |

|----------|-------------------------|--------------------------|----------------------------|-----------------------------|----------------------------|----------------------------|----------------------------|--------------------------------|-------------------------------|------------------------------|----------------------------|-------------------|---------------------------|---------------------------|------------------|--------------------------|

|          | 0                       | 1                        | 2                          | 3                           | 4                          | 5                          | 6                          | 7                              | 8                             | 9                            | А                          | В                 | С                         | D                         | E                | F                        |

| 0        | 1.2<br>BRK              | 2.2<br>SRP               | 2.3<br><b>ADD</b><br>r1,r2 | 2.4<br><b>ADD</b><br>r1,lr2 | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1       | 3.3<br><b>ADD</b><br>R1,IM | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1        | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1        | 2.2<br><b>RLC</b><br>R1 | 2.3<br><b>RLC</b><br>IR1 | 2.3<br>ADC<br>r1,r2        | 2.4<br>ADC<br>r1,lr2        | 3.3<br><b>ADC</b><br>R2,R1 | 3.4<br>ADC<br>IR2,R1       | 3.3<br>ADC<br>R1,IM        | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1        |                            |                   |                           |                           |                  | See 2nd<br>Opcode<br>Map |

| 2        | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2        | 2.4<br>SUB<br>r1,lr2        | 3.3<br>SUB<br>R2,R1        | 3.4<br>SUB<br>IR2,R1       | 3.3<br>SUB<br>R1,IM        | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1 |                            |                   |                           |                           |                  | map                      |

| 3        | 2.2<br>DEC<br>R1        | 2.3<br>DEC<br>IR1        | 2.3<br>SBC<br>r1,r2        | 2.4<br>SBC<br>r1,lr2        | 3.3<br>SBC<br>R2,R1        | 3.4<br>SBC<br>IR2,R1       | 3.3<br>SBC<br>R1,IM        | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br>SBCX                  |                            |                   |                           |                           |                  |                          |

| 4        | 2.2<br>DA<br>R1         | 2.3<br>DA<br>IR1         | 2.3<br>OR<br>r1,r2         | 2.4<br>OR<br>r1,lr2         | 3.3<br>OR<br>R2,R1         | 3.4<br>OR<br>IR2,R1        | 3.3<br>OR<br>R1,IM         | 3.4<br>OR<br>IR1,IM            | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b>            |                            |                   |                           |                           |                  |                          |

| 5        | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1 | 2.3<br>AND<br>r1,r2        | 2.4<br>AND<br>r1,lr2        | 3.3<br>AND<br>R2,R1        | 3.4<br>AND<br>IR2,R1       | 3.3<br>AND<br>R1,IM        | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1        |                            |                   |                           |                           |                  | 1.2<br>WDT               |

| 6        | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1        | 2.3<br>TCM<br>r1,r2        | 2.4<br>TCM<br>r1,lr2        | 3.3<br>TCM<br>R2,R1        | 3.4<br>TCM<br>IR2,R1       | 3.3<br>TCM<br>R1,IM        | 3.4<br>TCM<br>IR1,IM           | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1 |                            |                   |                           |                           |                  | 1.2<br>STOP              |

| <b>7</b> | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2       | 2.3<br><b>TM</b><br>r1,r2  | 2.4<br><b>TM</b><br>r1,lr2  | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1 | 3.3<br>TM<br>R1,IM         | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1  |                            |                   |                           |                           |                  | 1.2<br>HALT              |

| 8        | 2.5<br>DECW<br>RR1      | 2.6                      | 2.5<br>LDE<br>r1,lrr2      | 2.9<br>LDEI<br>Ir1,Irr2     | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2      | 3.4<br>LDX                 | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X       |                            |                   |                           |                           |                  | 1.2<br><b>DI</b>         |

| 9        | 2.2<br>RL<br>R1         | 2.3<br><b>RL</b><br>IR1  | 2.5<br>LDE<br>r2,Irr1      | 2.9<br>LDEI<br>Ir2,Irr1     | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1      | 3.4<br>LDX<br>R2,IRR1      | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br>LEA<br>r1,r2,X         | 3.5<br>LEA<br>rr1,rr2,X      |                            |                   |                           |                           |                  | 1.2<br>El                |

| A        | 2.5<br>INCW<br>RR1      | 2.6<br>INCW              | 2.3<br><b>CP</b><br>r1,r2  | 2.4<br><b>CP</b><br>r1,lr2  | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1 | 3.3<br><b>CP</b><br>R1,IM  | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1  |                            |                   |                           |                           |                  | 1.4<br>RET               |

| в        | 2.2<br>CLR<br>R1        | 2.3<br>CLR<br>IR1        | 2.3<br>XOR<br>r1,r2        | 2.4<br>XOR<br>r1,lr2        | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br>XOR<br>IR2,R1       | 3.3<br>XOR<br>R1,IM        | 3.4<br>XOR<br>IR1,IM           | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br>XORX<br>IM,ER1        |                            |                   |                           |                           |                  | 1.5<br>IRET              |

| с        | 2.2<br>RRC<br>R1        | 2.3<br>RRC<br>IR1        | 2.5<br>LDC<br>r1,lrr2      | 2.9<br>LDCI<br>Ir1,Irr2     | 2.3<br>JP<br>IRR1          | 2.9<br>LDC<br>lr1,lrr2     | i ci jim                   | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                              |                            |                   |                           |                           |                  | 1.2<br>RCF               |

| D        | 2.2<br>SRA<br>R1        | 2.3<br>SRA<br>IR1        | 2.5<br>LDC<br>r2,lrr1      | 2.9<br>LDCI<br>Ir2,Irr1     | 2.6<br>CALL<br>IRR1        | 2.2<br>BSWAP<br>R1         | 3.3<br>CALL<br>DA          | 3.4<br>LD<br>r2,r1,X           | 3.2<br>POPX<br>ER1            |                              |                            |                   |                           |                           |                  | 1.2<br>SCF               |

| Е        | 2.2<br>RR<br>R1         | 2.3<br><b>RR</b><br>IR1  | 2.2<br>BIT<br>p,b,r1       | 2.3<br>LD<br>r1,lr2         | 3.2<br>LD<br>R2,R1         | 3.3<br>LD<br>IR2,R1        | 3.2<br>LD<br>R1,IM         | 3.3<br>LD<br>IR1,IM            | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1         |                            |                   |                           |                           |                  | 1.2<br>CCF               |

| F        | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1       | 2.6<br>TRAP<br>Vector      | 2.3<br>LD<br>lr1,r2         | 2.8<br>MULT<br>RR1         | 3.3<br>LD<br>R2,IR1        | 3.3<br><b>BTJ</b>          | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               | ,                            | V                          |                   |                           |                           | ↓                |                          |

Figure 58. First Opcode Map

Upper Nibble (Hex)

231

## 240

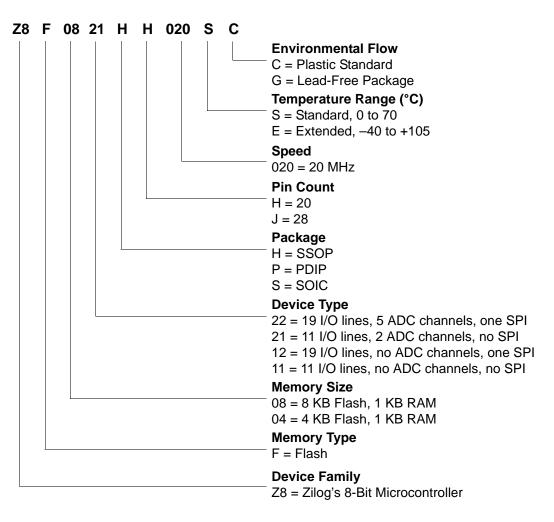

# Part Number Suffix Designations

For example, part number Z8F0821HH020SC is a Z8 Encore! XP Flash 8 KB microcontroller in a 20-pin SSOP package, operating with a maximum 20 MHz external clock frequency over a 0  $^{\circ}$ C to +70  $^{\circ}$ C temperature range and built using the Plastic-Standard environmental flow.

#### Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

ment addresses 216 load instructions 216 load using extended addressing 216 logical AND 217 logical AND/extended addressing 217 logical exclusive OR 217 logical exclusive OR/extended addressing 217 logical instructions 217 logical OR 217 logical OR 217 logical OR/extended addressing 217 logical OR/extended addressing 217

# Μ

master interrupt enable 59 master-in, slave-out and-in 115 memory program 13 **MISO 115** mode capture 81 capture/compare 82 continuous 81 counter 81 gated 82 one-shot 81 **PWM 81** modes 82 **MOSI 115 MULT 214** multiply 214 multiprocessor mode, UART 95

# N

NOP (no operation) 216 not acknowledge interrupt 128 notation b 211 cc 211 DA 211 ER 211 IM 211 IR 211

SPI 119 transmit 128 **UART 97** introduction 1 IR 211 Ir 211 IrDA architecture 109 block diagram 109 control register definitions 112 operation 109 receiving data 111 transmitting data 110 **IRET 217** IRQ0 enable high and low bit registers 63 IRQ1 enable high and low bit registers 64 IRQ2 enable high and low bit registers 65 IRR 211 Irr 211

# J

JP 217 jump, conditional, relative, and relative conditional 217

# L

LD 216 LDC 216 LDCI 215, 216 LDE 216 LDEI 215, 216 LDX 216 LEA 216 load 216 load constant 215 load constant to/from program memory 216 load constant with auto-increment addresses 216 load effective address 216 load external data 216 load external data to/from data memory and autoincrement addresses 215 load external to/from data memory and auto-incre-