# E·XFL

#### Zilog - Z8F0811HH020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I²C, IrDA, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                         |

| Number of I/O              | 11                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0811hh020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## ADC Data High Byte Register ..... 151 ADC Data Low Bits Register ..... 151 Flash Write/Erase Protection ..... 156

I2C Diagnostic Control Register ..... 145

| Mass Erase                                       |

|--------------------------------------------------|

| Flash Controller Bypass 158                      |

| Flash Controller Behavior in Debug Mode          |

| Flash Control Register Definitions               |

| Flash Control Register 159                       |

| Flash Status Register 160                        |

| Page Select Register 160                         |

| Flash Sector Protect Register 161                |

| Flash Frequency High and Low Byte Registers      |

| Option Bits                                      |

| Operation                                        |

| Option Bit Configuration By Reset                |

| Option Bit Address Space 163                     |

| Flash Memory Address 0000H 164                   |

| Flash Memory Address 0001H 165                   |

| On-Chip Oscillator                               |

| Operating Modes                                  |

| Crystal Oscillator Operation                     |

| Oscillator Operation with an External RC Network |

| On-Chip Debugger                                 |

| Architecture                                     |

| Operation                                        |

Table of Contents

## 13

# **Address Space**

The eZ8 CPU accesses three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, Peripheral, and GPIO Port Control Registers.

- The Program Memory contains addresses for all memory locations having executable code and/or data.

- The Data Memory contains addresses for all memory locations that hold data only.

These three address spaces are covered briefly in the following sections. For more information on the eZ8 CPU and its address space, refer to eZ8 CPU Core User Manual (UM0128) available for download at <u>www.zilog.com</u>.

#### **Register File**

The Register File address space in the Z8 Encore! XP<sup>®</sup> is 4 KB (4096 bytes). It is composed of two sections—Control Registers and General-Purpose Registers. When instructions are executed, registers are read from when defined as sources and written to when defined as destinations. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 1 KB Register File address space is reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256-byte Control Register section is reserved (unavailable). Reading from the reserved Register File addresses returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. Z8 Encore! XP F0822 Series contains 1 KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

#### **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. Z8 Encore! XP<sup>®</sup> F0822 Series contain 4 KB to 8 KB on-chip Flash in the Program Memory address space, depending on the device. Reading from Program Memory addresses outside the available Flash addresses returns FFH. Writing to unimplemented Program Memory addresses produces no effect Table 5 describes the Program Memory Maps for Z8 Encore! XP F0822 Series devices.

| Program Memory Address (Hex)                       | Function                 |  |  |

|----------------------------------------------------|--------------------------|--|--|

| Z8F082x and Z8F081x Products                       |                          |  |  |

| 0000-0001                                          | Option Bits              |  |  |

| 0002-0003                                          | Reset Vector             |  |  |

| 0004-0005                                          | WDT Interrupt Vector     |  |  |

| 0006-0007                                          | Illegal Instruction Trap |  |  |

| 0008-0037                                          | Interrupt Vectors*       |  |  |

| 0038-1FFF                                          | Program Memory           |  |  |

| Z8F042x and Z8F041x Products                       |                          |  |  |

| 0000-0001                                          | Option Bits              |  |  |

| 0002-0003                                          | Reset Vector             |  |  |

| 0004-0005                                          | WDT Interrupt Vector     |  |  |

| 0006-0007                                          | Illegal Instruction Trap |  |  |

| 0008-0037                                          | Interrupt Vectors*       |  |  |

| 0038-0FFF                                          | Program Memory           |  |  |

| Note: *See Table 24 on page 57 for a list of the i | interrupt vectors.       |  |  |

### Table 5. Z8 Encore! XP<sup>®</sup> F0822 Series Program Memory Maps

## **Data Memory**

Z8 Encore! XP<sup>®</sup> F0822 Series does not use the eZ8 CPU's 64 KB Data Memory address space.

## **Information Area**

Table 6 describes the Z8 Encore! XP F0822 Series Information Area. This 512 byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program Memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Information Area is read-only.

| Program Memory Address (Hex) Function |                                                                                                    |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| FE00H-FE3FH                           | Reserved                                                                                           |  |  |  |

| FE40H-FE53H                           | <b>Part Number</b><br>20-character ASCII alphanumeric code<br>Left justified and filled with zeros |  |  |  |

| FE54H-FFFFH                           | Reserved                                                                                           |  |  |  |

#### Table 6. Information Area Map

# **Register File Address Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F0822 Series products. Not all devices and package styles in the F0822 Series support the ADC, the SPI, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

Table 7. Register File Address Map

| Address<br>(Hex) | Register Description              | Mnemonic | Reset (Hex) | Page No    |

|------------------|-----------------------------------|----------|-------------|------------|

| General Pu       | <u> </u>                          |          |             | - <b>J</b> |

| 000-3FF          | General-Purpose Register File RAM | _        | XX          |            |

| 400-EFF          | Reserved                          | _        | XX          |            |

| Timer 0          |                                   |          |             |            |

| F00              | Timer 0 High Byte                 | ТОН      | 00          | 78         |

| F01              | Timer 0 Low Byte                  | TOL      | 01          | 78         |

| F02              | Timer 0 Reload High Byte          | TORH     | FF          | 79         |

| F03              | Timer 0 Reload Low Byte           | TORL     | FF          | 79         |

| F04              | Timer 0 PWM High Byte             | TOPWMH   | 00          | 79         |

| F05              | Timer 0 PWM Low Byte              | TOPWML   | 00          | 79         |

| F06              | Timer 0 Control 0                 | T0CTL0   | 00          | 81         |

| F07              | Timer 0 Control 1                 | T0CTL1   | 00          | 81         |

| Timer 1          |                                   |          |             |            |

| F08              | Timer 1 High Byte                 | T1H      | 00          | 78         |

| F09              | Timer 1 Low Byte                  | T1L      | 01          | 78         |

| F0A              | Timer 1 Reload High Byte          | T1RH     | FF          | 79         |

| F0B              | Timer 1 Reload Low Byte           | T1RL     | FF          | 79         |

| F0C              | Timer 1 PWM High Byte             | T1PWMH   | 00          | 79         |

| F0D              | Timer 1 PWM Low Byte              | T1PWML   | 00          | 79         |

| F0E              | Timer 1 Control 0                 | T1CTL0   | 00          | 81         |

| F0F              | Timer 1 Control 1                 | T1CTL1   | 00          | 81         |

| F10-F3F          | Reserved                          |          | XX          |            |

| UART 0           |                                   |          |             |            |

| F40              | UART0 Transmit Data               | U0TXD    | XX          | 100        |

|                  | UART0 Receive Data                | UORXD    | XX          | 101        |

| F41              | UART0 Status 0                    | U0STAT0  | 0000011Xb   | 101        |

| F42              | UART0 Control 0                   | U0CTL0   | 00          | 103        |

| F43              | UART0 Control 1                   | U0CTL1   | 00          | 103        |

| F44              | UART0 Status 1                    | U0STAT1  | 00          | 101        |

| F45              | UART0 Address Compare Register    | U0ADDR   | 00          | 105        |

| F46              | UART0 Baud Rate High Byte         | U0BRH    | FF          | 106        |

34

Port C Address PCADDR (FD8H - Read/Write) Port C Address[7:0] Selects Port Sub-Registers: 00H = No function 01H = Data direction 02H = Alternate function 03H = Output control (opendrain) 04H = High drive enable 05H = STOP mode recovery enable 06H = Pull-up enable 07H-FFH = No function

Port C Control PCCTL (FD9H - Read/Write) D7D6D5D4D3D2D1D0

|  | Port C Control [5:0]<br>Provides Access to Port<br>Sub-Registers |

|--|------------------------------------------------------------------|

|  | -Reserved                                                        |

Port C Input Data

PCIN (FDAH - Read Only) D7D6D5D4D3D2D1D0

Port C Input Data [5:0]

-----Reserved

Port C Output Data PCOUT (FDBH - Read/Write) D7/D6/D5/D4/D3/D2/D1/D0

Port C Output Data [5:0]

# **Reset and Stop Mode Recovery**

The Reset Controller within the Z8 Encore! XP<sup>®</sup> F0822 Series controls Reset and Stop Mode Recovery operation. In typical operation, the following events cause a Reset to occur:

- Power-On Reset (POR)

- Voltage Brownout

- WDT time-out (when configured through the WDT\_RES Option Bit to initiate a Reset)

- External **RESET** pin assertion

- On-Chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the Z8 Encore! XP F0822 Series device is in STOP mode, a Stop Mode Recovery is initiated by any of the following events:

- WDT time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

- DBG pin driven Low

### **Reset Types**

Z8 Encore! XP F0822 Series provides two types of reset operation (System Reset and Stop Mode Recovery). The type of reset is a function of both the current operating mode of the Z8 Encore! XP F0822 Series device and the source of the Reset. Table 8 lists the types of Resets and their operating characteristics.

|                       | Reset Characteristics and Latency      |            |                                                   |  |  |

|-----------------------|----------------------------------------|------------|---------------------------------------------------|--|--|

| Reset Type            | Control Registers                      | eZ8<br>CPU | Reset Latency (Delay)                             |  |  |

| System Reset          | Reset (as applicable)                  | Reset      | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |

| Stop Mode<br>Recovery | Unaffected, except<br>WDT_CTL register | Reset      | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |

pins.To determine the alternate function associated with each port pin, see GPIO Port Pin Block Diagram on page 48.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline can result in unpredictable operation.

Table 17. Port A–CA–C Alternate Function Sub-Registers

| BITS  | 7                                                                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | AF7                                                                                   | AF6 | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |

| RESET | 0                                                                                     |     |     |     |     |     |     |     |

| R/W   | R/W                                                                                   |     |     |     |     |     |     |     |

| ADDR  | If 02H in Port A–C Address Register, accessible through the Port A–C Control Register |     |     |     |     |     |     |     |

#### AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A–C Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A–C Output Control Sub-Registers

The Port A–C Output Control sub-register (Table 18) is accessed through the Port A–C Control Register by writing 03H to the Port A–C Address Register. Setting the bits in the Port A–C Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

| Table 18. Por | t A-C Output | t Control Sub-Regis | sters |

|---------------|--------------|---------------------|-------|

|---------------|--------------|---------------------|-------|

| BITS  | 7        | 6          | 5           | 4             | 3            | 2            | 1            | 0        |

|-------|----------|------------|-------------|---------------|--------------|--------------|--------------|----------|

| FIELD | POC7     | POC6       | POC5        | POC4          | POC3         | POC2         | POC1         | POC0     |

| RESET | 0        |            |             |               |              |              |              |          |

| R/W   | R/W      |            |             |               |              |              |              |          |

| ADDR  | lf 03H i | n Port A–C | Address Reo | gister, acces | sible throug | h the Port A | -C Control F | Register |

#### POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The drains are enabled for any output mode (unless overridden by the

| IRQ2ENH[x] | IRQ2ENL[ <i>x</i> ] | Priority | Description |

|------------|---------------------|----------|-------------|

| 0          | 0                   | Disabled | Disabled    |

| 0          | 1                   | Level 1  | Low         |

| 1          | 0                   | Level 2  | Nominal     |

| 1          | 1                   | Level 3  | High        |

Table 34. IRQ2 Enable and Priority Encoding

where *x* indicates the register bits from 0 through 7.

#### Table 35. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7    | 6    | 5     | 4 | 3     | 2                | 1 |  |  |  |  |

|-------|------|------|-------|---|-------|------------------|---|--|--|--|--|

| FIELD |      | Rese | erved |   | C3ENH | NH C2ENH C1ENH C |   |  |  |  |  |

| RESET | 0    |      |       |   |       |                  |   |  |  |  |  |

| R/W   | R/W  |      |       |   |       |                  |   |  |  |  |  |

| ADDR  | FC7H |      |       |   |       |                  |   |  |  |  |  |

**Reserved—Must be 0.**

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 36. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7    | 6    | 5     | 4 | 3     | 2     | 1 | 0 |  |  |  |  |

|-------|------|------|-------|---|-------|-------|---|---|--|--|--|--|

| FIELD |      | Rese | erved |   | C3ENL | C0ENL |   |   |  |  |  |  |

| RESET | 0    |      |       |   |       |       |   |   |  |  |  |  |

| R/W   | R/W  |      |       |   |       |       |   |   |  |  |  |  |

| ADDR  | FC8H |      |       |   |       |       |   |   |  |  |  |  |

#### Reserved—Must be 0.

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

## **Timers**

Z8 Encore! XP<sup>®</sup> F0822 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated signals. The timer features include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the Baud Rate Generators for any unused UART, SPI, or  $I^2C$  peripherals can also be used to provide basic timing functionality. See the respective serial communication peripheral chapters for information on using the Baud Rate Generators as timers.

### Architecture

Figure 10 displays the architecture of the timers.

### Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

- 4. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function

- 6. Write to the Timer Control Register to enable the timer and initiate counting

In COMPARE mode, the system clock always provides the timer input. The Compare time is calculated by the following equation:

Compare Mode Time (s) =  $\frac{(Compare Value - Start Value)xPrescale}{System Clock Frequency (Hz)}$

#### GATED Mode

In GATED mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte Registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte Registers is reset to 0001H and counting resumes (assuming the Timer Input signal is still asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Follow the steps below for configuring a timer for GATED mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for GATED mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte Registers to set the starting count value. This only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H

- 3. Write to the Timer Reload High and Low Byte Registers to set the Reload value

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers

- 5. Configure the associated GPIO port pin for the Timer Input alternate function

- 6. Write to the Timer Control Register to enable the timer

- 7. Assert the Timer Input signal to initiate the counting

## **Clear To Send Operation**

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this would be done during STOP bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

#### Multiprocessor (9-bit) Mode

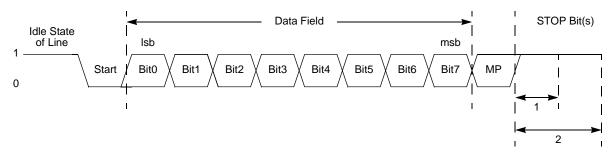

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit is transmitted following the 8-bits of data and immediately preceding the STOP bit(s) as displayed in Figure 14.

Figure 14. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 Registers provide Multiprocessor (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare Register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When multiprocessor mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software, or combination of the two depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not need to access the UART when it receives data directed to other devices on the

Table 75. I<sup>2</sup>C Diagnostic State Register (I2CDST)

| BITS  | 7     | 6     | 5      | 4         | 4 3 2 1 |  |  |  |  |  |  |  |           |  |  |  |  |  |  |

|-------|-------|-------|--------|-----------|---------|--|--|--|--|--|--|--|-----------|--|--|--|--|--|--|

| FIELD | SCLIN | SDAIN | STPCNT | TXRXSTATE |         |  |  |  |  |  |  |  | TXRXSTATE |  |  |  |  |  |  |

| RESET | >     | <     |        | 0         |         |  |  |  |  |  |  |  |           |  |  |  |  |  |  |

| R/W   | R     |       |        |           |         |  |  |  |  |  |  |  |           |  |  |  |  |  |  |

| ADDR  | F55H  |       |        |           |         |  |  |  |  |  |  |  |           |  |  |  |  |  |  |

**SCLIN**—Value of Serial Clock input signal **SDAIN**—Value of the Serial Data input signal **STPCNT**—Value of the internal Stop Count control signal **TXRXSTATE**—Value of the internal I<sup>2</sup>C state machine

| TXRXSTATE | State Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0_000     | Idle State                                                                                                                              |

| 0_0001    | START State                                                                                                                             |

| 0_0010    | Send/Receive data bit 7                                                                                                                 |

| 0_0011    | Send/Receive data bit 6                                                                                                                 |

| 0_0100    | Send/Receive data bit 5                                                                                                                 |

| 0_0101    | Send/Receive data bit 4                                                                                                                 |

| 0_0110    | Send/Receive data bit 3                                                                                                                 |

| 0_0111    | Send/Receive data bit 2                                                                                                                 |

| 0_1000    | Send/Receive data bit 1                                                                                                                 |

| 0_1001    | Send/Receive data bit 0                                                                                                                 |

| 0_1010    | Data Acknowledge State                                                                                                                  |

| 0_1011    | Second half of data Acknowledge State used only for not acknowledge                                                                     |

| 0_1100    | First part of STOP state                                                                                                                |

| 0_1101    | Second part of STOP state                                                                                                               |

| 0_1110    | 10-bit addressing: Acknowledge State for 2nd address byte<br>7-bit addressing: Address Acknowledge State                                |

| 0_1111    | 10-bit address: Bit 0 (Least significant bit) of 2nd address byte<br>7-bit address: Bit 0 (Least significant bit) (R/W) of address byte |

| 1_0000    | 10-bit addressing: Bit 7 (Most significant bit) of 1st address byte                                                                     |

| 1_0001    | 10-bit addressing: Bit 6 of 1st address byte                                                                                            |

| 1_0010    | 10-bit addressing: Bit 5 of 1st address byte                                                                                            |

| 1_0011    | 10-bit addressing: Bit 4 of 1st address byte                                                                                            |

| 1_0100    | 10-bit addressing: Bit 3 of 1st address byte                                                                                            |

| 1_0101    | 10-bit addressing: Bit 2 of 1st address byte                                                                                            |

| 1_0110    | 10-bit addressing: Bit 1 of 1st address byte                                                                                            |

|                   |                              | T <sub>A</sub> = - | 40 °C to         | 105 °C  |       |                                                                       |

|-------------------|------------------------------|--------------------|------------------|---------|-------|-----------------------------------------------------------------------|

| Symbol            | Parameter                    | Minimum Typical    |                  | Maximum | Units | Conditions                                                            |

| V <sub>RAM</sub>  | RAM Data<br>Retention        | 0.7                | _                | _       | V     |                                                                       |

| IIL               | Input Leakage<br>Current     | -5                 | -                | +5      | μA    | V <sub>DD</sub> = 3.6 V;<br>V <sub>IN</sub> = VDD or VSS <sup>1</sup> |

| I <sub>TL</sub>   | Tri-State<br>Leakage Current | -5                 | -                | +5      | μΑ    | V <sub>DD</sub> = 3.6 V                                               |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance | _                  | 8.0 <sup>2</sup> | _       | pF    |                                                                       |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance       | _                  | 8.0 <sup>2</sup> | _       | pF    |                                                                       |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance      | _                  | 9.5 <sup>2</sup> | _       | pF    |                                                                       |

| I <sub>PU1</sub>  | Weak Pull-up<br>Current      | 9                  | 20               | 50      | μA    | VDD = 2.7–3.6 V.<br>T <sub>A</sub> = 0 °C to +70 °C                   |

| I <sub>PU2</sub>  | Weak Pull-up<br>Current      | 7                  | 20               | 75      | μA    | VDD = 2.7–3.6 V.<br>T <sub>A</sub> = -40 °C to +105 °C                |

### Table 97. DC Characteristics (Continued)

<sup>1</sup> This condition excludes all pins that have on-chip pull-ups, when driven Low.

<sup>2</sup> These values are provided for design guidance only and are not tested in production.

Figure 41 on page 189 displays the typical active mode current consumption while operating at 25 °C, 3.3 V, versus the system clock frequency. All GPIO pins are configured as outputs and driven High.

## **Condition Codes**

The C, Z, S, and V flags control the operation of the conditional jump (JP cc and JR cc) instructions. Sixteen frequently useful functions of the flag settings are encoded in a 4-bit field called the condition code (cc), which forms Bits 7:4 of the conditional jump instructions. The condition codes are summarized in Table 117. Some binary condition codes can be created using more than one assembly code mnemonic. The result of the flag test operation decides if the conditional jump is executed.

| Binary | Hex | Assembly<br>Mnemonic | Definition                        | Flag Test Operation   |

|--------|-----|----------------------|-----------------------------------|-----------------------|

| 0000   | 0   | F                    | Always False                      | -                     |

| 0001   | 1   | LT                   | Less Than                         | (S XOR V) = 1         |

| 0010   | 2   | LE                   | Less Than or Equal                | (Z OR (S XOR V)) = 1  |

| 0011   | 3   | ULE                  | Unsigned Less Than or Equal       | (C OR Z) = 1          |

| 0100   | 4   | OV                   | Overflow                          | V = 1                 |

| 0101   | 5   | MI                   | Minus                             | S = 1                 |

| 0110   | 6   | Z                    | Zero                              | Z = 1                 |

| 0110   | 6   | EQ                   | Equal                             | Z = 1                 |

| 0111   | 7   | С                    | Carry                             | C = 1                 |

| 0111   | 7   | ULT                  | Unsigned Less Than                | C = 1                 |

| 1000   | 8   | T (or blank)         | Always True                       | -                     |

| 1001   | 9   | GE                   | Greater Than or Equal             | (S XOR V) = 0         |

| 1010   | А   | GT                   | Greater Than                      | (Z OR (S XOR V)) = 0  |

| 1011   | В   | UGT                  | Unsigned Greater Than             | (C = 0 AND Z = 0) = 1 |

| 1100   | С   | NOV                  | No Overflow                       | V = 0                 |

| 1101   | D   | PL                   | Plus                              | S = 0                 |

| 1110   | Е   | NZ                   | Non-Zero                          | Z = 0                 |

| 1110   | Е   | NE                   | Not Equal                         | Z = 0                 |

| 1111   | F   | NC                   | No Carry                          | C = 0                 |

| 1111   | F   | UGE                  | Unsigned Greater Than or<br>Equal | C = 0                 |

#### Table 117. Condition Codes

| Assembly         | Symbolic                      | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   |   | Fetch  | Instr. |

|------------------|-------------------------------|-----------------|-----|-------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic         | Operation                     | dst             | src | (Hex)       | С     | Ζ | S | V | D | Н | Cycles | Cycles |

| ADD dst, src     | $dst \gets dst + src$         | r               | r   | 02          | *     | * | * | * | 0 | * | 2      | 3      |

|                  |                               | r               | lr  | 03          | -     |   |   |   |   |   | 2      | 4      |

|                  |                               | R               | R   | 04          | -     |   |   |   |   |   | 3      | 3      |

|                  |                               | R               | IR  | 05          | -     |   |   |   |   |   | 3      | 4      |

|                  |                               | R               | IM  | 06          | -     |   |   |   |   |   | 3      | 3      |

|                  |                               | IR              | IM  | 07          | -     |   |   |   |   |   | 3      | 4      |

| ADDX dst, src    | $dst \gets dst + src$         | ER              | ER  | 08          | *     | * | * | * | 0 | * | 4      | 3      |

|                  |                               | ER              | IM  | 09          | -     |   |   |   |   |   | 4      | 3      |

| AND dst, src     | $dst \gets dst \ AND \ src$   | r               | r   | 52          | -     | * | * | 0 | - | - | 2      | 3      |

|                  |                               | r               | lr  | 53          | -     |   |   |   |   |   | 2      | 4      |

|                  |                               | R               | R   | 54          | -     |   |   |   |   |   | 3      | 3      |

|                  |                               | R               | IR  | 55          | -     |   |   |   |   |   | 3      | 4      |

|                  |                               | R               | IM  | 56          | -     |   |   |   |   |   | 3      | 3      |

|                  |                               | IR              | IM  | 57          | -     |   |   |   |   |   | 3      | 4      |

| ANDX dst, src    | $dst \gets dst \; AND \; src$ | ER              | ER  | 58          | -     | * | * | 0 | - | - | 4      | 3      |

|                  |                               | ER              | IM  | 59          | -     |   |   |   |   |   | 4      | 3      |

| BCLR bit, dst    | dst[bit] ← 0                  | r               |     | E2          | -     | - | - | - | - | - | 2      | 2      |

| BIT p, bit, dst  | dst[bit] ← p                  | r               |     | E2          | -     | - | - | - | - | - | 2      | 2      |

| BRK              | Debugger Break                |                 |     | 00          | -     | - | - | - | - | - | 1      | 1      |

| BSET bit, dst    | dst[bit] ← 1                  | r               |     | E2          | -     | - | - | - | - | - | 2      | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]           | R               |     | D5          | Х     | * | * | 0 | - | - | 2      | 2      |

| BTJ p, bit, src, |                               |                 | r   | F6          | -     | - | - | - | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$        |                 | lr  | F7          | -     |   |   |   |   |   | 3      | 4      |

| BTJNZ bit, src,  |                               |                 | r   | F6          | -     | - | - | - | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$        |                 | lr  | F7          | -     |   |   |   |   |   | 3      | 4      |

| BTJZ bit, src,   | if src[bit] = 0               |                 | r   | F6          | -     | - | - | - | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$        |                 | lr  | F7          | -     |   |   |   |   |   | 3      | 4      |

## Table 126. eZ8 CPU Instruction Summary (Continued)

| Assembly      | Symbolic                 |      | ress<br>ode | _ Opcode(s) |   |   | Fla | ıgs | Fetch | Instr. |   |   |

|---------------|--------------------------|------|-------------|-------------|---|---|-----|-----|-------|--------|---|---|

| Mnemonic      | Operation                | dst  | src         | (Hex)       | С | Ζ | S   | V   | D     | Н      |   |   |

| LD dst, rc    | $dst \gets src$          | r    | IM          | 0C-FC       | - | - | -   | -   | -     | -      | 2 | 2 |

|               |                          | r    | X(r)        | C7          | • |   |     |     |       |        | 3 | 3 |

|               |                          | X(r) | r           | D7          | • |   |     |     |       |        | 3 | 4 |

|               |                          | r    | lr          | E3          | • |   |     |     |       |        | 2 | 3 |

|               |                          | R    | R           | E4          | • |   |     |     |       |        | 3 | 2 |

|               |                          | R    | IR          | E5          | • |   |     |     |       |        | 3 | 4 |

|               |                          | R    | IM          | E6          | _ |   |     |     |       |        | 3 | 2 |

|               |                          | IR   | IM          | E7          |   |   |     |     |       |        | 3 | 3 |

|               |                          | lr   | r           | F3          |   |   |     |     |       |        | 2 | 3 |

|               |                          | IR   | R           | F5          |   |   |     |     |       |        | 3 | 3 |

| LDC dst, src  | $dst \gets src$          | r    | Irr         | C2          | - | - | -   | -   | -     | -      | 2 | 5 |

|               |                          | Ir   | Irr         | C5          |   |   |     |     |       |        | 2 | 9 |

|               |                          | Irr  | r           | D2          |   |   |     |     |       |        | 2 | 5 |

| LDCI dst, src | dst ← src                | Ir   | Irr         | C3          | - | - | -   | -   | -     | -      | 2 | 9 |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | D3          |   |   |     |     |       |        | 2 | 9 |

| LDE dst, src  | dst $\leftarrow$ src     | r    | Irr         | 82          | - | - | -   | -   | -     | -      | 2 | 5 |

|               |                          | Irr  | r           | 92          | • |   |     |     |       |        | 2 | 5 |

| LDEI dst, src | dst ← src                | lr   | Irr         | 83          | - | - | -   | -   | -     | -      | 2 | 9 |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | 93          |   |   |     |     |       |        | 2 | 9 |

## Table 126. eZ8 CPU Instruction Summary (Continued)

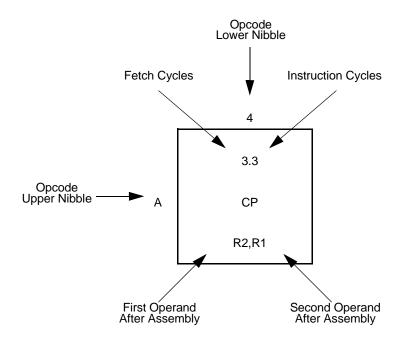

# **Opcode Maps**

A description of the opcode map data and the abbreviations are provided in Figure 57 and Table 127 on page 230. Figure 58 on page 231 and Figure 59 on page 232 provide information on each of the eZ8 CPU instructions.

Figure 57. Opcode Map Cell Description

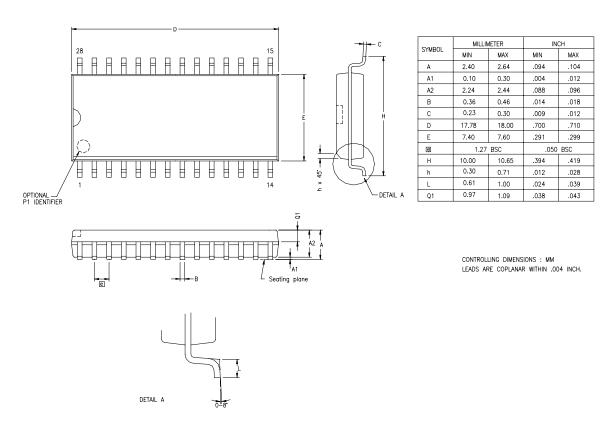

Figure 62 displays the 28-pin SOIC package available for Z8 Encore! XP F0822 Series devices.

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

program control instructions 217 program counter 212 program flash configurations 153 program memory 13, 153 PUSH 216 push using extended addressing 216 PUSHX 216 PWM mode 81 PxADDR register 50 PxCTL register 51

## R

R 211 r 211 RCF 215, 216 receive 10-bit data format (I2C) 137 7-bit data transfer format (I2C) 136 IrDA data 111 receive interrupt 128 receiving UART data-interrupt-driven method 94 receiving UART data-polled method 93 register 124, 211 ADC control (ADCCTL) 150 ADC data high byte (ADCDH) 151 ADC data low bits (ADCDL) 151 baud low and high byte (I2C) 143, 145 baud rate high and low byte (SPI) 125 control (SPI) 122 control, I2C 141 data, SPI 121 flash control (FCTL) 159 flash high and low byte (FFREQH and FRE-EQL) 161 flash page select (FPS) 160 flash status (FSTAT) 160 GPIO port A-H address (PxADDR) 50 GPIO port A-H alternate function sub-registers 52 GPIO port A-H control address (PxCTL) 51 GPIO port A-H data direction sub-registers 51 I2C baud rate high (I2CBRH) 143, 144, 145

I2C control (I2CCTL) 141 I2C data (I2CDATA) 139 I2C status 140 I2C status (I2CSTAT) 140 I2Cbaud rate low (I2CBRL) 143 mode, SPI 124 OCD control 181 OCD status 183 SPI baud rate high byte (SPIBRH) 125 SPI baud rate low byte (SPIBRL) 126 SPI control (SPICTL) 122 SPI data (SPIDATA) 121 SPI status (SPISTAT) 123 status, I2C 140 status, SPI 123 UARTx baud rate high byte (UxBRH) 106 UARTx baud rate low byte (UxBRL) 106 UARTx Control 0 (UxCTL0) 103, 106 UARTx control 1 (UxCTL1) 104 UARTx receive data (UxRXD) 101 UARTx status 0 (UxSTAT0) 101 UARTx status 1 (UxSTAT1) 102 UARTx transmit data (UxTXD) 100 watch-dog timer control (WDTCTL) 86 watch-dog timer reload high byte (WDTH) 88 watch-dog timer reload low byte (WDTL) 88 watch-dog timer reload upper byte (WDTU) 87 register address (RA) 211 register file 13 register file address map 15 register pair 211 register pointer 212 reset and stop mode characteristics 39 and stop mode recovery 39 carry flag 215 controller 5 sources 40 **RET 217** return 217 RL 218 **RLC 218** rotate and shift instructions 218 rotate left 218

247

### Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

test complement under mask - extended addressing 215 test under mask 215 test under mask - extended addressing 215 timer signals 10 timers 5, 69 architecture 69 block diagram 70 capture mode 74, 81 capture/compare mode 77, 82 compare mode 75, 82 continuous mode 71, 81 counter mode 72 counter modes 81 gated mode 76, 82 one-shot mode 70, 81 operating mode 70 PWM mode 73, 81 reading the timer count values 77 reload high and low byte registers 79 timer control register definitions 78 timer output signal operation 78 timers 0-3 control 0 registers 80 control registers 81 high and low byte registers 78, 79 TM 215 TMX 215 transmit IrDA data 110 transmit interrupt 128 transmitting UART data-interrupt-driven method

92 transmitting UART data-polled method 91 TRAP 217

## U

UART 4 architecture 89 baud rate generator 99 baud rates table 107 control register definitions 100 controller signals 10

data format 90 interrupts 97 multiprocessor mode 95 receiving data using interrupt-driven method 94 receiving data using the polled method 93 transmitting data using the interrupt-driven method 92 transmitting data using the polled method 91 x baud rate high and low registers 106 x control 0 and control 1 registers 103 x status 0 and status 1 registers 101, 102 UxBRH register 106 UxBRL register 106 UxCTL0 register 103, 106 UxCTL1 register 104 UxRXD register 101 UxSTAT0 register 101 UxSTAT1 register 102 UxTXD register 100

## V

vector 211 voltage brown-out reset (VBR) 41

## W

watch-dog timer approximate time-out delay 83 CNTL 42 control register 86 electrical characteristics and timing 197 interrupt in normal operation 84 refresh 84, 216 reload unlock sequence 85 reload upper, high and low registers 87 reset 42 reset in normal operation 85 reset in STOP mode 84, 85 time-out response 84 WDTCTL register 86 WDTH register 88 WDTL register 88 working register 211