Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 19                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            |                                                           |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0812sj020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### X

# Introduction

This Product Specification provides detailed operating information for Z8 Encore! XP<sup>®</sup> F0822 Series devices within the Z8 Encore! XP Microcontroller (MCU) family of products. Within this document, Z8 Encore! XP<sup>®</sup> F0822 Series is referred as Z8 Encore! XP or the F0822 Series unless specifically stated otherwise.

#### About This Manual

Zilog recommends that you read and understand everything in this manual before setting up and using the product. We have designed this Product Specification to be used either as a *how to* procedural manual or a reference guide to important data.

#### Intended Audience

This document is written for Zilog customers who are experienced at working with microcontrollers, integrated circuits, or printed circuit assemblies.

#### **Manual Conventions**

The following assumptions and conventions are adopted to provide clarity and ease of use:

#### **Courier Typeface**

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various executable items are distinguished from general text by the use of the Courier typeface. Where the use of the font is not indicated, as in the Index, the name of the entity is presented in upper case.

• **Example:** FLAGS[1] is smrf.

#### **Hexadecimal Values**

Hexadecimal values are designated by uppercase *H* suffix and appear in the Courier typeface.

• **Example:** R1 is set to F8H.

#### Brackets

The square brackets [], indicate a register or bus.

• **Example:** For the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

# **Pin Characteristics**

Table 4 provides detailed information on the characteristics for each pin available on Z8 Encore! XP<sup>®</sup> F0822 Series products. Table 4 data is sorted alphabetically by the pin symbol mnemonic.

### **Table 4. Pin Characteristics**

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active Low<br>or<br>Active High | Tri-State<br>Output | Internal<br>Pull-up or<br>Pull-down | Schmitt-Trigger<br>Input | Open Drain<br>Output |

|--------------------|-----------|--------------------|---------------------------------|---------------------|-------------------------------------|--------------------------|----------------------|

| AV <sub>DD</sub>   | N/A       | N/A                | N/A                             | N/A                 | No                                  | No                       | N/A                  |

| AV <sub>SS</sub>   | N/A       | N/A                | N/A                             | N/A                 | No                                  | No                       | N/A                  |

| DBG                | I/O       | I                  | N/A                             | Yes                 | No                                  | Yes                      | Yes                  |

| PA[7:0]            | I/O       | I                  | N/A                             | Yes                 | Programmable<br>Pull-up             | Yes                      | Yes,<br>Programmable |

| PB[4:0]            | I/O       | I                  | N/A                             | Yes                 | Programmable<br>Pull-up             | Yes                      | Yes,<br>Programmable |

| PC[5:0]            | I/O       | I                  | N/A                             | Yes                 | Programmable<br>Pull-up             | Yes                      | Yes,<br>Programmable |

| RESET              | I         | I                  | Low                             | N/A                 | Pull-up                             | Yes                      | N/A                  |

| V <sub>DD</sub>    | N/A       | N/A                | N/A                             | N/A                 | No                                  | No                       | N/A                  |

| VREF               | Analog    | N/A                | N/A                             | N/A                 | No                                  | No                       | N/A                  |

| V <sub>SS</sub>    | N/A       | N/A                | N/A                             | N/A                 | No                                  | No                       | N/A                  |

| XIN                | I         | I                  | N/A                             | N/A                 | No                                  | No                       | N/A                  |

| XOUT               | 0         | 0                  | N/A                             | No                  | No                                  | No                       | No                   |

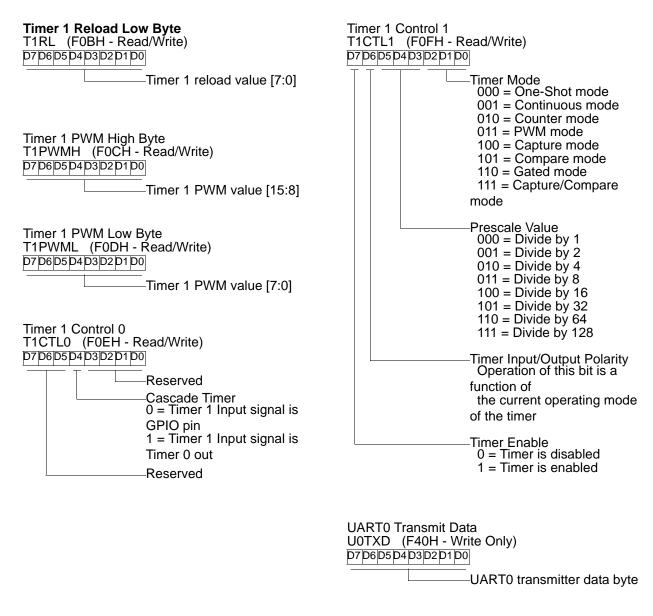

UART0 Receive Data U0RXD (F40H - Read Only) D7D6D5D4D3D2D1D0

—UART0 receiver data byte

PS022517-0508

20

Port B Address PBADDR (FD4H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 Port B Address[7:0] Selects Port Sub-Registers: 00H = No function 01H = Data direction 02H = Alternate function03H = Output control (opendrain) 04H = High drive enable05H = STOP mode recovery enable 06H = Pull-up enable07H-FFH = No function Port B Control PBCTL (FD5H - Read/Write) D7D6D5D4D3D2D1D0 Port B Control [4:0] Provides Access to Port Sub-Registers Reserved Port B Input Data PBIN (FD6H - Read Only) D7 D6 D5 D4 D3 D2 D1 D0 -Port B Input Data [4:0] -Reserved Port B Output Data PBOUT (FD7H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0

Port B Output Data [4:0]

pins.To determine the alternate function associated with each port pin, see GPIO Port Pin Block Diagram on page 48.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline can result in unpredictable operation.

Table 17. Port A–CA–C Alternate Function Sub-Registers

| BITS  | 7        | 6                               | 5           | 4             | 3            | 2             | 1            | 0        |  |  |

|-------|----------|---------------------------------|-------------|---------------|--------------|---------------|--------------|----------|--|--|

| FIELD | AF7      | AF7 AF6 AF5 AF4 AF3 AF2 AF1 AF0 |             |               |              |               |              |          |  |  |

| RESET | 0        |                                 |             |               |              |               |              |          |  |  |

| R/W   |          | R/W                             |             |               |              |               |              |          |  |  |

| ADDR  | lf 02H i | n Port A–C                      | Address Reg | gister, acces | sible throug | h the Port A- | -C Control F | Register |  |  |

#### AF[7:0]—Port Alternate Function enabled

- 0 = The port pin is in NORMAL mode and the DDx bit in the Port A–C Data Direction sub-register determines the direction of the pin.

- 1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A–C Output Control Sub-Registers

The Port A–C Output Control sub-register (Table 18) is accessed through the Port A–C Control Register by writing 03H to the Port A–C Address Register. Setting the bits in the Port A–C Output Control sub-registers to 1 configures the specified port pins for open-drain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

| Table 18. Por | t A-C Output | t Control Sub-Regis | sters |

|---------------|--------------|---------------------|-------|

|---------------|--------------|---------------------|-------|

| BITS  | 7        | 6                                      | 5           | 4             | 3            | 2            | 1            | 0        |  |  |  |

|-------|----------|----------------------------------------|-------------|---------------|--------------|--------------|--------------|----------|--|--|--|

| FIELD | POC7     | POC7 POC6 POC5 POC4 POC3 POC2 POC1 POC |             |               |              |              |              |          |  |  |  |

| RESET |          | 0                                      |             |               |              |              |              |          |  |  |  |

| R/W   |          | R/W                                    |             |               |              |              |              |          |  |  |  |

| ADDR  | lf 03H i | n Port A–C                             | Address Reo | gister, acces | sible throug | h the Port A | -C Control F | Register |  |  |  |

#### POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

0 = The drains are enabled for any output mode (unless overridden by the

# Port A–C Output Data Register

The Port A–C Output Data Register (Table 23) controls the output data to the pins.

#### Table 23. Port A–C Output Data Register (PxOUT)

| BITS  | 7     | 6                                              | 5 | 4        | 3        | 2 | 1 | 0 |  |  |

|-------|-------|------------------------------------------------|---|----------|----------|---|---|---|--|--|

| FIELD | POUT7 | POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT |   |          |          |   |   |   |  |  |

| RESET | 0     |                                                |   |          |          |   |   |   |  |  |

| R/W   |       | R/W                                            |   |          |          |   |   |   |  |  |

| ADDR  |       |                                                |   | FD3H, FD | 7H, FDBH |   |   |   |  |  |

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

| Priority | Program Memory<br>Vector Address | Interrupt Source                      |

|----------|----------------------------------|---------------------------------------|

|          | 0008H                            | Reserved                              |

|          | 000AH                            | Timer 1                               |

|          | 000CH                            | Timer 0                               |

|          | 000EH                            | UART 0 receiver                       |

|          | 0010H                            | UART 0 transmitter                    |

|          | 0012H                            | l <sup>2</sup> C                      |

|          | 0014H                            | SPI                                   |

|          | 0016H                            | ADC                                   |

|          | 0018H                            | Port A7, rising or falling input edge |

|          | 001AH                            | Port A6, rising or falling input edge |

|          | 001CH                            | Port A5, rising or falling input edge |

|          | 001EH                            | Port A4, rising or falling input edge |

|          | 0020H                            | Port A3, rising or falling input edge |

|          | 0022H                            | Port A2, rising or falling input edge |

|          | 0024H                            | Port A1, rising or falling input edge |

|          | 0026H                            | Port A0, rising or falling input edge |

|          | 0028H                            | Reserved                              |

|          | 002AH                            | Reserved                              |

|          | 002CH                            | Reserved                              |

|          | 002EH                            | Reserved                              |

|          | 0030H                            | Port C3, both input edges             |

|          | 0032H                            | Port C2, both input edges             |

|          | 0034H                            | Port C1, both input edges             |

| Lowest   | 0036H                            | Port C0, both input edges             |

|          |                                  |                                       |

# Table 24. Interrupt Vectors in Order of Priority (Continued)

#### Reserved—Must be 0

**NEWFRM**—Status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame.

1 = The current byte is the first data byte of a new frame.

#### MPRX—Multiprocessor Receive

Returns the value of the last multiprocessor bit received. Reading from the UART Receive Data Register resets this bit to 0.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 56 and Table 57 on page 104) configure the properties of the UART's transmit and receive operations. The UART Control Registers must not been written while the UART is enabled.

#### Table 56. UART Control 0 Register (U0CTL0)

| BITS  | 7   | 6                                    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----|--------------------------------------|---|---|---|---|---|---|--|--|

| FIELD | TEN | TEN REN CTSE PEN PSEL SBRK STOP LBEN |   |   |   |   |   |   |  |  |

| RESET | 0   |                                      |   |   |   |   |   |   |  |  |

| R/W   |     | R/W                                  |   |   |   |   |   |   |  |  |

| ADDR  |     | F42H                                 |   |   |   |   |   |   |  |  |

#### **TEN—Transmit Enable**

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

- 0 = Transmitter disabled.

- 1 = Transmitter enabled.

#### **REN**—Receive Enable

This bit enables or disables the receiver.

- 0 = Receiver disabled.

- 1 =Receiver enabled.

#### CTSE—CTS Enable

$0 = \text{The } \overline{\text{CTS}}$  signal has no effect on the transmitter.

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter.

#### **PEN—Parity Enable**

This bit enables or disables parity. Even or odd is determined by the PSEL bit. This bit is overridden by the MPEN bit.

- 0 =Parity is disabled.

- 1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.

#### **PSEL—Parity Select**

0 = Even parity is transmitted and expected on all received data.

1 = Odd parity is transmitted and expected on all received data.

#### SBRK—Send Break

This bit pauses or breaks data transmission by forcing the Transmit data output to 0. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit. The UART does not automatically generate a STOP Bit when SBRK is deasserted. Software must time the duration of the Break and the duration of any STOP Bit time desired following the Break.

- 0 = No break is sent.

- 1 = The output of the transmitter is zero.

#### **STOP—STOP Bit Select**

0 = The transmitter sends one stop bit.

1 = The transmitter sends two stop bits.

#### LBEN—Loop Back Enable

0 = Normal operation.

1 = All transmitted data is looped back to the receiver.

#### Table 57. UART Control 1 Register (U0CTL1)

| BITS  | 7                                                 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---------------------------------------------------|------|---|---|---|---|---|---|--|--|

| FIELD | MPMD[1] MPEN MPMD[0] MPBT DEPOL BRGCTL RDAIRQ IRE |      |   |   |   |   |   |   |  |  |

| RESET | 0                                                 |      |   |   |   |   |   |   |  |  |

| R/W   |                                                   | R/W  |   |   |   |   |   |   |  |  |

| ADDR  |                                                   | F43H |   |   |   |   |   |   |  |  |

#### MPMD[1:0]—Multiprocessor Mode

If Multiprocessor (9-bit) mode is enabled,

- 00 = The UART generates an interrupt request on all received bytes (data and address).

- 01 = The UART generates an interrupt request only on received address bytes.

- 10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

- 11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—Multiprocessor (9-bit) Enable

This bit is used to enable Multiprocessor (9-bit) mode.

- 0 =Disable Multiprocessor (9-bit) mode.

- 1 = Enable Multiprocessor (9-bit) mode.

#### Table 58. UART Address Compare Register (U0ADDR)

| BITS  | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------|---|---|---|---|---|---|--|--|--|

| FIELD |   | COMP_ADDR |   |   |   |   |   |   |  |  |  |

| RESET | 0 |           |   |   |   |   |   |   |  |  |  |

| R/W   |   | R/W       |   |   |   |   |   |   |  |  |  |

| ADDR  |   | F45H      |   |   |   |   |   |   |  |  |  |

#### **COMP\_ADDR**—Compare Address

This 8-bit value is compared to the incoming address bytes.

# **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High and Low Byte registers (Table 59 and Table 60) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

#### Table 59. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7   | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|-----|-----|---|----|----|---|---|---|--|

| FIELD | BRH |     |   |    |    |   |   |   |  |

| RESET | 1   |     |   |    |    |   |   |   |  |

| R/W   |     | R/W |   |    |    |   |   |   |  |

| ADDR  |     |     |   | F4 | 6H |   |   |   |  |

#### Table 60. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----|------|---|---|---|---|---|---|--|--|

| FIELD | BRL |      |   |   |   |   |   |   |  |  |

| RESET | 1   |      |   |   |   |   |   |   |  |  |

| R/W   | R/W |      |   |   |   |   |   |   |  |  |

| ADDR  |     | F47H |   |   |   |   |   |   |  |  |

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \text{ xUART Baud Rate Divisor Value}}$

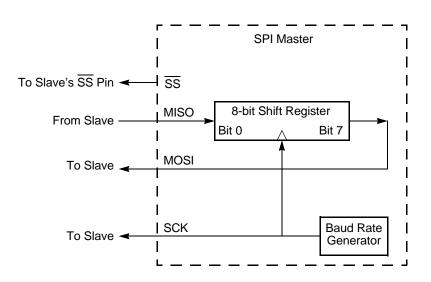

# **Serial Peripheral Interface**

The Serial Peripheral Interface (SPI) is a synchronous interface allowing several SPI-type devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, and character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-half the system clock frequency

- Error detection

- Dedicated Baud Rate Generator

The SPI is not available in 20-pin package devices.

# Architecture

The SPI is be configured as either a Master (in single or multi-master systems) or a Slave as displayed in Figure 20 through Figure 22.

#### Figure 20. SPI Configured as a Master in a Single Master, Single Slave System

# **SPI Control Register**

The SPI Control Register configures the SPI for transmit and receive operations.

#### Table 64. SPI Control Register (SPICTL)

| BITS  | 7    | 6   | 5          | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-------|------|-----|------------|----|----|---|---|---|--|--|--|--|

| FIELD | IRQE | STR | MMEN SPIEN |    |    |   |   |   |  |  |  |  |

| RESET |      | 0   |            |    |    |   |   |   |  |  |  |  |

| R/W   |      | R/W |            |    |    |   |   |   |  |  |  |  |

| ADDR  |      |     |            | F6 | 1H |   |   |   |  |  |  |  |

#### **IRQE**—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

#### STR—Start an SPI Interrupt Request

- 0 = No effect.

- 1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status Register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status Register clears this bit to 0.

#### **BIRQ—BRG Timer Interrupt Request**

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

- 0 = BRG timer function is disabled.

- 1 = BRG timer function and time-out interrupt are enabled.

#### **PHASE**—Phase Select

Sets the phase relationship of the data to the clock. For more information on operation of the PHASE bit, see SPI Clock Phase and Polarity Control on page 116.

#### **CLKPOL**—Clock Polarity

- 0 = SCK idles Low (0).

- 1 = SCK idle High (1).

#### WOR-Wire-OR (Open-Drain) Mode Enabled

0 = SPI signal pins not configured for open-drain.

$1 = \text{All four SPI signal pins (SCK, \overline{SS}, MISO, MOSI)}$  configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

#### MMEN—SPI MASTER Mode Enable

0 = SPI configured in SLAVE mode.

1 = SPI configured in MASTER mode.

#### SPIEN—SPI Enable

- 0 = SPI disabled.

- 1 = SPI enabled.

#### **BRH = SPI Baud Rate High Byte**

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

### Table 69. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|--|

| FIELD |   | BRL |   |    |    |   |   |   |  |  |  |

| RESET |   | 1   |   |    |    |   |   |   |  |  |  |

| R/W   |   | R/W |   |    |    |   |   |   |  |  |  |

| ADDR  |   |     |   | F6 | 7H |   |   |   |  |  |  |

### **BRL = SPI Baud Rate Low Byte**

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

Receive interrupts occur when a byte of data has been received by the  $I^2C$  Controller (Master reading data from Slave). This procedure sets the RDRF bit of the  $I^2C$  Status Register. The RDRF bit is cleared by reading the  $I^2C$  Data Register. The RDRF bit is set during the acknowledge phase. The  $I^2C$  Controller pauses after the acknowledge phase until the receive interrupt is cleared before performing any other action.

Transmit interrupts occur when the TDRE bit of the  $I^2C$  Status register sets and the TXI bit in the  $I^2C$  Control Register is set. Transmit interrupts occur under the following conditions when the Transmit Data Register is empty:

- The I<sup>2</sup>C Controller is enabled

- The first bit of the byte of an address is shifting out and the RD bit of the I<sup>2</sup>C Status register is deasserted.

- The first bit of a 10-bit address shifts out.

- The first bit of write data shifts out.

**Note:** Writing to the  $I^2C$  Data Register always clears the TRDE bit to 0. When TDRE is asserted, the  $I^2C$  Controller pauses at the beginning of the Acknowledge cycle of the byte currently shifting out until the data register is written with the next value to send or the STOP or START bits are set indicating the current byte is the last one to send.

The fourth interrupt source is the BRG. If the I<sup>2</sup>C Controller is disabled (IEN bit in the I2CCTL Register = 0) and the BIRQ bit in the I2CCTL Register = 1, an interrupt is generated when the BRG counts down to 1. This allows the I<sup>2</sup>C Baud Rate Generator to be used by software as a general purpose timer when IEN = 0.

# Software Control of I<sup>2</sup>C Transactions

Software controls I<sup>2</sup>C transactions by using the I<sup>2</sup>C Controller interrupt, by polling the I<sup>2</sup>C Status register or by DMA. Note that not all products include a DMA Controller.

To use interrupts, the  $I^2C$  interrupt must be enabled in the Interrupt Controller. The TXI bit in the  $I^2C$  Control Register must be set to enable transmit interrupts.

To control transactions by polling, the interrupt bits (TDRE, RDRF and NCKI) in the  $I^2C$  Status Register should be polled. The TDRE bit asserts regardless of the state of the TXI bit.

Either or both transmit and receive data movement can be controlled by the DMA Controller. The DMA Controller channel(s) must be initialized to select the I<sup>2</sup>C transmit and receive requests. Transmit DMA requests require that the TXI bit in the I<sup>2</sup>C Control Register be set.

**Caution:** A transmit (write) DMA operation hangs if the slave responds with a Not Acknowledge before the last byte has been sent. After receiving the Not Acknowledge, the I<sup>2</sup>C Controller sets the NCKI bit in the Status Register and pauses until either the STOP or

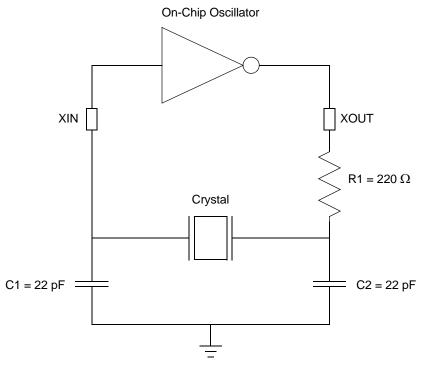

Figure 34. Recommended 20 MHz Crystal Oscillator Configuration

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 25          | W     | Maximum  |

| Load Capacitance (CL)               | 20          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

Table 91. Recommended Crystal Oscillator Specifications (20 MHz Operation)

# **Oscillator Operation with an External RC Network**

The External RC oscillator mode is applicable to timing insensitive applications. Figure 35 on page 169 displays a recommended configuration for connection with an external resistor-capacitor (RC) network.

Table 118. Arithmetic Instructions (Continued)

| Mnemonic Operands |          | Instruction                                   |

|-------------------|----------|-----------------------------------------------|

| SBC               | dst, src | Subtract with Carry                           |

| SBCX              | dst, src | Subtract with Carry using Extended Addressing |

| SUB               | dst, src | Subtract                                      |

| SUBX              | dst, src | Subtract using Extended Addressing            |

Table 119. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | —           | Complement Carry Flag                                |

| RCF      | —           | Reset Carry Flag                                     |

| SCF      | —           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 120. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| Assembly         | Symbolic<br>Operation       | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   |   | Fetch  | Instr. |

|------------------|-----------------------------|-----------------|-----|-------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic         |                             | dst             | src | (Hex)       | С     | Ζ | S | V | D | Н | Cycles | Cycles |

| ADD dst, src     | $dst \gets dst + src$       | r               | r   | 02          | *     | * | * | * | 0 | * | 2      | 3      |

|                  |                             | r               | lr  | 03          | -     |   |   |   |   |   | 2      | 4      |

|                  |                             | R               | R   | 04          | -     |   |   |   |   |   | 3      | 3      |

|                  |                             | R               | IR  | 05          | -     |   |   |   |   |   | 3      | 4      |

|                  |                             | R               | IM  | 06          | -     |   |   |   |   |   | 3      | 3      |

|                  |                             | IR              | IM  | 07          | -     |   |   |   |   |   | 3      | 4      |

| ADDX dst, src    | $dst \gets dst + src$       | ER              | ER  | 08          | *     | * | * | * | 0 | * | 4      | 3      |

|                  |                             | ER              | IM  | 09          | -     |   |   |   |   |   | 4      | 3      |

| AND dst, src     | $dst \gets dst \ AND \ src$ | r               | r   | 52          | -     | * | * | 0 | - | - | 2      | 3      |

|                  |                             | r               | lr  | 53          | -     |   |   |   |   |   | 2      | 4      |

|                  |                             | R               | R   | 54          | -     |   |   |   |   |   | 3      | 3      |

|                  |                             | R               | IR  | 55          | -     |   |   |   |   |   | 3      | 4      |

|                  |                             | R               | IM  | 56          | -     |   |   |   |   |   | 3      | 3      |

|                  |                             | IR              | IM  | 57          | -     |   |   |   |   |   | 3      | 4      |

| ANDX dst, src    | $dst \gets dst \ AND \ src$ | ER              | ER  | 58          | -     | * | * | 0 | - | - | 4      | 3      |

|                  |                             | ER              | IM  | 59          | -     |   |   |   |   |   | 4      | 3      |

| BCLR bit, dst    | dst[bit] ← 0                | r               |     | E2          | -     | - | - | - | - | - | 2      | 2      |

| BIT p, bit, dst  | dst[bit] ← p                | r               |     | E2          | -     | - | - | - | - | - | 2      | 2      |

| BRK              | Debugger Break              |                 |     | 00          | -     | - | - | - | - | - | 1      | 1      |

| BSET bit, dst    | dst[bit] ← 1                | r               |     | E2          | -     | - | - | - | - | - | 2      | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]         | R               |     | D5          | Х     | * | * | 0 | - | - | 2      | 2      |

| BTJ p, bit, src, | if src[bit] = p             |                 | r   | F6          | -     | - | - | - | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$      |                 | lr  | F7          | -     |   |   |   |   |   | 3      | 4      |

| BTJNZ bit, src,  |                             |                 | r   | F6          | -     | - | - | - | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$      |                 | lr  | F7          | -     |   |   |   |   |   | 3      | 4      |

| BTJZ bit, src,   | if src[bit] = 0             |                 | r   | F6          | -     | - | - | - | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$      |                 | lr  | F7          | -     |   |   |   |   |   | 3      | 4      |

# Table 126. eZ8 CPU Instruction Summary (Continued)

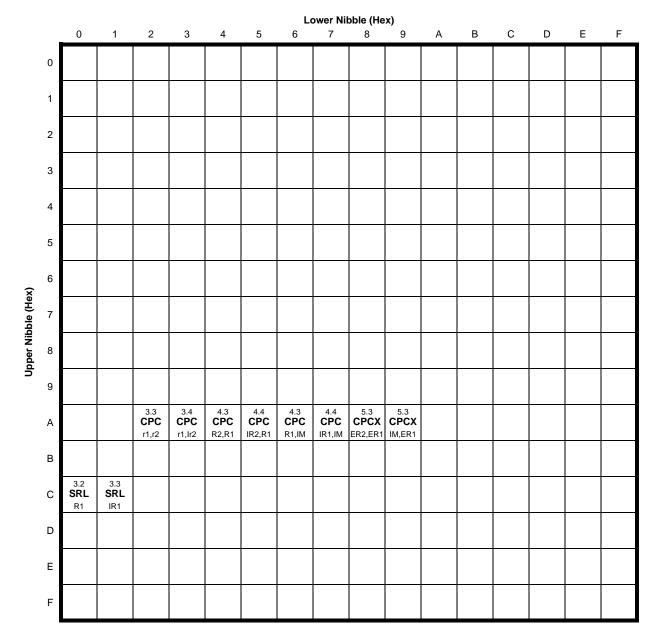

Figure 59. Second Opcode Map after 1FH

232

# Packaging

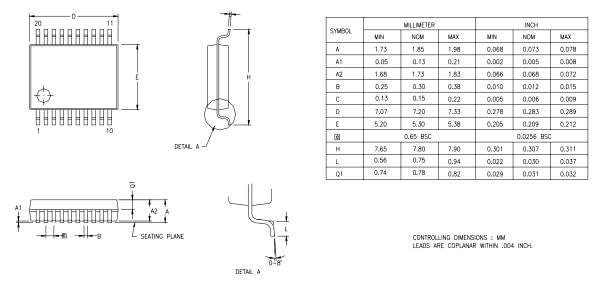

Figure 60 displays the 20-pin SSOP package available for Z8 Encore!  $XP^{\mbox{\sc B}}$  F0822 Series devices.

Figure 60. 20-Pin Small Shrink Outline Package (SSOP)

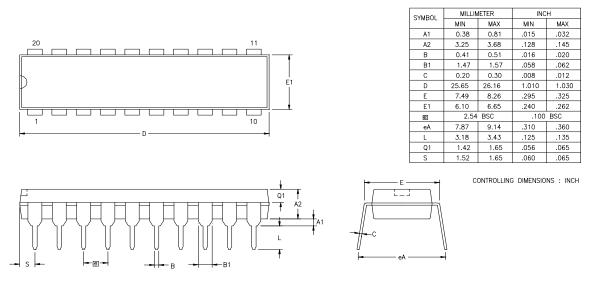

Figure 61 displays the 20-pin PDIP package available for Z8 Encore! XP F0822 Series devices.

Figure 61. 20-Pin Plastic Dual-Inline Package (PDIP)

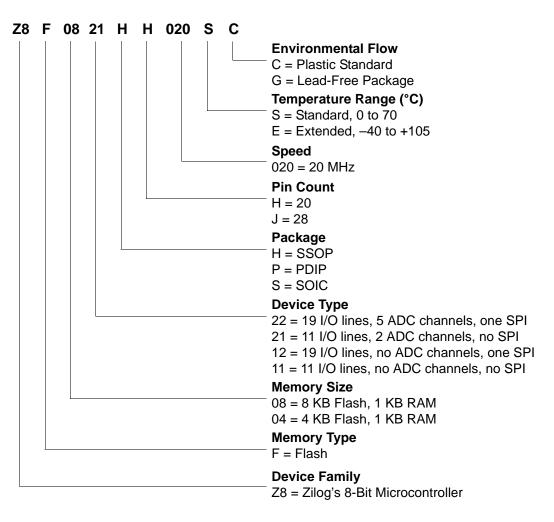

# Part Number Suffix Designations

For example, part number Z8F0821HH020SC is a Z8 Encore! XP Flash 8 KB microcontroller in a 20-pin SSOP package, operating with a maximum 20 MHz external clock frequency over a 0  $^{\circ}$ C to +70  $^{\circ}$ C temperature range and built using the Plastic-Standard environmental flow.