# E·XFL

#### Zilog - Z8F0821HH020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                         |

| Number of I/O              | 11                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 2x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0821hh020sc00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Introduction

Zilog's Z8 Encore! XP<sup>®</sup> MCU product family is a line of Zilog microcontrollers based on the 8-bit eZ8 CPU. Z8 Encore! XP<sup>®</sup> F0822 Series, hereafter referred as Z8 Encore! XP or the 8K Series adds Flash memory to Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming allows faster development time and program changes in the field. The new eZ8 CPU is upward-compatible with the existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

#### **Features**

The features of Z8 Encore! XP MCU product family include:

- 20 MHz eZ8 CPU core

- Up to 8 KB Flash with in-circuit programming capability

- 1 KB Register RAM

- Optional 2- to 5-channel, 10-bit Analog-to-Digital Converter (ADC)

- Full-duplex 9-bit Universal Asynchronous Receiver/Transmitter (UART) with bus transceiver Driver Enable Control

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Serial Peripheral Interface (SPI)

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders

- Two 16-bit timers with Capture, Compare, and PWM capability

- Watchdog Timer (WDT) with internal RC oscillator

- 11 to 19 Input/Output pins depending upon package

- Up to 19 interrupts with configurable priority

- On-Chip Debugger (OCD)

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

- Crystal oscillator with three power settings and RC oscillator option

- 2.7 V to 3.6 V operating voltage with 5 V-tolerant inputs

- 20-pin and 28-pin packages

- 0 °C to +70 °C standard temperature and -40 °C to +105 °C extended temperature operating ranges

## **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\text{®}}$  F0822 Series product line.

| Dert           | Flash | RAM  |     | 16-bit<br>Timers | ADC | UARTs     |                  |     | Package Pin<br>Counts |    |

|----------------|-------|------|-----|------------------|-----|-----------|------------------|-----|-----------------------|----|

| Part<br>Number | (KB)  | (KB) | I/O | with PWM         | -   | with IrDA | I <sup>2</sup> C | SPI | 20                    | 28 |

| Z8F0822        | 8     | 1    | 19  | 2                | 5   | 1         | 1                | 1   |                       | Х  |

| Z8F0821        | 8     | 1    | 11  | 2                | 2   | 1         | 1                |     | Х                     |    |

| Z8F0812        | 8     | 1    | 19  | 2                | 0   | 1         | 1                | 1   |                       | Х  |

| Z8F0811        | 8     | 1    | 11  | 2                | 0   | 1         | 1                |     | Х                     |    |

| Z8F0422        | 4     | 1    | 19  | 2                | 5   | 1         | 1                | 1   |                       | Х  |

| Z8F0421        | 4     | 1    | 11  | 2                | 2   | 1         | 1                |     | Х                     |    |

| Z8F0412        | 4     | 1    | 19  | 2                | 0   | 1         | 1                | 1   |                       | Х  |

| Z8F0411        | 4     | 1    | 11  | 2                | 0   | 1         | 1                |     | Х                     |    |

# Table 1. Z8 Encore! XP<sup>®</sup> F0822 Series Part Selection Guide

| Signal<br>Mnemonic | ; I/O    | Description                                                                                                                                                                                                                                                                                                                                          |

|--------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        | S        |                                                                                                                                                                                                                                                                                                                                                      |

| XIN                | I        | <b>External Crystal Input</b> —This is the input pin to the crystal oscillator. A crystal is connected between the external crystal input and the XOUT pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock to the system.                                      |

| XOUT               | 0        | <b>External Crystal Output</b> —This pin is the output of the crystal oscillator. A crystal is connected between external crystal output and the XIN pin to form the oscillator. When the system clock is referred in this manual, it refers to the frequency of the signal at this pin. This pin must be left unconnected when not using a crystal. |

| On-Chip D          | ebugger  |                                                                                                                                                                                                                                                                                                                                                      |

| DBG                | I/O      | <b>Debug</b> —This pin is the control and data input and output to and from the OCD. This pin is open-drain.                                                                                                                                                                                                                                         |

| !                  | Caution: | For operation of the OCD, all power pins $(V_{DD} \text{ and } AV_{DD})$ must be supplied<br>with power and all ground pins $(V_{SS} \text{ and } AV_{SS})$ must be properly grounded.<br>The DBG pin is open-drain and must have an external pull-up resistor to ensure<br>proper operation.                                                        |

| Reset              |          |                                                                                                                                                                                                                                                                                                                                                      |

| RESET              | I        | RESET—Generates a Reset when asserted (driven Low).                                                                                                                                                                                                                                                                                                  |

| Power Sup          | oply     |                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>DD</sub>    | I        | Digital Power Supply.                                                                                                                                                                                                                                                                                                                                |

| $AV_{DD}$          | Ι        | <b>Analog Power Supply</b> —Must be powered up and grounded to VDD, even if not using analog features.                                                                                                                                                                                                                                               |

| V <sub>SS</sub>    | Ι        | Digital Ground.                                                                                                                                                                                                                                                                                                                                      |

| AV <sub>SS</sub>   | Ι        | Analog Ground—Must be grounded and connected to VSS, even if not using analog features.                                                                                                                                                                                                                                                              |

## Table 3. Signal Descriptions (Continued)

28

#### ADC Control ADCCTL (F70H - Read/Write) D7D6D5D4D3D2D1D0

| <br> | <br>-                                                                                                        |                 |

|------|--------------------------------------------------------------------------------------------------------------|-----------------|

|      | Analog Input Sele                                                                                            | ct<br>0001 =    |

|      | ANA1<br>0010 = ANA2                                                                                          | 0011 =          |

|      | ANA3<br>0100 = ANA4<br>0101 through 21<br>Reserved                                                           | 111 =           |

|      | <br>-Continuous Mode<br>0 = Single-shot c<br>1 = Continuous c                                                | conversion      |

|      | <br>External VREF se<br>0 = Internal volta<br>reference selected<br>1 = External volta<br>reference selected | ige<br>d<br>age |

|      | <br>-Reserved                                                                                                |                 |

|      | -Conversion Enabl<br>0 = Conversion i<br>1 = Begin conve                                                     | s complete      |

# ADC Data High Byte ADCD\_H (F72H - Read Only) D7D6D5D4D3D2D1D0 ADC Data [9:2]

#### ADC Data Low Bits ADCD\_L (F73H - Read Only) D7D6D5D4D3D2D1D0

\_\_\_\_\_ADC Data [1:0]

#### **Power-On Reset**

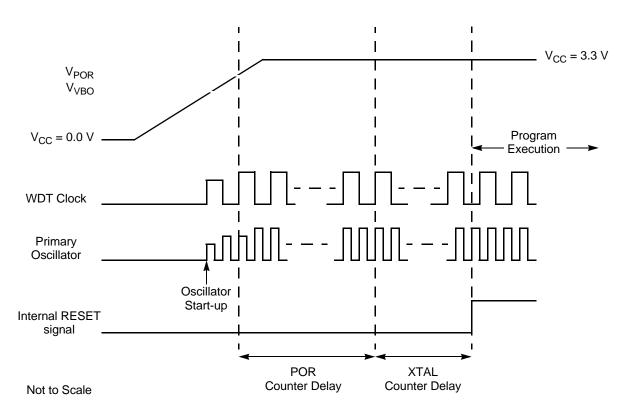

Each device in the Z8 Encore!  $XP^{(B)}$  F0822 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 66 cycles of the WDT oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The device is held in the Reset state until both the POR Counter and XTAL counter have timed out. After the Z8 Encore! XP F0822 Series device exits the POR state, the eZ8 CPU fetches the Reset vector. Following POR, the POR status bit in the Watchdog Timer Control Register (WDTCTL) is set to 1.

Figure 6 displays POR operation. See Electrical Characteristics for POR threshold voltage  $(V_{POR})$ .

Figure 6. Power-On Reset Operation

#### **Voltage Brownout Reset**

The devices in Z8 Encore! XP F0822 Series provide low Voltage Brownout protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage

#### Port A–C Control Registers

The Port A–C Control Registers set the GPIO port operation. The value in the corresponding Port A–C Address Register determines the control sub-registers accessible using the Port A–C Control Register (Table 15).

#### Table 15. Port A–C Control Registers (PxCTL)

| BITS  | 7 | 6    | 5 | 4        | 3        | 2 | 1 | 0 |  |  |  |

|-------|---|------|---|----------|----------|---|---|---|--|--|--|

| FIELD |   | PCTL |   |          |          |   |   |   |  |  |  |

| RESET |   | 00H  |   |          |          |   |   |   |  |  |  |

| R/W   |   | R/W  |   |          |          |   |   |   |  |  |  |

| ADDR  |   |      |   | FD1H, FD | 5H, FD9H |   |   |   |  |  |  |

#### PCTL[7:0]—Port Control

The Port Control Register provides access to all sub-registers that configure the GPIO Port operation.

#### Port A–C Data Direction Sub-Registers

The Port A–C Data Direction sub-register is accessed through the Port A–C Control register by writing 01H to the Port A–C Address Register (Table 16).

#### Table 16. Port A–C Data Direction Sub-Registers

| BITS  | 7        | 6          | 5           | 4             | 3            | 2            | 1            | 0        |  |  |  |

|-------|----------|------------|-------------|---------------|--------------|--------------|--------------|----------|--|--|--|

| FIELD | DD7      | DD6        | DD5         | DD4           | DD3          | DD2          | DD1          | DD0      |  |  |  |

| RESET |          | 1          |             |               |              |              |              |          |  |  |  |

| R/W   |          | R/W        |             |               |              |              |              |          |  |  |  |

| ADDR  | lf 01H i | n Port A–C | Address Reg | gister, acces | sible throug | h the Port A | -C Control F | Register |  |  |  |

#### DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

- 0 = Output. Data in the Port A–C Output Data Register is driven onto the port pin.

- 1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tri-stated.

#### Port A–C Alternate Function Sub-Registers

The Port A–C Alternate Function sub-register (Table 17) is accessed through the Port A–C Control Register by writing 02H to the Port A–C Address Register. The Port A–C Alternate Function sub-registers select the alternate functions for the selected

#### **U0RXI—UART 0 Receiver Interrupt Request**

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

#### **U0TXI—UART 0 Transmitter Interrupt Request**

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

#### I2CI—I<sup>2</sup>C Interrupt Request

0 = No interrupt request is pending for the I<sup>2</sup>C.

1 = An interrupt request from the I<sup>2</sup>C is awaiting service.

#### **SPII**—SPI Interrupt Request

0 = No interrupt request is pending for the SPI.

1 = An interrupt request from the SPI is awaiting service.

#### **ADCI**—ADC Interrupt Request

0 = No interrupt request is pending for the ADC.

1 = An interrupt request from the ADC is awaiting service.

#### Interrupt Request 1 Register

The Interrupt Request 1 (IRQ1) Register (Table 26) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the IRQ1 Register to determine if any interrupt requests are pending.

| BITS  | 7    | 6                                                                                               | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|------|-------------------------------------------------------------------------------------------------|---|----|----|---|---|---|--|--|--|

| FIELD | PA7I | PA7I         PA6I         PA5I         PA4I         PA3I         PA2I         PA1I         PA0I |   |    |    |   |   |   |  |  |  |

| RESET |      | 0                                                                                               |   |    |    |   |   |   |  |  |  |

| R/W   |      | R/W                                                                                             |   |    |    |   |   |   |  |  |  |

| ADDR  |      |                                                                                                 |   | FC | 3H |   |   |   |  |  |  |

#### Table 26. Interrupt Request 1 Register (IRQ1)

#### PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin *x*.

1 = An interrupt request from GPIO Port A pin x is awaiting service.

Where *x* indicates the specific GPIO Port pin number (0 through 7).

64

#### Table 29. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6     | 5     | 4      | 3      | 2      | 1      | 0      |  |  |  |  |

|-------|----------|-------|-------|--------|--------|--------|--------|--------|--|--|--|--|

| FIELD | Reserved | T1ENH | T0ENH | U0RENH | U0TENH | I2CENH | SPIENH | ADCENH |  |  |  |  |

| RESET |          | 0     |       |        |        |        |        |        |  |  |  |  |

| R/W   |          | R/W   |       |        |        |        |        |        |  |  |  |  |

| ADDR  |          |       |       | FC     | 1H     |        |        |        |  |  |  |  |

Reserved—Must be 0 T1ENH—Timer 1 Interrupt Request Enable High Bit

**TOENH**—Timer 0 Interrupt Request Enable High Bit **UORENH**—UART 0 Receive Interrupt Request Enable High Bit **UOTENH**—UART 0 Transmit Interrupt Request Enable High Bit **I2CENH**—I<sup>2</sup>C Interrupt Request Enable High Bit **SPIENH**—SPI Interrupt Request Enable High Bit **ADCENH**—ADC Interrupt Request Enable High Bit

#### Table 30. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5     | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|----------|-------|-------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | Reserved | T1ENL | T0ENL | UORENL | U0TENL | I2CENL | SPIENL | ADCENL |  |  |  |

| RESET |          | 0     |       |        |        |        |        |        |  |  |  |

| R/W   |          | R/W   |       |        |        |        |        |        |  |  |  |

| ADDR  |          |       |       | FC     | 2H     |        |        |        |  |  |  |

#### Reserved—Must be 0

**T1ENL**—Timer 1 Interrupt Request Enable Low Bit **T0ENL**—Timer 0 Interrupt Request Enable Low Bit **U0RENL**—UART 0 Receive Interrupt Request Enable Low Bit **U0TENL**—UART 0 Transmit Interrupt Request Enable Low Bit **I2CENL**—I<sup>2</sup>C Interrupt Request Enable Low Bit **SPIENL**—SPI Interrupt Request Enable Low Bit **ADCENL**—ADC Interrupt Request Enable Low Bit

#### **IRQ1 Enable High and Low Bit Registers**

Table 31 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit Registers (Table 32 and Table 33) form a priority encoded enabling for interrupts in the Interrupt Request 1 Register. Priority is generated by setting bits in each register.

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 37) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port input pin. The minimum pulse width must be greater than 1 system clock to guarantee capture of the edge triggered interrupt. Edge detection for pulses less than 1 system clock are not guaranteed.

#### Table 37. Interrupt Edge Select Register (IRQES)

| BITS  | 7    | 6                                       | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|------|-----------------------------------------|---|----|----|---|---|---|--|--|--|

| FIELD | IES7 | IES7 IES6 IES5 IES4 IES3 IES2 IES1 IES0 |   |    |    |   |   |   |  |  |  |

| RESET |      | 0                                       |   |    |    |   |   |   |  |  |  |

| R/W   |      | R/W                                     |   |    |    |   |   |   |  |  |  |

| ADDR  |      |                                         |   | FC | DH |   |   |   |  |  |  |

#### IES*x*—Interrupt Edge Select *x*

0 = An interrupt request is generated on the falling edge of the PAx input.

1 = An interrupt request is generated on the rising edge of the PAx input.

Where *x* indicates the specific GPIO Port pin number (0 through 7).

# Interrupt Control Register

The Interrupt Control (IRQCTL) register (Table 38) contains the master enable bit for all interrupts.

# Table 38. Interrupt Control Register (IRQCTL)

| BITS  | 7    | 6   | 5        | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------|-----|----------|----|----|---|---|---|--|--|

| FIELD | IRQE |     | Reserved |    |    |   |   |   |  |  |

| RESET |      | 0   |          |    |    |   |   |   |  |  |

| R/W   | R/W  | V R |          |    |    |   |   |   |  |  |

| ADDR  |      |     |          | FC | FH |   |   |   |  |  |

#### IRQE—Interrupt Request Enable

This bit is set to 1 by execution of an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.

- 0 = Interrupts are disabled.

- 1 = Interrupts are enabled.

#### Reserved—Must be 0

#### **Receiving Data Using Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte Registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt Control Registers to enable the UART Receiver interrupt and set the required priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request Register.

- 6. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) mode functions, if desired.

- Set the Multiprocessor Mode Select (MPEN) to enable MULTIPROCESSOR mode.

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the required address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic multiprocessor modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if required, and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver Interrupt is detected, the associated ISR performs the following:

- 1. Check the UART Status 0 Register to determine the source of the interrupt-error, break, or received data.

- 2. If the interrupt was due to data available, read the data from the UART Receive Data Register. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the Multiprocessor Mode bits MPMD[1:0].

- 3. Clear the UART Receiver Interrupt in the applicable Interrupt Request Register.

- 4. Execute the IRET instruction to return from the ISR and await more data.

When the UART is disabled, the BRG functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the BRG as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the desired 16-bit count value into the UART Baud Rate High and Low Byte Registers.

- 3. Enable the BRG timer function and associated interrupt by setting the BKGCTL bit in the UART Control 1 Register to 1.

When configured as a general-purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0] ]

## **UART Control Register Definitions**

The UART Control Registers support the UART and the associated Infrared Encoder/ Decoders. See Infrared Encoder/Decoder on page 109 for more information on the infrared operation.

#### **UART Transmit Data Register**

Data bytes written to the UART Transmit Data Register (Table 52) are shifted out on the TXD*x* pin. The Write-only UART Transmit Data Register shares a Register File address with the Read-only UART Receive Data Register.

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|--|--|

| FIELD |   | TXD |   |    |    |   |   |   |  |  |  |  |

| RESET | Х | Х   | Х | Х  | Х  | Х | Х | Х |  |  |  |  |

| R/W   | W | W   | W | W  | W  | W | W | W |  |  |  |  |

| ADDR  |   |     |   | F4 | 0H |   |   |   |  |  |  |  |

Table 52. UART Transmit Data Register (U0TXD)

#### TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXD*x* pin.

START bits in the Control Register are set.

In order for a receive (read) DMA transaction to send a Not Acknowledge on the last byte, the receive DMA must be set up to receive n-1 bytes, then software must set the NAK bit and receive the last (nth) byte directly.

#### **Start and Stop Conditions**

The Master ( $I^2C$ ) drives all Start and Stop signals and initiates all transactions. To start a transaction, the  $I^2C$  Controller generates a START condition by pulling the SDA signal Low while SCL is High. To complete a transaction, the  $I^2C$  Controller generates a Stop condition by creating a low-to-high transition of the SDA signal while the SCL signal is high. The START and STOP bits in the  $I^2C$  Control Register control the sending of the Start and Stop conditions. A Master is also allowed to end one transaction and begin a new one by issuing a Restart. This is accomplished by setting the START bit at the end of a transaction, rather than the STOP bit.

**Note:** The Start condition not sent until the START bit is set and data has been written to the  $I^2C$ Data Register.

#### **Master Write and Read Transactions**

The following sections provide a recommended procedure for performing  $I^2C$  write and read transactions from the  $I^2C$  Controller (Master) to slave  $I^2C$  devices. In general software should rely on the TDRE, RDRF and NCKI bits of the status register (these bits generate interrupts) to initiate software actions. When using interrupts or DMA, the TXI bit is set to start each transaction and cleared at the end of each transaction to eliminate a 'trailing' Transmit Interrupt.

Caution should be used in using the ACK status bit within a transaction because it is difficult for software to tell when it is updated by hardware.

When writing data to a slave, the I<sup>2</sup>C pauses at the beginning of the Acknowledge cycle if the data register has not been written with the next value to be sent (TDRE bit in the I<sup>2</sup>C Status register equal to 1). In this scenario where software is not keeping up with the I<sup>2</sup>C bus (TDRE asserted longer than one byte time), the Acknowledge clock cycle for byte n is delayed until the data register is written with byte n + 1, and appears to be grouped with the data clock cycles for byte n + 1. If either the START or STOP bit is set, the I<sup>2</sup>C does not pause prior to the Acknowledge cycle because no additional data is sent.

When a Not Acknowledge condition is received during a write (either during the address or data phases), the I<sup>2</sup>C Controller generates the Not Acknowledge interrupt (NCKI = 1) and pause until either the STOP or START bit is set. Unless the Not Acknowledge was received on the last byte, the data register will already have been written with the next address or data byte to send. In this case the FLUSH bit of the control register should be set at the same time the STOP or START bit is set to remove the stale transmit data and enable subsequent Transmit Interrupts.

# **Caution:** In CONTINUOUS mode, ensure that ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not seen at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the desired analog input by configuring the GPIO pins for alternate function. This disables the digital input and output driver.

- 2. Write to the ADC Control Register to configure the ADC for continuous conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN [3:0] field to select one of the 5 analog input sources.

- Set CONT to 1 to select continuous conversion.

- Write to the  $\overline{\text{VREF}}$  bit to enable or disable the internal voltage reference generator.

- Set CEN to 1 to start the conversions.

- 3. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete.

- 4. Thereafter, the ADC writes a new 10-bit data result to {ADCD\_H[7:0], ADCD\_L[7:6]} every 256 system clock cycles. An interrupt request is sent to the Interrupt Controller when each conversion is complete.

- 5. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

#### **INFO\_EN**—Information Area Enable

0 = Information Area is not selected.

1 = Information Area is selected. The Information area is mapped into the Flash Memory address space at addresses FE00H through FFFFH.

#### PAGE—Page Select

This 7-bit field selects the Flash memory page for Programming and Page Erase operations. Flash Memory Address[15:9] = PAGE[6:0].

#### Flash Sector Protect Register

The Flash Sector Protect Register (Table 86) protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH. User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code).

|                                                                                                         |       |       | _     |       |       |       |       |       |  |  |

|---------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| BITS                                                                                                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

| FIELD                                                                                                   | SECT7 | SECT6 | SECT5 | SECT4 | SECT3 | SECT2 | SECT1 | SECT0 |  |  |

| RESET                                                                                                   | 0     |       |       |       |       |       |       |       |  |  |

| R/W                                                                                                     | R/W1  |       |       |       |       |       |       |       |  |  |

| ADDR                                                                                                    | FF9H  |       |       |       |       |       |       |       |  |  |

| R/W1 = Register is accessible for Read operations. Register can be written to 1 only (using user code). |       |       |       |       |       |       |       |       |  |  |

Table 86. Flash Sector Protect Register (FPROT)

#### SECT*n*—Sector Protect

0 = Sector *n* can be programmed or erased from user code.

1 = Sector *n* is protected and cannot be programmed or erased from user code. User code can only write bits from 0 to 1.

# Flash Frequency High and Low Byte Registers

The Flash Frequency High and Low Byte Registers (Table 87 and Table 88) combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit Flash Frequency registers must be written with the system clock frequency in kHz for Program and Erase operations. The Flash Frequency value is calculated using the following equation:

$\mathsf{FFREQ[15:0]} = \{\mathsf{FFREQH[7:0]}, \mathsf{FFREQL[7:0]}\} = \frac{\mathsf{System Clock Frequency}}{1000}$

**Caution:** Flash programming and erasure is not supported for system clock frequencies below 20 kHz, above 20 MHz, or outside of the valid operating

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter. If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, the Program Counter values are discarded.

```

DBG \leftarrow 06H

DBG \leftarrow ProgramCounter[15:8]

DBG \leftarrow ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter. If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, this command returns FFFFH.

```

DBG ← 07H

DBG → ProgramCounter[15:8]

DBG → ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the device is not in DEBUG mode, the address and data values are discarded. If the Read Protect Option Bit is enabled, then only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1-256 bytes at a time (256 bytes can be read by setting size to zero). Reading peripheral control registers through the OCD does not effect peripheral operation. For example, register bits that are normally cleared upon a read operation will not be effected (WDTSTAT register is affected by OCD read register operation). If the device is not in DEBUG mode or if the Read Protect Option Bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

# **AC Characteristics**

Table 98 provides information on the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

#### **Table 98. AC Characteristics**

|                     |                                |          | .7 - 3.6 V<br>C to 105 °C |       |                                                                                                          |  |

|---------------------|--------------------------------|----------|---------------------------|-------|----------------------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                      | Minimum  | Maximum                   | Units | Conditions                                                                                               |  |

| F <sub>SYSCLK</sub> | System Clock Frequency (ROM)   | -        | 20.0                      | MHz   |                                                                                                          |  |

| F <sub>SYSCLK</sub> | System Clock Frequency (Flash) | -        | 20.0                      | MHz   | Read-only from Flash memory.                                                                             |  |

|                     |                                | 0.032768 | 20.0                      | MHz   | Program or erasure of the<br>Flash memory.                                                               |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency   | 0.032768 | 20.0                      | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an external<br>clock driver. |  |

| T <sub>XIN</sub>    | System Clock Period            | 50       | _                         | ns    | T <sub>CLK</sub> = 1/F <sub>syscik</sub>                                                                 |  |

| T <sub>XINH</sub>   | System Clock High Time         | 20       | 30                        | ns    | T <sub>CLK</sub> = 50 ns                                                                                 |  |

| T <sub>XINL</sub>   | System Clock Low Time          | 20       | 30                        | ns    | T <sub>CLK</sub> = 50 ns                                                                                 |  |

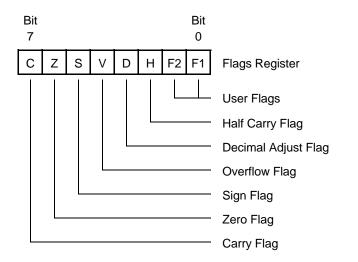

## **Flags Register**

The Flags Register contains the status information regarding the most recent arithmetic, logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits of status information that are set or cleared by CPU operations. Four of the bits (C, V, Z and S) can be tested with conditional jump instructions. Two flags (H and D) cannot be tested and are used for Binary-Coded Decimal (BCD) arithmetic.

The two remaining bits, User Flags (F1 and F2), are available as general-purpose status bits. User Flags are unaffected by arithmetic operations and must be set or cleared by instructions. The User Flags cannot be used with conditional Jumps. They are undefined at initial power-up and are unaffected by Reset. Figure 56 illustrates the flags and their bit positions in the Flags Register.

#### Figure 56. Flags Register

Interrupts, the Software Trap (TRAP) instruction, and Illegal Instruction Traps all write the value of the Flags Register to the stack. Executing an Interrupt Return (IRET) instruction restores the value saved on the stack into the Flags Register.

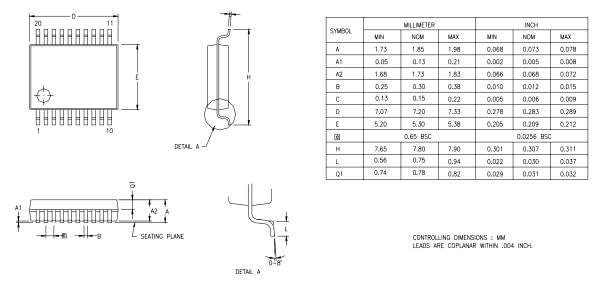

# Packaging

Figure 60 displays the 20-pin SSOP package available for Z8 Encore!  $XP^{\mbox{\sc B}}$  F0822 Series devices.

Figure 60. 20-Pin Small Shrink Outline Package (SSOP)

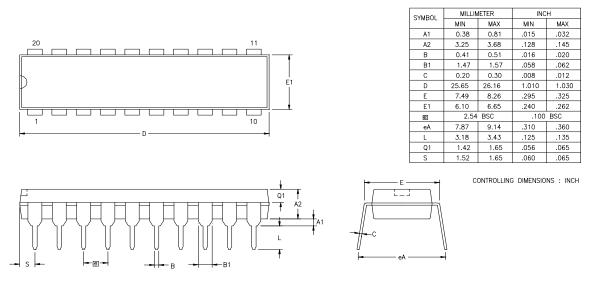

Figure 61 displays the 20-pin PDIP package available for Z8 Encore! XP F0822 Series devices.

Figure 61. 20-Pin Plastic Dual-Inline Package (PDIP)

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

rotate left through carry 218 rotate right 218 rotate right through carry 218 RP 212 RR 211, 218 rr 211 RRC 218

# S

**SBC 215** SCF 215, 216 **SCK 115** SDA and SCL (IrDA) signals 128 second opcode map after 1FH 232 serial clock 115 serial peripheral interface (SPI) 113 set carry flag 215, 216 set register pointer 216 shift right arithmetic 218 shift right logical 218 signal descriptions 9 single-shot conversion (ADC) 148 SIO 5 slave data transfer formats (I2C) 134 slave select 116 software trap 217 source operand 212 SP 212 SPI architecture 113 baud rate generator 120 baud rate high and low byte register 125 clock phase 116 configured as slave 114 control register 122 control register definitions 121 data register 121 error detection 119 interrupts 119 mode fault error 119 mode register 124 multi-master operation 118 operation 114

overrun error 119 signals 115 single master, multiple slave system 114 single master, single slave system 113 status register 123 timing, PHASE = 0.117timing, PHASE=1 118 SPI controller signals 10 SPI mode (SPIMODE) 124 SPIBRH register 125 SPIBRL register 126 SPICTL register 122 SPIDATA register 121 SPIMODE register 124 SPISTAT register 123 **SRA 218** src 212 SRL 218 **SRP 216** SS, SPI signal 115 stack pointer 212 status register, I2C 140 **STOP 216** stop mode 45, 216 stop mode recovery sources 43 using a GPIO port pin transition 44 using watch-dog timer time-out 44 **SUB 215** subtract 215 subtract - extended addressing 215 subtract with carry 215 subtract with carry - extended addressing 215 **SUBX 215 SWAP 218** swap nibbles 218 symbols, additional 212 system and core resets 40

# Т

TCM 215 TCMX 215 test complement under mask 215 248

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <u>http://www.zilog.com/kb</u>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.