Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 2x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0821ph020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **¢** Warning: DO NOT USE IN LIFE SUPPORT

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

## As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Table of Contents**

| Introduction                       |

|------------------------------------|

| About This Manual                  |

| Intended Audience                  |

| Manual Conventionsx                |

| Safeguards                         |

| Abbreviations/Acronymsxii          |

| Introduction                       |

| Features                           |

| Part Selection Guide               |

| Block Diagram                      |

| CPU and Peripheral Overview        |

| eZ8 CPU Features                   |

| General Purpose Input/Output 4     |

| Flash Controller                   |

| 10-Bit Analog-to-Digital Converter |

| UART                               |

| I <sup>2</sup> C                   |

| Serial Peripheral Interface        |

| Timers                             |

| Interrupt Controller               |

| Reset Controller                   |

| On-Chip Debugger                   |

| Signal and Pin Descriptions        |

| Available Packages                 |

| Pin Configurations                 |

| Signal Descriptions                |

| Pin Characteristics                |

| Address Space                      |

| Register File                      |

| Program Memory                     |

| Data Memory                        |

| Information Area                   |

| Register File Address Map 15       |

| Control Register Summary           |

| Reset and Stop Mode Recovery       |

| Reset Types                        |

| System Reset                       |

# **Block Diagram**

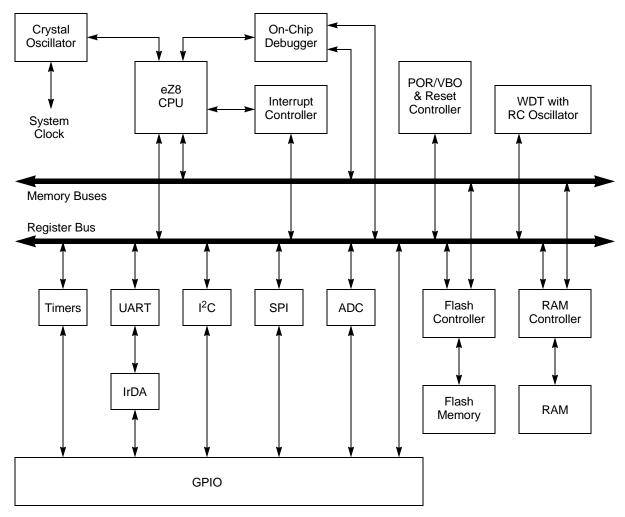

Figure 1 displays the block diagram of the architecture of Z8 Encore!  $XP^{\mbox{\ensuremath{\mathbb{R}}}}$  F0822 Series devices.

Figure 1. Z8 Encore! XP<sup>®</sup> F0822 Series Block Diagram

# **CPU and Peripheral Overview**

# eZ8 CPU Features

Zilog's latest eZ8 8-bit CPU, meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{$ <sup>®</sup> instruction set.

UART0 Receive Data U0RXD (F40H - Read Only) D7D6D5D4D3D2D1D0

—UART0 receiver data byte

PS022517-0508

20

28

# ADC Control ADCCTL (F70H - Read/Write) D7D6D5D4D3D2D1D0

| <br> | <br>-                                                                                                        |                 |

|------|--------------------------------------------------------------------------------------------------------------|-----------------|

|      | Analog Input Sele                                                                                            | ct<br>0001 =    |

|      | ANA1<br>0010 = ANA2                                                                                          | 0011 =          |

|      | ANA3<br>0100 = ANA4<br>0101 through 21<br>Reserved                                                           | 111 =           |

|      | <br>-Continuous Mode<br>0 = Single-shot c<br>1 = Continuous c                                                | conversion      |

|      | <br>External VREF se<br>0 = Internal volta<br>reference selected<br>1 = External volta<br>reference selected | ige<br>d<br>age |

|      | <br>-Reserved                                                                                                |                 |

|      | -Conversion Enabl<br>0 = Conversion i<br>1 = Begin conve                                                     | s complete      |

# ADC Data High Byte ADCD\_H (F72H - Read Only) D7D6D5D4D3D2D1D0 ADC Data [9:2]

#### ADC Data Low Bits ADCD\_L (F73H - Read Only) D7D6D5D4D3D2D1D0

\_\_\_\_\_ADC Data [1:0]

# Stop Mode Recovery Using WDT Time-Out

If the WDT times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the WDT Control Register, the WDT and STOP bits are set to 1. If the WDT is configured to generate an interrupt upon time-out and the Z8 Encore! XP<sup>®</sup> F0822 Series device is configured to respond to interrupts, the eZ8 CPU services the WDT interrupt request following the normal Stop Mode Recovery sequence.

# Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO Port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a STOP Mode Recover source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. The GPIO Stop Mode Recovery signals are filtered to reject pulses less than 10 ns (typical) in duration. In the WDT Control Register, the STOP bit is set to 1.

#### Caution:

In STOP mode, the GPIO Port Input Data Registers (PxIN) are disabled. The Port Input Data Registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. Therefore, short pulses on the Port pin initiates Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

# Port A–C Control Registers

The Port A–C Control Registers set the GPIO port operation. The value in the corresponding Port A–C Address Register determines the control sub-registers accessible using the Port A–C Control Register (Table 15).

# Table 15. Port A–C Control Registers (PxCTL)

| BITS  | 7 | 6    | 5 | 4        | 3        | 2 | 1 | 0 |  |

|-------|---|------|---|----------|----------|---|---|---|--|

| FIELD |   | PCTL |   |          |          |   |   |   |  |

| RESET |   | 00H  |   |          |          |   |   |   |  |

| R/W   |   | R/W  |   |          |          |   |   |   |  |

| ADDR  |   |      |   | FD1H, FD | 5H, FD9H |   |   |   |  |

#### PCTL[7:0]—Port Control

The Port Control Register provides access to all sub-registers that configure the GPIO Port operation.

## Port A–C Data Direction Sub-Registers

The Port A–C Data Direction sub-register is accessed through the Port A–C Control register by writing 01H to the Port A–C Address Register (Table 16).

#### Table 16. Port A–C Data Direction Sub-Registers

| BITS  | 7        | 6          | 5           | 4             | 3            | 2            | 1            | 0        |  |

|-------|----------|------------|-------------|---------------|--------------|--------------|--------------|----------|--|

| FIELD | DD7      | DD6        | DD5         | DD4           | DD3          | DD2          | DD1          | DD0      |  |

| RESET |          | 1          |             |               |              |              |              |          |  |

| R/W   |          | R/W        |             |               |              |              |              |          |  |

| ADDR  | lf 01H i | n Port A–C | Address Reg | gister, acces | sible throug | h the Port A | -C Control F | Register |  |

# DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

- 0 = Output. Data in the Port A–C Output Data Register is driven onto the port pin.

- 1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tri-stated.

#### Port A–C Alternate Function Sub-Registers

The Port A–C Alternate Function sub-register (Table 17) is accessed through the Port A–C Control Register by writing 02H to the Port A–C Address Register. The Port A–C Alternate Function sub-registers select the alternate functions for the selected

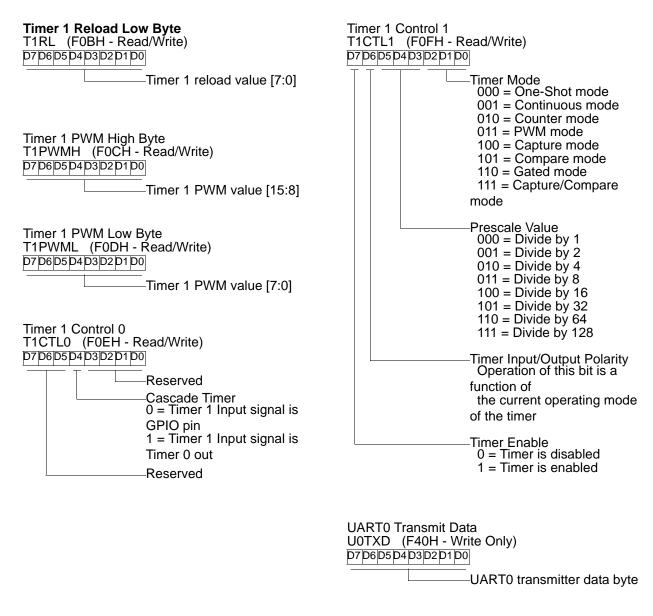

# Table 43. Timer 0–1 PWM High Byte Register (TxPWMH)

| BITS  | 7 | 6    | 5 | 4     | 3    | 2 | 1 | 0 |  |

|-------|---|------|---|-------|------|---|---|---|--|

| FIELD |   | PWMH |   |       |      |   |   |   |  |

| RESET |   | 0    |   |       |      |   |   |   |  |

| R/W   |   | R/W  |   |       |      |   |   |   |  |

| ADDR  |   |      |   | F04H, | F0CH |   |   |   |  |

## Table 44. Timer 0–1 PWM Low Byte Register (TxPWML)

| BITS  | 7 | 6    | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|-------|---|------|---|-------|------|---|---|---|--|--|

| FIELD |   | PWML |   |       |      |   |   |   |  |  |

| RESET |   | 0    |   |       |      |   |   |   |  |  |

| R/W   |   | R/W  |   |       |      |   |   |   |  |  |

| ADDR  |   |      |   | F05H, | F0DH |   |   |   |  |  |

#### PWMH and PWML—Pulse-Width Modulator High and Low Bytes

These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

# Timer 0–3 Control 0 Registers

The Timer 0–3 Control 0 (TxCTL0) registers (Table 45) allow cascading of the Timers.

| BITS  | 7                     | 6   | 5 | 4          | 3          | 2 | 1 | 0 |  |  |

|-------|-----------------------|-----|---|------------|------------|---|---|---|--|--|

| FIELD | Reserved CSC Reserved |     |   |            |            |   |   |   |  |  |

| RESET |                       | 0   |   |            |            |   |   |   |  |  |

| R/W   |                       | R/W |   |            |            |   |   |   |  |  |

| ADDR  |                       |     | F | 06H, F0EH, | F16H, F1EI | Н |   |   |  |  |

#### **CSC—Cascade Timers**

- 0 = Timer Input signal comes from the pin.

- 1 = For Timer 0, input signal is connected to Timer 1 output.

- For Timer 1, input signal is connected to Timer 0 output.

# Timer 0–1 Control 1 Registers

The Timer 0–1 Control (TxCTL) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

## Table 46. Timer 0–1 Control Register (TxCTL)

| BITS  | 7   | 6    | 5 | 4          | 3    | 2 | 1 | 0 |  |  |

|-------|-----|------|---|------------|------|---|---|---|--|--|

| FIELD | TEN | TPOL |   | PRES TMODE |      |   |   |   |  |  |

| RESET |     | 0    |   |            |      |   |   |   |  |  |

| R/W   |     | R/W  |   |            |      |   |   |   |  |  |

| ADDR  |     |      |   | F07H,      | F0FH |   |   |   |  |  |

**TEN**—**Timer** Enable

0 = Timer is disabled.

1 = Timer enabled to count.

#### **TPOL—Timer Input/Output Polarity**

Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

#### **PWM Mode**

- 0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

- 1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

#### **CAPTURE Mode**

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

# **Clear To Send Operation**

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this would be done during STOP bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

# Multiprocessor (9-bit) Mode

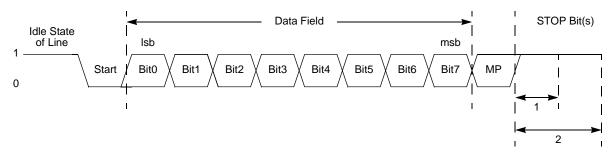

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit is transmitted following the 8-bits of data and immediately preceding the STOP bit(s) as displayed in Figure 14.

Figure 14. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9th bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 Registers provide Multiprocessor (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare Register holds the network address of the device.

# **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When multiprocessor mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software, or combination of the two depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not need to access the UART when it receives data directed to other devices on the

# **SPI Mode Register**

The SPI Mode Register configures the character bit width and the direction and value of the  $\overline{SS}$  pin.

## Table 66. SPI Mode Register (SPIMODE)

| BITS  | 7             | 6     | 5 | 4  | 3                     | 2 | 1 | 0 |  |  |  |

|-------|---------------|-------|---|----|-----------------------|---|---|---|--|--|--|

| FIELD | Reserved DIAG |       |   |    | NUMBITS[2:0] SSIO SSV |   |   |   |  |  |  |

| RESET |               |       |   | (  | )                     |   |   |   |  |  |  |

| R/W   | F             | R R/W |   |    |                       |   |   |   |  |  |  |

| ADDR  |               |       |   | F6 | 3H                    |   |   |   |  |  |  |

#### Reserved—Must be 0

#### **DIAG-Diagnostic Mode Control bit**

This bit is for SPI diagnostics. Setting this bit allows the BRG value to be read using the SPIBRH and SPIBRL Register locations.

0 = Reading SPIBRH, SPIBRL returns the value in the SPIBRH and SPIBRL Registers 1 = Reading SPIBRH returns bits [15:8] of the SPI Baud Rate Generator; and reading SPIBRL returns bits [7:0] of the SPI Baud Rate Counter. The Baud Rate Counter High and Low byte values are not buffered.

**Caution:** *Take precautions if you are reading the values while BRG is counting.*

#### NUMBITS[2:0]—Number of Data Bits Per Character to Transfer

This field contains the number of bits to shift for each character transfer. See the SPI Data Register description for information on valid bit positions when the character length is less than 8-bits.

000 = 8 bits 001 = 1 bit 010 = 2 bits 011 = 3 bits 100 = 4 bits 101 = 5 bits 110 = 6 bits 111 = 7 bits

## SSIO—Slave Select I/O

$0 = \overline{SS}$  pin configured as an input.

$1 = \overline{SS}$  pin configured as an output (MASTER mode only).

#### SSV—Slave Select Value

If SSIO = 1 and SPI configured as a Master:  $0 = \overline{SS}$  pin driven Low (0).

# 126

## **BRH = SPI Baud Rate High Byte**

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

# Table 69. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|

| FIELD |   | BRL |   |    |    |   |   |   |  |  |

| RESET |   | 1   |   |    |    |   |   |   |  |  |

| R/W   |   | R/W |   |    |    |   |   |   |  |  |

| ADDR  |   |     |   | F6 | 7H |   |   |   |  |  |

# **BRL = SPI Baud Rate Low Byte**

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

# ADCD\_L—ADC Data Low Bits

These are the least significant two bits of the 10-bit ADC output. These bits are undefined after a Reset.

## Reserved

These bits are reserved and are always undefined.

# **On-Chip Oscillator**

Z8 Encore! XP<sup>®</sup> F0822 Series products feature an on-chip oscillator for use with external crystals with frequencies from 32 kHz to 20 MHz. In addition, the oscillator can support external RC networks with oscillation frequencies up to 4 MHz or ceramic resonators with oscillation frequencies up to 20 MHz. This oscillator generates the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{IN}$  input pin can also accept a CMOS-level clock input signal (32 kHz–20 MHz). If an external clock generator is used, the  $X_{OUT}$  pin must be left unconnected.

When configured for use with crystal oscillators or external clock drivers, the frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock (that is, no internal clock divider). In RC operation, the system clock is driven by a clock divider (divide by 2) to ensure 50% duty cycle.

# **Operating Modes**

Z8 Encore! XP F0822 Series products support 4 different oscillator modes:

- On-chip oscillator configured for use with external RC networks (<4 MHz).

- Minimum power for use with very low frequency crystals (32 kHz to 1.0 MHz).

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 10.0 MHz).

- Maximum power for use with high frequency crystals or ceramic resonators (8.0 MHz to 20.0 MHz).

The oscillator mode is selected through user-programmable Option Bits. For more information, see Option Bits on page 163.

# **Crystal Oscillator Operation**

Figure 34 on page 168 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 91 on page 168. Resistor R1 is optional and limits total power dissipation by the crystal. The printed circuit board layout must add no more than 4 pF of stray capacitance to either the  $X_{IN}$  or  $X_{OUT}$  pins. If oscillation does not occur, reduce the values of capacitors C1 and C2 to decrease loading.

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

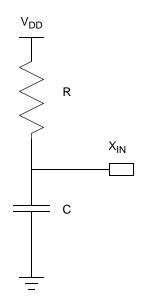

#### Figure 35. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of 45 k $\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the below equation:

Oscillator Frequency (kHz) =  $\frac{1 \times 10^{6}}{(0.4 \times R \times C) + (4 \times C)}$

Figure 36 on page 170 displays the typical (3.3 V and 25  $^{0}$ C) oscillator frequency as a function of the capacitor (*C* in pF) employed in the RC network assuming a 45 k $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board should be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasites, external capacitance values in excess of 20 pF are recommended.

# **AC Characteristics**

Table 98 provides information on the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

# **Table 98. AC Characteristics**

|                     |                                |          | .7 - 3.6 V<br>C to 105 °C |       |                                                                                                          |

|---------------------|--------------------------------|----------|---------------------------|-------|----------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                      | Minimum  | Maximum                   | Units | Conditions                                                                                               |

| F <sub>SYSCLK</sub> | System Clock Frequency (ROM)   | -        | 20.0                      | MHz   |                                                                                                          |

| F <sub>SYSCLK</sub> | System Clock Frequency (Flash) | -        | 20.0                      | MHz   | Read-only from Flash memory.                                                                             |

|                     |                                | 0.032768 | 20.0                      | MHz   | Program or erasure of the<br>Flash memory.                                                               |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency   | 0.032768 | 20.0                      | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an external<br>clock driver. |

| T <sub>XIN</sub>    | System Clock Period            | 50       | _                         | ns    | T <sub>CLK</sub> = 1/F <sub>syscik</sub>                                                                 |

| T <sub>XINH</sub>   | System Clock High Time         | 20       | 30                        | ns    | T <sub>CLK</sub> = 50 ns                                                                                 |

| T <sub>XINL</sub>   | System Clock Low Time          | 20       | 30                        | ns    | T <sub>CLK</sub> = 50 ns                                                                                 |

| Assembly                                 | Symbolic<br>Operation                  | Address<br>Mode |       | _ Opcode(s) | Flags |   |   |   |   |   | Fetch  | Instr. |

|------------------------------------------|----------------------------------------|-----------------|-------|-------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic                                 |                                        | dst             | src   | (Hex)       | С     | Ζ | S | ۷ | D | Н | Cycles | Cycles |

| LDX dst, src                             | dst ← src                              | r               | ER    | 84          | -     | - | - | - | - | - | 3      | 2      |

|                                          |                                        | lr              | ER    | 85          | -     |   |   |   |   |   | 3      | 3      |

|                                          |                                        | R               | IRR   | 86          | -     |   |   |   |   |   | 3      | 4      |

|                                          |                                        | IR              | IRR   | 87          | -     |   |   |   |   |   | 3      | 5      |

|                                          |                                        | r               | X(rr) | 88          | -     |   |   |   |   |   | 3      | 4      |

|                                          |                                        | X(rr)           | r     | 89          | -     |   |   |   |   |   | 3      | 4      |

|                                          |                                        | ER              | r     | 94          | -     |   |   |   |   |   | 3      | 2      |

|                                          |                                        | ER              | lr    | 95          | -     |   |   |   |   |   | 3      | 3      |

|                                          |                                        | IRR             | R     | 96          | -     |   |   |   |   |   | 3      | 4      |

|                                          |                                        | IRR             | IR    | 97          | -     |   |   |   |   |   | 3      | 5      |

|                                          |                                        | ER              | ER    | E8          | -     |   |   |   |   |   | 4      | 2      |

|                                          |                                        | ER              | IM    | E9          | -     |   |   |   |   |   | 4      | 2      |

| LEA dst, X(src) dst $\leftarrow$ src + X |                                        | r               | X(r)  | 98          | -     | - | - | - | - | - | 3      | 3      |

|                                          |                                        | rr              | X(rr) | 99          | -     |   |   |   |   |   | 3      | 5      |

| MULT dst                                 | dst[15:0] ←<br>dst[15:8] *<br>dst[7:0] | RR              |       | F4          | -     | - | - | - | - | - | 2      | 8      |

| NOP                                      | No operation                           |                 |       | 0F          | -     | - | - | - | - | - | 1      | 2      |

| OR dst, src                              | $dst \gets dst \ OR \ src$             | r               | r     | 42          | -     | * | * | 0 | - | - | 2      | 3      |

|                                          |                                        | r               | lr    | 43          | -     |   |   |   |   |   | 2      | 4      |

|                                          |                                        | R               | R     | 44          | -     |   |   |   |   |   | 3      | 3      |

|                                          |                                        | R               | IR    | 45          | -     |   |   |   |   |   | 3      | 4      |

|                                          |                                        | R               | IM    | 46          | -     |   |   |   |   |   | 3      | 3      |

|                                          |                                        | IR              | IM    | 47          | -     |   |   |   |   |   | 3      | 4      |

| ORX dst, src                             | $dst \gets dst \ OR \ src$             | ER              | ER    | 48          | -     | * | * | 0 | - | - | 4      | 3      |

|                                          |                                        | ER              | IM    | 49          | -     |   |   |   |   |   | 4      | 3      |

| POP dst                                  | $dst \gets @SP$                        | R               |       | 50          | -     | - | - | - | - | - | 2      | 2      |

|                                          | $SP \leftarrow SP + 1$                 | IR              |       | 51          | •     |   |   |   |   |   | 2      | 3      |

# Table 126. eZ8 CPU Instruction Summary (Continued)

| Jaquin<br>Quin<br>N<br>trig<br>Z8F04xx with 4 KB Flas | y<br>Flash | RAM    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI | UARTs with IrDA | Description                                    |  |

|-------------------------------------------------------|------------|--------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|------------------------------------------------|--|

| Standard Temperature: 0 °C to 70 °C                   |            |        |           |            |                     |                     |                  |     |                 |                                                |  |

| Z8F0411HH020SC                                        | 4 KB       | 1 KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package                            |  |

| Z8F0411PH020SC                                        | 4 KB       | 1 KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package                            |  |

| Z8F0412SJ020SC                                        | 4 KB       | 1 KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package                            |  |

| Z8F0412PJ020SC                                        | 4 KB       | 1 KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package                            |  |

| Extended Temperature:                                 | 40 °C to   | 105 °C |           |            |                     |                     |                  |     |                 |                                                |  |

| Z8F0411HH020EC                                        | 4 KB       | 1 KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package                            |  |

| Z8F0411PH020EC                                        | 4 KB       | 1 KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package                            |  |

| Z8F0412SJ020EC                                        | 4 KB       | 1 KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package                            |  |

| Z8F0412PJ020EC                                        | 4 KB       | 1 KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package                            |  |

| Z8F08200100KITG                                       |            |        |           |            |                     |                     |                  |     |                 | Development Kit (20- and 28-pin)               |  |

| ZUSBSC00100ZACG                                       |            |        |           |            |                     |                     |                  |     |                 | USB Smart Cable<br>Accessory Kit               |  |

| ZUSBOPTSC01ZACG                                       |            |        |           |            |                     |                     |                  |     |                 | Opto-Isolated USB Smart<br>Cable Accessory Kit |  |

| Note: Replace C with G for lead-free packaging.       |            |        |           |            |                     |                     |                  |     |                 |                                                |  |

239

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

program control instructions 217 program counter 212 program flash configurations 153 program memory 13, 153 PUSH 216 push using extended addressing 216 PUSHX 216 PWM mode 81 PxADDR register 50 PxCTL register 51

# R

R 211 r 211 RCF 215, 216 receive 10-bit data format (I2C) 137 7-bit data transfer format (I2C) 136 IrDA data 111 receive interrupt 128 receiving UART data-interrupt-driven method 94 receiving UART data-polled method 93 register 124, 211 ADC control (ADCCTL) 150 ADC data high byte (ADCDH) 151 ADC data low bits (ADCDL) 151 baud low and high byte (I2C) 143, 145 baud rate high and low byte (SPI) 125 control (SPI) 122 control, I2C 141 data, SPI 121 flash control (FCTL) 159 flash high and low byte (FFREQH and FRE-EQL) 161 flash page select (FPS) 160 flash status (FSTAT) 160 GPIO port A-H address (PxADDR) 50 GPIO port A-H alternate function sub-registers 52 GPIO port A-H control address (PxCTL) 51 GPIO port A-H data direction sub-registers 51 I2C baud rate high (I2CBRH) 143, 144, 145

I2C control (I2CCTL) 141 I2C data (I2CDATA) 139 I2C status 140 I2C status (I2CSTAT) 140 I2Cbaud rate low (I2CBRL) 143 mode, SPI 124 OCD control 181 OCD status 183 SPI baud rate high byte (SPIBRH) 125 SPI baud rate low byte (SPIBRL) 126 SPI control (SPICTL) 122 SPI data (SPIDATA) 121 SPI status (SPISTAT) 123 status, I2C 140 status, SPI 123 UARTx baud rate high byte (UxBRH) 106 UARTx baud rate low byte (UxBRL) 106 UARTx Control 0 (UxCTL0) 103, 106 UARTx control 1 (UxCTL1) 104 UARTx receive data (UxRXD) 101 UARTx status 0 (UxSTAT0) 101 UARTx status 1 (UxSTAT1) 102 UARTx transmit data (UxTXD) 100 watch-dog timer control (WDTCTL) 86 watch-dog timer reload high byte (WDTH) 88 watch-dog timer reload low byte (WDTL) 88 watch-dog timer reload upper byte (WDTU) 87 register address (RA) 211 register file 13 register file address map 15 register pair 211 register pointer 212 reset and stop mode characteristics 39 and stop mode recovery 39 carry flag 215 controller 5 sources 40 **RET 217** return 217 RL 218 **RLC 218** rotate and shift instructions 218 rotate left 218

247

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

250

working register pair 211 WTDU register 87

# Х

X 211 XOR 217 XORX 217

# Z

Z8 Encore! block diagram 3 features 1 introduction 1 part selection guide 2