Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 2x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0821ph020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Figure 5. Z8F0812 and Z8F0412 in 28-Pin SOIC and PDIP Packages

## **Signal Descriptions**

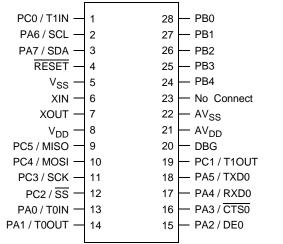

Table 3 describes Z8 Encore! XP<sup>®</sup> F0822 Series signals. See Pin Configurations on page 7 to determine the signals available for the specific package styles

| Signal<br>Mnemonic            | I/O | Description                                                                                                                                                                                                                                                                   |  |  |  |  |

|-------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| General-Purpose I/O Ports A-H |     |                                                                                                                                                                                                                                                                               |  |  |  |  |

| PA[7:0]                       | I/O | <b>Port C</b> —These pins are used for general-purpose I/O and supports 5 V-tolerant inputs.                                                                                                                                                                                  |  |  |  |  |

| PB[4:0]                       | I/O | Port B—These pins are used for general-purpose I/O.                                                                                                                                                                                                                           |  |  |  |  |

| PC[5:0]                       | I/O | <b>Port C</b> —These pins are used for general-purpose I/O and support 5 V-tolerant inputs.                                                                                                                                                                                   |  |  |  |  |

| I <sup>2</sup> C Controller   |     |                                                                                                                                                                                                                                                                               |  |  |  |  |

| SCL                           | I/O | <b>Serial Clock</b> —This open-drain pin clocks data transfers in accordance with the I <sup>2</sup> C standard protocol. This pin is multiplexed with a GPIO pin. When the GPIO pin is configured for alternate function to enable the SCL function, this pin is open-drain. |  |  |  |  |

| SDA                           | I/O | <b>Serial Data</b> —This open-drain pin transfers data between the $I^2C$ and a slave.<br>This pin is multiplexed with a GPIO pin. When the GPIO pin is configured for<br>alternate function to enable the SDA function, this pin is<br>open-drain.                           |  |  |  |  |

#### **Table 3. Signal Descriptions**

9

| Signal<br>Mnemonic | ; I/O    | Description                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|--------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Oscillators        | S        |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| XIN                | I        | <b>External Crystal Input</b> —This is the input pin to the crystal oscillator. A crystal is connected between the external crystal input and the XOUT pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock to the system.                                      |  |  |  |  |

| XOUT O             |          | <b>External Crystal Output</b> —This pin is the output of the crystal oscillator. A crystal is connected between external crystal output and the XIN pin to form the oscillator. When the system clock is referred in this manual, it refers to the frequency of the signal at this pin. This pin must be left unconnected when not using a crystal. |  |  |  |  |

| On-Chip D          | ebugger  |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| DBG                | I/O      | <b>Debug</b> —This pin is the control and data input and output to and from the OCD. This pin is open-drain.                                                                                                                                                                                                                                         |  |  |  |  |

| !                  | Caution: | For operation of the OCD, all power pins $(V_{DD} \text{ and } AV_{DD})$ must be supplied<br>with power and all ground pins $(V_{SS} \text{ and } AV_{SS})$ must be properly grounded.<br>The DBG pin is open-drain and must have an external pull-up resistor to ensure<br>proper operation.                                                        |  |  |  |  |

| Reset              |          |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RESET              | I        | RESET—Generates a Reset when asserted (driven Low).                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Power Sup          | oply     |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| V <sub>DD</sub>    | I        | Digital Power Supply.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| $AV_{DD}$          | Ι        | <b>Analog Power Supply</b> —Must be powered up and grounded to VDD, even if not using analog features.                                                                                                                                                                                                                                               |  |  |  |  |

| V <sub>SS</sub>    | I        | Digital Ground.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| AV <sub>SS</sub>   | Ι        | Analog Ground—Must be grounded and connected to VSS, even if not using analog features.                                                                                                                                                                                                                                                              |  |  |  |  |

## Table 3. Signal Descriptions (Continued)

24

34

Port C Address PCADDR (FD8H - Read/Write) Port C Address[7:0] Selects Port Sub-Registers: 00H = No function 01H = Data direction 02H = Alternate function 03H = Output control (opendrain) 04H = High drive enable 05H = STOP mode recovery enable 06H = Pull-up enable 07H-FFH = No function

Port C Control PCCTL (FD9H - Read/Write) D7D6D5D4D3D2D1D0

|  | Port C Control [5:0]<br>Provides Access to Port<br>Sub-Registers |

|--|------------------------------------------------------------------|

|  | -Reserved                                                        |

Port C Input Data

PCIN (FDAH - Read Only) D7D6D5D4D3D2D1D0

Port C Input Data [5:0]

-----Reserved

Port C Output Data PCOUT (FDBH - Read/Write) D7/D6/D5/D4/D3/D2/D1/D0

Port C Output Data [5:0]

#### **External Pin Reset**

The RESET pin contains a Schmitt-triggered input, an internal pull-up, an analog filter, and a digital filter to reject noise. After the RESET pin is asserted for at least 4 system clock cycles, the device progresses through the System Reset sequence. While the RESET input pin is asserted Low, Z8 Encore! XP F0822 Series device continues to be held in the Reset state. If the RESET pin is held Low beyond the System Reset time-out, the device exits the Reset state immediately following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the Watchdog Timer Control Register (WDTCTL) is set to 1.

#### **On-Chip Debugger Initiated Reset**

A POR is initiated using the OCD by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the WDT Control Register is set.

## **Stop Mode Recovery**

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. For detailed information on STOP mode, see Low-Power Modes on page 45. During Stop Mode Recovery, the device is held in reset for 66 cycles of the WDT oscillator followed by 16 cycles of the system clock. Stop Mode Recovery only affects the contents of the WDT Control Register and does not affect any other values in the Register File, including the Stack Pointer, Register Pointer, Flags, Peripheral Control Registers, and General-Purpose RAM.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the STOP bit in the WDT Control Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information on each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                      | Action                                                               |

|----------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode      | WDT time-out when configured for Reset                                         | Stop Mode Recovery                                                   |

|                | WDT time-out when configured for interrupt                                     | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

| Table 10. Stop Mode Recovery Sources and Resulting Action | Table 10. Sto |

|-----------------------------------------------------------|---------------|

|-----------------------------------------------------------|---------------|

| Port   | Pin | Mnemonic | Alternate Function Description |  |  |  |

|--------|-----|----------|--------------------------------|--|--|--|

| Port C | PC0 | T1IN     | Timer 1 Input                  |  |  |  |

|        | PC1 | T1OUT    | Timer 1 Output                 |  |  |  |

| PC2 SS |     | SS       | SPI Slave Select               |  |  |  |

|        | PC3 | SCK      | SPI Serial Clock               |  |  |  |

|        | PC4 | MOSI     | SPI Master Out Slave In        |  |  |  |

|        | PC5 | MISO     | SPI Master In Slave Out        |  |  |  |

|        |     |          |                                |  |  |  |

Table 12. Port Alternate Function Mapping (Continued)

## **GPIO Interrupts**

Many of GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupts generate an interrupt when any edge occurs (both rising and falling). For more details on interrupts using the GPIO pins, see GPIO Port Pin Block Diagram on page 48.

## **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data, and output data. Table 13 lists the GPIO Port Registers and Sub-Registers. Use the Port A–C Address and Control Registers together to provide access to sub-registers for Port configuration and control.

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| P <i>x</i> ADDR            | Port A–C Address Register<br>(selects sub-registers)            |

| P <i>x</i> CTL             | Port A–C Control Register<br>(provides access to sub-registers) |

| PxIN                       | Port A–C Input Data Register                                    |

| P <i>x</i> OUT             | Port A–C Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

| P <i>x</i> DD              | Data Direction                                                  |

| P <i>x</i> AF              | Alternate Function                                              |

|                            |                                                                 |

Table 13. GPIO Port Registers and Sub-Registers

## Port A–C Output Data Register

The Port A–C Output Data Register (Table 23) controls the output data to the pins.

#### Table 23. Port A–C Output Data Register (PxOUT)

| BITS  | 7     | 6                                               | 5 | 4        | 3        | 2 | 1 | 0 |  |

|-------|-------|-------------------------------------------------|---|----------|----------|---|---|---|--|

| FIELD | POUT7 | POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT0 |   |          |          |   |   |   |  |

| RESET | 0     |                                                 |   |          |          |   |   |   |  |

| R/W   | R/W   |                                                 |   |          |          |   |   |   |  |

| ADDR  |       |                                                 |   | FD3H, FD | 7H, FDBH |   |   |   |  |

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

#### TH and TL—Timer High and Low Bytes

These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value.

## Timer Reload High and Low Byte Registers

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) Registers (Table 41) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte Register occurs, the temporary holding register value is written to the Timer High Byte Register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In COMPARE mode, the Timer Reload High and Low Byte Registers store the 16-bit Compare value.

#### Table 41. Timer 0–1 Reload High Byte Register (TxRH)

| BITS  | 7   | 6 | 5 | 4     | 3    | 2 | 1 | 0 |

|-------|-----|---|---|-------|------|---|---|---|

| FIELD | TRH |   |   |       |      |   |   |   |

| RESET | 1   |   |   |       |      |   |   |   |

| R/W   | R/W |   |   |       |      |   |   |   |

| ADDR  |     |   |   | F02H, | F0AH |   |   |   |

#### Table 42. Timer 0–1 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|------------|---|---|---|---|---|---|--|

| FIELD | TRL |            |   |   |   |   |   |   |  |

| RESET | 1   |            |   |   |   |   |   |   |  |

| R/W   | R/W |            |   |   |   |   |   |   |  |

| ADDR  |     | F03H, F0BH |   |   |   |   |   |   |  |

#### TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE mode, these two bytes form the 16-bit Compare value.

#### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 43 and Table 44) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

## Universal Asynchronous Receiver/Transmitter

The Universal Asynchronous Receiver/Transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit Baud Rate Generator

- Selectable Multiprocessor (9-bit) mode with three configurable interrupt schemes

- BRG timer mode

- Driver Enable output for external bus transceivers

### Architecture

The UART consists of three primary functional blocks: Transmitter, Receiver, and Baud Rate Generator. The UART's transmitter and receiver functions independently, but use the same baud rate and data format. Figure 11 on page 90 displays the UART architecture.

of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal. This procedure allows the Endec to tolerate jitter and baud rate errors in the incoming data stream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## **Infrared Endec Control Register Definitions**

All Infrared Endec configuration and status information is set by the UART control registers as defined in UART Control Register Definitions on page 100.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Endec before enabling the GPIO Port alternate function for the corresponding pin.

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

#### **SPI Signals**

The four basic SPI signals are:

- MISO (Master-In, Slave-Out)

- MOSI (Master-Out, Slave-In)

- SCK (Serial Clock)

- <u>SS</u> (Slave Select)

The following sections discuss these SPI signals. Each signal is described in both Master and Slave modes.

#### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

115

## 121

## **SPI Control Register Definitions**

### **SPI Data Register**

The SPI Data Register stores both the outgoing (transmit) data and the incoming (receive) data. Reads from the SPI Data Register always return the current contents of the 8-bit Shift Register. Data is shifted out starting with bit 7. The last bit received resides in bit position 0.

With the SPI configured as a Master, writing a data byte to this register initiates the data transmission. With the SPI configured as a Slave, writing a data byte to this register loads the shift register in preparation for the next data transfer with the external Master. In either the Master or Slave modes, if a transmission is already in progress, writes to this register are ignored and the Overrun error Flag, OVR, is set in the SPI Status Register.

When the character length is less than 8 bits (as set by the NUMBITS field in the SPI Mode Register), the transmit character must be left justified in the SPI Data Register. A received character of less than 8 bits is right justified (last bit received is in bit position 0). For example, if the SPI is configured for 4-bit characters, the transmit characters must be written to SPIDATA[7:4] and the received characters are read from SPIDATA[3:0].

| BITS  | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|---|---|----|----|---|---|---|

| FIELD |   |   |   | DA | TA |   |   |   |

| RESET |   |   |   | )  | <  |   |   |   |

| R/W   |   |   |   | R/ | W  |   |   |   |

| ADDR  |   |   |   | F6 | 0H |   |   |   |

#### **DATA—Data** Transmit and/or receive data.

## 126

#### **BRH = SPI Baud Rate High Byte**

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

### Table 69. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|---|---|----|----|---|---|---|

| FIELD |   |   |   | BF | RL |   |   |   |

| RESET |   |   |   |    | 1  |   |   |   |

| R/W   |   |   |   | R/ | W  |   |   |   |

| ADDR  |   |   |   | F6 | 7H |   |   |   |

### **BRL = SPI Baud Rate Low Byte**

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

- 5. Re-write the page written in step 2 to the Page Select Register.

- 6. Write Flash Memory using LDC or LDCI instructions to program the Flash.

- 7. Repeat step 6 to program additional memory locations on the same page.

- 8. Write 00H to the Flash Control Register to lock the Flash Controller.

#### Page Erase

Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Page Select Register identifies the page to be erased. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. Interrupts that occur when the Page Erase operation is in progress are serviced once the Page Erase operation is complete. When the Page Erase operation is complete, the Flash Controller returns to its locked state. Only pages located in unprotected sectors can be erased.

Follow the steps below to perform a Page Erase operation:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page to be erased to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

- 4. Write the second unlock command 8CH to the Flash Control Register.

- 5. Re-write the page written in step 2 to the Page Select Register.

- 6. Write the Page Erase command 95H to the Flash Control Register.

#### **Mass Erase**

The Flash memory cannot be Mass Erased by user code.

#### Flash Controller Bypass

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Programming algorithms by controlling the Flash programming signals directly.

Flash Controller Bypass is recommended for gang programming applications and large volume customers who do not require in-circuit programming of the Flash memory.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore! XP, available for download at <u>www.zilog.com</u>.

## **Option Bits**

Option Bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F0822 Series operation. The feature configuration data is stored in Flash Memory and read during Reset. Features available for control through the Option Bits are:

- Watchdog Timer time-out response selection-interrupt or Reset.

- Watchdog Timer enabled at Reset.

- The ability to prevent unwanted read access to user code in Flash Memory.

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Flash Memory.

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption.

- Oscillator mode selection-for high, medium, and low power crystal oscillators, or external RC oscillator.

## Operation

#### **Option Bit Configuration By Reset**

During any reset operation (System Reset, Reset, or Stop Mode Recovery), the Option Bits are automatically read from the Flash Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F0822 Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access. Each time the Option Bits are programmed or erased, the device must be Reset for the change to take place (Flash version only)

## **Option Bit Address Space**

The first two bytes of Flash Memory at addresses 0000H (Table 89 on page 164) and 0001H (Table 90 on page 165) are reserved for the user programmable Option Bits. The byte at Program Memory address 0000H configures user options. The byte at Flash Memory address 0001H is reserved for future use and must be left in its unprogrammed state.

# **On-Chip Debugger**

Z8 Encore! XP<sup>®</sup> F0822 Series products have an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Reading and writing of the Register File

- Reading and (Flash version only) writing of Program and Data Memory

- Setting of Breakpoints

- Executing eZ8 CPU instructions

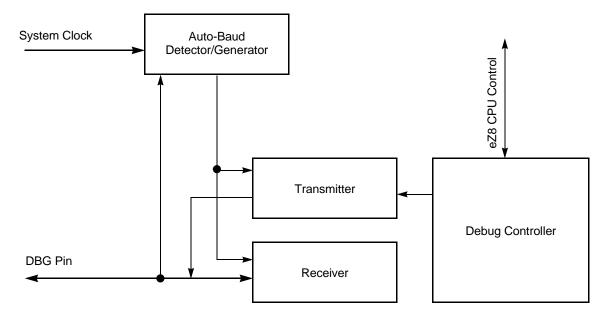

## Architecture

The OCD consists of four primary functional blocks: transmitter, receiver, autobaud generator, and debug controller. Figure 37 displays the architecture of the OCD.

Figure 37. On-Chip Debugger Block Diagram

## Operation

#### **OCD** Interface

The OCD uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional open-drain interface that transmits and receives data. Data

### **OCDCNTR Register**

The OCD contains a multipurpose 16-bit Counter Register. It can be used for the following:

- Count system clock cycles between Breakpoints.

- Generate a BRK when it counts down to zero.

- Generate a BRK when its value matches the Program Counter.

When configured as a counter, the OCDCNTR register starts counting when the OCD leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH. The OCDCNTR register automatically resets itself to 0000H when the OCD exits DEBUG mode if it is configured to count clock cycles between breakpoints.

**Caution:** The OCDCNTR register is used by many of the OCD commands. It counts the number of bytes for the register and memory read/write commands. It holds the residual value when generating the CRC. Therefore, if the OCD-CNTR is being used to generate a BRK, its value should be written as a last step before leaving DEBUG mode.

Since this register is overwritten by various OCD commands, it should only be used to generate temporary breakpoints, such as stepping over CALL instructions or running to a specific instruction and stopping.

## **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Read Protect Option Bit (RP). The Read Protect Option Bit prevents the code in memory from being read out of the Z8 Encore! XP F0822 Series products. When this option is enabled, several of the OCD commands are disabled. Table 93 on page 177 contains a summary of the OCD commands. Each OCD command is described further in the bulleted list. It also lists the commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit. A "reset and stop" function can be achieved by writing 81H to this register. A "reset and go" function can be achieved by writing 41H to this register. If the device is in DEBUG mode, a "run" function can be implemented by writing 40H to this register.

Table 94. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4       | 3     | 2      | 1        | 0   |

|-------|---------|-------|--------|---------|-------|--------|----------|-----|

| FIELD | DBGMODE | BRKEN | DBGACK | BRKLOOP | BRKPC | BRKZRO | Reserved | RST |

| RESET |         | 0     |        |         |       |        |          |     |

| R/W   | R/W R R |       |        |         |       | R/W    |          |     |

#### **DBGMODE—Debug Mode**

Setting this bit to 1 causes the device to enter DEBUG mode. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to start running again. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device, it cannot be written to 0.

0 = The Z8 Encore! XP F0822 Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F0822 Series device is in DEBUG mode.

#### **BRKEN**—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves like an NOP instruction. If this bit is set to 1 and a BRK instruction is decoded, the OCD takes action dependent upon the BRK-LOOP bit.

0 = BRK instruction is disabled.

1 = BRK instruction is enabled.

#### DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, then the OCD sends an Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled.

1 = Debug Acknowledge is enabled.

#### **BRKLOOP**—Breakpoint Loop

This bit determines what action the OCD takes when a BRK instruction is decoded if breakpoints are enabled (BRKEN is 1). If this bit is 0, then the DBGMODE bit is automatically set to 1 and the OCD enter DEBUG mode. If BRKLOOP is set to 1, then the eZ8 CPU loops on the BRK instruction.

0 = BRK instruction sets DBGMODE to 1.

1 = eZ8 CPU loops on BRK instruction.

#### **BRKPC—Break when PC == OCDCNTR**

If this bit is set to 1, then the OCDCNTR register is used as a hardware breakpoint. When the program counter matches the value in the OCDCNTR register, DBGMODE is

# **Electrical Characteristics**

## **Absolute Maximum Ratings**

These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect device reliability. For improved reliability, unused inputs must be tied to one of the supply voltages  $(V_{DD} \text{ or } V_{SS})$ .

| Parameter                                                       | Minimum     | Maximum | Units | Notes |

|-----------------------------------------------------------------|-------------|---------|-------|-------|

| Ambient temperature under bias                                  | -40         | +105    | °C    | 1     |

| Storage temperature                                             | -65         | +150    | °C    |       |

| Voltage on any pin with respect to $V_{SS}$                     | -0.3        | +5.5    | V     | 2     |

| Voltage on AV <sub>SS</sub> pin with respect to V <sub>SS</sub> | -0.3        | +0.3    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$                | -0.3        | +3.6    | V     |       |

| Voltage on $AV_{DD}$ pin with respect to $V_{DD}$               | -0.3        | +0.3    | V     |       |

| Maximum current on input and/or inactive output pin             | -5          | +5      | μA    |       |

| Maximum output current from active output pin                   | -25         | +25     | mA    |       |

| 20-pin SSOP Package Maximum Ratings at -40 °                    | C to 70 °C  |         |       |       |

| Total power dissipation                                         |             | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |             | 120     | mA    |       |

| 20-pin SSOP Package Maximum Ratings at 70 °C                    | c to 105 °C |         |       |       |

| Total power dissipation                                         |             | 250     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                |             | 69      | mA    |       |

| 20-pin PDIP Package Maximum Ratings at -40 °C                   | to 70 °C    |         |       |       |

| Total power dissipation                                         |             | 775     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |             | 215     | mA    |       |

#### Table 96. Absolute Maximum Ratings

<sup>1 0</sup>

**Caution:** *Stresses greater than those listed in* Table 96 *can cause permanent damage to the device.*

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

250

working register pair 211 WTDU register 87

## Х

X 211 XOR 217 XORX 217

## Z

Z8 Encore! block diagram 3 features 1 introduction 1 part selection guide 2