# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                         |

| Number of I/O              | 19                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 5x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0822sj020ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Introduction                       |

|------------------------------------|

| About This Manual                  |

| Intended Audience                  |

| Manual Conventionsx                |

| Safeguards                         |

| Abbreviations/Acronymsxii          |

| Introduction                       |

| Features                           |

| Part Selection Guide               |

| Block Diagram                      |

| CPU and Peripheral Overview        |

| eZ8 CPU Features                   |

| General Purpose Input/Output 4     |

| Flash Controller                   |

| 10-Bit Analog-to-Digital Converter |

| UART                               |

| I <sup>2</sup> C                   |

| Serial Peripheral Interface        |

| Timers                             |

| Interrupt Controller               |

| Reset Controller                   |

| On-Chip Debugger                   |

| Signal and Pin Descriptions        |

| Available Packages                 |

| Pin Configurations                 |

| Signal Descriptions                |

| Pin Characteristics                |

| Address Space                      |

| Register File                      |

| Program Memory                     |

| Data Memory                        |

| Information Area                   |

| Register File Address Map 15       |

| Control Register Summary           |

| Reset and Stop Mode Recovery       |

| Reset Types                        |

| System Reset                       |

### **Use of All Uppercase Letters**

The use of all uppercase letters designates the names of states, modes, and commands.

- **Example 1:** The bus is considered BUSY after the Start condition.

- **Example 2:** A START command triggers the processing of the initialization sequence.

- **Example 3:** STOP mode.

### **Bit Numbering**

Bits are numbered from 0 to n-1 where n indicates the total number of bits. For example, the 8 bits of a register are numbered from 0 to 7.

### Safeguards

It is important that you understand the following safety terms, which are defined here.

**Caution:** *Indicates a procedure or file can become corrupted if you does not follow directions.*

### Abbreviations/Acronyms

This document uses the following abbreviations or acronyms.

| Abbreviations/<br>Acronyms | Expansion                                   |

|----------------------------|---------------------------------------------|

| ADC                        | Analog-to-Digital Converter                 |

| LPO                        | Low-Power Operational Amplifier             |

| SPI                        | Serial Peripheral Interface                 |

| WDT                        | Watchdog Timer                              |

| GPIO                       | General-Purpose Input/Output                |

| OCD                        | On-Chip Debugger                            |

| POR                        | Power-On Reset                              |

| LVD                        | Low-Voltage Detection                       |

| VBO                        | Voltage Brownout                            |

| ISR                        | Interrupt Service Routine                   |

| UART                       | Universal Asynchronous Receiver/Transmitter |

| IrDA                       | Infrared Data Association                   |

| l <sup>2</sup> C           | Inter-Integrated Circuit                    |

## Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

xiii

| Abbreviations/<br>Acronyms | Expansion                        |

|----------------------------|----------------------------------|

| PDIP                       | Plastic Dual Inline Package      |

| SOIC                       | Small Outline Integrated Circuit |

| SSOP                       | Small Shrink Outline Package     |

| PC                         | Program Counter                  |

| IRQ                        | Interrupt Request                |

|                            |                                  |

| Address<br>(Hex) | Register Description    | Mnemonic | Reset (Hex) | Page No             |

|------------------|-------------------------|----------|-------------|---------------------|

| FFC              | Flags                   | —        | XX          | Refer to eZ8        |

| FFD              | Register Pointer        | RP       | XX          | CPU User            |

| FFE              | Stack Pointer High Byte | SPH      | XX          | <sup>–</sup> Manual |

| FFF              | Stack Pointer Low Byte  | SPL      | XX          | _                   |

| XX=Undefine      | b                       |          |             |                     |

### Table 7. Register File Address Map (Continued)

| IRQ1ENL[x] | Priority                       | Description               |

|------------|--------------------------------|---------------------------|

| 0          | Disabled                       | Disabled                  |

| 1          | Level 1                        | Low                       |

| 0          | Level 2                        | Nominal                   |

| 1          | Level 3                        | High                      |

|            | IRQ1ENL[x]<br>0<br>1<br>0<br>1 | 0Disabled1Level 10Level 2 |

Table 31. IRQ1 Enable and Priority Encoding

where *x* indicates the register bits from 0 through 7.

### Table 32. IRQ1 Enable High Bit Register (IRQ1ENH)

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | PA7ENH | PA6ENH | PA5ENH | PA4ENH | PA3ENH | PA2ENH | PA1ENH | PA0ENH |  |  |

| RESET |        | 0      |        |        |        |        |        |        |  |  |

| R/W   |        | R/W    |        |        |        |        |        |        |  |  |

| ADDR  |        |        |        | FC     | 4H     |        |        |        |  |  |

**PAxENH**—Port A Bit[*x*] Interrupt Request Enable High Bit

### Table 33. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | PA7ENL | PA6ENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |

| RESET |        | 0      |        |        |        |        |        |        |  |  |

| R/W   |        | R/W    |        |        |        |        |        |        |  |  |

| ADDR  |        |        |        | FC     | 5H     |        |        |        |  |  |

**PAxENL**—Port A Bit[*x*] Interrupt Request Enable Low Bit

### **IRQ2 Enable High and Low Bit Registers**

Table 34 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit Registers (Table 35 and Table 36) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register.

- 4. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

#### **PWM Mode**

In PWM mode, the timer outputs a Pulse-Width Modulator output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte Registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte Registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and then transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and then transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte Registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- Configure the timer for CAPTURE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte Registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte Registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte Registers to 0000H. This allows user software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte Registers still contains 0000H after the interrupt, then the interrupt was generated by a Reload.

- 5. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event is calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value)xPrescale}{System Clock Frequency (Hz)}$

### **COMPARE Mode**

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte Registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

Follow the steps below for configuring a timer for COMPARE mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE mode

- Set the prescale value

- Set the initial logic level (High or Low) for the Timer Output alternate function, if required

- 2. Write to the Timer High and Low Byte registers to set the starting count value

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value

## Watchdog Timer

Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place the Z8 Encore! XP<sup>®</sup> F0822 Series device into unsuitable operating states. It includes the following features:

- On-chip RC oscillator.

- A selectable time-out response—Reset or Interrupt.

- 24-bit programmable time-out value.

### Operation

WDT is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! XP F0822 Series device when the WDT reaches its terminal count. It uses its own dedicated on-chip RC oscillator as its clock source. The WDT has only two modes of operation—ON and OFF. When enabled, it always counts and must be refreshed to prevent a time-out. An enable is performed by executing the WDT instruction or by setting the WDT\_AO Option Bit. The WDT\_AO bit enables the WDT to operate all the time, even if a WDT instruction has not been executed.

The WDT is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is given by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. WDT cannot be refreshed once it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 47 provides information on approximate time-out delays for minimum and maximum WDT reload values.

| WDT Reload<br>Value | WDT Reload<br>Value | Approximate Time-Out Delay<br>(with 10 kHz typical WDT Oscillator Frequency) |                        |  |  |  |

|---------------------|---------------------|------------------------------------------------------------------------------|------------------------|--|--|--|

| (Hex)               | (Decimal)           | Typical Description                                                          |                        |  |  |  |

| 000004              | 4                   | 400 μs                                                                       | Minimum time-out delay |  |  |  |

| FFFFF               | 16,777,215          | 1677.5 s                                                                     | Maximum time-out delay |  |  |  |

### Table 50. Watchdog Timer Reload High Byte Register (WDTH)

| BITS     | 7                                                                                   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------|-------------------------------------------------------------------------------------|---|---|---|---|---|---|---|--|

| FIELD    | WDTH                                                                                |   |   |   |   |   |   |   |  |

| RESET    |                                                                                     |   |   |   |   |   |   |   |  |

| R/W      | R/W*                                                                                |   |   |   |   |   |   |   |  |

| ADDR     | FF2H                                                                                |   |   |   |   |   |   |   |  |

| R/W*-Rea | R/W*–Read returns the current WDT count value. Write sets the desired Reload Value. |   |   |   |   |   |   |   |  |

### WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

### Table 51. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS     | 7                                                                                   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------|-------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|

| FIELD    | WDTL                                                                                |      |   |   |   |   |   |   |  |

| RESET    |                                                                                     | 1    |   |   |   |   |   |   |  |

| R/W      |                                                                                     | R/W* |   |   |   |   |   |   |  |

| ADDR     | FF3H                                                                                |      |   |   |   |   |   |   |  |

| R/W*-Rea | R/W*–Read returns the current WDT count value. Write sets the desired Reload Value. |      |   |   |   |   |   |   |  |

### WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

- A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independent of the other receiver interrupt sources. The received data interrupt occurs once the receive character is received and placed in the Receive Data Register. Software must respond to this received data available condition before the next character is completely received to avoid an overrun error. In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte

- A break is received

- An overrun is detected

- A data framing error is detected

### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The break detect and overrun status bits are not displayed until the valid data is read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte cannot contain valid data and should be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data Register must be read again to clear the error bits is the UART Status 0 Register. Updates to the Receive Data Register occur only when the next data word is received.

### **UART Data and Error Handling Procedure**

Figure16 on page 99 displays the recommended procedure for UART receiver ISRs.

### **Baud Rate Generator Interrupts**

If the BRG interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This action allows the BRG to function as an additional counter if the UART functionality is not employed.

## **Infrared Encoder/Decoder**

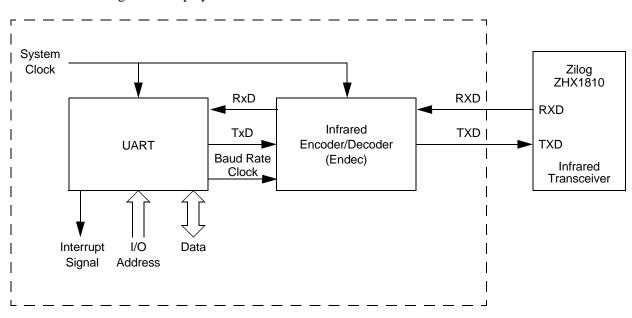

Z8 Encore! XP<sup>®</sup> F0822 Series products contain a fully-functional, high-performance UART to Infrared Encoder/Decoder (Endec). The Infrared Endec is integrated with an onchip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, v1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

### Architecture

Figure 17 displays the architecture of the Infrared Endec.

### Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the Infrared Endec through the RXD pin, decoded by the Infrared Endec, and then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 Kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation.

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

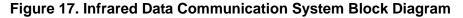

### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 18 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP<sup>®</sup> F0822 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 18. Infrared Data Transmission

of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal. This procedure allows the Endec to tolerate jitter and baud rate errors in the incoming data stream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## **Infrared Endec Control Register Definitions**

All Infrared Endec configuration and status information is set by the UART control registers as defined in UART Control Register Definitions on page 100.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Endec before enabling the GPIO Port alternate function for the corresponding pin.

When reading data from the slave, the  $I^2C$  pauses after the data Acknowledge cycle until the receive interrupt is serviced and the RDRF bit of the status register is cleared by reading the  $I^2C$  Data Register. Once the  $I^2C$  Data Register has been read, the  $I^2C$  reads the next data byte.

### Address Only Transaction with a 7-bit Address

In the situation where software determines if a slave with a 7-bit address is responding without sending or receiving data, a transaction can be done which only consists of an address phase. Figure 26 on page 131 displays this "address only" transaction to determine if a slave with a 7-bit address will acknowledge. As an example, this transaction can be used after a "write" has been done to a EEPROM to determine when the EEPROM completes its internal write operation and is once again responding to I<sup>2</sup>C transactions. If the slave does not Acknowledge, the transaction is repeated until the slave does Acknowledge.

Figure 26. 7-Bit Address Only Transaction Format

Follow the steps below for an address only transaction to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control Register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable Transmit interrupts.

- 3. The I<sup>2</sup>C interrupt asserts, because the I<sup>2</sup>C Data Register is empty (TDRE = 1)

- 4. Software responds to the TDRE bit by writing a 7-bit Slave address plus write bit (=0) to the I<sup>2</sup>C Data Register. As an alternative this could be a read operation instead of a write operation.

- 5. Software sets the START and STOP bits of the I<sup>2</sup>C Control Register and clears the TXI bit.

- 6. The  $I^2C$  Controller sends the START condition to the  $I^2C$  Slave.

- 7. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data Register.

- 8. Software polls the STOP bit of the I<sup>2</sup>C Control Register. Hardware deasserts the STOP bit when the address only transaction is completed.

- 9. Software checks the ACK bit of the I<sup>2</sup>C Status Register. If the slave acknowledged, the ACK bit is equal to 1. If the slave does not acknowledge, the ACK bit is equal to 0. The NCKI interrupt does not occur in the not acknowledge case because the STOP bit was set.

## **Flash Memory**

The products in Z8 Encore! XP<sup>®</sup> F0822 Series feature either 8 KB (8192) or 4 KB (4096) bytes of Flash memory with Read/Write/Erase capability. The Flash memory is programmed and erased in-circuit by either user code or through the OCD.

The Flash memory array is arranged in 512-byte per page. The 512-byte page is the minimum Flash block size that can be erased. The Flash memory is divided into eight sectors which is protected from programming and erase operations on a per sector basis.

Table 80 describes the Flash memory configuration for each device in the Z8F082x family. Table 81 lists the sector address ranges. Figure 33 on page 154 displays the Flash memory arrangement.

| Part Number | Flash Size  | Number<br>of Pages | Flash Memory<br>Addresses | Sector Size  | Number of<br>Sectors | Pages<br>per<br>Sector |

|-------------|-------------|--------------------|---------------------------|--------------|----------------------|------------------------|

| Z8F08xx     | 8 KB (8192) | 16                 | 0000H - 1FFFH             | 1 KB (1024)  | 8                    | 2                      |

| Z8F04xx     | 4 KB (4096) | 8                  | 0000H - 0FFFH             | 0.5 KB (512) | 8                    | 1                      |

### **Table 80. Flash Memory Configurations**

### Table 81. Flash Memory Sector Addresses

|               | Flash Sector Address Ranges |             |  |  |  |

|---------------|-----------------------------|-------------|--|--|--|

| Sector Number | Z8F04xx                     | Z8F08xx     |  |  |  |

| 0             | 0000H-01FFH                 | 0000H-03FFH |  |  |  |

| 1             | 0200H-03FFH                 | 0400H-07FFH |  |  |  |

| 2             | 0400H-05FFH                 | 0800H-0BFFH |  |  |  |

| 3             | 0600H-07FFH                 | 0C00H-0FFFH |  |  |  |

| 4             | 0800H-09FFH                 | 1000H-13FFH |  |  |  |

| 5             | 0A00H-0BFFH                 | 1400H-17FFH |  |  |  |

| 6             | 0C00H-0DFFH                 | 1800H-1BFFH |  |  |  |

| 7             | 0E00H-0FFFH                 | 1C00H-1FFFH |  |  |  |

## Table 93. On-Chip Debugger Commands

| Debug Command                 | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                                            |

|-------------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision             | 00H             | Yes                                   | -                                                                                                                                                                                                 |

| Write OCD Counter<br>Register | 01H             | -                                     | -                                                                                                                                                                                                 |

| Read OCD Status<br>Register   | 02H             | Yes                                   | -                                                                                                                                                                                                 |

| Read OCD Counter<br>Register  | 03H             | -                                     | -                                                                                                                                                                                                 |

| Write OCD Control<br>Register | 04H             | Yes                                   | Cannot clear DBGMODE bit                                                                                                                                                                          |

| Read OCD Control<br>Register  | 05H             | Yes                                   | -                                                                                                                                                                                                 |

| Write Program Counter         | 06H             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Counter          | 07H             | -                                     | Disabled                                                                                                                                                                                          |

| Write Register                | 08H             | -                                     | Only writes of the peripheral control<br>registers at address F00H-FFH are<br>allowed.<br>Additionally, only the Mass Erase<br>command is allowed to be written to the<br>Flash Control Register. |

| Read Register                 | 09H             | -                                     | Only reads of the peripheral control registers at address F00H-FFH are allowed.                                                                                                                   |

| Write Program Memory          | 0AH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Memory           | 0BH             | -                                     | Disabled                                                                                                                                                                                          |

| Write Data Memory             | 0CH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Data Memory              | 0DH             | -                                     | Disabled                                                                                                                                                                                          |

| Read Program Memory<br>CRC    | 0EH             | -                                     | -                                                                                                                                                                                                 |

| Reserved                      | 0FH             | -                                     | -                                                                                                                                                                                                 |

| Step Instruction              | 10H             | -                                     | Disabled                                                                                                                                                                                          |

| Stuff Instruction             | 11H             | -                                     | Disabled                                                                                                                                                                                          |

177

automatically set to 1. If this bit is set, the OCDCNTR register does not count when the CPU is running.

0 = OCDCNTR is setup as counter

1 = OCDCNTR generates hardware break when PC == OCDCNTR

### BRKZRO—Break when OCDCNTR == 0000H

If this bit is set, then the OCD automatically sets the DBGMODE bit when the OCD-CNTR register counts down to 0000H. If this bit is set, the OCDCNTR register is not reset when the part leaves DEBUG Mode.

0 = OCD does not generate BRK when OCDCNTR decrements to 0000H 1 = OCD sets DBGMODE to 1 when OCDCNTR decrements to 0000H

#### Reserved

These bits are reserved and must be 0.

#### **RST**—Reset

Setting this bit to 1 resets the Z8 Encore! XP<sup>®</sup> F0822 Series device. The device goes through a normal POR sequence with the exception that the OCD is not reset. This bit is automatically cleared to 0 when the reset finishes.

0 = No effect.

1 = Reset the Z8 Encore! XP F0822 Series device.

### **OCD Status Register**

The OCD Status register reports status information about the current state of the debugger and the system.

| BITS  | 7    | 6    | 5    | 4        | 3 | 2 | 1 | 0 |

|-------|------|------|------|----------|---|---|---|---|

| FIELD | IDLE | HALT | RPEN | Reserved |   |   |   |   |

| RESET | 0    |      |      |          |   |   |   |   |

| R/W   | R    |      |      |          |   |   |   |   |

### Table 95. OCD Status Register (OCDSTAT)

### **IDLE—CPU Idling**

This bit is set if the part is in DEBUG mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.

0 = The eZ8 CPU is running.

1 = The eZ8 CPU is either stopped or looping on a BRK instruction.

### HALT—HALT Mode

- 0 = The device is not in HALT mode.

- 1 = The device is in HALT mode.

|                   |                                                                     | V <sub>DD</sub> = 3.0–3.6 V<br>T <sub>A</sub> = -40 °C to 105 °C |      |         |                                                   |                                                                                                                                  |  |

|-------------------|---------------------------------------------------------------------|------------------------------------------------------------------|------|---------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                           | Minimum Typica                                                   |      | Maximum | Units                                             | Conditions                                                                                                                       |  |

|                   | Resolution                                                          | 10                                                               | _    | _       | bits                                              | External V <sub>REF</sub> = 3.0 V;                                                                                               |  |

|                   | Differential Nonlinearity<br>(DNL)                                  | -0.25                                                            | -    | 0.25    | lsb                                               | Guaranteed by design                                                                                                             |  |

|                   | Integral Nonlinearity (INL)                                         | -2.0                                                             | -    | 2.0     | lsb                                               | External V <sub>REF</sub> = 3.0 V                                                                                                |  |

|                   | DC Offset Error                                                     | -35                                                              | -    | 25      | mV                                                |                                                                                                                                  |  |

| V <sub>REF</sub>  | Internal Reference Voltage                                          | 1.9                                                              | 2.0  | 2.4     | V                                                 | V <sub>DD</sub> = 3.0 - 3.6 V<br>T <sub>A</sub> = -40 °C to 105 °C                                                               |  |

| VC <sub>REF</sub> | Voltage Coefficient of<br>Internal Reference Voltage                | - 78 -                                                           |      | mV/V    | V <sub>REF</sub> variation as a function of AVDD. |                                                                                                                                  |  |

| TC <sub>REF</sub> | Temperature Coefficient of Internal Reference Voltage               | -                                                                | 1    | -       | mV/ <sup>0</sup> C                                |                                                                                                                                  |  |

|                   | Single-Shot Conversion<br>Period                                    |                                                                  | 5129 |         | cycles                                            | System clock cycles                                                                                                              |  |

|                   | Continuous Conversion<br>Period                                     | 256                                                              |      | cycles  | System clock cycles                               |                                                                                                                                  |  |

| R <sub>S</sub>    | Analog Source Impedance                                             | -                                                                | -    | 150     | W                                                 | Recommended                                                                                                                      |  |

| Zin               | Input Impedance                                                     |                                                                  | 150  |         | KΩ                                                |                                                                                                                                  |  |

| V <sub>REF</sub>  | External Reference<br>Voltage                                       |                                                                  |      | AVDD    | V                                                 | AVDD <= VDD. When<br>using an external<br>reference voltage,<br>decoupling capacitance<br>should be placed from<br>VREF to AVSS. |  |

| I <sub>REF</sub>  | Current draw into VREF<br>pin when driving with<br>external source. |                                                                  | 25.0 | 40.0    | μA                                                |                                                                                                                                  |  |

## Table 104. Analog-to-Digital Converter Electrical Characteristics and Timing

## Packaging

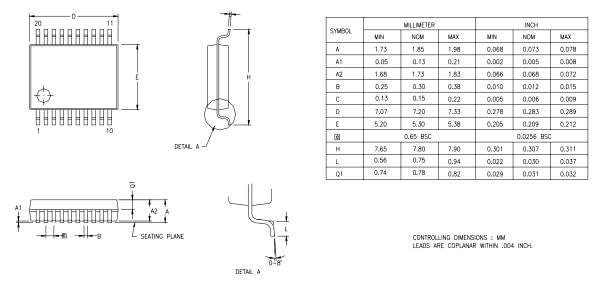

Figure 60 displays the 20-pin SSOP package available for Z8 Encore!  $XP^{\mbox{\sc B}}$  F0822 Series devices.

Figure 60. 20-Pin Small Shrink Outline Package (SSOP)

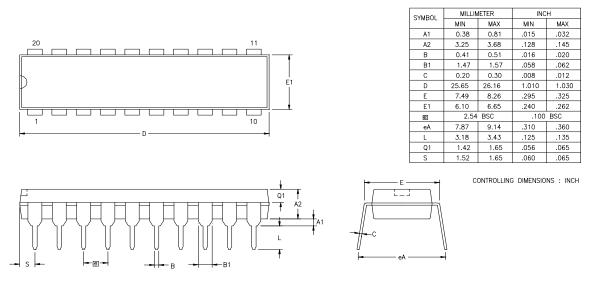

Figure 61 displays the 20-pin PDIP package available for Z8 Encore! XP F0822 Series devices.

Figure 61. 20-Pin Plastic Dual-Inline Package (PDIP)

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

operation timing 155 page erase 158 page select register 160 FPS register 160 FSTAT register 160

## G

gated mode 82 general-purpose I/O 47 GPIO 4, 47 alternate functions 47 architecture 47 control register definitions 49 input data sample timing 200 interrupts 49 port A-C pull-up enable sub-registers 54 port A-H address registers 50 port A-H alternate function sub-registers 51 port A-H control registers 51 port A-H data direction sub-registers 51 port A-H high drive enable sub-registers 53 port A-H input data registers 54 port A-H output control sub-registers 52 port A-H output data registers 55 port A-H stop mode recovery sub-registers 53 port availability by device 47 port input timing 200 port output timing 201

## Η

H 212 HALT 216 halt mode 45, 216 hexadecimal number prefix/suffix 212

## I

I2C 4 10-bit address read transaction 137 10-bit address transaction 134 10-bit addressed slave data transfer format 134 10-bit receive data format 137

7-bit address transaction 132 7-bit address, reading a transaction 136 7-bit addressed slave data transfer format 131, 132.133 7-bit receive data transfer format 136 baud high and low byte registers 143, 145 C status register 140 control register definitions 139 controller 127 controller signals 9 interrupts 128 operation 128 SDA and SCL signals 128 stop and start conditions 130 I2CBRH register 143, 144, 145 I2CBRL register 143 I2CCTL register 141 I2CDATA register 139 I2CSTAT register 140 IM 211 immediate data 211 immediate operand prefix 212 **INC 214** increment 214 increment word 214 **INCW 214** indexed 211 indirect address prefix 212 indirect register 211 indirect register pair 211 indirect working register 211 indirect working register pair 211 infrared encoder/decoder (IrDA) 109 instruction set, ez8 CPU 209 instructions ADC 214 ADCX 214 ADD 214 **ADDX 214** AND 217 **ANDX 217** arithmetic 214 BCLR 215 **BIT 215**