### Zilog - Z8F0822SJ020SC Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 19                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 5x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

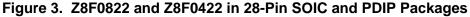

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0822sj020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| OCD Interface                                           | 1 |

|---------------------------------------------------------|---|

| Debug Mode                                              | 3 |

| OCD Data Format 173                                     | 3 |

| OCD Auto-Baud Detector/Generator 174                    | 4 |

| OCD Serial Errors 174                                   |   |

| Breakpoints                                             |   |

| OCDCNTR Register                                        |   |

| On-Chip Debugger Commands 176                           |   |

| On-Chip Debugger Control Register Definitions           |   |

| OCD Control Register                                    |   |

| OCD Status Register                                     |   |

| Electrical Characteristics                              |   |

| Absolute Maximum Ratings                                |   |

| DC Characteristics                                      |   |

| AC Characteristics                                      |   |

| On-Chip Peripheral AC and DC Electrical Characteristics |   |

| General Purpose I/O Port Input Data Sample Timing       |   |

| General Purpose I/O Port Output Timing                  |   |

| On-Chip Debugger Timing                                 |   |

| SPI MASTER Mode Timing                                  |   |

| SPI SLAVE Mode Timing                                   |   |

| I2C Timing                                              |   |

| eZ8 CPU Instruction Set                                 |   |

| Assembly Language Programming Introduction              |   |

| Assembly Language Programming infoduction               |   |

| eZ8 CPU Instruction Notation                            |   |

| Condition Codes                                         |   |

| eZ8 CPU Instruction Classes                             |   |

| eZ8 CPU Instruction Summary                             |   |

| Flags Register                                          |   |

| Opcode Maps                                             |   |

| Packaging                                               |   |

| Ordering Information                                    |   |

| Part Number Suffix Designations                         |   |

| Index                                                   |   |

| Customer Support                                        |   |

|                                                         |   |

Table of Contents

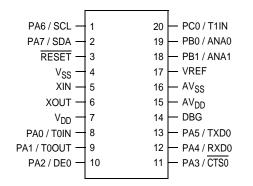

Figure 4. Z8F0811 and Z8F0411 in 20-Pin SSOP and PDIP Packages

#### **UARTO Status 0** U0STAT0 (F41H - Read Only) **UART0** Control 0 D7 D6 D5 D4 D3 D2 D1 D0 U0CTL0 (F42H - Read/Write) D7 D6 D5 D4 D3 D2 D1 D0 -CTS signal Returns the level of the CTS -Loop Back Enable 0 = Normal operation 1 = Transmit data is looped signal Transmitter Empty 0 = Data is currently back to the receiver transmitting 1 = Transmission is STOP Bit Select 0 = Transmitter sends 1 complete STOP bit -Transmitter Data Register 0 = Transmit Data Register is 1 = Transmitter sends 2STOP bits full 1 = Transmit Data register is Send Break 0 = No break is sent empty 1 = Output of the transmitter Break Detect 0 = No break occurred is zero Parity Select 0 = Even parity 1 = A break occurred 1 = Odd parity Framing Error 0 = No framing error Parity Enable 0 = Parity is disabled occurred 1 = A framing occurred 1 = Parity is enabled Overrun Error CTS Enable 0 = No overrrun error0 = CTS signal has no effect occurred on the 1 = An overrun error transmitter occurred 1 = UART recognizes $\overline{CTS}$ signal as a Parity Error transmit enable control 0 = No parity error occurred 1 = A parity error occurred signal Receive Data Available Receive Enable 0 = Receive Data Register is 0 = Receiver disabled 1 = Receiver enabled empty 1 = A byte is available in the Transmit Enable 0 = Transmitter disabled Receive Data Register 1 = Transmitter enabled

- WDT's internal RC oscillator continues to operate.

- If enabled, the WDT continues to operate.

- All other on-chip peripherals continue to operate.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- WDT time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout reset

- External **RESET** pin assertion

To minimize current in HALT mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

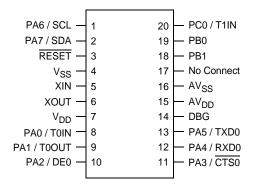

Figure 8. GPIO Port Pin Block Diagram

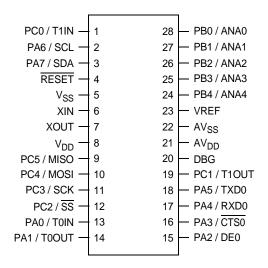

| Port   | Pin              | Mnemonic     | Alternate Function Description                    |  |  |  |  |

|--------|------------------|--------------|---------------------------------------------------|--|--|--|--|

| Port A | PA0              | TOIN         | Timer 0 Input                                     |  |  |  |  |

|        | PA1              | TOOUT        | Timer 0 Output                                    |  |  |  |  |

|        | PA2              | DE           | UART 0 Driver Enable                              |  |  |  |  |

|        | PA3              | CTS0         | UART 0 Clear to Send                              |  |  |  |  |

|        | PA4              | RXD0 / IRRX0 | UART 0 / IrDA 0 Receive Data                      |  |  |  |  |

|        | PA5 TXD0 / IRTX0 |              | UART 0 / IrDA 0 Transmit Data                     |  |  |  |  |

|        | PA6              | SCL          | I <sup>2</sup> C Clock (automatically open-drain) |  |  |  |  |

|        | PA7              | SDA          | I <sup>2</sup> C Data (automatically open-drain)  |  |  |  |  |

| Port B | PB0              | ANA0         | ADC Analog Input 0                                |  |  |  |  |

|        | PB1              | ANA1         | ADC Analog Input 1                                |  |  |  |  |

|        | PB2              | ANA2         | ADC Analog Input 2                                |  |  |  |  |

|        | PB3              | ANA3         | ADC Analog Input 3                                |  |  |  |  |

|        | PB4              | ANA4         | ADC Analog Input 4                                |  |  |  |  |

| Table 12. Port Alternate | e Function Mappin | ıg |

|--------------------------|-------------------|----|

|--------------------------|-------------------|----|

## Port A–C Control Registers

The Port A–C Control Registers set the GPIO port operation. The value in the corresponding Port A–C Address Register determines the control sub-registers accessible using the Port A–C Control Register (Table 15).

### Table 15. Port A–C Control Registers (PxCTL)

| BITS  | 7    | 6 | 5 | 4        | 3        | 2 | 1 | 0 |  |  |  |  |

|-------|------|---|---|----------|----------|---|---|---|--|--|--|--|

| FIELD | PCTL |   |   |          |          |   |   |   |  |  |  |  |

| RESET | 00H  |   |   |          |          |   |   |   |  |  |  |  |

| R/W   | R/W  |   |   |          |          |   |   |   |  |  |  |  |

| ADDR  |      |   |   | FD1H, FD | 5H, FD9H |   |   |   |  |  |  |  |

#### PCTL[7:0]—Port Control

The Port Control Register provides access to all sub-registers that configure the GPIO Port operation.

### Port A–C Data Direction Sub-Registers

The Port A–C Data Direction sub-register is accessed through the Port A–C Control register by writing 01H to the Port A–C Address Register (Table 16).

#### Table 16. Port A–C Data Direction Sub-Registers

| BITS  | 7        | 6                               | 5           | 4             | 3            | 2            | 1            | 0        |  |  |  |  |  |

|-------|----------|---------------------------------|-------------|---------------|--------------|--------------|--------------|----------|--|--|--|--|--|

| FIELD | DD7      | DD7 DD6 DD5 DD4 DD3 DD2 DD1 DD0 |             |               |              |              |              |          |  |  |  |  |  |

| RESET | <u> </u> |                                 |             |               |              |              |              |          |  |  |  |  |  |

| R/W   | R/W      |                                 |             |               |              |              |              |          |  |  |  |  |  |

| ADDR  | lf 01H i | n Port A–C                      | Address Reg | gister, acces | sible throug | h the Port A | -C Control F | Register |  |  |  |  |  |

### DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

- 0 = Output. Data in the Port A–C Output Data Register is driven onto the port pin.

- 1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tri-stated.

#### Port A–C Alternate Function Sub-Registers

The Port A–C Alternate Function sub-register (Table 17) is accessed through the Port A–C Control Register by writing 02H to the Port A–C Address Register. The Port A–C Alternate Function sub-registers select the alternate functions for the selected

- 4. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

#### **PWM Mode**

In PWM mode, the timer outputs a Pulse-Width Modulator output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte Registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte Registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and then transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and then transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte Registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

### Table 43. Timer 0–1 PWM High Byte Register (TxPWMH)

| BITS  | 7          | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------------|---|---|----|----|---|---|---|--|--|

| FIELD |            |   |   | PW | ΜH |   |   |   |  |  |

| RESET | 0          |   |   |    |    |   |   |   |  |  |

| R/W   | R/W        |   |   |    |    |   |   |   |  |  |

| ADDR  | F04H, F0CH |   |   |    |    |   |   |   |  |  |

### Table 44. Timer 0–1 PWM Low Byte Register (TxPWML)

| BITS  | 7    | 6 | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |  |  |  |

|-------|------|---|---|-------|------|---|---|---|--|--|--|--|--|--|

| FIELD | PWML |   |   |       |      |   |   |   |  |  |  |  |  |  |

| RESET | 0    |   |   |       |      |   |   |   |  |  |  |  |  |  |

| R/W   | R/W  |   |   |       |      |   |   |   |  |  |  |  |  |  |

| ADDR  |      |   |   | F05H, | F0DH |   |   |   |  |  |  |  |  |  |

#### PWMH and PWML—Pulse-Width Modulator High and Low Bytes

These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

## Timer 0–3 Control 0 Registers

The Timer 0–3 Control 0 (TxCTL0) registers (Table 45) allow cascading of the Timers.

| BITS  | 7                      | 6 | 5 | 4 | 3 | 2 1 0 |  |  |  |  |  |

|-------|------------------------|---|---|---|---|-------|--|--|--|--|--|

| FIELD | Reserved CSC Reserved  |   |   |   |   |       |  |  |  |  |  |

| RESET | 0                      |   |   |   |   |       |  |  |  |  |  |

| R/W   | R/W                    |   |   |   |   |       |  |  |  |  |  |

| ADDR  | F06H, F0EH, F16H, F1EH |   |   |   |   |       |  |  |  |  |  |

#### **CSC—Cascade Timers**

- 0 = Timer Input signal comes from the pin.

- 1 = For Timer 0, input signal is connected to Timer 1 output.

- For Timer 1, input signal is connected to Timer 0 output.

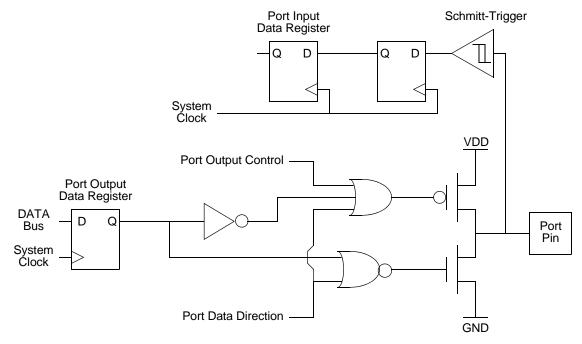

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

### **SPI Signals**

The four basic SPI signals are:

- MISO (Master-In, Slave-Out)

- MOSI (Master-Out, Slave-In)

- SCK (Serial Clock)

- <u>SS</u> (Slave Select)

The following sections discuss these SPI signals. Each signal is described in both Master and Slave modes.

#### Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Serial Clock**

The Serial Clock (SCK) synchronizes data movement both in and out of the device through its MOSI and MISO pins. In MASTER mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted. When configured as a slave, the SPI block requires a minimum SCK period of greater than or equal to 8 times the system (XIN) clock period.

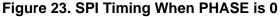

### **Transfer Format PHASE is 0**

Figure 23 displays the timing diagram for an SPI transfer in which PHASE is cleared to 0. The two SCK waveforms show polarity with CLKPOL reset to 0 and with CLKPOL set to one. The diagram can be interpreted as either a Master or Slave timing diagram since the SCK Master-In/Slave-Out (MISO) and Master-Out/Slave-In (MOSI) pins are directly connected between the Master and the Slave.

#### **Transfer Format PHASE is 1**

Figure 24 displays the timing diagram for an SPI transfer in which PHASE is one. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

NUMBITS field in the SPIMODE Register must be set to be consistent with the other SPI devices. The STR bit in the SPICTL Register can be used if desired to force a "startup" interrupt. The BIRQ bit in the SPICTL Register and the SSV bit in the SPIMODE Register is not used in SLAVE mode. The SPI Baud Rate Generator is not used in SLAVE mode so the SPIBRH and SPIBRL Registers need not be initialized.

If the slave has data to send to the master, the data must be written to the SPIDAT Register before the transaction starts (first edge of SCK when  $\overline{SS}$  is asserted). If the SPIDAT Register is not written prior to the slave transaction, the MISO pin outputs whatever value is currently in the SPIDAT Register.

Due to the delay resulting from synchronization of the SPI input signals to the internal system clock, the maximum SPICLK baud rate that can be supported in SLAVE mode is the system clock frequency (XIN) divided by 8. This rate is controlled by the SPI Master.

### **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status Register indicates when a data transmission error has been detected.

#### **Overrun (Write Collision)**

An overrun error (write collision) indicates a write to the SPI Data Register was attempted while a data transfer is in progress (in either Master or Slave modes). An overrun sets the OVR bit in the SPI Status Register to 1. Writing a 1 to OVR clears this error flag. The data register is not altered when a write occurs while data transfer is in progress.

#### Mode Fault (Multi-Master Collision)

A mode fault indicates when more than one Master is trying to communicate at the same time (a multi-master collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status Register to 1. Writing a 1 to COL clears this error Flag.

#### **SLAVE Mode Abort**

In SLAVE mode, if the  $\overline{SS}$  pin deasserts before all bits in a character have been transferred, the transaction aborts. When this condition occurs the ABT bit is set in the SPISTAT Register as well as the IRQ bit (indicating the transaction is complete). The next time  $\overline{SS}$  asserts, the MISO pin outputs SPIDAT[7], regardless of where the previous transaction left off. Writing a 1 to ABT clears this error flag.

#### SPI Interrupts

When SPI interrupts are enabled, the SPI generates an interrupt after character transmission/reception completes in both Master and Slave modes. A character is defined to be 1 through 8 bits by the NUMBITS field in the SPI Mode Register. In SLAVE mode it is not If the slave does not acknowledge, the Not Acknowledge interrupt occurs (NCKI bit is set in the Status register, ACK bit is cleared). Software responds to the Not Acknowledge interrupt by setting the STOP bit and clearing the TXI bit. The I2C Controller sends the STOP condition on the bus and clears the STOP and NCKI bits. The transaction is complete (ignore the following steps).

- The I<sup>2</sup>C Controller shifts in the byte of data from the I<sup>2</sup>C Slave on the SDA signal. The I<sup>2</sup>C Controller sends a Not Acknowledge to the I<sup>2</sup>C Slave if the NAK bit is set (last byte), else it sends an Acknowledge.

- 8. The  $I^2C$  Controller asserts the Receive interrupt (RDRF bit set in the Status register).

- 9. Software responds by reading the I<sup>2</sup>C Data Register which clears the RDRF bit. If there is only one more byte to receive, set the NAK bit of the I<sup>2</sup>C Control Register.

- 10. If there are more bytes to transfer, return to Step 7.

- 11. After the last byte is shifted in, a Not Acknowledge interrupt is generated by the I<sup>2</sup>C Controller.

- 12. Software responds by setting the STOP bit of the  $I^2C$  Control Register.

- 13. A STOP condition is sent to the  $I^2C$  Slave, the STOP and NCKI bits are cleared.

### **Read Transaction with a 10-Bit Address**

Figure 31 displays the read transaction format for a 10-bit addressed slave. The shaded regions indicate data transferred from the  $I^2C$  Controller to slaves and unshaded regions indicate data transferred from the slaves to the  $I^2C$  Controller.

| S | Slave Address<br>1st 7 bits | W=0 | A | Slave Address<br>2nd Byte | A | Slave Address<br>1st 7 bits | R=1 | Α | Data | A | Data | Ā | Ρ |

|---|-----------------------------|-----|---|---------------------------|---|-----------------------------|-----|---|------|---|------|---|---|

### Figure 31. Receive Data Format for a 10-Bit Addressed Slave

The first seven bits transmitted in the first byte are 11110XX. The two bits XX are the two most-significant bits of the 10-bit address. The lowest bit of the first byte transferred is the write control bit.

Follow the steps below for the data transfer procedure for a read operation to a 10-bit addressed slave:

- 1. Software writes 11110B followed by the two address bits and a 0 (write) to the I<sup>2</sup>C Data Register.

- 2. Software asserts the START and TXI bits of the  $I^2C$  Control Register.

- 3. The  $I^2C$  Controller sends the Start condition.

- 4. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift register with the contents of the I<sup>2</sup>C Data Register.

# Operation

### **Automatic Power-Down**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered-down. From this power-down state, the ADC requires 40 system clock cycles to power-up. The ADC powers up when a conversion is requested using the ADC Control Register.

### Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the desired analog inputs by configuring the GPIO pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write to the ADC Control Register to configure the ADC and begin the conversion. The bit fields in the ADC Control Register is written simultaneously:

- Write to the ANAIN [3:0] field to select one of the 5 analog input sources.

- Clear CONT to 0 to select a single-shot conversion.

- Write to the VREF bit to enable or disable the internal voltage reference generator.

- Set CEN to 1 to start the conversion.

- 3. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

- 4. When the conversion is complete, the ADC control logic performs the following operations:

- 10-bit data result written to {ADCD\_H[7:0], ADCD\_L[7:6]}.

- CEN resets to 0 to indicate the conversion is complete.

- An interrupt request is sent to the Interrupt Controller.

- 5. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analog-to-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data Registers. An interrupt is generated after each conversion.

### 173

### **Debug Mode**

The operating characteristics of the Z8 Encore! XP<sup>®</sup> F0822 Series devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

### **Entering Debug Mode**

The device enters DEBUG mode following any of the following operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface.

- eZ8 CPU execution of a BRK (Breakpoint) instruction.

- Match of PC to OCDCNTR register (when enabled)

- OCDCNTR register decrements to 0000H (when enabled)

- If the DBG pin is Low when the device exits Reset, the OCD automatically puts the device into DEBUG mode.

#### **Exiting Debug Mode**

The device exits DEBUG mode following any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0.

- Power-On Reset

- Voltage Brownout reset

- Asserting the **RESET** pin Low to initiate a Reset.

- Driving the DBG pin Low while the device is in STOP mode initiates a System Reset.

### **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 STOP bit (see Figure 40).

| ST | ART | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|----|-----|----|----|----|----|----|----|----|----|------|

|----|-----|----|----|----|----|----|----|----|----|------|

### Figure 40. OCD Data Format

### **SPI SLAVE Mode Timing**

Figure 52 and Table 109 provide timing information for the SPI SLAVE mode pins. Timing is shown with SCK rising edge used to source MISO output data, SCK falling edge used to sample MOSI input data.

| Figure 5 | 2. SPI | SLAVE | Mode | Timing |

|----------|--------|-------|------|--------|

|----------|--------|-------|------|--------|

|                |                                                | Delay (ns)     |                             |  |  |  |  |  |

|----------------|------------------------------------------------|----------------|-----------------------------|--|--|--|--|--|

| Parameter      | Abbreviation                                   | Minimum        | Maximum                     |  |  |  |  |  |

| SPI SLAVE      |                                                |                |                             |  |  |  |  |  |

| T <sub>1</sub> | SCK (transmit edge) to MISO output Valid Delay | 2 * Xin period | 3 * Xin period +<br>20 nsec |  |  |  |  |  |

| T <sub>2</sub> | MOSI input to SCK (receive edge) Setup Time    | 0              |                             |  |  |  |  |  |

| T <sub>3</sub> | MOSI input to SCK (receive edge) Hold Time     | 3 * Xin period |                             |  |  |  |  |  |

| T <sub>4</sub> | SS input assertion to SCK setup                | 1 * Xin period |                             |  |  |  |  |  |

### Table 109. SPI SLAVE Mode Timing

|        | Operand | Range                                                     |

|--------|---------|-----------------------------------------------------------|

|        | b       | b represents a value from 0 to 7 (000B to 111B).          |

|        | _       | See Condition Codes overview in the eZ8 CPU User Manual.  |

|        | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH |

| jister | Reg     | Reg. represents a number in the range of 000H to FFFH     |

|        |         |                                                           |

### Table 115. Notational Shorthand

Notation Description

|        | -                              |        | -                                                                                                                            |

|--------|--------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------|

| b      | Bit                            | b      | b represents a value from 0 to 7 (000B to 111B).                                                                             |

| СС     | Condition Code                 | —      | See Condition Codes overview in the eZ8 CPU User Manual.                                                                     |

| DA     | Direct Address                 | Addrs  | Addrs. represents a number in the range of 0000H to FFFFH                                                                    |

| ER     | Extended Addressing Register   | Reg    | Reg. represents a number in the range of 000H to FFFH                                                                        |

| IM     | Immediate Data                 | #Data  | Data is a number between 00H to FFH                                                                                          |

| lr     | Indirect Working Register      | @Rn    | n = 0 –15                                                                                                                    |

| IR     | Indirect Register              | @Reg   | Reg. represents a number in the range of 00H to FFH                                                                          |

| Irr    | Indirect Working Register Pair | @RRp   | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |

| IRR    | Indirect Register Pair         | @Reg   | Reg. represents an even number in the range 00H to FEH                                                                       |

| р      | Polarity                       | р      | Polarity is a single bit binary value of either 0B or 1B.                                                                    |

| r      | Working Register               | Rn     | n = 0 - 15                                                                                                                   |

| R      | Register                       | Reg    | Reg. represents a number in the range of 00H to FFH                                                                          |

| RA     | Relative Address               | Х      | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |

| rr     | Working Register Pair          | RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |

| RR     | Register Pair                  | Reg    | Reg. represents an even number in the range of 00H to FEH                                                                    |

| Vector | Vector Address                 | Vector | Vector represents a number in the range of 00H to FFH                                                                        |

| Х      | Indexed                        | #Index | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.      |

| Assembly      | Symbolic                                                                 | Address<br>Mode |     | _ Opcode(s) |   |   | Fla | ags |   | Fetch | Instr. |        |

|---------------|--------------------------------------------------------------------------|-----------------|-----|-------------|---|---|-----|-----|---|-------|--------|--------|

| Mnemonic      | Operation                                                                | dst             | src | (Hex)       | С | Ζ | S   | V   | D | Н     |        | Cycles |

| POPX dst      | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1                           | ER              |     | D8          | - | - | -   | -   | - | -     | 3      | 2      |

| PUSH src      | $SP \leftarrow SP - 1$                                                   | R               |     | 70          | - | - | -   | -   | - | -     | 2      | 2      |

|               | $@SP \leftarrow src$                                                     | IR              |     | 71          | • |   |     |     |   |       | 2      | 3      |

| PUSHX src     | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                           | ER              |     | C8          | - | - | -   | -   | - | -     | 3      | 2      |

| RCF           | C ← 0                                                                    |                 |     | CF          | 0 | - | -   | -   | - | -     | 1      | 2      |

| RET           | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |                 |     | AF          | - | - | -   | -   | - | -     | 1      | 4      |

| RL dst        |                                                                          | R               |     | 90          | * | * | *   | *   | - | -     | 2      | 2      |

|               | dst                                                                      | IR              |     | 91          |   |   |     |     |   |       | 2      | 3      |

| RLC dst       |                                                                          | R               |     | 10          | * | * | *   | *   | - | -     | 2      | 2      |

|               | C < D7 D6 D5 D4 D3 D2 D1 D0 -<br>dst                                     | IR              |     | 11          |   |   |     |     |   |       | 2      | 3      |

| RR dst        |                                                                          | R               |     | E0          | * | * | *   | *   | - | -     | 2      | 2      |

|               | D7 D6 D5 D4 D3 D2 D1 D0 → dst                                            | IR              |     | E1          |   |   |     |     |   |       | 2      | 3      |

| RRC dst       |                                                                          | R               |     | C0          | * | * | *   | *   | - | -     | 2      | 2      |

|               | -D7 D6 D5 D4 D3 D2 D1 D0 → C -<br>dst                                    | IR              |     | C1          |   |   |     |     |   |       | 2      | 3      |

| SBC dst, src  | $dst \leftarrow dst - src - C$                                           | r               | r   | 32          | * | * | *   | *   | 1 | *     | 2      | 3      |

|               | -                                                                        | r               | lr  | 33          | • |   |     |     |   |       | 2      | 4      |

|               | -                                                                        | R               | R   | 34          | • |   |     |     |   |       | 3      | 3      |

|               | -                                                                        | R               | IR  | 35          |   |   |     |     |   |       | 3      | 4      |

|               | -                                                                        | R               | IM  | 36          |   |   |     |     |   |       | 3      | 3      |

|               | -                                                                        | IR              | IM  | 37          | • |   |     |     |   |       | 3      | 4      |

| SBCX dst, src | $dst \gets dst - src - C$                                                | ER              | ER  | 38          | * | * | *   | *   | 1 | *     | 4      | 3      |

|               | -                                                                        | ER              | IM  | 39          |   |   |     |     |   |       | 4      | 3      |

# Table 126. eZ8 CPU Instruction Summary (Continued)

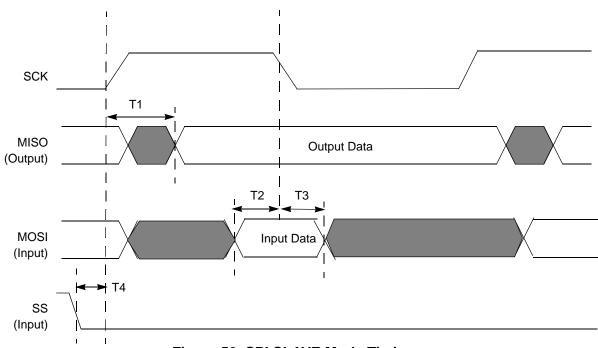

# **Flags Register**

The Flags Register contains the status information regarding the most recent arithmetic, logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits of status information that are set or cleared by CPU operations. Four of the bits (C, V, Z and S) can be tested with conditional jump instructions. Two flags (H and D) cannot be tested and are used for Binary-Coded Decimal (BCD) arithmetic.

The two remaining bits, User Flags (F1 and F2), are available as general-purpose status bits. User Flags are unaffected by arithmetic operations and must be set or cleared by instructions. The User Flags cannot be used with conditional Jumps. They are undefined at initial power-up and are unaffected by Reset. Figure 56 illustrates the flags and their bit positions in the Flags Register.

#### Figure 56. Flags Register

Interrupts, the Software Trap (TRAP) instruction, and Illegal Instruction Traps all write the value of the Flags Register to the stack. Executing an Interrupt Return (IRET) instruction restores the value saved on the stack into the Flags Register.

# Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

|          | Lower Nibble (Hex)      |                          |                            |                             |                            |                             |                            |                                |                               |                                |                            |                   |                           |                           |                  |                          |

|----------|-------------------------|--------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------|----------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|-------------------|---------------------------|---------------------------|------------------|--------------------------|

|          | 0                       | 1                        | 2                          | 3                           | 4                          | 5                           | 6                          | 7                              | 8                             | 9                              | Α                          | В                 | С                         | D                         | E                | F                        |

| 0        | 1.2<br>BRK              | 2.2<br>SRP               | 2.3<br><b>ADD</b><br>r1,r2 | 2.4<br><b>ADD</b><br>r1,lr2 | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br><b>ADD</b><br>IR2,R1 | 3.3<br><b>ADD</b><br>R1,IM | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1        | 2.2<br><b>RLC</b><br>R1 | 2.3<br><b>RLC</b><br>IR1 | 2.3<br>ADC<br>r1,r2        | 2.4<br>ADC<br>r1,lr2        | 3.3<br><b>ADC</b><br>R2,R1 | 3.4<br>ADC<br>IR2,R1        | 3.3<br>ADC<br>R1,IM        | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                   |                           |                           |                  | See 2nd<br>Opcode<br>Map |

| 2        | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2        | 2.4<br>SUB<br>r1,lr2        | 3.3<br>SUB<br>R2,R1        | 3.4<br>SUB<br>IR2,R1        | 3.3<br>SUB<br>R1,IM        | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                   |                           |                           |                  | map                      |

| 3        | 2.2<br>DEC<br>R1        | 2.3<br>DEC<br>IR1        | 2.3<br>SBC<br>r1,r2        | 2.4<br>SBC<br>r1,lr2        | 3.3<br>SBC<br>R2,R1        | 3.4<br><b>SBC</b><br>IR2,R1 | 3.3<br>SBC<br>R1,IM        | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br>SBCX                    |                            |                   |                           |                           |                  |                          |

| 4        | 2.2<br>DA<br>R1         | 2.3<br>DA<br>IR1         | 2.3<br>OR<br>r1,r2         | 2.4<br>OR<br>r1,lr2         | 3.3<br>OR<br>R2,R1         | 3.4<br>OR<br>IR2,R1         | 3.3<br>OR<br>R1,IM         | 3.4<br>OR<br>IR1,IM            | 4.3<br>ORX<br>ER2,ER1         | 4.3<br><b>ORX</b>              |                            |                   |                           |                           |                  |                          |

| 5        | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1 | 2.3<br>AND<br>r1,r2        | 2.4<br>AND<br>r1,lr2        | 3.3<br>AND<br>R2,R1        | 3.4<br>AND<br>IR2,R1        | 3.3<br>AND<br>R1,IM        | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                   |                           |                           |                  | 1.2<br>WDT               |

| 6        | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1        | 2.3<br>TCM<br>r1,r2        | 2.4<br>TCM<br>r1,lr2        | 3.3<br>TCM<br>R2,R1        | 3.4<br>TCM<br>IR2,R1        | 3.3<br>TCM<br>R1,IM        | 3.4<br>TCM<br>IR1,IM           | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1.2<br>STOP              |

| <b>7</b> | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2       | 2.3<br><b>TM</b><br>r1,r2  | 2.4<br><b>TM</b><br>r1,lr2  | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br>TM<br>R1,IM         | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.2<br>HALT              |

| 8        | 2.5<br>DECW<br>RR1      | 2.6                      | 2.5<br>LDE<br>r1,lrr2      | 2.9<br>LDEI<br>Ir1,Irr2     | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2       | 3.4<br>LDX                 | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X         |                            |                   |                           |                           |                  | 1.2<br><b>DI</b>         |

| 9        | 2.2<br>RL<br>R1         | 2.3<br><b>RL</b><br>IR1  | 2.5<br>LDE<br>r2,Irr1      | 2.9<br>LDEI<br>Ir2,Irr1     | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX<br>R2,IRR1      | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br>LEA<br>r1,r2,X         | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                   |                           |                           |                  | 1.2<br>El                |

| A        | 2.5<br>INCW<br>RR1      | 2.6<br>INCW              | 2.3<br><b>CP</b><br>r1,r2  | 2.4<br><b>CP</b><br>r1,lr2  | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM  | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.4<br>RET               |

| в        | 2.2<br>CLR<br>R1        | 2.3<br>CLR<br>IR1        | 2.3<br>XOR<br>r1,r2        | 2.4<br>XOR<br>r1,lr2        | 3.3<br>XOR<br>R2,R1        | 3.4<br>XOR<br>IR2,R1        | 3.3<br>XOR<br>R1,IM        | 3.4<br>XOR<br>IR1,IM           | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br>XORX<br>IM,ER1          |                            |                   |                           |                           |                  | 1.5<br>IRET              |

| с        | 2.2<br>RRC<br>R1        | 2.3<br>RRC<br>IR1        | 2.5<br>LDC<br>r1,lrr2      | 2.9<br>LDCI<br>Ir1,Irr2     | 2.3<br><b>JP</b><br>IRR1   | 2.9<br>LDC<br>lr1,lrr2      | i ci ,imi                  | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br><b>PUSHX</b><br>ER2    |                                |                            |                   |                           |                           |                  | 1.2<br>RCF               |

| D        | 2.2<br>SRA<br>R1        | 2.3<br>SRA<br>IR1        | 2.5<br>LDC<br>r2,Irr1      | 2.9<br>LDCI<br>Ir2,Irr1     | 2.6<br>CALL<br>IRR1        | 2.2<br>BSWAP<br>R1          | 3.3<br>CALL<br>DA          | 3.4<br>LD<br>r2,r1,X           | 3.2<br>POPX<br>ER1            |                                |                            |                   |                           |                           |                  | 1.2<br>SCF               |

| Е        | 2.2<br>RR<br>R1         | 2.3<br><b>RR</b><br>IR1  | 2.2<br>BIT<br>p,b,r1       | 2.3<br>LD<br>r1,lr2         | 3.2<br>LD<br>R2,R1         | 3.3<br>LD<br>IR2,R1         | 3.2<br>LD<br>R1,IM         | 3.3<br>LD<br>IR1,IM            | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1           |                            |                   |                           |                           |                  | 1.2<br>CCF               |

| F        | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1       | 2.6<br>TRAP<br>Vector      | 2.3<br>LD<br>lr1,r2         | 2.8<br>MULT<br>RR1         | 3.3<br>LD<br>R2,IR1         | 3.3<br><b>BTJ</b>          | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               | ,                              | V                          | V                 |                           |                           |                  |                          |

Figure 58. First Opcode Map

Upper Nibble (Hex)

| Japa<br>Enguina<br>Zared<br>Z8F08xx with 8 KB Flas | y<br>Flash | RAM     | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI | UARTs with IrDA | Description         |

|----------------------------------------------------|------------|---------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|---------------------|

| Standard Temperature: 0                            | °C to 70   | °C      |           |            |                     |                     |                  |     |                 |                     |

| Z8F0811HH020SC                                     | 8 KB       | 1 KB    | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package |

| Z8F0811PH020SC                                     | 8 KB       | 1 KB    | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package |

| Z8F0812SJ020SC                                     | 8 KB       | 1 KB    | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package |

| Z8F0812PJ020SC                                     | 8 KB       | 1 KB    | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package |

| Extended Temperature: -4                           | 40 °C to   | +105 °C | ;         |            |                     |                     |                  |     |                 |                     |

| Z8F0811HH020EC                                     | 8 KB       | 1 KB    | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package |

| Z8F0811PH020EC                                     | 8 KB       | 1 KB    | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package |

| Z8F0812SJ020EC                                     | 8 KB       | 1 KB    | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package |

| Z8F0812PJ020EC                                     | 8 KB       | 1 KB    | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package |