Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 24K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 3x16b; D/A 3x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f373cbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1 | Intro | duction                                                                |  |  |  |  |  |  |  |  |  |  |

|---|-------|------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| 2 | Desc  | scription                                                              |  |  |  |  |  |  |  |  |  |  |

| 3 | Func  | tional overview                                                        |  |  |  |  |  |  |  |  |  |  |

|   | 3.1   | ARM® Cortex®-M4 core with embedded Flash and SRAM 13                   |  |  |  |  |  |  |  |  |  |  |

|   | 3.2   | Memory protection unit                                                 |  |  |  |  |  |  |  |  |  |  |

|   | 3.3   | Embedded Flash memory 14                                               |  |  |  |  |  |  |  |  |  |  |

|   | 3.4   | Cyclic redundancy check (CRC) calculation unit                         |  |  |  |  |  |  |  |  |  |  |

|   | 3.5   | Embedded SRAM                                                          |  |  |  |  |  |  |  |  |  |  |

|   | 3.6   | Boot modes                                                             |  |  |  |  |  |  |  |  |  |  |

|   | 3.7   | Power management                                                       |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.7.1 Power supply schemes                                             |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.7.2 Power supply supervisor                                          |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.7.3 Voltage regulator                                                |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.7.4 Low-power modes                                                  |  |  |  |  |  |  |  |  |  |  |

|   | 3.8   | Clocks and startup                                                     |  |  |  |  |  |  |  |  |  |  |

|   | 3.9   | General-purpose input/outputs (GPIOs) 16                               |  |  |  |  |  |  |  |  |  |  |

|   | 3.10  | Direct memory access (DMA) 17                                          |  |  |  |  |  |  |  |  |  |  |

|   | 3.11  | Interrupts and events 17                                               |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.11.1 Nested vectored interrupt controller (NVIC)                     |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.11.2 Extended interrupt/event controller (EXTI)                      |  |  |  |  |  |  |  |  |  |  |

|   | 3.12  | 12-bit analog-to-digital converter (ADC)                               |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.12.1 Temperature sensor                                              |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.12.2 Internal voltage reference (V <sub>REFINT</sub> )               |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.12.3 V <sub>BAT</sub> battery voltage monitoring                     |  |  |  |  |  |  |  |  |  |  |

|   | 3.13  | 16-bit sigma delta analog-to-digital converters (SDADC) 19             |  |  |  |  |  |  |  |  |  |  |

|   | 3.14  | Digital-to-analog converter (DAC) 19                                   |  |  |  |  |  |  |  |  |  |  |

|   | 3.15  | Fast comparators (COMP) 20                                             |  |  |  |  |  |  |  |  |  |  |

|   | 3.16  | Touch sensing controller (TSC) 20                                      |  |  |  |  |  |  |  |  |  |  |

|   | 3.17  | Timers and watchdogs 22                                                |  |  |  |  |  |  |  |  |  |  |

|   |       | 3.17.1 General-purpose timers (TIM2 to TIM5, TIM12 to TIM17, TIM19) 23 |  |  |  |  |  |  |  |  |  |  |

DocID022691 Rev 7

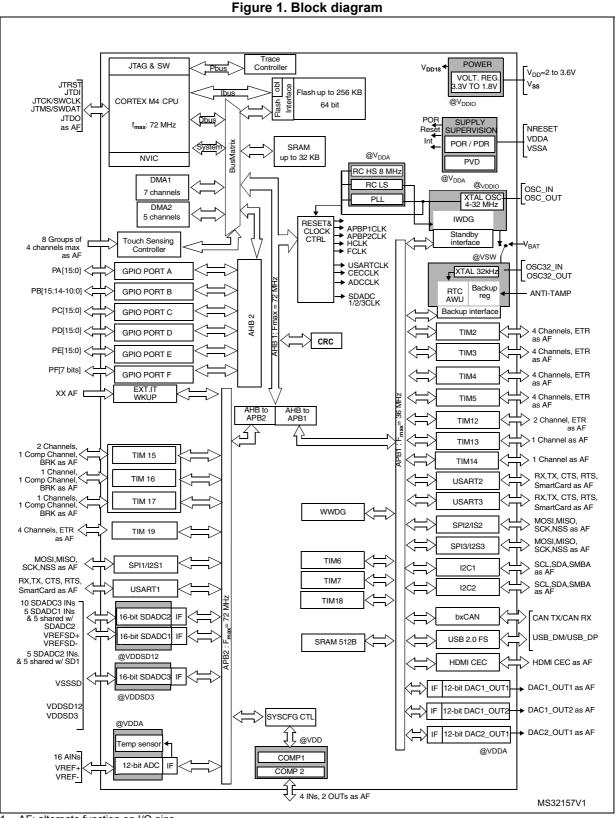

1. AF: alternate function on I/O pins.

DocID022691 Rev 7

## 3.13 **16-bit sigma delta analog-to-digital converters (SDADC)**

Three 16-bit sigma-delta analog-to-digital converters are embedded in the STM32F373xx. They have up to two separate supply voltages allowing the analog function voltage range to be independent from the STM32F373xx power supply. They share up to 21 input pins which may be configured in any combination of single-ended (up to 21) or differential inputs (up to 11).

The conversion speed is up to 16.6 ksps for each SDADC when converting multiple channels and up to 50 ksps per SDADC if single channel conversion is used. There are two conversion modes: single conversion mode or continuous mode, capable of automatically scanning any number of channels. The data can be automatically stored in a system RAM buffer, reducing the software overhead.

A timer triggering system can be used in order to control the start of conversion of the three SDADCs and/or the 12-bit fast ADC. This timing control is very flexible, capable of triggering simultaneous conversions or inserting a programmable delay between the ADCs.

Up to two external reference pins (VREFSD+, VREFSD-) and an internal 1.2/1.8 V reference can be used in conjunction with a programmable gain (x0.5 to x32) in order to fine-tune the input voltage range of the SDADC. VREFSD - pin is used as negative signal reference in case of single-ended input mode.

## 3.14 Digital-to-analog converter (DAC)

The devices feature two 12-bit buffered DACs with three output channels that can be used to convert three digital signals into three analog voltage signal outputs. The internal structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital Interface supports the following features:

- Two DAC converters with three output channels:

- DAC1 with two output channels

- DAC2 with one output channel.

- 8-bit or 10-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation (DAC1 only)

- Triangular wave generation (DAC1 only)

- Dual DAC channel independent or simultaneous conversions (DAC1 only)

- DMA capability for each channel

- External triggers for conversion

## **3.15** Fast comparators (COMP)

The STM32F373xx embeds 2 comparators with rail-to-rail inputs and high-speed output. The reference voltage can be internal or external (delivered by an I/O).

The threshold can be one of the following:

- DACs channel outputs

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or submultiple (1/4 V<sub>REFINT</sub>, 1/2 V<sub>REFINT</sub> and 3/4 V<sub>REFINT</sub>)

The comparators can be combined into a window comparator.

Both comparators can wake up the device from Stop mode and generate interrupts and breaks for the timers.

## **3.16** Touch sensing controller (TSC)

The devices provide a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect the presence of a finger near an electrode which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the electrode capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

Up to 24 touch sensing electrodes can be controlled by the TSC. The touch sensing I/Os are organized in 8 acquisition groups, with up to 4 I/Os in each group.

| Group | Group Capacitive sensing<br>signal name Pin name |                    | Group | Capacitive sensing<br>signal name | Pin<br>name |      |

|-------|--------------------------------------------------|--------------------|-------|-----------------------------------|-------------|------|

|       | TSC_G1_IO1                                       | TSC_G1_IO1 PA0     |       |                                   | TSC_G5_IO1  | PB3  |

| 1     | TSC_G1_IO2                                       | PA1                |       | 5                                 | TSC_G5_IO2  | PB4  |

| 1     | TSC_G1_IO3                                       | PA2                |       | 5                                 | TSC_G5_IO3  | PB6  |

|       | TSC_G1_IO4                                       | PA3                |       |                                   | TSC_G5_IO4  | PB7  |

|       | TSC_G2_IO1                                       | PA4 <sup>(1)</sup> |       |                                   | TSC_G6_IO1  | PB14 |

| 2     | TSC_G2_IO2                                       | PA5 <sup>(1)</sup> |       | 6                                 | TSC_G6_IO2  | PB15 |

| 2     | TSC_G2_IO3                                       | PA6 <sup>(1)</sup> |       | 0                                 | TSC_G6_IO3  | PD8  |

|       | TSC_G2_IO4                                       | PA7                |       |                                   | TSC_G6_IO4  | PD9  |

Table 3. Capacitive sensing GPIOs available on STM32F373xx devices

#### 3.17.3 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### 3.17.4 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB1 clock (PCLK1) derived from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.17.5 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source

## 3.18 Real-time clock (RTC) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either from  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are thirty two 32-bit registers used to store 128 bytes of user application data.

They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28th, 29th (leap year), 30th and 31st day of the month.

- 2 programmable alarms with wake up from Stop and Standby mode capability.

- Periodic wakeup unit with programmable resolution and period.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy.

- 3 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

| I <sup>2</sup> C features <sup>(1)</sup> | I2C1 | I2C2 |

|------------------------------------------|------|------|

| SMBus                                    | Х    | Х    |

| Wakeup from STOP                         | Х    | Х    |

| Table 7. STM32F373xx I <sup>2</sup> C im | plementation (continued) |

|------------------------------------------|--------------------------|

|------------------------------------------|--------------------------|

1. X = supported.

# 3.20 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F373xx embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

All USARTs interfaces are able to communicate at speeds of up to 9 Mbit/s.

They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode, Smartcard mode (ISO/IEC 7816 compliant), autobaudrate feature and have LIN Master/Slave capability. The USART interfaces can be served by the DMA controller.

Refer to *Table 8* for the features of USART1, USART2 and USART3.

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 | USART3 |

|---------------------------------------------|--------|--------|--------|

| Hardware flow control for modem             | Х      | Х      | Х      |

| Continuous communication using DMA          | Х      | Х      | Х      |

| Multiprocessor communication                | Х      | Х      | Х      |

| Synchronous mode                            | Х      | Х      | Х      |

| Smartcard mode                              | Х      | Х      | Х      |

| Single-wire half-duplex communication       | Х      | Х      | Х      |

| IrDA SIR ENDEC block                        | Х      | Х      | Х      |

| LIN mode                                    | Х      | Х      | Х      |

| Dual clock domain and wakeup from Stop mode | Х      | Х      | Х      |

| Receiver timeout interrupt                  | Х      | Х      | Х      |

| Modbus communication                        | Х      | Х      | Х      |

| Auto baud rate detection                    | Х      | Х      | Х      |

| Driver Enable                               | Х      | Х      | Х      |

Table 8. STM32F373xx USART implementation

1. X = supported.

| Na               | me                   | Abbreviation                                                     | Definition                                                                                            |  |  |  |  |  |

|------------------|----------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin r            | name                 |                                                                  | e specified in brackets below the pin name, the pin function reset is the same as the actual pin name |  |  |  |  |  |

|                  |                      | S                                                                | Supply pin                                                                                            |  |  |  |  |  |

| Pin              | type                 | I                                                                | Input only pin                                                                                        |  |  |  |  |  |

|                  |                      | I/O                                                              | Input / output pin                                                                                    |  |  |  |  |  |

|                  |                      | FT                                                               | 5 V tolerant I/O                                                                                      |  |  |  |  |  |

|                  |                      | FTf 5 V tolerant I/O, FM+ capable                                |                                                                                                       |  |  |  |  |  |

| I/O atr          | ucture               | TTa 3.3 V tolerant I/O directly connected to ADC                 |                                                                                                       |  |  |  |  |  |

| i/O su           | ucluie               | TC Standard 3.3 V I/O                                            |                                                                                                       |  |  |  |  |  |

|                  |                      | В                                                                | Dedicated BOOT0 pin                                                                                   |  |  |  |  |  |

|                  |                      | RST                                                              | Bidirectional reset pin with embedded weak pull-up resistor                                           |  |  |  |  |  |

| No               | tes                  | Unless otherwis<br>and after reset                               | e specified by a note, all I/Os are set as floating inputs during                                     |  |  |  |  |  |

| D.               | Alternate functions  | Functions select                                                 | ted through GPIOx_AFR registers                                                                       |  |  |  |  |  |

| Pin<br>functions | Additional functions | Functions directly selected/enabled through peripheral registers |                                                                                                       |  |  |  |  |  |

| Table 10. Legend/abbreviations used in the | pinout table |

|--------------------------------------------|--------------|

#### Table 11. STM32F373xx pin definitions

| Pi      | n nun    | nber   | s      |                                       |             |               |       | Pin func             | tions                                                     |

|---------|----------|--------|--------|---------------------------------------|-------------|---------------|-------|----------------------|-----------------------------------------------------------|

| LQFP100 | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function   | Additional functions                                      |

| 1       | B2       | -      | -      | PE2                                   | I/O         | FT            | (2)   | TSC_G7_IO1, TRACECLK | -                                                         |

| 2       | A1       | -      | -      | PE3                                   | I/O         | FT            | (2)   | TSC_G7_IO2, TRACED0  | -                                                         |

| 3       | B1       | -      | -      | PE4                                   | I/O         | FT            | (2)   | TSC_G7_IO3, TRACED1  | -                                                         |

| 4       | C2       | -      | -      | PE5                                   | I/O         | FT            | (2)   | TSC_G7_IO4, TRACED2  | -                                                         |

| 5       | D2       | -      | -      | PE6                                   | I/O         | FT            | (2)   | TRACED3              | WKUP3, RTC_TAMPER3                                        |

| 6       | E2       | 1      | 1      | VBAT                                  | S           | -             | -     | Backup pow           | er supply                                                 |

| 7       | C1       | 2      | 2      | PC13 <sup>(1)</sup>                   | I/O         | тс            | -     | -                    | WKUP2, ALARM_OUT,<br>CALIB_OUT, TIMESTAMP,<br>RTC_TAMPER1 |

DocID022691 Rev 7

| Table 11. STM32F373xx pin definitions (continued)      Pin numbers    Pin functions |          |        |        |                                       |             |               |            |                                                                                                                                                                      |                                                                 |  |  |  |

|-------------------------------------------------------------------------------------|----------|--------|--------|---------------------------------------|-------------|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|

| Pi                                                                                  | n nun    | nber   | S      |                                       |             |               |            | Pin func                                                                                                                                                             | ctions                                                          |  |  |  |

| LQFP100                                                                             | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate function                                                                                                                                                   | Additional functions                                            |  |  |  |

| 38                                                                                  | M7       | -      | -      | PE7                                   | I/O         | тс            | (3)<br>(2) | -                                                                                                                                                                    | SDADC1_AIN3P,<br>SDADC1_AIN4M,<br>SDADC2_AIN5P,<br>SDADC2_AIN6M |  |  |  |

| 39                                                                                  | L7       | 29     | 21     | PE8                                   | I/O         | тс            | (3)        | -                                                                                                                                                                    | SDADC1_AIN8P,<br>SDADC2_AIN8P                                   |  |  |  |

| 40                                                                                  | M8       | 30     | 22     | PE9                                   | I/O         | тс            | (3)        | -                                                                                                                                                                    | SDADC1_AIN7P,<br>SDADC1_AIN8M,<br>SDADC2_AIN7P,<br>SDADC2_AIN8M |  |  |  |

| 41                                                                                  | L8       | -      | -      | PE10                                  | I/O         | тс            | (3)<br>(2) | -                                                                                                                                                                    | SDADC1_AIN2P                                                    |  |  |  |

| 42                                                                                  | M9       | -      | -      | PE11                                  | I/O         | тс            | (3)<br>(2) | -                                                                                                                                                                    | SDADC1_AIN1P,<br>SDADC1_AIN2M,<br>SDADC2_AIN4P                  |  |  |  |

| 43                                                                                  | L9       | -      | -      | PE12                                  | I/O         | тс            | (3)<br>(2) | -                                                                                                                                                                    | SDADC1_AIN0P,<br>SDADC2_AIN3P,<br>SDADC2_AIN4M                  |  |  |  |

| 44                                                                                  | M10      | -      | -      | PE13                                  | I/O         | тс            | (3)<br>(2) | -                                                                                                                                                                    | SDADC1_AIN0M ,<br>SDADC2_AIN2P                                  |  |  |  |

| 45                                                                                  | M11      | -      | -      | PE14                                  | I/O         | тс            | (3)<br>(2) | -                                                                                                                                                                    | SDADC2_AIN1P,<br>SDADC2_AIN2M                                   |  |  |  |

| 46                                                                                  | M12      | -      | -      | PE15                                  | I/O         | тс            | (3)<br>(2) | USART3_RX                                                                                                                                                            | SDADC2_AIN0P                                                    |  |  |  |

| 47                                                                                  | L10      | -      | -      | PB10                                  | I/O         | тс            | (3)<br>(2) | SPI2_SCK/I2S2_CK,<br>USART3_TX, CEC,<br>TSC_SYNC, TIM2_CH3                                                                                                           | SDADC2_AIN0M                                                    |  |  |  |

| 48                                                                                  | L11      | -      | -      | VREFSD-                               | S           | -             | (2)        | External reference voltage for SDADC1, SDADC2, SDADC<br>(negative input), negative SDADC analog input in SDADC<br>single ended mode                                  |                                                                 |  |  |  |

| 49                                                                                  | F12      | -      | -      | VSSSD                                 | S           | -             | (2)        | SDADC1, SDADC2, SDADC3 ground                                                                                                                                        |                                                                 |  |  |  |

| -                                                                                   | -        | 31     | 23     | VSSSD/<br>VREFSD-                     | S           | -             | -          | SDADC1, SDADC2, SDADC3 ground / External reference<br>voltage for SDADC1, SDADC2, SDADC3 (negative input),<br>negative SDADC analog input in SDADC single ended mode |                                                                 |  |  |  |

| 50                                                                                  | G12      | -      | -      | VDDSD12                               | S           | -             | (2)        | SDADC1 and SDAD                                                                                                                                                      | C2 power supply                                                 |  |  |  |

| -                                                                                   | -        | 32     | 24     | VDDSD                                 | S           | -             | -          | SDADC1, SDADC2, SE                                                                                                                                                   | DADC3 power supply                                              |  |  |  |

Table 11. STM32F373xx pin definitions (continued)

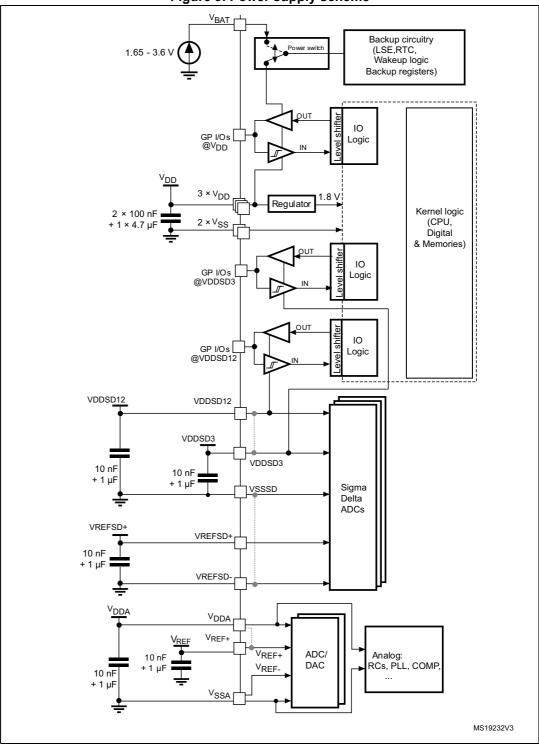

#### 6.1.6 Power supply scheme

Figure 9. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

#### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 10: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{APB1} = f_{AHB}/2$ ,  $f_{APB2} = f_{AHB}$

- When f<sub>HCLK</sub> > 8 MHz PLL is ON and PLL inputs is equal to HSI/2 = 4 MHz (if internal clock is used) or HSE = 8 MHz (if HSE bypass mode is used)

The parameters given in *Table 28* to *Table 34* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

|                 |                         |                       |                   | AI   | l periphe | erals ena           | abled  | All peripherals disabled |                                     |       |        |      |

|-----------------|-------------------------|-----------------------|-------------------|------|-----------|---------------------|--------|--------------------------|-------------------------------------|-------|--------|------|

| Symbol          | Parameter               | Conditions            | f <sub>HCLK</sub> | Tun  | м         | ax @ T <sub>A</sub> | (2)    | Tun                      | Max @ T <sub>A</sub> <sup>(2)</sup> |       |        | Unit |

|                 |                         |                       |                   | Тур  | 25 °C     | 85 °C               | 105 °C | Тур                      | 25 °C                               | 85 °C | 105 °C |      |

|                 |                         |                       | 72 MHz            | 63.1 | 70.7      | 71.5                | 73.4   | 29.2                     | 31.1                                | 31.7  | 34.2   |      |

|                 |                         | HSE                   | 64 MHz            | 56.3 | 63.3      | 64.1                | 64.9   | 26.1                     | 27.8                                | 28.4  | 30.4   |      |

|                 |                         | bypass,               | 48 MHz            | 42.5 | 48.5      | 48.0                | 50.1   | 19.9                     | 22.6                                | 21.9  | 23.1   |      |

|                 |                         | PLL on                | 32 MHz            | 28.8 | 31.4      | 32.2                | 34.3   | 13.1                     | 16.1                                | 14.9  | 16.2   |      |

|                 | Supply                  |                       | 24 MHz            | 21.9 | 24.4      | 24.4                | 25.8   | 10.1                     | 10.9                                | 11.9  | 12.4   |      |

|                 | current in              | HSE                   | 8 MHz             | 7.3  | 8.0       | 9.3                 | 9.3    | 3.7                      | 4.1                                 | 4.4   | 5.0    |      |

| I <sub>DD</sub> | Run mode,<br>code       | PLL off               | 1 MHz             | 1.1  | 1.5       | 1.8                 | 2.3    | 0.8                      | 1.1                                 | 1.4   | 1.9    | mA   |

|                 | executing<br>from Flash |                       | 64 MHz            | 51.7 | 57.7      | 58.0                | 60.4   | 25.8                     | 27.6                                | 28.1  | 30.1   |      |

|                 |                         |                       | 48 MHz            | 38.6 | 45.9      | 43.5                | 46.9   | 19.8                     | 21.9                                | 21.7  | 22.8   |      |

|                 |                         | PLL on                | 32 MHz            | 26.4 | 31.1      | 29.7                | 31.9   | 13.1                     | 15.7                                | 14.8  | 16.2   |      |

|                 |                         |                       | 24 MHz            | 20.3 | 22.6      | 22.6                | 23.7   | 6.9                      | 7.5                                 | 8.1   | 8.8    |      |

|                 |                         | HSI clock,<br>PLL off | 8 MHz             | 7.0  | 7.6       | 8.8                 | 8.8    | 3.7                      | 4.1                                 | 4.4   | 5.0    |      |

#### Table 28. Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6 V<sup>(1)</sup>

| Symbol           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                                                           |                         | Тур(  | @V <sub>DD</sub> ( | V <sub>DD</sub> =V |       |       |                           |                           |                            |      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------|-------------------------|-------|--------------------|--------------------|-------|-------|---------------------------|---------------------------|----------------------------|------|

|                  | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | Conditions                                                |                         | 2.4 V | 2.7 V              | 3.0 V              | 3.3 V | 3.6 V | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>85 °С | T <sub>A</sub> =<br>105 °C | Unit |

| I <sub>DDA</sub> | Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | Regulator in run mode, all oscillators OFF                | 1.99                    | 2.07  | 2.19               | 2.33               | 2.46  | 2.64  | 10.8                      | 11.8                      | 12.4                       |      |

|                  | current in<br>Stop mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DDSD12 | Regulator in<br>low-power<br>mode, all<br>oscillators OFF | 1.99                    | 2.07  | 2.18               | 2.32               | 2.47  | 2.63  | 10.6                      | 11.5                      | 12.5                       |      |

|                  | Supply purcent in but the second seco | >      | LSI ON and<br>IWDG ON                                     | 2.44                    | 2.53  | 2.7                | 2.89               | 3.09  | 3.33  | -                         | -                         | -                          | μA   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | V <sub>DDA</sub>                                          | LSI OFF and<br>IWDG OFF | 1.87  | 1.94               | 2.06               | 2.19  | 2.35  | 2.51                      | 4.1                       | 4.5                        | 4.8  |

| IDDAmon          | Supply current for $V_{DDA}$ and $V_{DDSD12}$ monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | -                                                         |                         | 1.02  | 1.12               | 1.2                | 1.27  | 1.4   | -                         | -                         | -                          |      |

| Table 31. Typical and maximum V <sub>DDA</sub> consumption in Stop and Standby modes |

|--------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------|

1. Data based on characterization results and tested in production.

2. To obtain data with monitoring OFF is necessary to substract the IDDAmon current.

| Table 32. Typical and maximum current consumption from V <sub>BAT</sub> supply." |                                                                                 |                                                                                  |                        |         |         |         |         |         |                    |                          |                           |                            |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------|---------|---------|---------|---------|---------|--------------------|--------------------------|---------------------------|----------------------------|

| Symbol F                                                                         | Parameter                                                                       | Conditions                                                                       | Тур @ V <sub>ВАТ</sub> |         |         |         |         |         | Max <sup>(2)</sup> |                          |                           |                            |

|                                                                                  |                                                                                 |                                                                                  | = 1.65 V               | = 1.8 V | = 2.0 V | = 2.4 V | = 2.7 V | = 3.3 V | = 3.6 V            | T <sub>A</sub> =<br>25 ℃ | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C |

| Backup<br>I <sub>DD_</sub> domain<br><sub>VBAT</sub> supply<br>current           | LSE & RTC ON;<br>"Xtal mode" lower<br>driving capability;<br>LSEDRV[1:0] = '00' | 0.50                                                                             | 0.52                   | 0.55    | 0.63    | 0.70    | 0.87    | 0.95    | 1.1                | 1.6                      | 2.2                       | μA                         |

|                                                                                  | supply                                                                          | LSE & RTC ON;<br>"Xtal mode" higher<br>driving capability;<br>LSEDRV[1:0] = '11' | 0.85                   | 0.90    | 0.93    | 1.02    | 1.10    | 1.27    | 1.38               | 1.6                      | 2.4                       | 3.0                        |

## Table 32. Typical and maximum current consumption from $V_{BAT}$ supply<sup>(1)</sup>

1. Crystal used: Abracon ABS07-120-32.768kHz-T with 6 pF of CL for typical values.

2. Guaranteed by characterization results.

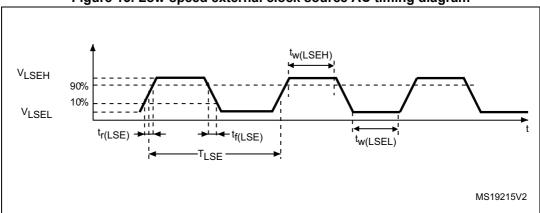

Figure 13. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                   | Conditions <sup>(1)</sup>                             | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------|-------------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency        | -                                                     | 4                  | 8   | 32                 | MHz  |

| R <sub>F</sub>                      | Feedback resistor           | -                                                     | -                  | 200 | -                  | kΩ   |

|                                     |                             | During startup <sup>(3)</sup>                         | -                  | -   | 8.5                |      |

| I <sub>DD</sub>                     |                             | V <sub>DD</sub> = 3.3 V, Rm= 30 Ω<br>CL= 10 pF@8 MHz  | -                  | 0.4 | -                  |      |

|                                     | HSE current consumption     | V <sub>DD</sub> = 3.3 V, Rm= 45 Ω<br>CL= 10 pF@8 MHz  | -                  | 0.5 | -                  |      |

|                                     |                             | V <sub>DD</sub> = 3.3 V, Rm= 30 Ω<br>CL=5 pF@32 MHz   | -                  | 0.8 | -                  | mA   |

|                                     |                             | V <sub>DD</sub> = 3.3 V, Rm= 30 Ω<br>CL= 10 pF@32 MHz | -                  | 1   | -                  |      |

|                                     |                             | V <sub>DD</sub> = 3.3 V, Rm= 30 Ω<br>CL= 20 pF@32 MHz | -                  | 1.5 | -                  |      |

| 9 <sub>m</sub>                      | Oscillator transconductance | scillator transconductance Startup                    |                    | -   | -                  | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                | V <sub>DD</sub> is stabilized                         | -                  | 2   | -                  | ms   |

| Table 40. HSE of | scillator cha | aracteristics |

|------------------|---------------|---------------|

|------------------|---------------|---------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by design.

3. This consumption level occurs during the first 2/3 of the  $t_{SU(HSE)}$  startup time

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 41*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol              | Parameter                                                         | Conditions <sup>(1)</sup>                          | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|---------------------|-------------------------------------------------------------------|----------------------------------------------------|--------------------|-----|--------------------|------|

| I <sub>DD</sub>     |                                                                   | LSEDRV[1:0]=00<br>lower driving capability         | -                  | 0.5 | 0.9                |      |

|                     | LSE current consumption                                           | LSEDRV[1:0]= 10<br>medium low driving capability   | -                  | -   | 1                  |      |

|                     |                                                                   | LSEDRV[1:0] = 01<br>medium high driving capability | -                  | -   | 1.3                | μA   |

|                     |                                                                   | LSEDRV[1:0]=11<br>higher driving capability        | -                  | -   | 1.6                |      |

| 9 <sub>m</sub>      |                                                                   | LSEDRV[1:0]=00<br>lower driving capability         | 5                  | -   | -                  |      |

|                     | Oscillator medium low driving c<br>transconductance LSEDRV[1:0] = | LSEDRV[1:0]= 10<br>medium low driving capability   | 8                  | -   | -                  | μA/V |

|                     |                                                                   | LSEDRV[1:0] = 01<br>medium high driving capability | 15 -               |     | -                  | μΑνν |

|                     |                                                                   | LSEDRV[1:0]=11<br>higher driving capability        | 25                 | -   | -                  |      |

| $t_{SU(LSE)}^{(3)}$ | Startup time                                                      | V <sub>DD</sub> is stabilized                      | -                  | 2   | -                  | s    |

#### Table 41. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design.

3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

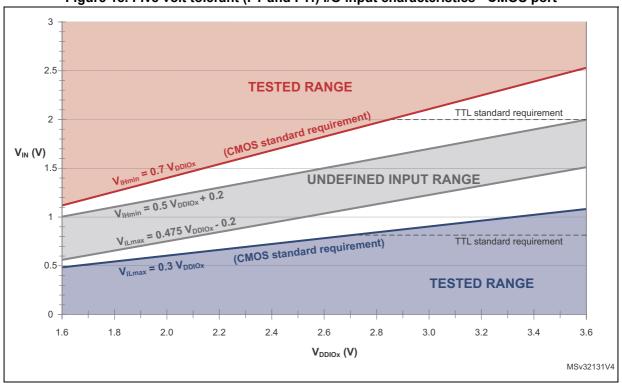

Figure 18. Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to ± 8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH})$ .

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on all VDD\_x and VDDSDx, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub> cannot exceed the absolute maximum rating SI<sub>VDD</sub> (see *Table 20*).

- The sum of the currents sunk by all the I/Os on all VSS\_x and VSSSD, plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating SI<sub>VSS</sub> (see *Table 20*).

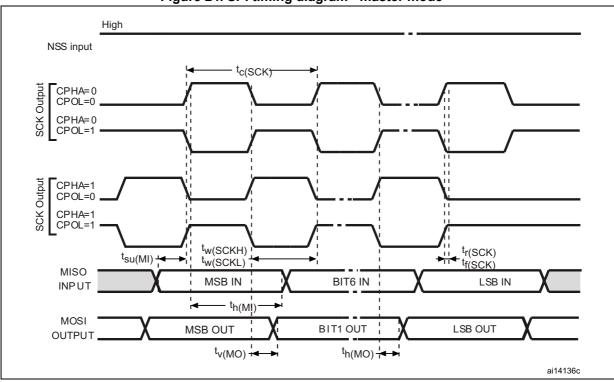

Figure 24. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

## 6.3.19 Comparator characteristics

| Symbol                   | Parameter                                                         | Conditio                                              | ns                       | Min | Тур | Max <sup>(1)</sup>  | Unit  |

|--------------------------|-------------------------------------------------------------------|-------------------------------------------------------|--------------------------|-----|-----|---------------------|-------|

| V <sub>DDA</sub>         | Analog supply voltage                                             | -                                                     |                          |     | -   | 3.6                 | V     |

| V <sub>IN</sub>          | Comparator<br>input voltage range                                 | -                                                     |                          |     | -   | V <sub>DDA</sub>    | V     |

| $V_{BG}$                 | V <sub>REFINT</sub> scaler<br>input voltage                       | -                                                     |                          |     | 1.2 | -                   | V     |

| $V_{SC}$                 | V <sub>REFINT</sub> scaler<br>offset voltage                      | -                                                     |                          | -   | ±5  | ±10                 | mV    |

| t <sub>s_sc</sub>        | Scaler startup time from power down                               | First V <sub>REFINT</sub> scaler activ<br>power o     |                          | -   | -   | 1000 <sup>(2)</sup> | ms    |

| -                        | nom power down                                                    | Next activa                                           | tions                    |     |     | 0.2                 |       |

| t <sub>START</sub>       | Comparator startup time                                           | Startup time to reach propagation delay specification |                          | -   | -   | 60                  | μs    |

|                          |                                                                   | Ultra-low power mode                                  |                          |     | 2   | 4.5                 | μs    |

|                          | Propagation delay for<br>200 mV step with 100 mV<br>overdrive     | Low power mode                                        |                          |     | 0.7 | 1.5                 |       |

|                          |                                                                   | Medium power mode                                     |                          |     | 0.3 | 0.6                 |       |

|                          |                                                                   | High speed mode                                       | $V_{DDA} \ge 2.7 V$      | -   | 50  | 100 n               | 20    |

| 4                        |                                                                   | riigh speed mode                                      | V <sub>DDA</sub> < 2.7 V | -   | 100 | 240                 | ns    |

| t <sub>D</sub>           |                                                                   | Ultra-low power mode                                  |                          |     | 2   | 7                   |       |

|                          | Propagation delay for full<br>range step with 100 mV<br>overdrive | Low power mode                                        |                          |     | 0.7 | 2.1                 | μs    |

|                          |                                                                   | Medium power mode                                     |                          |     | 0.3 | 1.2                 |       |

|                          |                                                                   | High speed mode                                       | $V_{DDA} \ge 2.7 V$      | -   | 90  | 180                 | ns    |

|                          |                                                                   | nigh speed mode                                       | V <sub>DDA</sub> < 2.7 V | -   | 110 | 300                 | 110   |

| V <sub>offset</sub>      | Comparator offset error                                           |                                                       |                          |     | ±4  | ±10                 | mV    |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                              | -                                                     |                          |     | 18  | -                   | μV/°C |

|                          |                                                                   | Ultra-low power mode                                  |                          |     | 1.2 | 1.5                 | -μA   |

|                          | COMP current                                                      | Low power mode                                        |                          |     | 3   | 5                   |       |

| I <sub>DD(COMP)</sub>    | consumption                                                       | Medium power mode                                     |                          |     | 10  | 15                  |       |

|                          |                                                                   | High speed mode                                       |                          |     | 75  | 100                 |       |

Table 64. Comparator characteristics

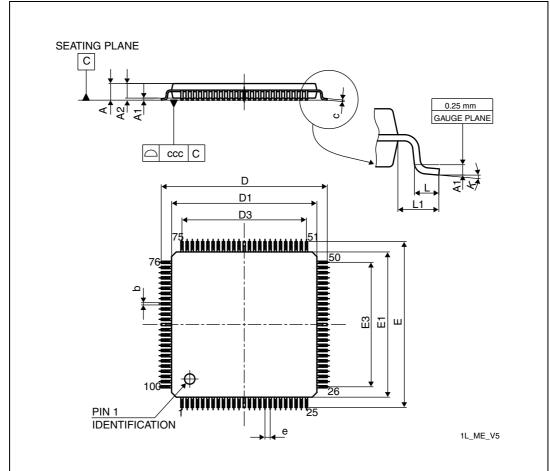

## 7.2 LQFP100 package information

Figure 35. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Cumhal |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol | Min    | Тур         | Мах    | Min                   | Тур    | Max    |  |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |  |

| k      | 0.0°   | 3.5°        | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |

| CCC    | -      | -           | 0.080  | -                     | -      | 0.0031 |  |

# Table 78. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat packagemechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

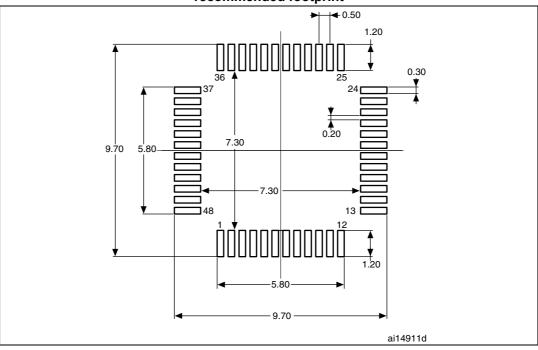

## Figure 42. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

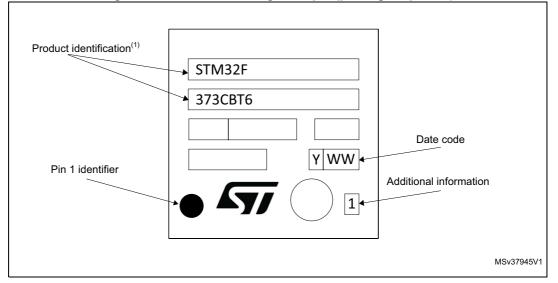

#### **Device marking for LQFP48**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 43. LQFP48 marking example (package top view)

Samples marked "ES" are to be considered as "Engineering Samples": i.e. they are intended to be sent to customer for electrical compatibility evaluation and may be used to start customer qualification where specifically authorized by ST in writing. In no event ST will be liable for any customer usage in production. Only if ST has authorized in writing the customer qualification Engineering Samples can be used for reliability qualification trials.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|