Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core Processor             | ARM® Cortex®-M4                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 3x16b; D/A 3x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f373cct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 44. LQFP64 P <sub>D</sub> max vs. T <sub>A</sub> | 129 |

|---------------------------------------------------------|-----|

|---------------------------------------------------------|-----|

# 3.12 12-bit analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter is based on a successive approximation register (SAR) architecture. It has up to 16 external channels (AIN15:0) and 3 internal channels (temperature sensor, voltage reference,  $V_{BAT}$  voltage measurement) performing conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the timers (TIMx) can be internally connected to the ADC start and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

## 3.12.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode. See *Table 65: Temperature sensor calibration values on page 105*.

# 3.12.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

# 3.12.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

# 3.13 **16-bit sigma delta analog-to-digital converters (SDADC)**

Three 16-bit sigma-delta analog-to-digital converters are embedded in the STM32F373xx. They have up to two separate supply voltages allowing the analog function voltage range to be independent from the STM32F373xx power supply. They share up to 21 input pins which may be configured in any combination of single-ended (up to 21) or differential inputs (up to 11).

The conversion speed is up to 16.6 ksps for each SDADC when converting multiple channels and up to 50 ksps per SDADC if single channel conversion is used. There are two conversion modes: single conversion mode or continuous mode, capable of automatically scanning any number of channels. The data can be automatically stored in a system RAM buffer, reducing the software overhead.

A timer triggering system can be used in order to control the start of conversion of the three SDADCs and/or the 12-bit fast ADC. This timing control is very flexible, capable of triggering simultaneous conversions or inserting a programmable delay between the ADCs.

Up to two external reference pins (VREFSD+, VREFSD-) and an internal 1.2/1.8 V reference can be used in conjunction with a programmable gain (x0.5 to x32) in order to fine-tune the input voltage range of the SDADC. VREFSD - pin is used as negative signal reference in case of single-ended input mode.

# 3.14 Digital-to-analog converter (DAC)

The devices feature two 12-bit buffered DACs with three output channels that can be used to convert three digital signals into three analog voltage signal outputs. The internal structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital Interface supports the following features:

- Two DAC converters with three output channels:

- DAC1 with two output channels

- DAC2 with one output channel.

- 8-bit or 10-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation (DAC1 only)

- Triangular wave generation (DAC1 only)

- Dual DAC channel independent or simultaneous conversions (DAC1 only)

- DMA capability for each channel

- External triggers for conversion

## 3.17.3 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

# 3.17.4 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB1 clock (PCLK1) derived from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.17.5 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source

# 3.18 Real-time clock (RTC) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either from  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are thirty two 32-bit registers used to store 128 bytes of user application data.

They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28th, 29th (leap year), 30th and 31st day of the month.

- 2 programmable alarms with wake up from Stop and Standby mode capability.

- Periodic wakeup unit with programmable resolution and period.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy.

- 3 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

| Table 11. STM32F373xx | pin definitions | (continued) |

|-----------------------|-----------------|-------------|

|-----------------------|-----------------|-------------|

| Pi      | n nun    | nber   | S      |                                       |             |               |     | Pin func                                                                                                            | <i>,</i>             |  |  |

|---------|----------|--------|--------|---------------------------------------|-------------|---------------|-----|---------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| LQFP100 | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | 9   |                                                                                                                     | Additional functions |  |  |

| 91      | C5       | 57     | 41     | PB5                                   | I/O         | FT            | -   | SPI1_MOSI/I2S1_SD,<br>SPI3_MOSI/I2S3_SD,<br>I2C1_SMBAI, USART2_CK,<br>TIM16_BKIN, TIM3_CH2,<br>TIM17_CH1, TIM19_ETR | -                    |  |  |

| 92      | В5       | 58     | 42     | PB6                                   | I/O         | FTf           | -   | I2C1_SCL, USART1_TX,<br>TIM16_CH1N, TIM3_CH3,<br>TIM4_CH1, TIM19_CH1,<br>TIM15_CH1, TSC_G5_IO3                      | -                    |  |  |

| 93      | B4       | 59     | 43     | PB7                                   | I/O         | FTf           | -   | I2C1_SDA, USART1_RX,<br>TIM17_CH1N, TIM3_CH4,<br>TIM4_CH2, TIM19_CH2,<br>TIM15_CH2, TSC_G5_IO4                      |                      |  |  |

| 94      | A4       | 60     | 44     | BOOT0                                 | Ι           | В             | -   | Boot memory                                                                                                         | selection            |  |  |

| 95      | A3       | 61     | 45     | PB8                                   | I/O         | FTf           | -   | SPI2_SCK/I2S2_CK,<br>I2C1_SCL, USART3_TX,<br>CAN_RX, CEC, TIM16_CH1,<br>TIM4_CH3, TIM19_CH3,<br>COMP1_OUT, TSC_SYNC | -                    |  |  |

| 96      | В3       | 62     | 46     | PB9                                   | I/O         | FTf           | -   | SPI2_NSS/I2S2_WS,<br>I2C1_SDA, USART3_RX,<br>CAN_TX, IR_OUT,<br>TIM17_CH1, TIM4_CH4,<br>TIM19_CH4, COMP2_OUT        |                      |  |  |

| 97      | C3       | -      | -      | PE0                                   | I/O         | FT            | (2) | USART1_TX, TIM4_ETR -                                                                                               |                      |  |  |

| 98      | A2       | -      | -      | PE1                                   | I/O         | FT            | (2) | USART1_RX                                                                                                           | -                    |  |  |

| 99      | D3       | 63     | 47     | VSS_1                                 | S           | -             | -   | Groui                                                                                                               | nd                   |  |  |

| 100     | C4       | 64     | 48     | VDD_1                                 | S           | -             | -   | Digital power supply                                                                                                |                      |  |  |

1.

PC13, PC14 and PC15 are supplied through the power switch. Since the switch sinks only a limited amount of current (3 mA), the use of GPIO PC13 to PC15 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF - These GPIOs must not be used as current sources (e.g. to drive an LED) After the first backup domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the Backup registers which is not reset by the main reset. For details on how to manage these GPIOs, refer to the Battery backup domain and BKP register description sections in the RM0313 reference manual.

2. When using the small packages (48 and 64 pin packages), the GPIO pins which are not present on these packages, must not be configured in analog mode.

3. these pins are powered by VDDSD12.

4. these pins are powered by VDDSD3.

The following relationship must be respected between V<sub>REFSD+</sub> and V<sub>DDSD12</sub>, V<sub>DDSD3</sub>: V<sub>REFSD+</sub> must be lower than V<sub>DDSD3</sub>.

Depending on the SDADCx operation mode, there can be more constraints between  $V_{REFSD+}$ ,  $V_{DDSD12}$  and  $V_{DDSD3}$  which are described in reference manual RM0313.

| Symbol                 | Ratings                                                                            | Max.  | Unit |

|------------------------|------------------------------------------------------------------------------------|-------|------|

| ΣI <sub>VDD</sub>      | Total current into sum of all VDD_x and VDDSDx power lines (source) <sup>(1)</sup> | 160   |      |

| ΣI <sub>VSS</sub>      | Total current out of sum of all VSS_x and VSSSD ground lines $({\rm sink})^{(1)}$  | -160  |      |

| I <sub>VDD(PIN)</sub>  | Maximum current into each VDD_x or VDDSDx power pin (source) <sup>(1)</sup>        | 100   |      |

| I <sub>VSS(PIN)</sub>  | Maximum current out of each VSS_x or VSSSD ground pin (sink) <sup>(1)</sup>        | -100  |      |

|                        | Output current sunk by any I/O and control pin                                     | 25    |      |

| I <sub>IO(PIN)</sub>   | Output current source by any I/O and control pin                                   | -25   | mA   |

| <b>N</b> I             | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>        | 80    |      |

| $\Sigma I_{IO(PIN)}$   | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup>     | -80   |      |

|                        | Injected current on FT, FTf and B pins <sup>(3)</sup>                              | -5/+0 |      |

| I <sub>INJ(PIN)</sub>  | Injected current on TC and RST pin <sup>(4)</sup>                                  | ± 5   |      |

|                        | Injected current on TTa pins <sup>(5)</sup>                                        | ± 5   |      |

| ΣI <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>            | ± 25  |      |

| Table 20. Current character | ristics |

|-----------------------------|---------|

|-----------------------------|---------|

VDDSD12 is the external power supply for the PB2, PB10, and PE7 to PE15 I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>). V<sub>DD</sub> (VDD\_x) is the external power supply for all remaining I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>).

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

- 3. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 19: Voltage characteristics* for the maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DDA</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ</sub>(PIN) must never be exceeded. Refer also to *Table 19: Voltage characteristics* for the maximum allowed input voltage values. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 62*.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

#### Table 21. Thermal characteristics

### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 10: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{APB1} = f_{AHB}/2$ ,  $f_{APB2} = f_{AHB}$

- When f<sub>HCLK</sub> > 8 MHz PLL is ON and PLL inputs is equal to HSI/2 = 4 MHz (if internal clock is used) or HSE = 8 MHz (if HSE bypass mode is used)

The parameters given in *Table 28* to *Table 34* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

|                 |                         | All peripherals enabled |                   |      |                                     | abled | All peripherals disabled |      |                                     |       |        |      |

|-----------------|-------------------------|-------------------------|-------------------|------|-------------------------------------|-------|--------------------------|------|-------------------------------------|-------|--------|------|

| Symbol          | Parameter               | Conditions              | f <sub>HCLK</sub> | _к _ | Max @ T <sub>A</sub> <sup>(2)</sup> |       |                          | Tun  | Max @ T <sub>A</sub> <sup>(2)</sup> |       |        | Unit |

|                 |                         |                         |                   | Тур  | 25 °C                               | 85 °C | 105 °C                   | Тур  | 25 °C                               | 85 °C | 105 °C |      |

|                 |                         |                         | 72 MHz            | 63.1 | 70.7                                | 71.5  | 73.4                     | 29.2 | 31.1                                | 31.7  | 34.2   |      |

|                 |                         | HSE                     | 64 MHz            | 56.3 | 63.3                                | 64.1  | 64.9                     | 26.1 | 27.8                                | 28.4  | 30.4   |      |

|                 |                         | bypass,                 | 48 MHz            | 42.5 | 48.5                                | 48.0  | 50.1                     | 19.9 | 22.6                                | 21.9  | 23.1   |      |

|                 |                         | PLL on                  | 32 MHz            | 28.8 | 31.4                                | 32.2  | 34.3                     | 13.1 | 16.1                                | 14.9  | 16.2   |      |

|                 | Supply                  |                         | 24 MHz            | 21.9 | 24.4                                | 24.4  | 25.8                     | 10.1 | 10.9                                | 11.9  | 12.4   |      |

|                 | current in              | HSE                     | 8 MHz             | 7.3  | 8.0                                 | 9.3   | 9.3                      | 3.7  | 4.1                                 | 4.4   | 5.0    |      |

| I <sub>DD</sub> | Run mode,<br>code       | bypass,<br>PLL off      | 1 MHz             | 1.1  | 1.5                                 | 1.8   | 2.3                      | 0.8  | 1.1                                 | 1.4   | 1.9    | mA   |

|                 | executing<br>from Flash |                         | 64 MHz            | 51.7 | 57.7                                | 58.0  | 60.4                     | 25.8 | 27.6                                | 28.1  | 30.1   |      |

|                 | HSI clock,<br>PLL on    | 48 MHz                  | 38.6              | 45.9 | 43.5                                | 46.9  | 19.8                     | 21.9 | 21.7                                | 22.8  |        |      |

|                 |                         | 32 MHz                  | 26.4              | 31.1 | 29.7                                | 31.9  | 13.1                     | 15.7 | 14.8                                | 16.2  |        |      |

|                 |                         | 24 MHz                  | 20.3              | 22.6 | 22.6                                | 23.7  | 6.9                      | 7.5  | 8.1                                 | 8.8   |        |      |

|                 |                         | HSI clock,<br>PLL off   | 8 MHz             | 7.0  | 7.6                                 | 8.8   | 8.8                      | 3.7  | 4.1                                 | 4.4   | 5.0    |      |

#### Table 28. Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6 V<sup>(1)</sup>

|                                 |                                   |                                                                         | • •     |                        | Тур                     |      |  |

|---------------------------------|-----------------------------------|-------------------------------------------------------------------------|---------|------------------------|-------------------------|------|--|

| Symbol                          | Parameter                         | Conditions                                                              | fhclk   | Peripherals<br>enabled | Peripherals<br>disabled | Unit |  |

|                                 |                                   |                                                                         | 72 MHz  | 42.8                   | 6.9                     |      |  |

| I <sub>DD</sub>                 |                                   | Running from HSE                                                        | 64 MHz  | 38.2                   | 6.2                     |      |  |

|                                 |                                   | crystal clock 8 MHz,<br>code executing                                  | 48 MHz  | 28.9                   | 4.8                     |      |  |

|                                 |                                   | from Flash or RAM,                                                      | 32 MHz  | 19.5                   | 3.4                     |      |  |

|                                 |                                   | PLL on                                                                  | 24 MHz  | 14.7                   | 2.7                     |      |  |

|                                 | Supply current in Sleep mode from |                                                                         | 16 MHz  | 10.2                   | 2.0                     | mA   |  |

|                                 | V <sub>DD</sub> supply            |                                                                         | 8 MHz   | 5.2                    | 1.2                     | ШA   |  |

|                                 |                                   | Running from HSE                                                        | 4 MHz   | 3.4                    | 1.1                     |      |  |

|                                 |                                   | crystal clock 8 MHz,<br>code executing<br>from Flash or RAM,<br>PLL off | 2 MHz   | 2.2                    | 0.9                     |      |  |

|                                 |                                   |                                                                         | 1 MHz   | 1.6                    | 0.9                     |      |  |

|                                 |                                   |                                                                         | 500 kHz | 1.4                    | 0.8                     |      |  |

|                                 |                                   |                                                                         | 125 kHz | 1.1                    | 0.8                     |      |  |

|                                 |                                   |                                                                         | 72 MHz  | 242.9                  | 241.5                   |      |  |

|                                 |                                   | Running from HSE                                                        | 64 MHz  | 213.7                  | 212.7                   |      |  |

|                                 |                                   | crystal clock 8 MHz,                                                    | 48 MHz  | 158.8                  | 158.0                   |      |  |

|                                 |                                   | code executing<br>from Flash or RAM,                                    | 32 MHz  | 107.6                  | 107.3                   |      |  |

|                                 |                                   | PLL on                                                                  | 24 MHz  | 82.7                   | 82.6                    |      |  |

| ı (1)                           | Supply current in Sleep mode from |                                                                         | 16 MHz  | 58.3                   | 58.2                    |      |  |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply           |                                                                         | 8 MHz   | 1.2                    | 1.2                     | μA   |  |

|                                 |                                   | Running from HSE                                                        | 4 MHz   | 1.2                    | 1.2                     |      |  |

|                                 |                                   | crystal clock 8 MHz,                                                    | 2 MHz   | 1.2                    | 1.2                     |      |  |

|                                 |                                   | code executing<br>from Flash or RAM,                                    | 1 MHz   | 1.2                    | 1.2                     |      |  |

|                                 |                                   | PLL off                                                                 | 500 kHz | 1.2                    | 1.2                     |      |  |

|                                 |                                   |                                                                         | 125 kHz | 1.2                    | 1.2                     |      |  |

1.  $V_{DDA}$  monitoring is off,  $V_{DDSD12}$  monitoring is off.

All timings are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 22*.

| Symbol                        | Parameter                   | Conditions                     |         | Мах     | Unit    |       |         |     |                        |

|-------------------------------|-----------------------------|--------------------------------|---------|---------|---------|-------|---------|-----|------------------------|

| Symbol                        | Farameter                   |                                | = 2.0 V | = 2.4 V | = 2.7 V | = 3 V | = 3.3 V | _   | Unit                   |

|                               | Wakoup from Stop            | Regulator in run mode          | 4.1     | 3.9     | 3.8     | 3.7   | 3.6     | 4.5 |                        |

| twustop Wakeup from Stop mode |                             | Regulator in low<br>power mode | 7.9     | 6.7     | 6.1     | 5.7   | 5.4     | 8.6 | μs                     |

| t <sub>WUSTANDB</sub><br>Y    | Wakeup from<br>Standby mode | LSI and IWDG off               | 62.6    | 53.7    | 49.2    | 45.7  | 42.7    | 100 |                        |

| t <sub>WUSLEEP</sub>          | Wakeup from Sleep<br>mode   | After WFE instruction          |         |         | 6       |       |         |     | CPU<br>clock<br>cycles |

| Table 37. L | Low-power mode wakeup timings |

|-------------|-------------------------------|

|-------------|-------------------------------|

## 6.3.7 External clock source characteristics

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 12*.

| Symbol                                       | Parameter <sup>(1)</sup>            | Conditions                  | Min          | Тур | Мах                 | Unit |  |  |  |

|----------------------------------------------|-------------------------------------|-----------------------------|--------------|-----|---------------------|------|--|--|--|

| f <sub>HSE_ext</sub>                         | User external clock source          | CSS is on or<br>PLL is used | 1            | 8   | 32                  | MHz  |  |  |  |

|                                              | frequency                           | CSS is off,<br>PLL not used | 0            | 0   | 52                  |      |  |  |  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage | -                           | $0.7 V_{DD}$ | -   | V <sub>DD</sub>     | v    |  |  |  |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  | -                           | $V_{SS}$     | -   | 0.3 V <sub>DD</sub> | v    |  |  |  |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             | -                           | 15           | -   | -                   | ns   |  |  |  |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            | -                           | -            | _   | 20                  | 115  |  |  |  |

| Table 38 | . High-speed | external | user clock | characteristics |

|----------|--------------|----------|------------|-----------------|

|----------|--------------|----------|------------|-----------------|

1. Guaranteed by design.

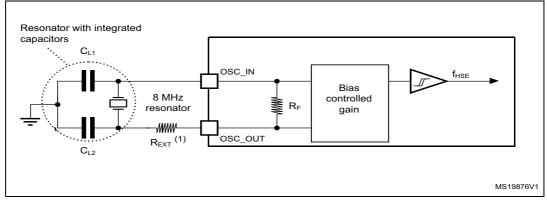

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 14*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1.  $R_{EXT}$  value depends on the crystal characteristics.

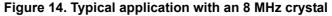

Figure 16. HSI oscillator accuracy characterization results

### Low-speed internal (LSI) RC oscillator

Table 43. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30  | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

1.  $V_{DDA}$  = 3.3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

### 6.3.9 PLL characteristics

The parameters given in *Table 44* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

| Symbol               | Parameter                      |                   | Unit |                    |     |

|----------------------|--------------------------------|-------------------|------|--------------------|-----|

|                      | Faidilleter                    | Min               | Тур  | Мах                |     |

| f <sub>PLL_IN</sub>  | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | -    | 24 <sup>(2)</sup>  | MHz |

|                      | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %   |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 72                 | MHz |

| t <sub>LOCK</sub>    | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs  |

| Jitter               | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps  |

1. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_{OUT}}$ .

2. Guaranteed by design.

DocID022691 Rev 7

## 6.3.14 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 52* are derived from tests performed under the conditions summarized in *Table 22*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                               | Conditions                                                                                       | Min                                        | Тур                | Мах                                      | Unit |  |

|------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|------------------------------------------|------|--|

|                  |                                                         | TC and TTa I/O                                                                                   | -                                          | -                  | 0.3V <sub>DD</sub> +0.07 <sup>(2)</sup>  |      |  |

|                  | Low level input                                         | FT and FTf I/O                                                                                   | -                                          | -                  | 0.475V <sub>DD</sub> -0.2 <sup>(2)</sup> |      |  |

| V <sub>IL</sub>  | voltage                                                 | BOOT0                                                                                            | -                                          | -                  | 0.3V <sub>DD</sub> -0.3 <sup>(2)</sup>   |      |  |

|                  |                                                         | All I/Os except BOOT0 pin                                                                        | -                                          | -                  | 0.3V <sub>DD</sub>                       | V    |  |

|                  |                                                         | TC and TTa I/O                                                                                   | 0.445V <sub>DD</sub> +0.398 <sup>(2)</sup> | -                  | -                                        | V    |  |

| V                | High level input                                        | FT and FTf I/O                                                                                   | 0.5V <sub>DD+0.2</sub> <sup>(2)</sup>      | -                  | -                                        |      |  |

| V <sub>IH</sub>  | voltage                                                 | BOOT0                                                                                            | 0.2V <sub>DD</sub> +0.95 <sup>(2)</sup>    | -                  | -                                        |      |  |

|                  |                                                         | All I/Os except BOOT0 pin                                                                        | 0.7V <sub>DD</sub>                         | -                  | -                                        |      |  |

|                  | Schmitt trigger<br>hysteresis                           | TC and TTa I/O                                                                                   | -                                          | 200 <sup>(2)</sup> | -                                        |      |  |

| V <sub>hys</sub> |                                                         |                                                                                                  |                                            |                    | -                                        | mV   |  |

|                  |                                                         | BOOTO                                                                                            |                                            | 300 <sup>(2)</sup> | -                                        |      |  |

|                  |                                                         | TC, FT and FTf I/O<br>TTa in digital mode<br>V <sub>SS</sub> < V <sub>IN</sub> < V <sub>DD</sub> | -                                          | -                  | ±0.1                                     |      |  |

| l <sub>lkg</sub> | Input leakage<br>current <sup>(3)</sup>                 | TTa in digital mode<br>V <sub>DD</sub> ≤ V <sub>IN</sub> ≤V <sub>DDA</sub>                       | -                                          | -                  | 1                                        | μA   |  |

|                  |                                                         | TTa in analog mode<br>V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DDA</sub>                         | -                                          | -                  | ±0.2                                     |      |  |

|                  |                                                         | FT and FTf I/O <sup>(3)</sup><br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V                           | -                                          | -                  | 10                                       |      |  |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent<br>resistor <sup>(4)</sup>   | V <sub>IN</sub> = V <sub>SS</sub>                                                                | 25                                         | 40                 | 55                                       | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent<br>resistor <sup>(4)</sup> | V <sub>IN</sub> = V <sub>DD</sub>                                                                | 25                                         | 40                 | 55                                       | K22  |  |

| C <sub>IO</sub>  | I/O pin capacitance                                     | -                                                                                                | -                                          | 5                  | -                                        | pF   |  |

| Table 52. I/O static characteri | stics <sup>(1)</sup> |

|---------------------------------|----------------------|

|---------------------------------|----------------------|

VDDSD12 is the external power supply for the PB2, PB10, and PE7 to PE15 I/O pins (the I/O pin ground is internally connected to VSS). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O pin ground is internally connected to VSS). For those pins all V<sub>DD</sub> supply references in this table are related to their given VDDSDx power supply.

2. Guaranteed by design.

3. Leakage could be higher than maximum value, if negative current is injected on adjacent pins.

4. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

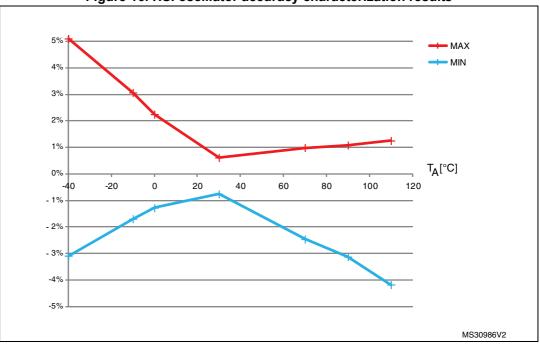

Figure 18. Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to ± 8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH})$ .

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on all VDD\_x and VDDSDx, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub> cannot exceed the absolute maximum rating SI<sub>VDD</sub> (see *Table 20*).

- The sum of the currents sunk by all the I/Os on all VSS\_x and VSSSD, plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating SI<sub>VSS</sub> (see *Table 20*).

| Symbol          | Parameter                                                              | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

1. Guaranteed by design.

- 2. Spikes width below  $t_{AF}(min)$  are filtered.

- 3. Spikes width above  $t_{AF}(max)$  are not filtered.

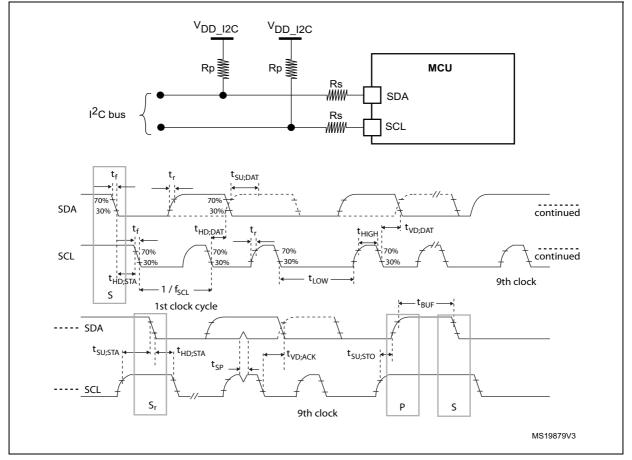

1. Legend: Rs: Series protection resistors. Rp: Pull-up resistors. V<sub>DD\_12C</sub>: I2C bus supply.

- ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for lawyour and Σlawyour in Section 6.3.14 does not

- Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.14 does not affect the ADC accuracy.

- 3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

- 4. Guaranteed by characterization results.

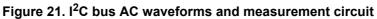

#### Figure 27. ADC accuracy characteristics

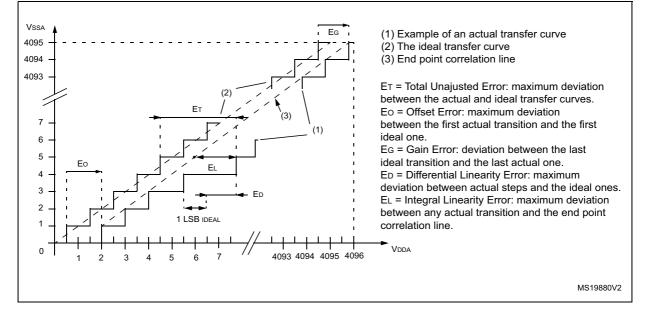

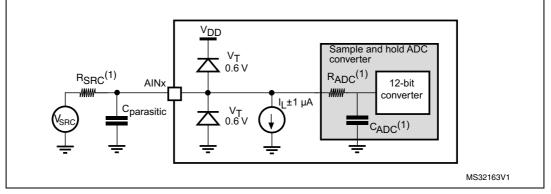

1. Refer to *Table 60* for the values of  $R_{SRC}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 9*. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

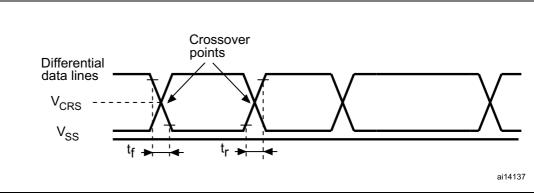

#### Figure 31. USB timings: definition of data signal rise and fall time

| Table 73. USB: Full-speed electrical characteristics <sup>(1)</sup> |                                 |                                |     |     |     |      |  |  |  |  |

|---------------------------------------------------------------------|---------------------------------|--------------------------------|-----|-----|-----|------|--|--|--|--|

| Symbol                                                              | Parameter                       | Conditions                     | Min | Тур | Max | Unit |  |  |  |  |

| Driver charac                                                       | teristics                       |                                |     |     |     |      |  |  |  |  |

| t <sub>r</sub>                                                      | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |  |  |  |

| t <sub>f</sub>                                                      | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |  |  |  |

| t <sub>rfm</sub>                                                    | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | -   | 110 | %    |  |  |  |  |

| V <sub>CRS</sub>                                                    | Output signal crossover voltage | -                              | 1.3 | -   | 2.0 | V    |  |  |  |  |

| Output driver<br>Impedance <sup>(3)</sup>                           | Z <sub>DRV</sub>                | driving high and<br>low        | 28  | 40  | 44  | Ω    |  |  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-), the matching impedance is already included in the embedded driver.

### 6.3.24 CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

### 6.3.25 SDADC characteristics

| Symbol                             | Parameter                   | Conditions                                | Min | Тур | Max                | Unit | Note |

|------------------------------------|-----------------------------|-------------------------------------------|-----|-----|--------------------|------|------|

| V <sub>DDSDx</sub> Power<br>supply | Power                       | Slow mode ( $f_{ADC}$ = 1.5 MHz)          | 2.2 | -   | $V_{DDA}$          | v    | -    |

|                                    | supply                      | Normal mode ( $f_{ADC} = 6 \text{ MHz}$ ) | 2.4 | -   | V <sub>DDA</sub>   | v    | -    |

| f <sub>ADC</sub>                   | SDADC<br>clock<br>frequency | Slow mode (f <sub>ADC</sub> = 1.5 MHz)    | 0.5 | 1.5 | 1.65               |      | -    |

|                                    |                             | Normal mode (f <sub>ADC</sub> = 6 MHz)    | 0.5 | 6   | 6.3                | MHz  | -    |

| V <sub>REFSD+</sub>                | Positive ref. voltage       | -                                         | 1.1 | -   | V <sub>DDSDx</sub> | V    | -    |

### Table 74. SDADC characteristics <sup>(1)</sup>

| Symbol             | Parameter             |                   |            | Con                           | ditions                     |                                              | Min        | Тур                          | Max  | Unit | Note |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|--------------------|-----------------------|-------------------|------------|-------------------------------|-----------------------------|----------------------------------------------|------------|------------------------------|------|------|------|------|-------|------|------------------------------|------|------|----------|--------------------|--|---------------------------------------------|----|----|---|--|--|

|                    |                       |                   |            | f <sub>ADC</sub> =<br>1.5 MHz |                             | $V_{\text{REFSD}^+} = 3.3^{(3)}$             | 84         | 85                           | -    |      |      |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|                    |                       | a)                | gain = 1   | f <sub>ADC</sub> =            |                             | V <sub>REFSD+</sub><br>= 1.2 <sup>(4)</sup>  | 86         | 88                           | -    |      |      |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|                    |                       | Differential mode | 0,         | 6 MHz                         |                             | V <sub>REFSD+</sub><br>= 3.3                 | 88         | 92                           | -    |      |      |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|                    |                       | ifferent          |            | f <sub>ADC</sub> =            |                             | V <sub>REFSD+</sub><br>= 1.2 <sup>(4)</sup>  | 76         | 78                           | -    |      |      |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|                    | Signal to noise ratio | Δ                 | gain =     | f <sub>ADC</sub> =<br>6 MHz   |                             | V <sub>REFSD+</sub><br>= 3.3                 | 82         | 86                           | -    |      | -    |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

| SNR <sup>(5)</sup> |                       |                   |            | f <sub>ADC</sub> =<br>1.5 MHz | V <sub>DDSDx</sub><br>= 3.3 | $V_{\text{REFSD}^+}$<br>= 3.3 <sup>(3)</sup> | 76         | 80                           | -    | dB   |      |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|                    |                       | Single ended mode |            | f <sub>ADC</sub> =<br>1.5 MHz |                             | V <sub>REFSD+</sub><br>= 3.3                 | 80         | 84                           | -    |      |      |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|                    |                       |                   | ended mode | ended mode                    | ended mode                  | ended mode                                   | ended mode | ended mode                   | mode | mode | mode | mode | mode  | mode | mode                         | mode | mode | gain = 1 | f <sub>ADC</sub> = |  | V <sub>REFSD+</sub><br>= 1.2 <sup>(4)</sup> | 77 | 81 | - |  |  |

|                    |                       |                   |            |                               |                             |                                              |            |                              | 0    | 0,   | 0,   |      | 6 MHz |      | V <sub>REFSD+</sub><br>= 3.3 | 85   | 90   | -        |                    |  |                                             |    |    |   |  |  |

|                    |                       |                   | = 8        | f <sub>ADC</sub> =            |                             | V <sub>REFSD+</sub><br>= 1.2 <sup>(4)</sup>  | 66         | 71                           | -    |      |      |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

|                    |                       |                   |            |                               | gain =                      | 6 MHz                                        |            | V <sub>REFSD+</sub><br>= 3.3 | 74   | 78   | -    |      |       |      |                              |      |      |          |                    |  |                                             |    |    |   |  |  |

Table 74. SDADC characteristics (continued)<sup>(1)</sup>

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| ССС    | -           | -     | 0.080 | -                     | -      | 0.0031 |

| Table 80. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 7.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 22: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J max = T_A max + (P_D max x Q_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Q<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \mathsf{S} \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \mathsf{S}((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                         | Value | Unit |

|-----------------|-----------------------------------------------------------------------------------|-------|------|

| Θ <sub>JA</sub> | <b>Thermal resistance junction-ambient</b><br>LQFP64 - 10 × 10 mm / 0.5 mm pitch  | 45    | °C/W |

|                 | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm                   | 55    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 46    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>UFBGA100 - 7 x 7 mm                 | 59    |      |

#### Table 81. Package thermal characteristics

#### 7.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

| Date                | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>21-Dec-2012 |          | Updated Table 2: Device overview, capacitive sensing<br>channels peripheral added.     Updated Table 3: Capacitive sensing GPIOs available on<br>STM32F373xx devices     Updated Section 3.19: Inter-integrated circuit interface (I2C)     Updated the function names in Table 11: STM32F373 pin<br>definitions     Updated Table 20: Current characteristics     Updated Table 30: Typical and maximum VDD consumption<br>in Stop and Standby modes     Updated Table 32: Typical and maximum current consumption<br>from VBAT supply     Added Figure 11: Typical VBAT current consumption (LSE<br>and RTC ON/LSEDRV[1:0]='00')     Updated Table 33: Typical current consumption in Run mode,<br>code with data processing running from Flash and Table 34:<br>Typical current consumption in Sleep mode, code running<br>from Flash or RAM     Added Table 36: Peripheral current consumption, Figure 16:<br>HSI oscillator accuracy characterization results     Updated Table 37: Low-power mode wakeup timings     Updated Table 51: I/O current injection susceptibility     Updated Table 52: I/O static characteristics     Updated Table 52: UO static characteristics     Updated Table 53: Output voltage characteristics     Updated Table 55: NRST pin characteristics     Updated Table 55: NAC port and Figure 20: Five volt tolerant<br>(FT and FTf) I/O input characteri |

|                     |          | profile quad flat package outline, Figure 35: LQFP64 – 10 x<br>10 mm 64 pin low-profile quad flat package outline and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 83. Document revision history (continued)