# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 3x16b; D/A 3x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f373v8t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | 6.3.7     | External clock source characteristics       | 72  |

|--------|-----------|---------------------------------------------|-----|

|        | 6.3.8     | Internal clock source characteristics       |     |

|        | 6.3.9     | PLL characteristics                         | 78  |

|        | 6.3.10    | Memory characteristics                      | 79  |

|        | 6.3.11    | EMC characteristics                         | 80  |

|        | 6.3.12    | Electrical sensitivity characteristics      | 81  |

|        | 6.3.13    | I/O current injection characteristics       | 82  |

|        | 6.3.14    | I/O port characteristics                    | 84  |

|        | 6.3.15    | NRST characteristics                        | 89  |

|        | 6.3.16    | Communications interfaces                   | 91  |

|        | 6.3.17    | 12-bit ADC characteristics                  |     |

|        | 6.3.18    | DAC electrical specifications               | 101 |

|        | 6.3.19    | Comparator characteristics                  | 103 |

|        | 6.3.20    | Temperature sensor characteristics          | 105 |

|        | 6.3.21    | V <sub>BAT</sub> monitoring characteristics | 105 |

|        | 6.3.22    | Timer characteristics                       | 105 |

|        | 6.3.23    | USB characteristics                         | 107 |

|        | 6.3.24    | CAN (controller area network) interface     | 108 |

|        | 6.3.25    | SDADC characteristics                       | 108 |

| Pacl   | kage inf  | ormation                                    |     |

| 7.1    | UFBG      | A100 package information                    |     |

| 7.2    | LQFP1     | 100 package information                     |     |

| 7.3    | LQFP6     | 64 package information                      |     |

| 7.4    | LQFP4     | 18 package information                      |     |

| 7.5    | Therm     | al characteristics                          |     |

|        | 7.5.1     | Reference document                          |     |

|        | 7.5.2     | Selecting the product temperature range     |     |

| Part   | numbe     | ring                                        | 130 |

| Rovi   | ision his | story                                       | 121 |

| 110 41 |           |                                             |     |

7

8

9

Do not reconfigure GPIO pins which are not present on 48 and 64 pin packages to the analog mode. Additional current consumption in the range of tens of  $\mu$ A per pin can be observed if V<sub>DDA</sub> is higher than V<sub>DDIO</sub>.

## 3.10 Direct memory access (DMA)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The two DMAs can be used with the main peripherals: SPIs, I2Cs, USARTs, DACs, ADC, SDADCs, general-purpose timers.

## 3.11 Interrupts and events

#### 3.11.1 Nested vectored interrupt controller (NVIC)

The STM32F373xx devices embed a nested vectored interrupt controller (NVIC) able to handle up to 60 maskable interrupt channels and 16 priority levels.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

#### 3.11.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 29 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 84 GPIOs can be connected to the 16 external interrupt lines.

#### 3.17.1 General-purpose timers (TIM2 to TIM5, TIM12 to TIM17, TIM19)

There are eleven synchronizable general-purpose timers embedded in the STM32F373xx (see *Table 5* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

• TIM2, 3, 4, 5 and 19

These five timers are full-featured general-purpose timers:

- TIM2 and TIM5 have 32-bit auto-reload up/downcounters and 32-bit prescalers

- TIM3, 4, and 19 have 16-bit auto-reload up/downcounters and 16-bit prescalers

These timers all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. They can work together, or with the other generalpurpose timers via the Timer Link feature for synchronization or event chaining. The counters can be frozen in debug mode.

All have independent DMA request generation and support quadrature encoders.

• TIM12, 13, 14, 15, 16, 17

These six timers general-purpose timers with mid-range features:

They have 16-bit auto-reload upcounters and 16-bit prescalers.

- TIM12 has 2 channels

- TIM13 and TIM14 have 1 channel

- TIM15 has 2 channels and 1 complementary channel

- TIM16 and TIM17 have 1 channel and 1 complementary channel

All channels can be used for input capture/output compare, PWM or one-pulse mode output.

The timers can work together via the Timer Link feature for synchronization or event chaining. The timers have independent DMA request generation.

The counters can be frozen in debug mode.

#### **3.17.2 Basic timers (TIM6, TIM7, TIM18)**

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

| Na               | me                   | Abbreviation                                                     | Definition                                                                                            |  |  |  |  |

|------------------|----------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin r            | name                 |                                                                  | e specified in brackets below the pin name, the pin function reset is the same as the actual pin name |  |  |  |  |

|                  |                      | S                                                                | Supply pin                                                                                            |  |  |  |  |

| Pin              | type                 | I                                                                | Input only pin                                                                                        |  |  |  |  |

|                  |                      | I/O                                                              | Input / output pin                                                                                    |  |  |  |  |

|                  |                      | FT                                                               | 5 V tolerant I/O                                                                                      |  |  |  |  |

|                  |                      | FTf 5 V tolerant I/O, FM+ capable                                |                                                                                                       |  |  |  |  |

| I/O atr          | ucture               | TTa 3.3 V tolerant I/O directly connected to ADC                 |                                                                                                       |  |  |  |  |

| i/O su           | ucluie               | TC                                                               | TC Standard 3.3 V I/O                                                                                 |  |  |  |  |

|                  |                      | B Dedicated BOOT0 pin                                            |                                                                                                       |  |  |  |  |

|                  |                      | RST                                                              | Bidirectional reset pin with embedded weak pull-up resistor                                           |  |  |  |  |

| No               | tes                  | Unless otherwis<br>and after reset                               | e specified by a note, all I/Os are set as floating inputs during                                     |  |  |  |  |

| D.               | Alternate functions  | Functions selected through GPIOx_AFR registers                   |                                                                                                       |  |  |  |  |

| Pin<br>functions | Additional functions | Functions directly selected/enabled through peripheral registers |                                                                                                       |  |  |  |  |

| Table 10. Legend/abbreviations used in the | pinout table |

|--------------------------------------------|--------------|

#### Table 11. STM32F373xx pin definitions

| Pi      | n nun    | nber   | s      |                                       |             |               |       | Pin func             | tions                                                     |

|---------|----------|--------|--------|---------------------------------------|-------------|---------------|-------|----------------------|-----------------------------------------------------------|

| LQFP100 | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function   | Additional functions                                      |

| 1       | B2       | -      | -      | PE2                                   | I/O         | FT            | (2)   | TSC_G7_IO1, TRACECLK | -                                                         |

| 2       | A1       | -      | -      | PE3                                   | I/O         | FT            | (2)   | TSC_G7_IO2, TRACED0  | -                                                         |

| 3       | B1       | -      | -      | PE4                                   | I/O         | FT            | (2)   | TSC_G7_IO3, TRACED1  | -                                                         |

| 4       | C2       | -      | -      | PE5                                   | I/O         | FT            | (2)   | TSC_G7_IO4, TRACED2  | -                                                         |

| 5       | D2       | -      | -      | PE6                                   | I/O         | FT            | (2)   | TRACED3              | WKUP3, RTC_TAMPER3                                        |

| 6       | E2       | 1      | 1      | VBAT                                  | S           | -             | -     | Backup pow           | er supply                                                 |

| 7       | C1       | 2      | 2      | PC13 <sup>(1)</sup>                   | I/O         | тс            | -     | -                    | WKUP2, ALARM_OUT,<br>CALIB_OUT, TIMESTAMP,<br>RTC_TAMPER1 |

DocID022691 Rev 7

|         | Table 11. STM32F373xx pin definitions (continued) |        |        |                                       |             |               |            |                                                                                     |                               |  |

|---------|---------------------------------------------------|--------|--------|---------------------------------------|-------------|---------------|------------|-------------------------------------------------------------------------------------|-------------------------------|--|

| Pi      | in nun                                            | nber   | s      |                                       |             |               |            | Pin func                                                                            | tions                         |  |

| LQFP100 | UFBGA100                                          | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate function                                                                  | Additional functions          |  |

| 51      | L12                                               | -      | -      | VDDSD3                                | S           | -             | (2)        | SDADC3 pov                                                                          | ver supply                    |  |

| 52      | K12                                               | 33     | 25     | VREFSD+                               | S           | -             | -          | External reference voltage for S<br>(positive                                       |                               |  |

| 53      | K11                                               | 34     | 26     | PB14                                  | I/O         | тс            | (4)        | SPI2_MISO/I2S2_MCK,<br>USART3_RTS, TIM15_CH1,<br>TIM12_CH1, TSC_G6_IO1              | SDADC3_AIN8P                  |  |

| 54      | K10                                               | 35     | 27     | PB15                                  | I/O         | тс            | (4)        | SPI2_MOSI/I2S2_SD,<br>TIM15_CH1N, TIM15_CH2,<br>TIM12_CH2, TSC_G6_IO2,<br>RTC_REFIN | SDADC3_AIN7P,<br>SDADC3_AIN8M |  |

| 55      | K9                                                | 36     | 28     | PD8                                   | I/O         | тс            | (4)        | SPI2_SCK/I2S2_CK,<br>USART3_TX, TSC_G6_IO3                                          | SDADC3_AIN6P                  |  |

| 56      | K8                                                | -      | -      | PD9                                   | I/O         | тс            | (4)<br>(2) | USART3_RX, TSC_G6_IO4                                                               | SDADC3_AIN5P,<br>SDADC3_AIN6M |  |

| 57      | J12                                               | -      | -      | PD10                                  | I/O         | тс            | (4)<br>(2) | USART3_CK                                                                           | SDADC3_AIN4P                  |  |

| 58      | J11                                               | -      | -      | PD11                                  | I/O         | тс            | (4)<br>(2) | USART3_CTS                                                                          | SDADC3_AIN3P,<br>SDADC3_AIN4M |  |

| 59      | J10                                               | -      | -      | PD12                                  | I/O         | тс            | (4)<br>(2) | USART3_RTS, TIM4_CH1,<br>TSC_G8_IO1                                                 | SDADC3_AIN2P                  |  |

| 60      | H12                                               | -      | -      | PD13                                  | I/O         | тс            | (4)<br>(2) | TIM4_CH2, TSC_G8_IO2                                                                | SDADC3_AIN1P,<br>SDADC3_AIN2M |  |

| 61      | H11                                               | -      | -      | PD14                                  | I/O         | тс            | (4)<br>(2) | TIM4_CH3, TSC_G8_IO3                                                                | SDADC3_AIN0P                  |  |

| 62      | H10                                               | -      | -      | PD15                                  | I/O         | тс            | (4)<br>(2) | TIM4_CH4, TSC_G8_IO4                                                                | SDADC3_AIN0M                  |  |

| 63      | E12                                               | 37     | -      | PC6                                   | I/O         | FT            | (2)        | TIM3_CH1,<br>SPI1_NSS/I2S1_WS                                                       | -                             |  |

|         |                                                   |        |        |                                       |             |               |            |                                                                                     |                               |  |

38

-

-

-

PC7

PC8

PC9

E11

E10 39

D12 40

64

65

66

TIM3\_CH2,

SPI1\_SCK/I2S1\_CK,

SPI1\_MISO/I2S1\_MCK, TIM3\_CH3

SPI1\_MOSI/I2S1\_SD, TIM3\_CH4

(2)

(2)

(2)

FΤ

FΤ

FT

I/O

I/O

I/O

-

-

-

| Table 11. STM32F373xx | pin definitions | (continued) |

|-----------------------|-----------------|-------------|

|-----------------------|-----------------|-------------|

| Pi      | in nun   | nber   | S      |                                       |             |               |       | Pin func                                                                                                   | -                    |

|---------|----------|--------|--------|---------------------------------------|-------------|---------------|-------|------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP100 | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function                                                                                         | Additional functions |

| 67      | D11      | 41     | 29     | PA8                                   | I/O         | FT            | -     | SPI2_SCK/I2S2_CK,<br>I2C2_SMBA, USART1_CK,<br>TIM4_ETR, TIM5_CH1_ETR,<br>MCO                               | -                    |

| 68      | D10      | 42     | 30     | PA9                                   | I/O         | FTf           | -     | SPI2_MISO/I2S2_MCK,<br>I2C2_SCL, USART1_TX,<br>TIM2_CH3, TIM15_BKIN,<br>TIM13_CH1, TSC_G4_IO1              | -                    |

| 69      | C12      | 43     | 31     | PA10                                  | I/O         | FTf           | -     | SPI2_MOSI/I2S2_SD,<br>I2C2_SDA, USART1_RX,<br>TIM2_CH4, TIM17_BKIN,<br>TIM14_CH1, TSC_G4_IO2               | -                    |

| 70      | B12      | 44     | 32     | PA11                                  | I/O         | FT            | -     | SPI2_NSS/I2S2_WS,<br>SPI1_NSS/I2S1_WS,<br>USART1_CTS, CAN_RX,<br>TIM4_CH1, USB_DM,<br>TIM5_CH2, COMP1_OUT  | -                    |

| 71      | A12      | 45     | 33     | PA12                                  | I/O         | FT            | -     | SPI1_SCK/I2S1_CK,<br>USART1_RTS, CAN_TX,<br>USB_DP, TIM16_CH1,<br>TIM4_CH2, TIM5_CH3,<br>COMP2_OUT         | -                    |

| 72      | A11      | 46     | 34     | PA13                                  | I/O         | FT            | -     | SPI1_MISO/I2S1_MCK,<br>USART3_CTS, IR_OUT,<br>TIM16_CH1N, TIM4_CH3,<br>TIM5_CH4, TSC_G4_IO3,<br>SWDIO-JTMS | -                    |

| 73      | C11      | 47     | 35     | PF6                                   | I/O         | FTf           | -     | SPI1_MOSI/I2S1_SD,<br>USART3_RTS, TIM4_CH4,<br>I2C2_SCL                                                    | -                    |

| 74      | F11      | -      | -      | VSS_3                                 | S           | -             | (2)   | Grou                                                                                                       | nd                   |

| 75      | G11      | -      | -      | VDD_3                                 | S           | -             | (2)   | Digital powe                                                                                               | er supply            |

| -       | -        | 48     | 36     | PF7                                   | I/O         | FTf           | -     | I2C2_SDA, USART2_CK                                                                                        | -                    |

| 76      | A10      | 49     | 37     | PA14                                  | I/O         | FTf           | -     | I2C1_SDA, TIM12_CH1,<br>TSC_G4_IO4, SWCLK-JTCK                                                             | -                    |

41/137

5

|             | Table 12. Alternate functions for port PA |                      |                      |                |               |                        |                        |            |               |                |               |               |      |              |

|-------------|-------------------------------------------|----------------------|----------------------|----------------|---------------|------------------------|------------------------|------------|---------------|----------------|---------------|---------------|------|--------------|

| Pin<br>Name | AF0                                       | AF1                  | AF2                  | AF3            | AF4           | AF5                    | AF6                    | AF7        | AF8           | AF9            | AF10          | AF11          | AF14 | AF15         |

| PA0         | -                                         | TIM2_<br>CH1_<br>ETR | TIM5_<br>CH1_<br>ETR | TSC_<br>G1_IO1 | -             | -                      | -                      | USART2_CTS | COMP1<br>_OUT | -              | -             | TIM19<br>_CH1 | -    | EVENT<br>OUT |

| PA1         | RTC_<br>REFIN                             | TIM2_<br>CH2         | TIM5_<br>CH2         | TSC_<br>G1_IO2 | -             | -                      | SPI3_SCK/<br>I2S3_CK   | USART2_RTS | -             | TIM15_<br>CH1N | -             | TIM19<br>_CH2 | -    | EVENT<br>OUT |

| PA2         | -                                         | TIM2_<br>CH3         | TIM5_<br>CH3         | TSC_<br>G1_IO3 | -             | -                      | SPI3_MISO/<br>I2S3_MCK | USART2_TX  | COMP2<br>_OUT | TIM15_<br>CH1  | -             | TIM19<br>_CH3 | -    | EVENT<br>OUT |

| PA3         | -                                         | TIM2_<br>CH4         | TIM5_<br>CH4         | TSC_<br>G1_IO4 | -             | -                      | SPI3_MOSI<br>/I2S3_SD  | USART2_RX  | -             | TIM15_<br>CH2  | -             | TIM19<br>_CH4 | -    | EVENT<br>OUT |

| PA4         | -                                         | -                    | TIM3_<br>CH2         | TSC_<br>G2_IO1 | -             | SPI1_NSS/<br>I2S1_WS   | SPI3_NSS/<br>I2S3_WS   | USART2_CK  | -             | -              | TIM12<br>_CH1 | -             | -    | EVENT<br>OUT |

| PA5         | -                                         | TIM2_<br>CH1_<br>ETR | -                    | TSC_<br>G2_IO2 | -             | SPI1_SCK/<br>I2S1_CK   | -                      | CEC        | -             | TIM14_<br>CH1  | TIM12<br>_CH2 | -             | -    | EVENT<br>OUT |

| PA6         | -                                         | TIM16_<br>CH1        | TIM3_<br>CH1         | TSC_<br>G2_IO3 | -             | SPI1_MISO<br>/I2S1_MCK | -                      | -          | COMP1<br>_OUT | TIM13_<br>CH1  | -             | -             | -    | EVENT<br>OUT |

| PA7         | -                                         | TIM17_<br>CH1        | TIM3_<br>CH2         | TSC_<br>G2_IO4 | -             | SPI1_MOSI<br>/I2S1_SD  | -                      | -          | COMP2<br>_OUT | TIM14_<br>CH1  | -             | -             | -    | EVENT<br>OUT |

| PA8         | мсо                                       | -                    | TIM5_<br>CH1_<br>ETR | -              | I2C2_<br>SMBA | SPI2_SCK/<br>I2S2_CK   | -                      | USART1_CK  | -             | -              | TIM4_<br>ETR  | -             | -    | EVENT<br>OUT |

| PA9         | -                                         | -                    | TIM13<br>_CH1        | TSC_<br>G4_IO1 | I2C2_<br>SCL  | SPI2_MISO<br>/I2S2_MCK | -                      | USART1_TX  | -             | TIM15_<br>BKIN | TIM2_<br>CH3  | -             | -    | EVENT<br>OUT |

| PA10        | -                                         | TIM17_<br>BKIN       | -                    | TSC_<br>G4_IO2 | I2C2_<br>SDA  | SPI2_MOSI<br>/I2S2_SD  | -                      | USART1_RX  | -             | TIM14_<br>CH1  | TIM2_<br>CH4  | -             | -    | EVENT<br>OUT |

| PA11        | -                                         | -                    | TIM5_<br>CH2         | -              | -             | SPI2_NSS/<br>I2S2_WS   | SPI1_NSS/<br>I2S1_WS   | USART1_CTS | COMP1<br>_OUT | CAN_<br>RX     | TIM4_<br>CH1  | -             | -    | EVENT<br>OUT |

| PA12        | -                                         | TIM16_<br>CH1        | TIM5_<br>CH3         | -              | -             | -                      | SPI1_SCK/<br>I2S1_CK   | USART1_RTS | COMP2<br>_OUT | CAN_TX         | TIM4_<br>CH2  | -             | -    | EVENT<br>OUT |

STM32F373xx

## 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = V_{DDSDx} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC and SDADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

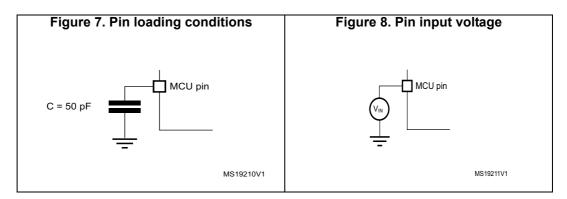

The loading conditions used for pin parameter measurement are shown in Figure 7.

#### 6.1.5 Pin input voltage

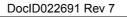

The input voltage measurement on a pin of the device is described in Figure 8.

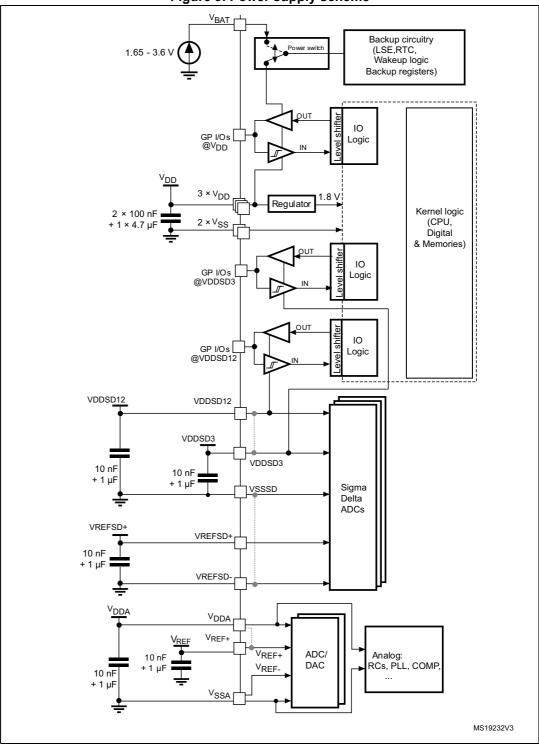

### 6.1.6 Power supply scheme

Figure 9. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

| Peripheral                 | Typical consumption (continued) | Unit   |

|----------------------------|---------------------------------|--------|

| APB1                       | peripherals                     |        |

| APB1-Bridge <sup>(3)</sup> | 6.9                             | _      |

| TIM2                       | 47.9                            |        |

| TIM3                       | 36.8                            |        |

| TIM4                       | 36.9                            |        |

| TIM5                       | 45.5                            |        |

| TIM6                       | 8.4                             |        |

| TIM7                       | 8.2                             |        |

| TIM12                      | 21.3                            |        |

| TIM13                      | 14.2                            |        |

| TIM14                      | 14.4                            |        |

| TIM18                      | 10.1                            |        |

| WWDG                       | 4.7                             | µA/MHz |

| SPI2                       | 24.3                            |        |

| SPI3                       | 25.3                            |        |

| USART2                     | 45.3                            |        |

| USART3                     | 43.1                            |        |

| I2C1                       | 14.0                            |        |

| I2C2                       | 13.9                            |        |

| USB                        | 27.9                            |        |

| CAN                        | 38.1                            |        |

| DAC2                       | 7.7                             |        |

| PWR                        | 5.4                             |        |

| DAC1                       | 14.8                            |        |

| CEC                        | 5.4                             |        |

Table 36. Peripheral current consumption (continued)

1. When peripherals are enabled, power consumption of the analog part of peripherals such as ADC, DACs, Comparators, etc. is not included. Refer to those peripherals characteristics in the subsequent sections.

2. The BusMatrix is automatically active when at least one master is ON (CPU, DMA1 or DMA2).

3. The APBx Bridge is automatically active when at least one peripheral is ON on the same Bus.

## 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 37* are measured from the wakeup event trigger to the first instruction executed by the CPU. The clock source used to wake up the device depends from the current operating mode:

- Stop or sleep mode: the wakeup event is WFE.

- The WKUP1 (PA0) pin is used to wakeup from standby, stop and sleep modes.

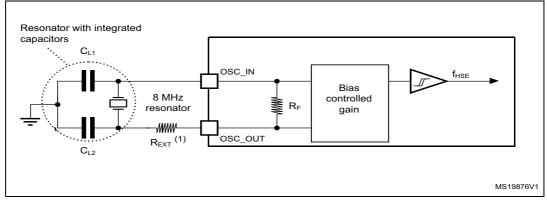

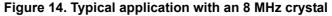

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 14*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1.  $R_{EXT}$  value depends on the crystal characteristics.

### 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 60* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 22*.

*Note:* It is recommended to perform a calibration after each power-up.

| Symbol                               | Parameter                                 | Conditions                                            | Min                                                         | Тур                | Max                | Unit               |

|--------------------------------------|-------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|

| V <sub>DDA</sub>                     | Power supply                              | -                                                     | 2.4                                                         | -                  | 3.6                | V                  |

| V <sub>REF+</sub>                    | Positive reference voltage                | -                                                     | 2.4                                                         | -                  | V <sub>DDA</sub>   | V                  |

| V <sub>REF-</sub>                    | Negative reference voltage                | -                                                     | 0                                                           | -                  | -                  | V                  |

| I <sub>DDA(ADC)</sub> <sup>(1)</sup> | Current consumption from V <sub>DDA</sub> | $V_{DD} = V_{DDA} = 3.3 V$                            | -                                                           | 0.9                | -                  | mA                 |

| I <sub>VREF</sub>                    | Current on the V <sub>REF</sub> input pin | -                                                     | -                                                           | 160 <sup>(2)</sup> | 220 <sup>(2)</sup> | μA                 |

| f <sub>ADC</sub>                     | ADC clock frequency                       | -                                                     | 0.6                                                         | -                  | 14                 | MHz                |

| f <sub>S</sub> <sup>(3)</sup>        | Sampling rate                             | -                                                     | 0.05                                                        | -                  | 1                  | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>     | External trigger frequency                | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 823                | kHz                |

| 'TRIG` '                             |                                           | -                                                     | -                                                           | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                     | Conversion voltage range                  | -                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -                  | V <sub>REF+</sub>  | V                  |

| R <sub>SRC</sub> <sup>(3)</sup>      | Signal source impedance                   | See <i>Equation 1</i> and <i>Table 61</i> for details |                                                             |                    | 50                 | kΩ                 |

| R <sub>ADC</sub> <sup>(3)</sup>      | Sampling switch resistance                | -                                                     | -                                                           | -                  | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>      | Internal sample and hold capacitor        | -                                                     | -                                                           | -                  | 8                  | pF                 |

| + (3)                                | Colibration time                          | f <sub>ADC</sub> = 14 MHz                             | 5.9                                                         | 9                  | L                  | μs                 |

| t <sub>CAL</sub> <sup>(3)</sup>      | Calibration time                          | -                                                     | 83                                                          |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> <sup>(3)</sup>      | Injection trigger conversion              | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 0.214              | μs                 |

| <sup>4</sup> at` ´                   | latency                                   | -                                                     | -                                                           | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> <sup>(3)</sup>     | Regular trigger conversion                | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 0.143              | μs                 |

| 'latr` '                             | latency                                   | -                                                     | -                                                           | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(3)</sup>                    | Sampling time                             | f <sub>ADC</sub> = 14 MHz                             | 0.107                                                       | -                  | 17.1               | μs                 |

| Ū                                    |                                           | -                                                     | 1.5                                                         | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(3)</sup>     | Power-up time                             | -                                                     | -                                                           | -                  | 1                  | μs                 |

|                                      | Total conversion time (including          | f <sub>ADC</sub> = 14 MHz                             | 1                                                           | -                  | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(3)</sup>     | sampling time)                            | -                                                     | 14 to 252 (t <sub>S</sub> for sa<br>successive approx       |                    |                    | 1/f <sub>ADC</sub> |

| Table | 60  | ADC | characteristics |

|-------|-----|-----|-----------------|

| Iable | 00. | ADC |                 |

During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100 μA on I<sub>DDA</sub> and 60 μA on I<sub>DD</sub> is present

2. Guaranteed by characterization results.

3. Guaranteed by design.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 60

- ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for lawyour and Σlawyour in Section 6.3.14 does not

- Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.14 does not affect the ADC accuracy.

- 3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

- 4. Guaranteed by characterization results.

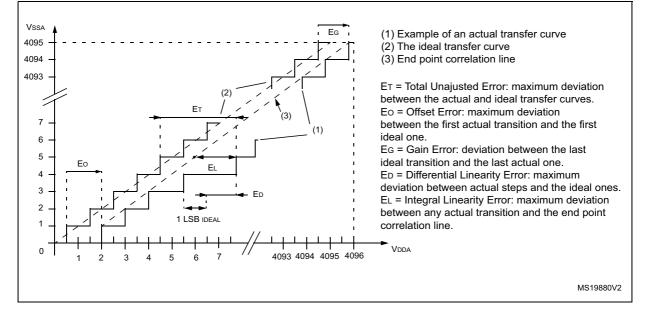

#### Figure 27. ADC accuracy characteristics

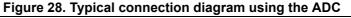

1. Refer to *Table 60* for the values of  $R_{SRC}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 9*. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

| Symbol                               | Parameter                                                                                                                                                             | Conditions                                                                                             | Min | Тур | Мах  | Unit |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|------|------|

|                                      | Offset error                                                                                                                                                          | -                                                                                                      | -   | -   | ±10  | mV   |

| Offset <sup>(3)</sup>                | (difference between measured value at Code                                                                                                                            | Given for the DAC in 10-bit at V <sub>REF+</sub> = 3.6 V                                               | -   | -   | ±3   | LSB  |

|                                      | (0x800) and the ideal<br>value = V <sub>REF+</sub> /2)                                                                                                                | Given for the DAC in 12-bit at $V_{REF+}$ = 3.6 V                                                      | -   | -   | ±12  | LSB  |

| Gain<br>error <sup>(3)</sup>         | Gain error                                                                                                                                                            | Given for the DAC in 12bit configuration                                                               | -   | -   | ±0.5 | %    |

| t <sub>SETTLING</sub> <sup>(3)</sup> | Settling time (full scale:<br>for a 10-bit input code<br>transition between the<br>lowest and the highest<br>input codes when<br>DAC_OUT reaches final<br>value ±1LSB | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                          | -   | 3   | 4    | μs   |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a<br>correct DAC_OUT<br>change when small<br>variation in the input code<br>(from code i to i+1LSB)                                                 | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                          | -   | -   | 1    | MS/s |

| t <sub>wakeup</sub> <sup>(3)</sup>   | Wakeup time from off<br>state (Setting the ENx bit<br>in the DAC Control<br>register)                                                                                 | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$ input code between lowest and highest possible ones. | -   | 6.5 | 10   | μs   |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection<br>ratio (to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                      | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                       | -   | -67 | -40  | dB   |

| Table 63. | DAC | characteristics | (continued) |

|-----------|-----|-----------------|-------------|

|-----------|-----|-----------------|-------------|

1. Guaranteed by design.

2. Quiescent mode refers to the state of the DAC keeping a steady value on the output, so no dynamic consumption is involved.

3. Guaranteed by characterization.

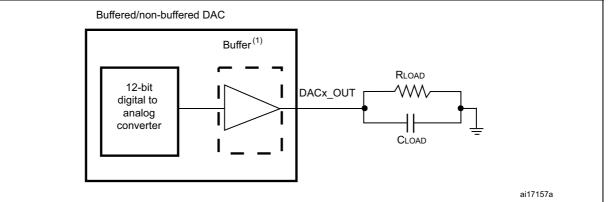

Figure 29. 12-bit buffered /non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

## 6.3.19 Comparator characteristics

| Symbol                   | Parameter                                                     | Conditio                                              | ns                       | Min | Тур | Max <sup>(1)</sup>  | Unit  |

|--------------------------|---------------------------------------------------------------|-------------------------------------------------------|--------------------------|-----|-----|---------------------|-------|

| V <sub>DDA</sub>         | Analog supply voltage                                         | -                                                     |                          |     | -   | 3.6                 | V     |

| V <sub>IN</sub>          | Comparator<br>input voltage range                             | -                                                     |                          | 0   | -   | V <sub>DDA</sub>    | V     |

| $V_{BG}$                 | V <sub>REFINT</sub> scaler<br>input voltage                   | -                                                     |                          | -   | 1.2 | -                   | V     |

| $V_{SC}$                 | V <sub>REFINT</sub> scaler<br>offset voltage                  | -                                                     |                          | -   | ±5  | ±10                 | mV    |

| t <sub>s_sc</sub>        | Scaler startup time from power down                           | First V <sub>REFINT</sub> scaler activ<br>power o     |                          | -   | -   | 1000 <sup>(2)</sup> | ms    |

| -                        | nom power down                                                | Next activa                                           | tions                    |     |     | 0.2                 |       |

| t <sub>START</sub>       | Comparator startup time                                       | Startup time to reach propagation delay specification |                          | -   | -   | 60                  | μs    |

|                          | Propagation delay for<br>200 mV step with 100 mV<br>overdrive | Ultra-low power mode                                  |                          | -   | 2   | 4.5                 | μs    |

|                          |                                                               | Low power mode                                        |                          | -   | 0.7 | 1.5                 |       |

|                          |                                                               | Medium power mode                                     |                          | -   | 0.3 | 0.6                 |       |

|                          |                                                               | High speed mode                                       | $V_{DDA} \ge 2.7 V$      | -   | 50  | 100                 | 20    |

| t_                       |                                                               |                                                       | V <sub>DDA</sub> < 2.7 V | -   | 100 | 240                 | ns    |

| t <sub>D</sub>           |                                                               | Ultra-low power mode                                  |                          | -   | 2   | 7                   |       |

|                          | Propagation delay for full                                    | Low power mode                                        |                          | -   | 0.7 | 2.1                 | μs    |

|                          | range step with 100 mV                                        | Medium power mode                                     |                          | -   | 0.3 | 1.2                 |       |

|                          | overdrive                                                     | High speed mode                                       | $V_{DDA} \ge 2.7 V$      | -   | 90  | 180                 | ns    |

|                          |                                                               | nigh speed mode                                       | V <sub>DDA</sub> < 2.7 V | -   | 110 | 300                 | 110   |

| V <sub>offset</sub>      | Comparator offset error                                       | _                                                     |                          | -   | ±4  | ±10                 | mV    |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                          | -                                                     |                          | -   | 18  | -                   | μV/°C |

|                          |                                                               | Ultra-low power mode                                  |                          | -   | 1.2 | 1.5                 |       |

|                          | COMP current                                                  | Low power mode                                        |                          | -   | 3   | 5                   | - μΑ  |

| I <sub>DD(COMP)</sub>    | consumption                                                   | Medium power mode                                     |                          | -   | 10  | 15                  |       |

|                          |                                                               | High speed mode                                       |                          | -   | 75  | 100                 |       |

Table 64. Comparator characteristics

- 1. Guaranteed by characterization results.

- 2. Integral linearity error can be improved by software calibration of SDADC transfer curve (2-nd order polynomial calibration).

- 3. For f<sub>ADC</sub> lower than 5 MHz, there will be a performance degradation of around 2 dB due to flicker noise increase.

- If the reference value is lower than 2.4 V, there will be a performance degradation proportional to the reference supply drop, according to this formula: 20\*log10(V<sub>REF</sub>/2.4) dB

- 5. SNR, THD, SINAD parameters are valid for frequency bandwidth 20Hz 1kHz. Input signal frequency is 300Hz (for  $f_{ADC}$ =6MHz) and 100Hz (for  $f_{ADC}$ =1.5MHz).

| Symbol                              | Parameter                             | Conditions                                               | Min  | Тур | Max   | Unit | Note                                                              |

|-------------------------------------|---------------------------------------|----------------------------------------------------------|------|-----|-------|------|-------------------------------------------------------------------|

| V <sub>REFINT</sub>                 | Internal reference                    | Buffered embedded<br>reference voltage (1.2 V)           | -    | 1.2 | -     | V    | See Section 6.3.4:<br>Embedded<br>reference voltage on<br>page 60 |

| voltage                             | Vollage                               | Embedded reference<br>voltage amplified by<br>factor 1.5 | -    | 1.8 | -     | V    | -                                                                 |

| C <sub>VREFSD+</sub> <sup>(2)</sup> | Reference voltage filtering capacitor | V <sub>REFSD+</sub> = V <sub>REFINT</sub>                | 1000 | -   | 10000 | nF   | -                                                                 |

| R <sub>VREFSD+</sub>                | Reference voltage<br>input impedance  | Normal mode<br>(f <sub>ADC</sub> = 6 MHz)                | -    | 238 | -     | kΩ   | See RM0313<br>reference manual for                                |

|                                     |                                       | Slow mode<br>(f <sub>ADC</sub> = 1.5 MHz)                | -    | 952 | -     | Ν32  | detailed description                                              |

Table 75. VREFSD+ pin characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

If internal reference voltage is selected then this capacitor is charged through internal resistance - typ. 300 ohm. If internal reference source is selected through the reference voltage selection bits (REFV<>"00" in SDADC\_CR1 register), the application must first configure REFV bits and then wait for capacitor charging. Recommended waiting time is 3 ms if 1 µF capacitor is used.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| D      | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| D1     | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |  |

| E      | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| E1     | 5.450       | 5.500 | 5.550 | 0.2146                | 0.2165 | 0.2185 |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| F      | 0.700       | 0.750 | 0.800 | 0.0276                | 0.0295 | 0.0315 |  |

| ddd    | -           | -     | 0.100 | -                     | -      | 0.0039 |  |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |  |

| fff    | -           | -     | 0.050 | -                     | -      | 0.0020 |  |

## Table 76. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid arraypackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

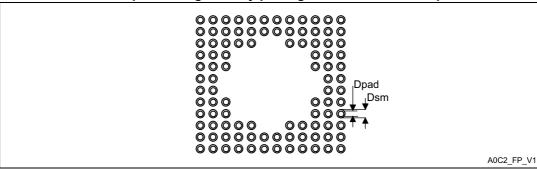

## Figure 33. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package recommended footprint

#### Table 77. UFBGA100 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Cumhal |       | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------------|-------|-----------------------|--------|--------|

| Symbol | Min   | Тур         | Мах   | Min                   | Тур    | Мах    |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -     | 5.500       | -     | -                     | 0.2165 | -      |

| E      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -     | 5.500       | -     | -                     | 0.2165 | -      |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |

| CCC    | -     | -           | 0.080 | -                     | -      | 0.0031 |

| Table 80. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## 7.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 22: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J max = T_A max + (P_D max x Q_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Q<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \mathsf{S} \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \mathsf{S}((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                         | Value | Unit |

|---------------|-----------------------------------------------------------------------------------|-------|------|

|               | <b>Thermal resistance junction-ambient</b><br>LQFP64 - 10 × 10 mm / 0.5 mm pitch  | 45    |      |

| 0             | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm                   | 55    | °C/W |

| $\Theta_{JA}$ | <b>Thermal resistance junction-ambient</b><br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 46    | C/VV |

|               | <b>Thermal resistance junction-ambient</b><br>UFBGA100 - 7 x 7 mm                 | 59    |      |

#### Table 81. Package thermal characteristics

#### 7.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

|             | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-Sep-2013 | 4        | Replaced "Cortex-M4F" with "Cortex-M4" throughout the document.<br>Removed part number STM32F372xx.<br>Added "1.25 DMIPS/MHz (Dhrystone 2.1)" in <i>Features</i> .<br>Updated <i>Introduction</i> .<br>Added reference to the STMTouch touch sensing firmware<br>library in <i>Section 3.16: Touch sensing controller (TSC)</i> .<br>Added "All I2S interfaces can operate in half-duplex mode<br>only." in <i>Section 3.21: Serial peripheral interface (SPI)/Inter-<br/>integrated sound interfaces (I2S)</i> .<br>Added row "I2S full-duplex mode" to <i>Table 9: STM32F373xx</i><br><i>SPI/I2S implementation</i> .<br>Modified introduction of <i>I2C interface characteristics</i> .<br>Added alternate function RTC_REFIN and removed additional<br>function RTC_REF_CLK_IN to pins PA1 and PB15.<br>Replaced alternate function JNTRST with NJTRST for pin<br>PB4.<br>In <i>Table 12: Alternate functions for port PA</i> : replaced alternate<br>function JTMS-SWDIO with SWDIO-JTMS for pin PA13, and<br>JTCK-SWCLK with SWCLK-JTCK for pin PA14.<br>Added rows V <sub>REF+</sub> and V <sub>REF5D+</sub> to <i>Table 22: General<br/>operating conditions</i> .<br>Replaced "f <sub>APB1</sub> = f <sub>AHB/2</sub> " with "f <sub>APB1</sub> = f <sub>AHB</sub> " for "When the<br>peripherals are enabled" in <i>Typical current consumption</i> .<br>Added COMP in <i>Table 36: Peripheral current consumption</i> .<br>Added Min and Max values for ACC <sub>HISI</sub> in <i>Table 42: HSI</i><br><i>oscillator characteristics</i> .<br>Replaced reference "JESD22-C101" with "ANSI/ESD<br>STM5.3.1" in <i>Table 49: ESD absolute maximum ratings</i> .<br>Removed pins PB0 and PB1 in description of I <sub>INJ</sub> in <i>Table 51:</i><br><i>I/O current injection susceptibility</i> .<br>Updated <i>Table 56: I2C characteristics</i> .<br>Replaced all occurrences of "gain/2" with "gain*2" in <i>Table 74:</i><br><i>SDADC characteristics</i> .<br>Corrected typo in <i>Figure 19: I/O AC characteristics definition</i> .<br>Replaced <i>Figure 21: I2C bus AC</i> waveforms and<br><i>measurement circuit</i> .<br>Added I <sub>DDA(ADC)</sub> and footnote 1 in <i>Table 60: ADC</i><br><i>characteristics</i> |

Table 83. Document revision history (continued)