Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 24K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 3x16b; D/A 3x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-UFBGA                                                             |

| Supplier Device Package    | 100-UFBGA (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f373vbh6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 44. LQFP64 P <sub>D</sub> max vs. T <sub>A</sub> | 129 |

|---------------------------------------------------------|-----|

|---------------------------------------------------------|-----|

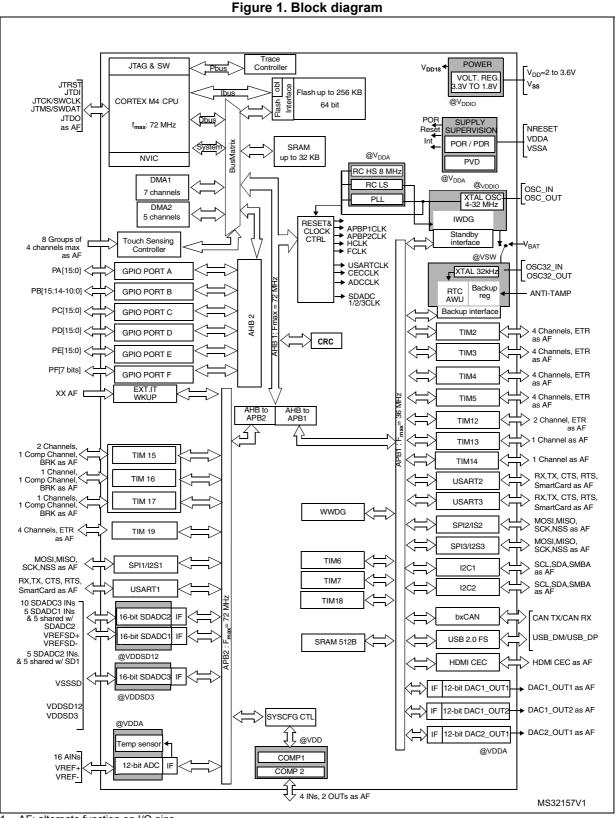

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F373xx microcontrollers.

This STM32F373xx datasheet should be read in conjunction with the RM0313 reference manual. The reference manual is available from the STMicroelectronics website www.st.com.

For information on the Cortex<sup>®</sup>-M4 with FPU core, please refer to:

- Cortex<sup>®</sup>-M4 with FPU Technical Reference Manual, available from www.arm.com.

- STM32F3xxx and STM32F4xxx Cortex<sup>®</sup>-M4 programming manual (PM0214) available from <u>www.st.com</u>.

|                             |                                       | Tub                                                                                                   | C 2. DC        | vice o |        |                |     | r               |                  |     |

|-----------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|----------------|--------|--------|----------------|-----|-----------------|------------------|-----|

| Per                         | ripheral                              |                                                                                                       | STM32<br>373Cx | -      |        | STM32<br>373Rx | -   | STM32F<br>373Vx |                  |     |

| Flash (Kbytes)              | )                                     | 64                                                                                                    | 128            | 256    | 64     | 128            | 256 | 64              | 128              | 256 |

| SRAM (Kbytes                | 5)                                    | 16                                                                                                    | 24             | 32     | 16     | 24             | 32  | 16              | 24               | 32  |

| Timers                      | 9 (16-bit)<br>2 (32 bit)              |                                                                                                       |                |        |        |                |     |                 |                  |     |

|                             | Basic                                 |                                                                                                       |                |        |        | 3 (16-bi       | it) |                 |                  |     |

|                             | SPI/I2S                               |                                                                                                       |                |        |        | 3              |     |                 |                  |     |

|                             | l <sup>2</sup> C                      |                                                                                                       |                |        |        | 2              |     |                 |                  |     |

| Comm.<br>interfaces         | USART                                 |                                                                                                       |                |        |        | 3              |     |                 |                  |     |

|                             | CAN                                   |                                                                                                       |                |        |        | 1              |     |                 |                  |     |

|                             | USB                                   |                                                                                                       |                |        |        | 1              |     |                 |                  |     |

|                             | Normal I/Os<br>(TC, TTa)              | 36                                                                                                    |                |        | 52     |                |     | 84              |                  |     |

| GPIOs                       | 5 volts Tolerant<br>I/Os<br>(FT, Ftf) |                                                                                                       | 20             |        | 28     |                |     | 45              |                  |     |

| 12-bit ADCs                 |                                       | 1                                                                                                     |                |        |        |                |     |                 |                  |     |

| 16-bit ADCs<br>Sigma- Delta |                                       |                                                                                                       |                |        |        | 3              |     |                 |                  |     |

| 12-bit DACs o               | utputs                                |                                                                                                       |                |        |        | 3              |     |                 |                  |     |

| Analog compa                | irator                                |                                                                                                       |                |        |        | 2              |     |                 |                  |     |

| Capacitive ser<br>channels  | nsing                                 | 14                                                                                                    |                |        | 17     |                |     | 24              |                  |     |

| Max. CPU free               | quency                                | 72 MHz                                                                                                |                |        |        |                |     |                 |                  |     |

| Main operating              | 2.0 to 3.6 V                          |                                                                                                       |                |        |        |                |     |                 |                  |     |

| 16-bit SDADC                | operating voltage                     | 2.2 to 3.6 V                                                                                          |                |        |        |                |     |                 |                  |     |

| Operating tem               | perature                              | Ambient operating temperature:<br>- 40 to 85 °C / - 40 to 105 °C<br>Junction temperature:40 to 125 °C |                |        |        |                |     |                 |                  |     |

| Packages                    |                                       | LQFP48                                                                                                |                |        | LQFP64 |                |     |                 | LQFP10<br>FBGA10 |     |

Table 2. Device overview

1. UFBGA100 package available on 256-KB versions only.

1. AF: alternate function on I/O pins.

# 3.3 Embedded Flash memory

All STM32F373xx devices feature up to 256 Kbytes of embedded Flash memory available for storing programs and data. The Flash memory access time is adjusted to the CPU clock frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

# 3.4 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

# 3.5 Embedded SRAM

All STM32F373xx devices feature up to 32 Kbytes of embedded SRAM with hardware parity check. The memory can be accessed in read/write at CPU clock speed with 0 wait states.

# 3.6 Boot modes

At startup, Boot0 pin and Boot1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART2 (PD5/PD6) or USB (PA11/PA12) through DFU (device firmware upgrade).

# **3.15** Fast comparators (COMP)

The STM32F373xx embeds 2 comparators with rail-to-rail inputs and high-speed output. The reference voltage can be internal or external (delivered by an I/O).

The threshold can be one of the following:

- DACs channel outputs

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or submultiple (1/4 V<sub>REFINT</sub>, 1/2 V<sub>REFINT</sub> and 3/4 V<sub>REFINT</sub>)

The comparators can be combined into a window comparator.

Both comparators can wake up the device from Stop mode and generate interrupts and breaks for the timers.

# **3.16** Touch sensing controller (TSC)

The devices provide a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect the presence of a finger near an electrode which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the electrode capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

Up to 24 touch sensing electrodes can be controlled by the TSC. The touch sensing I/Os are organized in 8 acquisition groups, with up to 4 I/Os in each group.

| Group | Capacitive sensing<br>signal name | Pin name           |  | Group | Capacitive sensing<br>signal name | Pin<br>name |

|-------|-----------------------------------|--------------------|--|-------|-----------------------------------|-------------|

|       | TSC_G1_IO1                        | PA0                |  |       | TSC_G5_IO1                        | PB3         |

| 1     | TSC_G1_IO2                        | PA1                |  | 5     | TSC_G5_IO2                        | PB4         |

| I     | TSC_G1_IO3                        | PA2                |  | 5     | TSC_G5_IO3                        | PB6         |

|       | TSC_G1_IO4                        | PA3                |  |       | TSC_G5_IO4                        | PB7         |

|       | TSC_G2_IO1                        | PA4 <sup>(1)</sup> |  |       | TSC_G6_IO1                        | PB14        |

| 2     | TSC_G2_IO2                        | PA5 <sup>(1)</sup> |  | 6     | TSC_G6_IO2                        | PB15        |

| 2     | TSC_G2_IO3                        | PA6 <sup>(1)</sup> |  | 0     | TSC_G6_IO3                        | PD8         |

|       | TSC_G2_IO4                        | PA7                |  |       | TSC_G6_IO4                        | PD9         |

Table 3. Capacitive sensing GPIOs available on STM32F373xx devices

• Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 40 kHz)

- The high-speed external clock divided by 32

# 3.19 Inter-integrated circuit interface (I<sup>2</sup>C)

Two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard (up to 100 kHz), fast (up to 400 kHz) and fast mode + (up to 1 MHz) modes with 20 mA output drive. They support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

| -                                   | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15 I <sup>2</sup> C peripheral clocks                                  |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled              |

#### Table 6. Comparison of I<sup>2</sup>C analog and digital filters

In addition, they provide hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeout verifications and ALERT protocol management. They also have a clock domain independent from the CPU clock, allowing the application to wake up the MCU from Stop mode on address match.

The I<sup>2</sup>C interfaces can be served by the DMA controller

Refer to Table 7 for the differences between I2C1 and I2C2.

| Table 7. | STM32F373xx | I <sup>2</sup> C im | plementation |

|----------|-------------|---------------------|--------------|

|----------|-------------|---------------------|--------------|

| l <sup>2</sup> C features <sup>(1)</sup>                    | I2C1 | I2C2 |

|-------------------------------------------------------------|------|------|

| 7-bit addressing mode                                       | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    |

| Independent clock                                           | Х    | Х    |

# 3.21 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I<sup>2</sup>S)

Three SPIs are able to communicate at up to 18 Mbits/s in slave and master modes in fullduplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The SPIs can be served by the DMA controller.

Three standard I<sup>2</sup>S interfaces (multiplexed with SPI1, SPI2 and SPI3) are available, that can be operated in master or slave mode. These interfaces can be configured to operate with 16/32 bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency. All I2S interfaces can operate in half-duplex mode only.

Refer to *Table 9* for the features between SPI1, SPI2 and SPI3.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 | SPI3 |

|-----------------------------|------|------|------|

| Hardware CRC calculation    | Х    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    | Х    |

| NSS pulse mode              | Х    | Х    | Х    |

| I2S mode                    | Х    | Х    | Х    |

| TI mode                     | Х    | Х    | Х    |

| I2S full-duplex mode        | -    | -    | -    |

| Table 9. STM32F373xx SPI/I2S i | implementation |

|--------------------------------|----------------|

|--------------------------------|----------------|

1. X = supported.

# 3.22 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

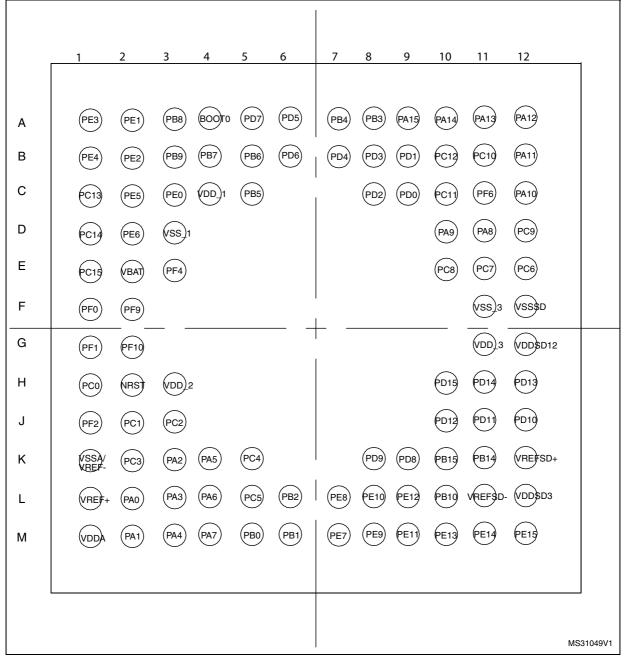

#### Pinouts and pin description

Figure 5. STM32F373xx UFBGA100 ballout

1. The above figure shows the package top view.

| Na               | me                   | Abbreviation                                     | Definition                                                                                            |  |  |  |

|------------------|----------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| Pin r            | name                 |                                                  | e specified in brackets below the pin name, the pin function reset is the same as the actual pin name |  |  |  |

|                  |                      | S                                                | Supply pin                                                                                            |  |  |  |

| Pin              | type                 | I                                                | Input only pin                                                                                        |  |  |  |

|                  |                      | I/O                                              | Input / output pin                                                                                    |  |  |  |

|                  |                      | FT                                               | 5 V tolerant I/O                                                                                      |  |  |  |

|                  |                      | FTf 5 V tolerant I/O, FM+ capable                |                                                                                                       |  |  |  |

| I/O atr          | ucture               | TTa 3.3 V tolerant I/O directly connected to ADC |                                                                                                       |  |  |  |

| i/O su           | ucluie               | TC Standard 3.3 V I/O                            |                                                                                                       |  |  |  |

|                  |                      | B Dedicated BOOT0 pin                            |                                                                                                       |  |  |  |

|                  |                      | RST                                              | Bidirectional reset pin with embedded weak pull-up resistor                                           |  |  |  |

| No               | tes                  | Unless otherwis<br>and after reset               | e specified by a note, all I/Os are set as floating inputs during                                     |  |  |  |

| D.               | Alternate functions  | Functions selected through GPIOx_AFR registers   |                                                                                                       |  |  |  |

| Pin<br>functions | Additional functions | Functions direct                                 | ly selected/enabled through peripheral registers                                                      |  |  |  |

| Table 10. Legend/abbreviations used in the | pinout table |

|--------------------------------------------|--------------|

#### Table 11. STM32F373xx pin definitions

| Pi      | n nun    | nber   | s      |                                       |             |               |       | Pin func             | tions                                                     |

|---------|----------|--------|--------|---------------------------------------|-------------|---------------|-------|----------------------|-----------------------------------------------------------|

| LQFP100 | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function   | Additional functions                                      |

| 1       | B2       | -      | -      | PE2                                   | I/O         | FT            | (2)   | TSC_G7_IO1, TRACECLK | -                                                         |

| 2       | A1       | -      | -      | PE3                                   | I/O         | FT            | (2)   | TSC_G7_IO2, TRACED0  | -                                                         |

| 3       | B1       | -      | -      | PE4                                   | I/O         | FT            | (2)   | TSC_G7_IO3, TRACED1  | -                                                         |

| 4       | C2       | -      | -      | PE5                                   | I/O         | FT            | (2)   | TSC_G7_IO4, TRACED2  | -                                                         |

| 5       | D2       | -      | -      | PE6                                   | I/O         | FT            | (2)   | TRACED3              | WKUP3, RTC_TAMPER3                                        |

| 6       | E2       | 1      | 1      | VBAT                                  | S           | -             | -     | Backup power supply  |                                                           |

| 7       | C1       | 2      | 2      | PC13 <sup>(1)</sup>                   | I/O         | тс            | -     | -                    | WKUP2, ALARM_OUT,<br>CALIB_OUT, TIMESTAMP,<br>RTC_TAMPER1 |

47/137

#### Table 17. Alternate functions for port PF AF0 AF2 AF3 AF4 Pin Name AF1 AF5 AF6 AF7 PF0 I2C2\_SDA -------PF1 -I2C2\_SCL ------PF2 EVENTOUT I2C2 SMBA ------PF4 EVENTOUT -------PF6 EVENTOUT TIM4\_CH4 I2C2\_SCL SPI1\_MOSI/I2S1\_SD USART3\_RTS ---PF7 EVENTOUT I2C2 SDA USART2 CK -----PF9 EVENTOUT TIM14\_CH1 ------PF10 EVENTOUT -------

### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 10: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{APB1} = f_{AHB}/2$ ,  $f_{APB2} = f_{AHB}$

- When f<sub>HCLK</sub> > 8 MHz PLL is ON and PLL inputs is equal to HSI/2 = 4 MHz (if internal clock is used) or HSE = 8 MHz (if HSE bypass mode is used)

The parameters given in *Table 28* to *Table 34* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

|                 |                                 |                       | All peripherals enabled |      |       |                     | abled  | All peripherals disabled |                                     |       |        |      |

|-----------------|---------------------------------|-----------------------|-------------------------|------|-------|---------------------|--------|--------------------------|-------------------------------------|-------|--------|------|

| Symbol          | Parameter                       | Conditions            | f <sub>HCLK</sub>       | Turn | м     | ax @ T <sub>A</sub> | (2)    | Tun                      | Max @ T <sub>A</sub> <sup>(2)</sup> |       | (2)    | Unit |

|                 |                                 |                       |                         | Тур  | 25 °C | 85 °C               | 105 °C | Тур                      | 25 °C                               | 85 °C | 105 °C |      |

|                 |                                 |                       | 72 MHz                  | 63.1 | 70.7  | 71.5                | 73.4   | 29.2                     | 31.1                                | 31.7  | 34.2   |      |

|                 |                                 | HSE                   | 64 MHz                  | 56.3 | 63.3  | 64.1                | 64.9   | 26.1                     | 27.8                                | 28.4  | 30.4   |      |

|                 |                                 | bypass,               | 48 MHz                  | 42.5 | 48.5  | 48.0                | 50.1   | 19.9                     | 22.6                                | 21.9  | 23.1   |      |

|                 |                                 | PLL on                | 32 MHz                  | 28.8 | 31.4  | 32.2                | 34.3   | 13.1                     | 16.1                                | 14.9  | 16.2   |      |

|                 | Supply                          |                       | 24 MHz                  | 21.9 | 24.4  | 24.4                | 25.8   | 10.1                     | 10.9                                | 11.9  | 12.4   |      |

|                 | current in                      | e, bypass,<br>PLL off | 8 MHz                   | 7.3  | 8.0   | 9.3                 | 9.3    | 3.7                      | 4.1                                 | 4.4   | 5.0    |      |

| I <sub>DD</sub> | Run mode,<br>code               |                       | 1 MHz                   | 1.1  | 1.5   | 1.8                 | 2.3    | 0.8                      | 1.1                                 | 1.4   | 1.9    | mA   |

|                 | executing<br>from Flash         |                       | 64 MHz                  | 51.7 | 57.7  | 58.0                | 60.4   | 25.8                     | 27.6                                | 28.1  | 30.1   |      |

|                 |                                 | HSI clock,<br>PLL on  | 48 MHz                  | 38.6 | 45.9  | 43.5                | 46.9   | 19.8                     | 21.9                                | 21.7  | 22.8   |      |

|                 | PLL on<br>HSI clock,<br>PLL off |                       | 32 MHz                  | 26.4 | 31.1  | 29.7                | 31.9   | 13.1                     | 15.7                                | 14.8  | 16.2   |      |

|                 |                                 |                       | 24 MHz                  | 20.3 | 22.6  | 22.6                | 23.7   | 6.9                      | 7.5                                 | 8.1   | 8.8    |      |

|                 |                                 |                       | 8 MHz                   | 7.0  | 7.6   | 8.8                 | 8.8    | 3.7                      | 4.1                                 | 4.4   | 5.0    |      |

#### Table 28. Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6 V<sup>(1)</sup>

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 41*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol              | Parameter                      | Conditions <sup>(1)</sup>                          | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |  |

|---------------------|--------------------------------|----------------------------------------------------|--------------------|-----|--------------------|------|--|

|                     |                                | LSEDRV[1:0]=00<br>lower driving capability         | -                  | 0.5 | 0.9                |      |  |

|                     |                                | LSEDRV[1:0]= 10<br>medium low driving capability   | -                  | -   | 1                  |      |  |

| I <sub>DD</sub>     | LSE current consumption        | LSEDRV[1:0] = 01<br>medium high driving capability | -                  | -   | 1.3                | μA   |  |

|                     |                                | LSEDRV[1:0]=11<br>higher driving capability        | -                  | -   | 1.6                |      |  |

|                     |                                | LSEDRV[1:0]=00<br>lower driving capability         | 5                  | -   | -                  |      |  |

| a                   | Oscillator<br>transconductance | LSEDRV[1:0]= 10<br>medium low driving capability   | 8                  | -   | -                  | μA/V |  |

| 9 <sub>m</sub>      |                                | LSEDRV[1:0] = 01<br>medium high driving capability | 15                 | -   | -                  | μΑνν |  |

|                     |                                | LSEDRV[1:0]=11<br>higher driving capability        | 25                 | -   | -                  |      |  |

| $t_{SU(LSE)}^{(3)}$ | Startup time                   | V <sub>DD</sub> is stabilized                      | -                  | 2   | -                  | s    |  |

#### Table 41. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design.

3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

# 6.3.10 Memory characteristics

#### Flash memory

The characteristics are given at  $T_{A}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

| Symbol Parameter   |                         | Conditions                      | Min | Тур  | Max <sup>(1)</sup> | Unit |  |  |

|--------------------|-------------------------|---------------------------------|-----|------|--------------------|------|--|--|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C | 40  | 53.5 | 60                 | μs   |  |  |

| t <sub>ERASE</sub> | Page (2 kB) erase time  | T <sub>A</sub> = -40 to +105 °C | 20  | -    | 40                 | ms   |  |  |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = -40 to +105 °C | 20  | -    | 40                 | ms   |  |  |

|                    | Supply current          | Write mode                      | -   | -    | 10                 | mA   |  |  |

| IDD                | Supply current          | Erase mode                      | -   | -    | 12                 | mA   |  |  |

1. Guaranteed by design.

|                  |                |                                                                                         | Value              |         |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Parameter      | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

#### Table 46. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

| Symbol           | Description                                                                                                                                                                                                     | Func<br>suscer     | Unit               |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                                                                     | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                                                                                                                   | -0                 | NA                 |      |

|                  | Injected current on PC0 pin                                                                                                                                                                                     | -0                 | +5                 |      |

|                  | Injected current on TC type I/O pins on VDDSD12 power<br>domain: PB2, PE7, PE8, PE9, PE10, PE11, PE12, PE13,<br>PE14, PE15, PB10 with induced leakage current on other pins<br>from this group less than -50 µA | +5                 |                    |      |

| I <sub>INJ</sub> | Injected current on TC type I/O pins on VDDSD3 power<br>domain: PB14, PB15, PD8, PD9, PD10, PD12, PD13, PD14,<br>PD15 with induced leakage current on other pins from this<br>group less than -50 µA            | -5                 | +5                 | mA   |

|                  | Injected current on TTa type pins: PA4, PA5, PA6 with induced leakage current on adjacent pins less than -10 $\mu A$                                                                                            |                    | +5                 |      |

|                  | Injected current on any other FT and FTf pins                                                                                                                                                                   | -5                 | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                                                              | -5                 | +5                 |      |

| Table 51. | . I/O current | injection | susceptibility |

|-----------|---------------|-----------|----------------|

|-----------|---------------|-----------|----------------|

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

# SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 58* for SPI or in *Table 59* for I<sup>2</sup>S are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                                                     | Parameter Conditions                |                                                       | Min            | Мах            | Unit |  |

|----------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|----------------|----------------|------|--|

| f <sub>scк</sub>                                                           |                                     | Master mode                                           | -              | 18             |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> <sup>(1)</sup>                   | SPI clock frequency                 | Slave mode                                            | -              | 18             | MHz  |  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub> (1)                             | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            | -              | 8              | ns   |  |

| DuCy(SCK) <sup>(1)</sup>                                                   | SPI slave input clock<br>duty cycle | Slave mode                                            | 30             | 70             | %    |  |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                                        | NSS setup time                      | Slave mode                                            | 2Tpclk         | -              |      |  |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                         | NSS hold time                       | Slave mode                                            | 4Tpclk         | -              |      |  |

| t <sub>w(SCKH)</sub> <sup>(1)</sup><br>t <sub>w(SCKL)</sub> <sup>(1)</sup> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2<br>- 3 | Tpclk/2<br>+ 3 |      |  |

|                                                                            | Data input setup time               | Master mode                                           | 5.5            | -              |      |  |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)                         | Data input setup time               | Slave mode                                            | 6.5            | -              |      |  |

| t <sub>h(MI)</sub> <sup>(1)</sup>                                          | Data input hold time                | Master mode                                           | 5              | -              |      |  |

| t <sub>h(SI)</sub> <sup>(1)</sup>                                          |                                     | Slave mode                                            | 5              | -              | ns   |  |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                                       | Data output access time             | Slave mode, f <sub>PCLK</sub> = 24 MHz                | 0              | 4Tpclk         |      |  |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                                     | Data output disable time            | Slave mode                                            | 0              | 24             |      |  |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Slave mode (after enable edge)                        | -              | 39             |      |  |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Master mode (after enable edge)                       | -              | 3              |      |  |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Slave mode (after enable edge)                        | 15             | -              |      |  |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Master mode (after enable edge)                       | 4              | -              |      |  |

| Table | 58. | SPI | chara | cteristics |

|-------|-----|-----|-------|------------|

|-------|-----|-----|-------|------------|

1. Guaranteed by characterization results.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

## 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 60* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 22*.

*Note:* It is recommended to perform a calibration after each power-up.

| Symbol                               | Parameter                                 | Conditions                                 | Min                                                                        | Тур                | Max                | Unit               |

|--------------------------------------|-------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| V <sub>DDA</sub>                     | Power supply                              | -                                          | 2.4                                                                        | -                  | 3.6                | V                  |

| V <sub>REF+</sub>                    | Positive reference voltage                | -                                          | 2.4                                                                        | -                  | V <sub>DDA</sub>   | V                  |

| V <sub>REF-</sub>                    | Negative reference voltage                | -                                          | 0                                                                          | -                  | -                  | V                  |

| I <sub>DDA(ADC)</sub> <sup>(1)</sup> | Current consumption from V <sub>DDA</sub> | $V_{DD} = V_{DDA} = 3.3 V$                 | -                                                                          | 0.9                | -                  | mA                 |

| I <sub>VREF</sub>                    | Current on the V <sub>REF</sub> input pin | -                                          | -                                                                          | 160 <sup>(2)</sup> | 220 <sup>(2)</sup> | μA                 |

| f <sub>ADC</sub>                     | ADC clock frequency                       | -                                          | 0.6                                                                        | -                  | 14                 | MHz                |

| f <sub>S</sub> <sup>(3)</sup>        | Sampling rate                             | -                                          | 0.05                                                                       | -                  | 1                  | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>     | External trigger frequency                | f <sub>ADC</sub> = 14 MHz                  | -                                                                          | -                  | 823                | kHz                |

| 'TRIG` '                             |                                           | -                                          | -                                                                          | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                     | Conversion voltage range                  | -                                          | _ 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground)              |                    | V <sub>REF+</sub>  | V                  |

| R <sub>SRC</sub> <sup>(3)</sup>      | Signal source impedance                   | See Equation 1 and<br>Table 61 for details |                                                                            | -                  | 50                 | kΩ                 |

| R <sub>ADC</sub> <sup>(3)</sup>      | Sampling switch resistance                | -                                          | -                                                                          | -                  | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>      | Internal sample and hold capacitor        | -                                          | -                                                                          | -                  | 8                  | pF                 |

| + (3)                                | Colibration time                          | f <sub>ADC</sub> = 14 MHz 5.9              |                                                                            | L                  | μs                 |                    |

| t <sub>CAL</sub> <sup>(3)</sup>      | Calibration time                          | -                                          | 83                                                                         |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> <sup>(3)</sup>      | Injection trigger conversion              | f <sub>ADC</sub> = 14 MHz                  | -                                                                          | -                  | 0.214              | μs                 |

| <sup>4</sup> at` ´                   | latency                                   | -                                          | -                                                                          | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> <sup>(3)</sup>     | Regular trigger conversion                | f <sub>ADC</sub> = 14 MHz                  | -                                                                          | -                  | 0.143              | μs                 |

| 'latr` '                             | latency                                   | -                                          | -                                                                          | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(3)</sup>                    | Sampling time                             | f <sub>ADC</sub> = 14 MHz                  | 0.107                                                                      | -                  | 17.1               | μs                 |

| Ū                                    |                                           | -                                          | 1.5                                                                        | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(3)</sup>     | Power-up time                             | -                                          | -                                                                          | -                  | 1                  | μs                 |

|                                      | Total conversion time (including          | f <sub>ADC</sub> = 14 MHz                  | 1                                                                          | -                  | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(3)</sup>     | sampling time)                            | -                                          | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    | 1/f <sub>ADC</sub> |                    |

| Table | 60  | ADC | characteristics |

|-------|-----|-----|-----------------|

| Iable | 00. | ADC |                 |

During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100 μA on I<sub>DDA</sub> and 60 μA on I<sub>DD</sub> is present

2. Guaranteed by characterization results.

3. Guaranteed by design.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 60

## 6.3.20 Temperature sensor characteristics

| Calibration value name | Description                                                                                           | Memory address            |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C $\pm$ 5 °C, V <sub>DDA</sub> = 3.3 V                 | 0x1FFF F7B8 - 0x1FFF F7B9 |  |  |  |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 110 $^{\circ}$ C ± 5 $^{\circ}$ C V <sub>DDA</sub> = 3.3 V | 0x1FFF F7C2 - 0x1FFF F7C3 |  |  |  |  |

Table 65. Temperature sensor calibration values

#### Table 66. TS characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| TL                                    | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>25</sub>                       | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>     | Startup time                                   | 4    | -    | 10   | μs    |

| T <sub>S_temp</sub> <sup>(2)(1)</sup> | ADC sampling time when reading the temperature | 17.1 | -    | -    | μs    |

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

# 6.3.21 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                                           | Min | Тур | Max | Unit |

|------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>                                | -   | 50  | -   | KΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement                               | -   | 2   | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                                          | -1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1mV accuracy | 5   | -   | -   | μs   |

#### Table 67. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

### 6.3.22 Timer characteristics

The parameters given in *Table 68* are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

|             | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-Sep-2013 | 4        | Replaced "Cortex-M4F" with "Cortex-M4" throughout the document.<br>Removed part number STM32F372xx.<br>Added "1.25 DMIPS/MHz (Dhrystone 2.1)" in <i>Features</i> .<br>Updated <i>Introduction</i> .<br>Added reference to the STMTouch touch sensing firmware<br>library in <i>Section 3.16: Touch sensing controller (TSC)</i> .<br>Added "All I2S interfaces can operate in half-duplex mode<br>only." in <i>Section 3.21: Serial peripheral interface (SPI)/Inter-<br/>integrated sound interfaces (I2S)</i> .<br>Added row "I2S full-duplex mode" to <i>Table 9: STM32F373xx</i><br><i>SPI/I2S implementation</i> .<br>Modified introduction of <i>I2C interface characteristics</i> .<br>Added alternate function RTC_REFIN and removed additional<br>function RTC_REF_CLK_IN to pins PA1 and PB15.<br>Replaced alternate function JNTRST with NJTRST for pin<br>PB4.<br>In <i>Table 12: Alternate functions for port PA</i> : replaced alternate<br>function JTMS-SWDIO with SWDIO-JTMS for pin PA13, and<br>JTCK-SWCLK with SWCLK-JTCK for pin PA14.<br>Added rows V <sub>REF+</sub> and V <sub>REF5D+</sub> to <i>Table 22: General<br/>operating conditions</i> .<br>Replaced "f <sub>APB1</sub> = f <sub>AHB/2</sub> " with "f <sub>APB1</sub> = f <sub>AHB</sub> " for "When the<br>peripherals are enabled" in <i>Typical current consumption</i> .<br>Added COMP in <i>Table 36: Peripheral current consumption</i> .<br>Added Min and Max values for ACC <sub>HISI</sub> in <i>Table 42: HSI</i><br><i>oscillator characteristics</i> .<br>Replaced reference "JESD22-C101" with "ANSI/ESD<br>STM5.3.1" in <i>Table 49: ESD absolute maximum ratings</i> .<br>Removed pins PB0 and PB1 in description of I <sub>INJ</sub> in <i>Table 51:</i><br><i>I/O current injection susceptibility</i> .<br>Updated <i>Table 56: I2C characteristics</i> .<br>Replaced all occurrences of "gain/2" with "gain*2" in <i>Table 74:</i><br><i>SDADC characteristics</i> .<br>Corrected typo in <i>Figure 19: I/O AC characteristics definition</i> .<br>Replaced <i>Figure 21: I2C bus AC</i> waveforms and<br><i>measurement circuit</i> .<br>Added I <sub>DDA(ADC)</sub> and footnote 1 in <i>Table 60: ADC</i><br><i>characteristics</i> |

Table 83. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved