Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 3x16b; D/A 3x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-UFBGA                                                             |

| Supplier Device Package    | 100-UFBGA (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f373vch6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F373xx microcontrollers.

This STM32F373xx datasheet should be read in conjunction with the RM0313 reference manual. The reference manual is available from the STMicroelectronics website www.st.com.

For information on the Cortex<sup>®</sup>-M4 with FPU core, please refer to:

- Cortex<sup>®</sup>-M4 with FPU Technical Reference Manual, available from www.arm.com.

- STM32F3xxx and STM32F4xxx Cortex<sup>®</sup>-M4 programming manual (PM0214) available from <u>www.st.com</u>.

# **3** Functional overview

## 3.1 ARM® Cortex®-M4 core with embedded Flash and SRAM

The ARM Cortex-M4 processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M4 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded ARM core, the STM32F373xx family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32F373xx family.

# 3.2 Memory protection unit

The memory protection unit (MPU) is used to separate the processing of tasks from the data protection. The MPU can manage up to 8 protection areas that can all be further divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The memory protection unit is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

The Cortex-M4 processor is a high performance 32-bit processor designed for the microcontroller market. It offers significant benefits to developers, including:

- Outstanding processing performance combined with fast interrupt handling

- Enhanced system debug with extensive breakpoint and trace capabilities

- Efficient processor core, system and memories

- Ultralow power consumption with integrated sleep modes

- Platform security robustness with optional integrated memory protection unit (MPU).

With its embedded ARM core, the STM32F373xx devices are compatible with all ARM development tools and software.

## 3.7.4 Low-power modes

The STM32F373xx supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### • Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the USARTs, the I2Cs, the CEC, the USB wakeup, the COMPx and the RTC alarm.

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

# 3.8 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz, while the maximum allowed frequency of the low speed APB domain is 36 MHz.

# 3.9 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current capable except for analog inputs.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# 3.12 12-bit analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter is based on a successive approximation register (SAR) architecture. It has up to 16 external channels (AIN15:0) and 3 internal channels (temperature sensor, voltage reference,  $V_{BAT}$  voltage measurement) performing conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the timers (TIMx) can be internally connected to the ADC start and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

## 3.12.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode. See *Table 65: Temperature sensor calibration values on page 105*.

## 3.12.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

## 3.12.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

# **3.15** Fast comparators (COMP)

The STM32F373xx embeds 2 comparators with rail-to-rail inputs and high-speed output. The reference voltage can be internal or external (delivered by an I/O).

The threshold can be one of the following:

- DACs channel outputs

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or submultiple (1/4 V<sub>REFINT</sub>, 1/2 V<sub>REFINT</sub> and 3/4 V<sub>REFINT</sub>)

The comparators can be combined into a window comparator.

Both comparators can wake up the device from Stop mode and generate interrupts and breaks for the timers.

# **3.16** Touch sensing controller (TSC)

The devices provide a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect the presence of a finger near an electrode which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the electrode capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

Up to 24 touch sensing electrodes can be controlled by the TSC. The touch sensing I/Os are organized in 8 acquisition groups, with up to 4 I/Os in each group.

| Group | Capacitive sensing<br>signal name | Pin name           | e Group |   | Capacitive sensing<br>signal name | Pin<br>name |

|-------|-----------------------------------|--------------------|---------|---|-----------------------------------|-------------|

|       | TSC_G1_IO1                        | PA0                |         |   | TSC_G5_IO1                        | PB3         |

| 1     | TSC_G1_IO2                        | PA1                |         | 5 | TSC_G5_IO2                        | PB4         |

|       | TSC_G1_IO3                        | PA2                |         | 5 | TSC_G5_IO3                        | PB6         |

|       | TSC_G1_IO4                        | PA3                |         |   | TSC_G5_IO4                        | PB7         |

|       | TSC_G2_IO1                        | PA4 <sup>(1)</sup> |         |   | TSC_G6_IO1                        | PB14        |

| 2     | TSC_G2_IO2                        | PA5 <sup>(1)</sup> |         | 6 | TSC_G6_IO2                        | PB15        |

|       | TSC_G2_IO3                        | PA6 <sup>(1)</sup> |         | 0 | TSC_G6_IO3                        | PD8         |

|       | TSC_G2_IO4                        | PA7                |         |   | TSC_G6_IO4                        | PD9         |

Table 3. Capacitive sensing GPIOs available on STM32F373xx devices

# 3.21 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I<sup>2</sup>S)

Three SPIs are able to communicate at up to 18 Mbits/s in slave and master modes in fullduplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The SPIs can be served by the DMA controller.

Three standard I<sup>2</sup>S interfaces (multiplexed with SPI1, SPI2 and SPI3) are available, that can be operated in master or slave mode. These interfaces can be configured to operate with 16/32 bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency. All I2S interfaces can operate in half-duplex mode only.

Refer to *Table 9* for the features between SPI1, SPI2 and SPI3.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 | SPI3 |

|-----------------------------|------|------|------|

| Hardware CRC calculation    | Х    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    | Х    |

| NSS pulse mode              | Х    | Х    | Х    |

| I2S mode                    | Х    | Х    | Х    |

| TI mode                     | Х    | Х    | Х    |

| I2S full-duplex mode        | -    | -    | -    |

| Table 9. STM32F373xx SPI/I2S i | implementation |

|--------------------------------|----------------|

|--------------------------------|----------------|

1. X = supported.

# 3.22 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

DocID022691 Rev 7

| Table 11. STM32F373xx pin definitions (continued)         Pin numbers       Pin functions |          |        |        |                                       |             |               |            |                                                                                        | ,                                                               |  |  |  |  |

|-------------------------------------------------------------------------------------------|----------|--------|--------|---------------------------------------|-------------|---------------|------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| Pi                                                                                        | n nun    | nber   | S      |                                       |             |               |            | Pin func                                                                               | Pin functions                                                   |  |  |  |  |

| LQFP100                                                                                   | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate function                                                                     | Additional functions                                            |  |  |  |  |

| 38                                                                                        | M7       | -      | -      | PE7                                   | I/O         | тс            | (3)<br>(2) | -                                                                                      | SDADC1_AIN3P,<br>SDADC1_AIN4M,<br>SDADC2_AIN5P,<br>SDADC2_AIN6M |  |  |  |  |

| 39                                                                                        | L7       | 29     | 21     | PE8                                   | I/O         | тс            | (3)        | -                                                                                      | SDADC1_AIN8P,<br>SDADC2_AIN8P                                   |  |  |  |  |

| 40                                                                                        | M8       | 30     | 22     | PE9                                   | I/O         | тс            | (3)        | -                                                                                      | SDADC1_AIN7P,<br>SDADC1_AIN8M,<br>SDADC2_AIN7P,<br>SDADC2_AIN8M |  |  |  |  |

| 41                                                                                        | L8       | -      | -      | PE10                                  | I/O         | тс            | (3)<br>(2) | -                                                                                      | SDADC1_AIN2P                                                    |  |  |  |  |

| 42                                                                                        | M9       | -      | -      | PE11                                  | I/O         | тс            | (3)<br>(2) | -                                                                                      | SDADC1_AIN1P,<br>SDADC1_AIN2M,<br>SDADC2_AIN4P                  |  |  |  |  |

| 43                                                                                        | L9       | -      | -      | PE12                                  | I/O         | тс            | (3)<br>(2) | -                                                                                      | SDADC1_AIN0P,<br>SDADC2_AIN3P,<br>SDADC2_AIN4M                  |  |  |  |  |

| 44                                                                                        | M10      | -      | -      | PE13                                  | I/O         | тс            | (3)<br>(2) | -                                                                                      | SDADC1_AIN0M ,<br>SDADC2_AIN2P                                  |  |  |  |  |

| 45                                                                                        | M11      | -      | -      | PE14                                  | I/O         | тс            | (3)<br>(2) | -                                                                                      | SDADC2_AIN1P,<br>SDADC2_AIN2M                                   |  |  |  |  |

| 46                                                                                        | M12      | -      | -      | PE15                                  | I/O         | тс            | (3)<br>(2) | USART3_RX                                                                              | SDADC2_AIN0P                                                    |  |  |  |  |

| 47                                                                                        | L10      | -      | -      | PB10                                  | I/O         | тс            | (3)<br>(2) | SPI2_SCK/I2S2_CK,<br>USART3_TX, CEC,<br>TSC_SYNC, TIM2_CH3                             | SDADC2_AIN0M                                                    |  |  |  |  |

| 48                                                                                        | L11      | -      | -      | VREFSD-                               | S           | -             | (2)        | External reference voltage for S<br>(negative input), negative SDA<br>single ende      | DC analog input in SDADC                                        |  |  |  |  |

| 49                                                                                        | F12      | -      | -      | VSSSD                                 | S           | -             | (2)        | SDADC1, SDADC2,                                                                        | SDADC3 ground                                                   |  |  |  |  |

| -                                                                                         | -        | 31     | 23     | VSSSD/<br>VREFSD-                     | S           | -             | -          | SDADC1, SDADC2, SDADC3<br>voltage for SDADC1, SDADC2<br>negative SDADC analog input ir | , SDADC3 (negative input),                                      |  |  |  |  |

| 50                                                                                        | G12      | -      | -      | VDDSD12                               | S           | -             | (2)        | SDADC1 and SDAD                                                                        | C2 power supply                                                 |  |  |  |  |

| -                                                                                         | -        | 32     | 24     | VDDSD                                 | S           | -             | -          | SDADC1, SDADC2, SE                                                                     | DADC3 power supply                                              |  |  |  |  |

Table 11. STM32F373xx pin definitions (continued)

| Table 11. STM32F373xx | pin definitions | (continued) |

|-----------------------|-----------------|-------------|

|-----------------------|-----------------|-------------|

| Pi      | in nun   | nber   | S      |                                       |             |               |       | Pin functions                                                                                              |                      |  |  |

|---------|----------|--------|--------|---------------------------------------|-------------|---------------|-------|------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| LQFP100 | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function                                                                                         | Additional functions |  |  |

| 67      | D11      | 41     | 29     | PA8                                   | I/O         | FT            | -     | SPI2_SCK/I2S2_CK,<br>I2C2_SMBA, USART1_CK,<br>TIM4_ETR, TIM5_CH1_ETR,<br>MCO                               | -                    |  |  |

| 68      | D10      | 42     | 30     | PA9                                   | I/O         | FTf           | -     | SPI2_MISO/I2S2_MCK,<br>I2C2_SCL, USART1_TX,<br>TIM2_CH3, TIM15_BKIN,<br>TIM13_CH1, TSC_G4_IO1              | -                    |  |  |

| 69      | C12      | 43     | 31     | PA10                                  | I/O         | FTf           | -     | SPI2_MOSI/I2S2_SD,<br>I2C2_SDA, USART1_RX,<br>TIM2_CH4, TIM17_BKIN,<br>TIM14_CH1, TSC_G4_IO2               | -                    |  |  |

| 70      | B12      | 44     | 32     | PA11                                  | I/O         | FT            | -     | SPI2_NSS/I2S2_WS,<br>SPI1_NSS/I2S1_WS,<br>USART1_CTS, CAN_RX,<br>TIM4_CH1, USB_DM,<br>TIM5_CH2, COMP1_OUT  | -                    |  |  |

| 71      | A12      | 45     | 33     | PA12                                  | I/O         | FT            | -     | SPI1_SCK/I2S1_CK,<br>USART1_RTS, CAN_TX,<br>USB_DP, TIM16_CH1,<br>TIM4_CH2, TIM5_CH3,<br>COMP2_OUT         | -                    |  |  |

| 72      | A11      | 46     | 34     | PA13                                  | I/O         | FT            | -     | SPI1_MISO/I2S1_MCK,<br>USART3_CTS, IR_OUT,<br>TIM16_CH1N, TIM4_CH3,<br>TIM5_CH4, TSC_G4_IO3,<br>SWDIO-JTMS | -                    |  |  |

| 73      | C11      | 47     | 35     | PF6                                   | I/O         | FTf           | -     | SPI1_MOSI/I2S1_SD,<br>USART3_RTS, TIM4_CH4,<br>I2C2_SCL                                                    | -                    |  |  |

| 74      | F11      | -      | -      | VSS_3                                 | S           | -             | (2)   | Grou                                                                                                       | nd                   |  |  |

| 75      | G11      | -      | -      | VDD_3                                 | S           | -             | (2)   | Digital powe                                                                                               | er supply            |  |  |

| -       | -        | 48     | 36     | PF7                                   | I/O         | FTf           | -     | I2C2_SDA, USART2_CK                                                                                        | -                    |  |  |

| 76      | A10      | 49     | 37     | PA14                                  | I/O         | FTf           | -     | I2C1_SDA, TIM12_CH1,<br>TSC_G4_IO4, SWCLK-JTCK                                                             | -                    |  |  |

42/137

DocID022691 Rev 7

571

|             | Table 12. Alternate functions for port PA (continued) |                  |              |                |              |                      |                        |            |     |     |               |      |      |              |

|-------------|-------------------------------------------------------|------------------|--------------|----------------|--------------|----------------------|------------------------|------------|-----|-----|---------------|------|------|--------------|

| Pin<br>Name | AF0                                                   | AF1              | AF2          | AF3            | AF4          | AF5                  | AF6                    | AF7        | AF8 | AF9 | AF10          | AF11 | AF14 | AF15         |

| PA13        | SWDIO<br>-JTMS                                        | TIM16_<br>CH1N   | TIM5_<br>CH4 | TSC_<br>G4_IO3 | -            | IR-OUT               | SPI1_MISO<br>/I2S1_MCK | USART3_CTS | -   | -   | TIM4_<br>CH3  | -    | -    | EVENT<br>OUT |

| PA14        | SWCLK<br>-JTCK                                        | -                | -            | TSC_<br>G4_IO4 | I2C1_<br>SDA | -                    | -                      | -          | -   | -   | TIM12<br>_CH1 | -    | -    | EVENT<br>OUT |

| PA15        | JTDI                                                  | TIM2_<br>CH1_ETR | -            | TSC_<br>SYNC   | I2C1_<br>SCL | SPI1_NSS/<br>I2S1_WS | SPI3_NSS/<br>I2S3_WS   | -          | -   | -   | TIM12<br>_CH2 | -    | -    | EVENT<br>OUT |

| Bus  | Boundary address          | Size    | Peripheral             |

|------|---------------------------|---------|------------------------|

|      | 0x4800 1400 - 0x4800 17FF | 1KB     | GPIOF                  |

|      | 0x4800 1000 - 0x4800 13FF | 1KB     | GPIOE                  |

| AHB2 | 0x4800 0C00 - 0x4800 0FFF | 1KB     | GPIOD                  |

| ANDZ | 0x4800 0800 - 0x4800 0BFF | 1KB     | GPIOC                  |

|      | 0x4800 0400 - 0x4800 07FF | 1KB     | GPIOB                  |

|      | 0x4800 0000 - 0x4800 03FF | 1KB     | GPIOA                  |

| -    | 0x4002 4400 - 0x47FF FFFF | ~128 MB | Reserved               |

|      | 0x4002 4000 - 0x4002 43FF | 1 KB    | TSC                    |

|      | 0x4002 3400 - 0x4002 3FFF | 3 KB    | Reserved               |

|      | 0x4002 3000 - 0x4002 33FF | 1 KB    | CRC                    |

|      | 0x4002 2400 - 0x4002 2FFF | 3 KB    | Reserved               |

| AHB1 | 0x4002 2000 - 0x4002 23FF | 1 KB    | FLASH memory interface |

| ANDI | 0x4002 1400 - 0x4002 1FFF | 3 KB    | Reserved               |

|      | 0x4002 1000 - 0x4002 13FF | 1 KB    | RCC                    |

|      | 0x4002 0800- 0x4002 0FFF  | 2 KB    | Reserved               |

|      | 0x4002 0400 - 0x4002 07FF | 1 KB    | DMA2                   |

|      | 0x4002 0000 - 0x4002 03FF | 1 KB    | DMA1                   |

| -    | 0x4001 6C00 - 0x4001 FFFF | 37 KB   | Reserved               |

|  | Table 18. STM32F373xx | peripheral register | er boundary addresses <sup>(1)</sup> |

|--|-----------------------|---------------------|--------------------------------------|

|--|-----------------------|---------------------|--------------------------------------|

## 6.3.4 Embedded reference voltage

The parameters given in *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

| Calibration value name | Description                                                              | Memory address            |

|------------------------|--------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 30 °C<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7BA - 0x1FFF F7BB |

#### Table 26. Embedded internal reference voltage calibration values

|                                      | _                                                             |                                   |       |      |      |        |

|--------------------------------------|---------------------------------------------------------------|-----------------------------------|-------|------|------|--------|

| Symbol                               | Parameter                                                     | Conditions                        | Min   | Тур  | Мах  | Unit   |

| V <sub>REFINT</sub>                  | Internal reference voltage                                    | –40 °C < T <sub>A</sub> < +105 °C | 1.20  | 1.23 | 1.25 | V      |

| T <sub>S_vrefint</sub> (1)           | ADC sampling time when reading the internal reference voltage | -                                 | 17.10 | -    | -    | μs     |

| V <sub>REFINT_s</sub> <sup>(2)</sup> | Internal reference voltage spread over the temperature range  | V <sub>DD</sub> = 3 V ±10 mV      | -     | -    | 10   | mV     |

| $T_{\text{Coeff}}^{(2)}$             | Temperature coefficient                                       | -                                 | -     | -    | 100  | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>    | Startup time                                                  | -                                 | -     | -    | 10   | μs     |

#### Table 27. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

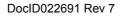

Figure 12. High-speed external clock source AC timing diagram

### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 13*.

| Symbol                                       | Parameter <sup>(1)</sup>                | Conditions | Min                | Тур    | Max                | Unit |  |

|----------------------------------------------|-----------------------------------------|------------|--------------------|--------|--------------------|------|--|

| f <sub>LSE_ext</sub>                         | User External clock source<br>frequency | -          | -                  | 32.768 | 1000               | kHz  |  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage   | -          | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |  |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage    | -          | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |  |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time               | -          | 450                | 450    |                    | ns   |  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time              | -          | -                  | -      | 50                 | 115  |  |

Table 39. Low-speed external user clock characteristics

1. Guaranteed by design.

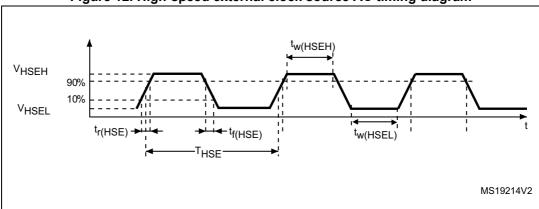

### Input/output AC characteristics

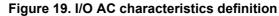

The definition and values of input/output AC characteristics are given in *Figure 19* and *Table 54*, respectively.

Unless otherwise specified, the parameters given are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                               | Min | Max                | Unit |

|----------------------------------------|-------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|-----|--------------------|------|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                   | -   | 2                  | MHz  |

| x0                                     | t <sub>f(IO)out</sub>   | Output high to low level<br>fall time                                 | C <sub>1</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V   | -   | 125 <sup>(3)</sup> | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | CL = 30 μr, v <sub>DD</sub> = 2 v to 3.0 v               | -   | 125 <sup>(3)</sup> | 115  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V   | -   | 10                 | MHz  |

| 01                                     | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C <sub>1</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V   | -   | 25 <sup>(3)</sup>  |      |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 μr, v <sub>DD</sub> = 2 v to 5.6 v   | -   | 25 <sup>(3)</sup>  | ns   |

|                                        |                         |                                                                       | C <sub>L</sub> = 30 pF, V <sub>DD</sub> = 2.7 V to 3.6 V | -   | 50                 | MHz  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)(3)</sup>                                   | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V | -   | 30                 | MHz  |

|                                        |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | -   | 20                 | MHz  |

|                                        |                         |                                                                       | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -   | 5 <sup>(3)</sup>   |      |

| 11                                     | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V | -   | 8 <sup>(3)</sup>   |      |

|                                        |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | -   | 12 <sup>(3)</sup>  | 1    |

|                                        |                         |                                                                       | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -   | 5 <sup>(3)</sup>   | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V | -   | 8 <sup>(3)</sup>   |      |

|                                        |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | -   | 12 <sup>(3)</sup>  |      |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      |                                                          | -   | 2                  | MHz  |

| FM+<br>configuration                   | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | CL = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V               | -   | 12                 |      |

| (4)                                    | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    |                                                          | -   | 34                 | ns   |

| -                                      | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                                        | 10  | -                  | ns   |

Table 54. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the RM0313 reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure 19*.

3. Guaranteed by design.

4. The I/O speed configuration is bypassed in FM+ I/O mode. Refer to the STM32F37xx reference manual RM0313 for a description of FM+ I/O mode configuration

## 6.3.15 NRST characteristics

#### **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 52*).

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

| Symbol                                | Parameter                                       | Conditions        | Min                                         | Тур | Мах                                      | Unit |

|---------------------------------------|-------------------------------------------------|-------------------|---------------------------------------------|-----|------------------------------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST Input low level voltage                    | -                 | -                                           | -   | 0.3V <sub>DD</sub> + 0.07 <sup>(1)</sup> | V    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST Input high level voltage                   | -                 | 0.445V <sub>DD</sub> + 0.398 <sup>(1)</sup> | -   | -                                        | v    |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage<br>hysteresis      | -                 | -                                           | 200 | -                                        | mV   |

| R <sub>PU</sub>                       | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25                                          | 40  | 55                                       | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST Input filtered pulse                       | -                 | -                                           | -   | 100                                      | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup>  | NRST Input not filtered pulse                   | -                 | 500                                         | -   | -                                        | ns   |

Table 55. NRST pin characteristics

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

# SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 58* for SPI or in *Table 59* for I<sup>2</sup>S are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                                                     | Parameter                           | Conditions                                            | Min            | Мах            | Unit |

|----------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|----------------|----------------|------|

| f <sub>scк</sub>                                                           |                                     | Master mode                                           | -              | 18             |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> <sup>(1)</sup>                   | SPI clock frequency                 | Slave mode                                            | -              | 18             | MHz  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub> (1)                             | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            | -              | 8              | ns   |

| DuCy(SCK) <sup>(1)</sup>                                                   | SPI slave input clock<br>duty cycle | Slave mode                                            | 30             | 70             | %    |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                                        | NSS setup time                      | Slave mode                                            | 2Tpclk         | -              |      |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                         | NSS hold time                       | Slave mode                                            | 4Tpclk         | -              |      |

| t <sub>w(SCKH)</sub> <sup>(1)</sup><br>t <sub>w(SCKL)</sub> <sup>(1)</sup> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2<br>- 3 | Tpclk/2<br>+ 3 |      |

|                                                                            | Data input setup time               | Master mode                                           | 5.5            | -              |      |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)                         | Data input setup time               | Slave mode                                            | 6.5            | -              |      |

| t <sub>h(MI)</sub> <sup>(1)</sup>                                          | Data input hold time                | Master mode                                           | 5              | -              |      |

| t <sub>h(SI)</sub> <sup>(1)</sup>                                          |                                     | Slave mode                                            | 5              | -              | ns   |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                                       | Data output access time             | Slave mode, f <sub>PCLK</sub> = 24 MHz                | 0              | 4Tpclk         |      |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                                     | Data output disable time            | Slave mode                                            | 0              | 24             |      |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Slave mode (after enable edge)                        | -              | 39             |      |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Master mode (after enable edge)                       | -              | 3              |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Slave mode (after enable edge)                        | 15             | -              |      |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Master mode (after enable edge)                       | 4              | -              |      |

| Table | 58. | SPI | chara | cteristics |

|-------|-----|-----|-------|------------|

|-------|-----|-----|-------|------------|

1. Guaranteed by characterization results.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

## 6.3.20 Temperature sensor characteristics

| Calibration value name | Description                                                                                           | Memory address            |

|------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C $\pm$ 5 °C, V <sub>DDA</sub> = 3.3 V                 | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at temperature of 110 $^{\circ}$ C ± 5 $^{\circ}$ C V <sub>DDA</sub> = 3.3 V | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 65. Temperature sensor calibration values

## Table 66. TS characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| TL                                    | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>25</sub>                       | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>     | Startup time                                   | 4    | -    | 10   | μs    |

| T <sub>S_temp</sub> <sup>(2)(1)</sup> | ADC sampling time when reading the temperature | 17.1 | -    | -    | μs    |

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

# 6.3.21 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                                           | Min | Тур | Max | Unit |

|------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>                                | -   | 50  | -   | KΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement                               | -   | 2   | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                                          | -1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1mV accuracy | 5   | -   | -   | μs   |

#### Table 67. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.22 Timer characteristics

The parameters given in *Table 68* are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

#### Figure 31. USB timings: definition of data signal rise and fall time

|                                           | Table 73. USB: Full-s                | peed electrical ch             | naracteris | tics <sup>(1)</sup> |     |    |  |  |  |

|-------------------------------------------|--------------------------------------|--------------------------------|------------|---------------------|-----|----|--|--|--|

| Symbol                                    | Parameter Conditions Min Typ Max Uni |                                |            |                     |     |    |  |  |  |

| Driver charac                             | teristics                            |                                |            |                     |     |    |  |  |  |

| t <sub>r</sub>                            | Rise time <sup>(2)</sup>             | C <sub>L</sub> = 50 pF         | 4          | -                   | 20  | ns |  |  |  |

| t <sub>f</sub>                            | Fall time <sup>(2)</sup>             | C <sub>L</sub> = 50 pF         | 4          | -                   | 20  | ns |  |  |  |

| t <sub>rfm</sub>                          | Rise/ fall time matching             | t <sub>r</sub> /t <sub>f</sub> | 90         | -                   | 110 | %  |  |  |  |

| V <sub>CRS</sub>                          | Output signal crossover voltage      | -                              | 1.3        | -                   | 2.0 | V  |  |  |  |

| Output driver<br>Impedance <sup>(3)</sup> | Z <sub>DRV</sub>                     | driving high and<br>low        | 28         | 40                  | 44  | Ω  |  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-), the matching impedance is already included in the embedded driver.

## 6.3.24 CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

## 6.3.25 SDADC characteristics

| Symbol              | Parameter                | Conditions                                | Min | Тур | Max                | Unit | Note |

|---------------------|--------------------------|-------------------------------------------|-----|-----|--------------------|------|------|

| Vanon               | Power                    | Slow mode ( $f_{ADC}$ = 1.5 MHz)          | 2.2 | -   | $V_{DDA}$          | v    | -    |

| V <sub>DDSDx</sub>  | supply                   | Normal mode ( $f_{ADC} = 6 \text{ MHz}$ ) | 2.4 | -   | V <sub>DDA</sub>   | v    | -    |

|                     | SDADC                    | Slow mode (f <sub>ADC</sub> = 1.5 MHz)    | 0.5 | 1.5 | 1.65               |      | -    |

| f <sub>ADC</sub>    | clock<br>frequency       | Normal mode (f <sub>ADC</sub> = 6 MHz)    | 0.5 | 6   | 6.3                | MHz  | -    |

| V <sub>REFSD+</sub> | Positive<br>ref. voltage | -                                         | 1.1 | -   | V <sub>DDSDx</sub> | V    | -    |

## Table 74. SDADC characteristics <sup>(1)</sup>

| Cumhal |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |  |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |

| С      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |  |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |  |

| D3     | -     | 5.500       | -     | -      | 0.2165                | -      |  |

| E      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |  |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |  |

| E3     | -     | 5.500       | -     | -      | 0.2165                | -      |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |  |

| k      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |  |

| ссс    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

| Table 80. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

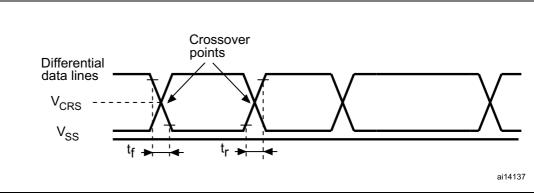

Using the values obtained in *Table 81*  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46°C/W

- $T_{Jmax}$  = 115 °C + (46°C/W × 98.8 mW) = 115 °C + 4.54 °C = 119.5 °C

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Part numbering*).

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Mar-2014 | 5        | Renamed part number STM32F37x to STM32F373xx<br>Added note1 in <i>Table 28: Typical and maximum current</i><br><i>consumption from VDD supply at VDD</i> = $3.6 V$<br>Updated <i>Chapter 3.14: Digital-to-analog converter (DAC)</i><br>Updated, added note 2 and 3 in <i>Table 57: I2C analog filter</i><br><i>characteristics</i><br>Renamed t <sub>SP</sub> symbol with t <sub>AF.</sub><br>Added note for EG Symbol in <i>Table 74: SDADC</i><br><i>characteristics</i><br>Added all packages top view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21-Jul-2015 | 6        | Updated Section 7<br>Updated Section 3.13<br>Updated Section 3.7.1, Section 3.7.4<br>Updated Table 11: STM32F373xx pin definitions, Table 19:<br>Voltage characteristics, Table 49: ESD absolute maximum<br>ratings, Table 74: SDADC characteristics, Table 76:<br>UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine<br>pitch ball grid array package mechanical data, and Table 78:<br>LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package<br>mechanical data<br>Updated Figure 2: STM32F373xx LQFP48 pinout, Figure 9:<br>Power supply scheme, Figure 32: UFBGA100 - 100-pin, 7 x<br>7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package<br>outline, Figure 34: UFBGA100 marking example (package top<br>view), Figure 36: LQFP100 - 100-pin, 14 x 14 mm low-profile<br>quad flat recommended footprint, Figure 37: LQFP100<br>marking example (package top view), Figure 38: LQFP64 -<br>64-pin, 10 x 10 mm low-profile quad flat package outline,<br>Figure 39: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat<br>package recommended footprint, Figure 40: LQFP64 marking<br>example (package top view), Figure 42: LQFP48 - 48-pin, 7 x<br>7 mm low-profile quad flat package recommended footprint,<br>Figure 33: LQFP48 marking example (package top view).<br>Added Table 32: Typical and maximum current consumption<br>from VBAT supply, Table 49: ESD absolute maximum ratings,<br>Table 64: Comparator characteristics, Table 77: UFBGA100<br>recommended PCB design rules (0.5 mm pitch BGA).<br>Added Figure 11: Typical VBAT current consumption (LSE<br>and RTC ON/LSEDRV[1:0]='00'), Figure 30: Maximum<br>VREFINT scaler startup time from power down, Figure 33:<br>UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine<br>pitch ball grid array package recommended footprint. |

Table 83. Document revision history (continued)