# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 3x16b; D/A 3x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f373vct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3 Embedded Flash memory

All STM32F373xx devices feature up to 256 Kbytes of embedded Flash memory available for storing programs and data. The Flash memory access time is adjusted to the CPU clock frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

### 3.4 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

### 3.5 Embedded SRAM

All STM32F373xx devices feature up to 32 Kbytes of embedded SRAM with hardware parity check. The memory can be accessed in read/write at CPU clock speed with 0 wait states.

### 3.6 Boot modes

At startup, Boot0 pin and Boot1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART2 (PD5/PD6) or USB (PA11/PA12) through DFU (device firmware upgrade).

### 3.12 12-bit analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter is based on a successive approximation register (SAR) architecture. It has up to 16 external channels (AIN15:0) and 3 internal channels (temperature sensor, voltage reference,  $V_{BAT}$  voltage measurement) performing conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the timers (TIMx) can be internally connected to the ADC start and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

### 3.12.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode. See *Table 65: Temperature sensor calibration values on page 105*.

### 3.12.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

### 3.12.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

• Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 40 kHz)

- The high-speed external clock divided by 32

### 3.19 Inter-integrated circuit interface (I<sup>2</sup>C)

Two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard (up to 100 kHz), fast (up to 400 kHz) and fast mode + (up to 1 MHz) modes with 20 mA output drive. They support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

| -                                   | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15 I <sup>2</sup> C peripheral clocks                                  |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled              |

### Table 6. Comparison of I<sup>2</sup>C analog and digital filters

In addition, they provide hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeout verifications and ALERT protocol management. They also have a clock domain independent from the CPU clock, allowing the application to wake up the MCU from Stop mode on address match.

The I<sup>2</sup>C interfaces can be served by the DMA controller

Refer to Table 7 for the differences between I2C1 and I2C2.

| Table 7. | STM32F373xx | I <sup>2</sup> C im | plementation |

|----------|-------------|---------------------|--------------|

|----------|-------------|---------------------|--------------|

| l <sup>2</sup> C features <sup>(1)</sup>                    | I2C1 | I2C2 |

|-------------------------------------------------------------|------|------|

| 7-bit addressing mode                                       | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    |

| Independent clock                                           | Х    | Х    |

|         |          |        |        | Table 11                              | . STN       | //32F3        | 373>  | x pin definitions (continued                                                                               | 1)                                         |

|---------|----------|--------|--------|---------------------------------------|-------------|---------------|-------|------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Pi      | n nun    | nber   | s      |                                       |             |               |       | Pin func                                                                                                   | tions                                      |

| LQFP100 | UFBGA100 | LQFP64 | LQFP48 | Pin name<br>(function after<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function                                                                                         | Additional functions                       |

| 8       | D1       | 3      | 3      | PC14 -<br>OSC32_IN <sup>(1)</sup>     | I/O         | тс            | -     | -                                                                                                          | OSC32_IN                                   |

| 9       | E1       | 4      | 4      | PC15 -<br>OSC32_OUT <sup>(1)</sup>    | I/O         | тс            | -     | -                                                                                                          | OSC32_OUT                                  |

| 10      | F2       | -      | -      | PF9                                   | I/O         | FT            | (2)   | TIM14_CH1                                                                                                  | -                                          |

| 11      | G2       | -      | -      | PF10                                  | I/O         | FT            | (2)   | -                                                                                                          | -                                          |

| 12      | F1       | 5      | 5      | PF0 - OSC_IN                          | I/O         | FTf           | -     | I2C2_SDA                                                                                                   | OSC_IN                                     |

| 13      | G1       | 6      | 6      | PF1 -<br>OSC_OUT                      | I/O         | FTf           | -     | I2C2_SCL                                                                                                   | OSC_OUT                                    |

| 14      | H2       | 7      | 7      | NRST                                  | I/O         | RST           | -     | Device reset input / internal                                                                              | reset output (active low)                  |

| 15      | H1       | 8      | -      | PC0                                   | I/O         | ТТа           | (2)   | TIM5_CH1_ETR                                                                                               | ADC_IN10                                   |

| 16      | J2       | 9      | -      | PC1                                   | I/O         | TTa           | (2)   | TIM5_CH2                                                                                                   | ADCIN11                                    |

| 17      | J3       | 10     | -      | PC2                                   | I/O         | ТТа           | (2)   | SPI2_MISO/I2S2_MCK,<br>TIM5_CH3                                                                            | ADC_IN12                                   |

| 18      | K2       | 11     | -      | PC3                                   | I/O         | TTa           | (2)   | SPI2_MOSI/I2S2_SD,<br>TIM5_CH4                                                                             | ADC_IN13                                   |

| 19      | J1       | -      | -      | PF2                                   | I/O         | FT            | (2)   | I2C2_SMBA                                                                                                  | -                                          |

| 20      | K1       | 12     | 8      | VSSA/VREF-                            | S           | -             | -     | Analog g                                                                                                   | round                                      |

| -       | -        | -      | 9      | VDDA/VREF+                            | S           | -             | (2)   | Analog power supply / Referen                                                                              |                                            |

| 21      | M1       | 13     | -      | VDDA                                  | S           | -             | (2)   | Analog pow                                                                                                 | er supply                                  |

| 22      | L1       | 17     | -      | VREF+                                 | S           | -             | (2)   | Reference voltage for                                                                                      | ADC, COMP, DAC                             |

| 23      | L2       | 14     | 10     | PA0                                   | I/O         | ТТа           | -     | USART2_CTS,<br>TIM2_CH1_ETR,<br>TIM5_CH1_ETR, TIM19_CH1,<br>TSC_G1_IO1, COMP1_OUT                          | RTC_ TAMPER2, WKUP1,<br>ADC_IN0, COMP1_INM |

| 24      | M2       | 15     | 11     | PA1                                   | I/O         | TTa           | -     | SPI3_SCK/I2S3_CK,<br>USART2_RTS, TIM2_CH2,<br>TIM15_CH1N, TIM5_CH2,<br>TIM19_CH2, TSC_G1_IO2,<br>RTC_REFIN | ADC_IN1, COMP1_INP                         |

Table 11. STM32F373xx pin definitions (continued)

41/137

5

|             |               |                      |                      |                | Та            | able 12. Alte          | rnate functio          | ons for port PA | 4             |                |               |               |      |              |

|-------------|---------------|----------------------|----------------------|----------------|---------------|------------------------|------------------------|-----------------|---------------|----------------|---------------|---------------|------|--------------|

| Pin<br>Name | AF0           | AF1                  | AF2                  | AF3            | AF4           | AF5                    | AF6                    | AF7             | AF8           | AF9            | AF10          | AF11          | AF14 | AF15         |

| PA0         | -             | TIM2_<br>CH1_<br>ETR | TIM5_<br>CH1_<br>ETR | TSC_<br>G1_IO1 | -             | -                      | -                      | USART2_CTS      | COMP1<br>_OUT | -              | -             | TIM19<br>_CH1 | -    | EVENT<br>OUT |

| PA1         | RTC_<br>REFIN | TIM2_<br>CH2         | TIM5_<br>CH2         | TSC_<br>G1_IO2 | -             | -                      | SPI3_SCK/<br>I2S3_CK   | USART2_RTS      | -             | TIM15_<br>CH1N | -             | TIM19<br>_CH2 | -    | EVENT<br>OUT |

| PA2         | -             | TIM2_<br>CH3         | TIM5_<br>CH3         | TSC_<br>G1_IO3 | -             | -                      | SPI3_MISO/<br>I2S3_MCK | USART2_TX       | COMP2<br>_OUT | TIM15_<br>CH1  | -             | TIM19<br>_CH3 | -    | EVENT<br>OUT |

| PA3         | -             | TIM2_<br>CH4         | TIM5_<br>CH4         | TSC_<br>G1_IO4 | -             | -                      | SPI3_MOSI<br>/I2S3_SD  | USART2_RX       | -             | TIM15_<br>CH2  | -             | TIM19<br>_CH4 | -    | EVENT<br>OUT |

| PA4         | -             | -                    | TIM3_<br>CH2         | TSC_<br>G2_IO1 | -             | SPI1_NSS/<br>I2S1_WS   | SPI3_NSS/<br>I2S3_WS   | USART2_CK       | -             | -              | TIM12<br>_CH1 | -             | -    | EVENT<br>OUT |

| PA5         | -             | TIM2_<br>CH1_<br>ETR | -                    | TSC_<br>G2_IO2 | -             | SPI1_SCK/<br>I2S1_CK   | -                      | CEC             | -             | TIM14_<br>CH1  | TIM12<br>_CH2 | -             | -    | EVENT<br>OUT |

| PA6         | -             | TIM16_<br>CH1        | TIM3_<br>CH1         | TSC_<br>G2_IO3 | -             | SPI1_MISO<br>/I2S1_MCK | -                      | -               | COMP1<br>_OUT | TIM13_<br>CH1  | -             | -             | -    | EVENT<br>OUT |

| PA7         | -             | TIM17_<br>CH1        | TIM3_<br>CH2         | TSC_<br>G2_IO4 | -             | SPI1_MOSI<br>/I2S1_SD  | -                      | -               | COMP2<br>_OUT | TIM14_<br>CH1  | -             | -             | -    | EVENT<br>OUT |

| PA8         | мсо           | -                    | TIM5_<br>CH1_<br>ETR | -              | I2C2_<br>SMBA | SPI2_SCK/<br>I2S2_CK   | -                      | USART1_CK       | -             | -              | TIM4_<br>ETR  | -             | -    | EVENT<br>OUT |

| PA9         | -             | -                    | TIM13<br>_CH1        | TSC_<br>G4_IO1 | I2C2_<br>SCL  | SPI2_MISO<br>/I2S2_MCK | -                      | USART1_TX       | -             | TIM15_<br>BKIN | TIM2_<br>CH3  | -             | -    | EVENT<br>OUT |

| PA10        | -             | TIM17_<br>BKIN       | -                    | TSC_<br>G4_IO2 | I2C2_<br>SDA  | SPI2_MOSI<br>/I2S2_SD  | -                      | USART1_RX       | -             | TIM14_<br>CH1  | TIM2_<br>CH4  | -             | -    | EVENT<br>OUT |

| PA11        | -             | -                    | TIM5_<br>CH2         | -              | -             | SPI2_NSS/<br>I2S2_WS   | SPI1_NSS/<br>I2S1_WS   | USART1_CTS      | COMP1<br>_OUT | CAN_<br>RX     | TIM4_<br>CH1  | -             | -    | EVENT<br>OUT |

| PA12        | -             | TIM16_<br>CH1        | TIM5_<br>CH3         | -              | -             | -                      | SPI1_SCK/<br>I2S1_CK   | USART1_RTS      | COMP2<br>_OUT | CAN_TX         | TIM4_<br>CH2  | -             | -    | EVENT<br>OUT |

STM32F373xx

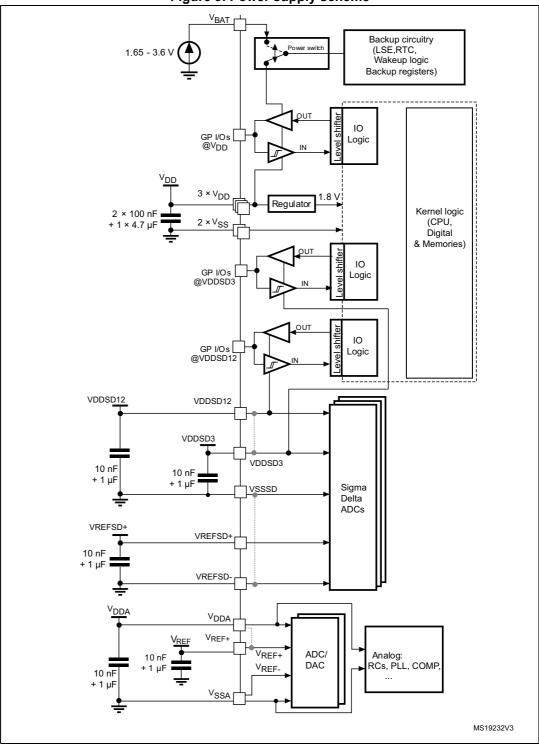

### 6.1.6 Power supply scheme

Figure 9. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

The following relationship must be respected between V<sub>REFSD+</sub> and V<sub>DDSD12</sub>, V<sub>DDSD3</sub>: V<sub>REFSD+</sub> must be lower than V<sub>DDSD3</sub>.

Depending on the SDADCx operation mode, there can be more constraints between  $V_{REFSD+}$ ,  $V_{DDSD12}$  and  $V_{DDSD3}$  which are described in reference manual RM0313.

| Symbol                 | Ratings                                                                            | Max.  | Unit |

|------------------------|------------------------------------------------------------------------------------|-------|------|

| ΣI <sub>VDD</sub>      | Total current into sum of all VDD_x and VDDSDx power lines (source) <sup>(1)</sup> | 160   |      |

| ΣI <sub>VSS</sub>      | Total current out of sum of all VSS_x and VSSSD ground lines $({\rm sink})^{(1)}$  | -160  |      |

| I <sub>VDD(PIN)</sub>  | Maximum current into each VDD_x or VDDSDx power pin (source) <sup>(1)</sup>        | 100   |      |

| I <sub>VSS(PIN)</sub>  | Maximum current out of each VSS_x or VSSSD ground pin (sink) <sup>(1)</sup>        | -100  |      |

|                        | Output current sunk by any I/O and control pin                                     | 25    |      |

| I <sub>IO(PIN)</sub>   | Output current source by any I/O and control pin                                   | -25   | mA   |

| <b>N</b>               | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>        | 80    |      |

| $\Sigma I_{IO(PIN)}$   | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup>     | -80   |      |

|                        | Injected current on FT, FTf and B pins <sup>(3)</sup>                              | -5/+0 |      |

| I <sub>INJ(PIN)</sub>  | Injected current on TC and RST pin <sup>(4)</sup>                                  | ± 5   |      |

|                        | Injected current on TTa pins <sup>(5)</sup>                                        | ± 5   |      |

| ΣI <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>            | ± 25  |      |

| Table 20. Current character | ristics |

|-----------------------------|---------|

|-----------------------------|---------|

VDDSD12 is the external power supply for the PB2, PB10, and PE7 to PE15 I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>). V<sub>DD</sub> (VDD\_x) is the external power supply for all remaining I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>).

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

- 3. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 19: Voltage characteristics* for the maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DDA</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ</sub>(PIN) must never be exceeded. Refer also to *Table 19: Voltage characteristics* for the maximum allowed input voltage values. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 62*.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

#### Table 21. Thermal characteristics

### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 10: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{APB1} = f_{AHB}/2$ ,  $f_{APB2} = f_{AHB}$

- When f<sub>HCLK</sub> > 8 MHz PLL is ON and PLL inputs is equal to HSI/2 = 4 MHz (if internal clock is used) or HSE = 8 MHz (if HSE bypass mode is used)

The parameters given in *Table 28* to *Table 34* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

|                 |                         |                       |                   | AI   | l periphe | erals ena           | abled  | All  | periphe | rals dis            | abled  |      |

|-----------------|-------------------------|-----------------------|-------------------|------|-----------|---------------------|--------|------|---------|---------------------|--------|------|

| Symbol          | Parameter               | Conditions            | f <sub>HCLK</sub> | Turn | м         | ax @ T <sub>A</sub> | (2)    | Tun  | Ma      | ax @ T <sub>A</sub> | (2)    | Unit |

|                 |                         |                       |                   | Тур  | 25 °C     | 85 °C               | 105 °C | Тур  | 25 °C   | 85 °C               | 105 °C |      |

|                 |                         |                       | 72 MHz            | 63.1 | 70.7      | 71.5                | 73.4   | 29.2 | 31.1    | 31.7                | 34.2   |      |

|                 |                         | HSE                   | 64 MHz            | 56.3 | 63.3      | 64.1                | 64.9   | 26.1 | 27.8    | 28.4                | 30.4   |      |

|                 |                         | bypass,               | 48 MHz            | 42.5 | 48.5      | 48.0                | 50.1   | 19.9 | 22.6    | 21.9                | 23.1   |      |

|                 |                         | PLL on                | 32 MHz            | 28.8 | 31.4      | 32.2                | 34.3   | 13.1 | 16.1    | 14.9                | 16.2   |      |

|                 | Supply                  |                       | 24 MHz            | 21.9 | 24.4      | 24.4                | 25.8   | 10.1 | 10.9    | 11.9                | 12.4   |      |

|                 | current in              | HSE                   | 8 MHz             | 7.3  | 8.0       | 9.3                 | 9.3    | 3.7  | 4.1     | 4.4                 | 5.0    |      |

| I <sub>DD</sub> | Run mode,<br>code       | bypass,<br>PLL off    | 1 MHz             | 1.1  | 1.5       | 1.8                 | 2.3    | 0.8  | 1.1     | 1.4                 | 1.9    | mA   |

|                 | executing<br>from Flash |                       | 64 MHz            | 51.7 | 57.7      | 58.0                | 60.4   | 25.8 | 27.6    | 28.1                | 30.1   |      |

|                 |                         | HSI clock,            | 48 MHz            | 38.6 | 45.9      | 43.5                | 46.9   | 19.8 | 21.9    | 21.7                | 22.8   |      |

|                 |                         | PLL on                | 32 MHz            | 26.4 | 31.1      | 29.7                | 31.9   | 13.1 | 15.7    | 14.8                | 16.2   |      |

|                 |                         |                       | 24 MHz            | 20.3 | 22.6      | 22.6                | 23.7   | 6.9  | 7.5     | 8.1                 | 8.8    |      |

|                 |                         | HSI clock,<br>PLL off | 8 MHz             | 7.0  | 7.6       | 8.8                 | 8.8    | 3.7  | 4.1     | 4.4                 | 5.0    |      |

#### Table 28. Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6 V<sup>(1)</sup>

|                  |                                                          |                  |                                                           |       | Тур(  | @V <sub>DD</sub> ( | V <sub>DD</sub> =V | ( <sub>ADD</sub> |       |                           | Max <sup>(1)</sup>        | )                          |      |

|------------------|----------------------------------------------------------|------------------|-----------------------------------------------------------|-------|-------|--------------------|--------------------|------------------|-------|---------------------------|---------------------------|----------------------------|------|

| Symbol           | Parameter                                                |                  | Conditions                                                | 2.0 V | 2.4 V | 2.7 V              | 3.0 V              | 3.3 V            | 3.6 V | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>85 °С | T <sub>A</sub> =<br>105 °C | Unit |

|                  | Supply                                                   |                  | Regulator in run mode, all oscillators OFF                | 1.99  | 2.07  | 2.19               | 2.33               | 2.46             | 2.64  | 10.8                      | 11.8                      | 12.4                       |      |

| I <sub>DDA</sub> | current in<br>Stop mode                                  | DDSD12           | Regulator in<br>low-power<br>mode, all<br>oscillators OFF | 1.99  | 2.07  | 2.18               | 2.32               | 2.47             | 2.63  | 10.6                      | 11.5                      | 12.5                       |      |

|                  | Supply current in                                        | and V            | LSI ON and<br>IWDG ON                                     | 2.44  | 2.53  | 2.7                | 2.89               | 3.09             | 3.33  | -                         | -                         | -                          | μA   |

|                  | Standby<br>mode                                          | V <sub>DDA</sub> | LSI OFF and<br>IWDG OFF                                   | 1.87  | 1.94  | 2.06               | 2.19               | 2.35             | 2.51  | 4.1                       | 4.5                       | 4.8                        |      |

| IDDAmon          | Supply current for $V_{DDA}$ and $V_{DDSD12}$ monitoring |                  | -                                                         | 0.95  | 1.02  | 1.12               | 1.2                | 1.27             | 1.4   | -                         | -                         | -                          |      |

| Table 31. Typical and maximum V <sub>DDA</sub> consumption in Stop and Standby modes |

|--------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------|

1. Data based on characterization results and tested in production.

2. To obtain data with monitoring OFF is necessary to substract the IDDAmon current.

| -                        | Table 32. Typical and maximum current consumption from V <sub>BAT</sub> supply." |                                                                                  |          |                        |         |         |         |         |         |                           |                           |                            |      |

|--------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------|------------------------|---------|---------|---------|---------|---------|---------------------------|---------------------------|----------------------------|------|

| Symbol                   |                                                                                  |                                                                                  |          | Тур @ V <sub>ВАТ</sub> |         |         |         |         |         | Max <sup>(2)</sup>        |                           |                            |      |

|                          | Parameter                                                                        | Conditions                                                                       | = 1.65 V | = 1.8 V                | = 2.0 V | = 2.4 V | = 2.7 V | = 3.3 V | = 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

| I <sub>DD_</sub><br>VBAT | Backup<br>domain<br>supply<br>current                                            | LSE & RTC ON;<br>"Xtal mode" lower<br>driving capability;<br>LSEDRV[1:0] = '00'  | 0.50     | 0.52                   | 0.55    | 0.63    | 0.70    | 0.87    | 0.95    | 1.1                       | 1.6                       | 2.2                        | μA   |

|                          |                                                                                  | LSE & RTC ON;<br>"Xtal mode" higher<br>driving capability;<br>LSEDRV[1:0] = '11' | 0.85     | 0.90                   | 0.93    | 1.02    | 1.10    | 1.27    | 1.38    | 1.6                       | 2.4                       | 3.0                        |      |

### Table 32. Typical and maximum current consumption from $V_{BAT}$ supply<sup>(1)</sup>

1. Crystal used: Abracon ABS07-120-32.768kHz-T with 6 pF of CL for typical values.

2. Guaranteed by characterization results.

All timings are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 22*.

| Symbol                     | Parameter                   | Conditions                     | Typ @V <sub>DD</sub> = V <sub>DDA</sub> |         |         |       |         | Мах | Unit                   |

|----------------------------|-----------------------------|--------------------------------|-----------------------------------------|---------|---------|-------|---------|-----|------------------------|

|                            | Farameter                   | Conditions                     | = 2.0 V                                 | = 2.4 V | = 2.7 V | = 3 V | = 3.3 V | -   | Unit                   |

| <sup>t</sup> wustop        | Wakeup from Stop            | Regulator in run mode          | 4.1                                     | 3.9     | 3.8     | 3.7   | 3.6     | 4.5 |                        |

|                            | mode                        | Regulator in low<br>power mode | 7.9                                     | 6.7     | 6.1     | 5.7   | 5.4     | 8.6 | μs                     |

| t <sub>WUSTANDB</sub><br>Y | Wakeup from<br>Standby mode | LSI and IWDG off               | 62.6                                    | 53.7    | 49.2    | 45.7  | 42.7    | 100 |                        |

| t <sub>WUSLEEP</sub>       | Wakeup from Sleep<br>mode   | After WFE instruction          | 6                                       |         |         |       |         |     | CPU<br>clock<br>cycles |

| Table 37. L | Low-power mode wakeup timings |

|-------------|-------------------------------|

|-------------|-------------------------------|

### 6.3.7 External clock source characteristics

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 12*.

| Symbol                                       | Parameter <sup>(1)</sup>            | Conditions                  | Min          | Тур | Мах                 | Unit |  |  |  |

|----------------------------------------------|-------------------------------------|-----------------------------|--------------|-----|---------------------|------|--|--|--|

| f <sub>HSE_ext</sub>                         | User external clock source          | CSS is on or<br>PLL is used | 1            | 8   | 32                  | MHz  |  |  |  |

|                                              | frequency                           | CSS is off,<br>PLL not used | 0            |     |                     |      |  |  |  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage | -                           | $0.7 V_{DD}$ | -   | V <sub>DD</sub>     | v    |  |  |  |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  | -                           | $V_{SS}$     | -   | 0.3 V <sub>DD</sub> | v    |  |  |  |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             | -                           | 15           | -   | -                   | ns   |  |  |  |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            | -                           | -            | _   | 20                  | 115  |  |  |  |

| Table 38 | . High-speed | external | user clock | characteristics |

|----------|--------------|----------|------------|-----------------|

|----------|--------------|----------|------------|-----------------|

1. Guaranteed by design.

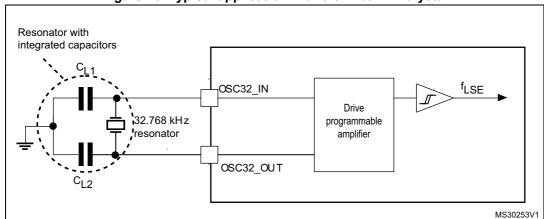

Figure 15. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

### 6.3.8 Internal clock source characteristics

The parameters given in *Table 42* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

The provided curves are characterization results, not tested in production.

#### High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                                                 | Conditions                    | Min                 | Тур | Мах                 | Unit |  |  |  |  |

|-----------------------|-----------------------------------------------------------|-------------------------------|---------------------|-----|---------------------|------|--|--|--|--|

| f <sub>HSI</sub>      | Frequency                                                 | -                             | -                   | 8   | -                   | MHz  |  |  |  |  |

| TRIM                  | HSI user trimming step                                    | -                             | -                   | -   | 1 <sup>(2)</sup>    | %    |  |  |  |  |

| DuCy <sub>(HSI)</sub> | Duty cycle                                                | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>   | %    |  |  |  |  |

|                       | Accuracy of the HSI<br>oscillator (factory<br>calibrated) | T <sub>A</sub> =40 to 105 °C  | -3.8 <sup>(3)</sup> | -   | 4.6 <sup>(3)</sup>  | %    |  |  |  |  |

|                       |                                                           | T <sub>A</sub> = −10 to 85 °C | -2.9 <sup>(3)</sup> | -   | 2.9 <sup>(3)</sup>  | %    |  |  |  |  |

| ACC <sub>HSI</sub>    |                                                           | T <sub>A</sub> = 0 to 70 °C   | -2.3 <sup>(3)</sup> | -   | -2.2 <sup>(3)</sup> | %    |  |  |  |  |

|                       |                                                           | T <sub>A</sub> = 25 °C        | -1                  | -   | 1                   | %    |  |  |  |  |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time                               | -                             | 1 <sup>(3)</sup>    | -   | 2 <sup>(3)</sup>    | μs   |  |  |  |  |

| I <sub>DD(HSI)</sub>  | HSI oscillator power<br>consumption                       | -                             | -                   | 80  | 100 <sup>(3)</sup>  | μA   |  |  |  |  |

Table 42. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  =3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 47*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                     | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-4 | 4A              |

| Table | 47. | EMS | charac | teristics |

|-------|-----|-----|--------|-----------|

| IUNIO |     |     | onarao |           |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter Conditions |                                                                                            | Monitored<br>frequency band | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ]<br>8/72 MHz | Unit |

|------------------|----------------------|--------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|

|                  | Peak level           | level $V_{DD}$ - 3.3 V, T <sub>A</sub> - 25 °C, LQFP100 package compliant with IEC 61967-2 | 0.1 to 30 MHz               | 9                                                          |      |

| 6                |                      |                                                                                            | 30 to 130 MHz               | 26                                                         | dBµV |

| S <sub>EMI</sub> |                      |                                                                                            | 130 MHz to 1 GHz            | 30                                                         |      |

|                  |                      |                                                                                            | SAE EMI Level               | 4                                                          | -    |

### 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| ······································ |                                                             |                                                                                                                        |       |                                 |      |  |  |  |

|----------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------|------|--|--|--|

| Symbol                                 | Ratings                                                     | Conditions                                                                                                             | Class | Maximum<br>value <sup>(1)</sup> | Unit |  |  |  |

| V <sub>ESD(HBM)</sub>                  | Electrostatic discharge voltage (human body model)          | $T_A$ = +25 °C,<br>conforming to JESD22-<br>A114                                                                       | 2     | 2000                            |      |  |  |  |

| V <sub>ESD(CDM)</sub>                  | Electrostatic discharge<br>voltage (charge device<br>model) | T <sub>A</sub> = +25 °C,<br>conforming to<br>ANSI/ESD STM5.3.1,<br>LQFP100, LQFP64,<br>LQFP48 and<br>UFBGA100 packages | II    | 500                             | V    |  |  |  |

Table 49. ESD absolute maximum ratings

1. Guaranteed by characterization results.

| Symbol           | Description                                                                                                                                                                                                     | Func<br>suscer     | Unit               |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                                                                     | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                                                                                                                   | -0                 | NA                 |      |

|                  | Injected current on PC0 pin                                                                                                                                                                                     | -0                 | +5                 |      |

|                  | Injected current on TC type I/O pins on VDDSD12 power<br>domain: PB2, PE7, PE8, PE9, PE10, PE11, PE12, PE13,<br>PE14, PE15, PB10 with induced leakage current on other pins<br>from this group less than -50 µA | -5                 | +5                 |      |

| I <sub>INJ</sub> | Injected current on TC type I/O pins on VDDSD3 power<br>domain: PB14, PB15, PD8, PD9, PD10, PD12, PD13, PD14,<br>PD15 with induced leakage current on other pins from this<br>group less than -50 µA            | -5                 | +5                 | mA   |

|                  | Injected current on TTa type pins: PA4, PA5, PA6 with induced leakage current on adjacent pins less than -10 $\mu A$                                                                                            | -5                 | +5                 |      |

|                  | Injected current on any other FT and FTf pins                                                                                                                                                                   | -5                 | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                                                              | -5                 | +5                 |      |

| Table 51. | . I/O current | injection | susceptibility |

|-----------|---------------|-----------|----------------|

|-----------|---------------|-----------|----------------|

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### 6.3.18 DAC electrical specifications

| Symbol                              | Parameter                                                                                                       |                               | Conditions                                                        | Min | Тур | Мах                      | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------|-----|-----|--------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage                                                                                           |                               | -                                                                 | 2.4 | -   | 3.6                      | V    |

| V <sub>REF+</sub>                   | Reference supply voltage                                                                                        | V <sub>REF+</sub> must        | t always be below V <sub>DDA</sub>                                | 2.4 | -   | 3.6                      | V    |

| V <sub>SSA</sub>                    | Ground                                                                                                          |                               | -                                                                 | 0   | -   | 0                        | V    |

| - (1)                               |                                                                                                                 | DAC                           | Connected to V <sub>SSA</sub>                                     | 5   | -   | -                        |      |

| R <sub>LOAD</sub> <sup>(1)</sup>    | Resistive load                                                                                                  | output<br>buffer ON           | Connected to V <sub>DDA</sub>                                     | 25  | -   | -                        | kΩ   |

| $R_0^{(1)}$                         | Output Impedance                                                                                                | DAC output                    | t buffer OFF                                                      | -   | -   | 15                       | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup>    | Capacitive load                                                                                                 |                               | apacitive load at DAC_OUT he buffer is ON).                       | -   | -   | 50                       | pF   |

| DAC_OUT<br>min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer ON                                                                            | of the DAC.<br>It correspor   | nds to 12-bit input code                                          | 0.2 | -   | -                        | V    |

| DAC_OUT<br>max <sup>(1)</sup>       | Higher DAC_OUT<br>voltage with buffer ON                                                                        |                               | (0xF1C) at $V_{REF+}$ = 3.6 V<br>) and (0xEAB) at $V_{REF+}$ =    | -   | -   | V <sub>DDA</sub> – 0.2   | V    |

| DAC_OUT<br>min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer OFF                                                                           |                               | maximum output excursion                                          | -   | 0.5 | -                        | mV   |

| DAC_OUT<br>max <sup>(1)</sup>       | Higher DAC_OUT<br>voltage with buffer OFF                                                                       | of the DAC                    |                                                                   | -   | -   | V <sub>REF+</sub> – 1LSB | V    |

| I <sub>DDVREF+</sub> <sup>(3)</sup> | DAC DC current<br>consumption in quiescent<br>mode (Standby mode)                                               | V <sub>REF+</sub> = 3.6       | d, worst code (0xF1C) at<br>5 V in terms of DC<br>n on the inputs | -   | -   | 220                      | μA   |

|                                     | DAC DC current                                                                                                  | With no loa<br>the inputs     | d, middle code (0x800) on                                         | -   | -   | 380                      | μA   |

| I <sub>DDA</sub> <sup>(3)</sup>     | consumption in quiescent mode <sup>(2)</sup>                                                                    | V <sub>REF+</sub> = 3.6       | d, worst code (0xF1C) at<br>S V in terms of DC<br>n on the inputs | -   | -   | 480                      | μA   |

| DNL <sup>(3)</sup>                  | Differential non linearity<br>Difference between two                                                            | Given for th configuration    | ne DAC in 10-bit<br>on                                            | -   | -   | ± 0.5                    | LSB  |

|                                     | consecutive code-1LSB)                                                                                          | Given for th<br>configuration | ie DAC in 12-bit<br>on                                            | -   | -   | ± 2                      | LSB  |

|                                     | Integral non linearity<br>(difference between                                                                   | Given for th<br>configuration | ne DAC in 10-bit<br>on                                            | -   | -   | ± 1                      | LSB  |

| INL <sup>(3)</sup>                  | measured value at Code i<br>and the value at Code i<br>on a line drawn between<br>Code 0 and last Code<br>1023) | Given for th configuratic     | ne DAC in 12-bit<br>on                                            | -   | -   | ± 4                      | LSB  |

#### Table 63. DAC characteristics

| Symbol           | Parameter             | Conditio                                 | ons                   | Min | Тур | Max <sup>(1)</sup> | Unit |

|------------------|-----------------------|------------------------------------------|-----------------------|-----|-----|--------------------|------|

|                  |                       | No hysteresis<br>(COMPxHYST[1:0]=00)     | -                     | -   | 0   | -                  |      |

|                  |                       |                                          | High speed mode       | 3   |     | 13                 |      |

|                  |                       | Low hysteresis<br>(COMPxHYST[1:0]=01)    | All other power modes | 5   | 8   | 10                 |      |

| V <sub>hys</sub> | Comparator hysteresis | Madium hystoresia                        | High speed mode       | 7   |     | 26                 | mV   |

|                  |                       | Medium hysteresis<br>(COMPxHYST[1:0]=10) | All other power modes | 9   | 15  | 19                 |      |

|                  |                       |                                          | High speed mode       | 18  |     | 49                 |      |

|                  |                       | High hysteresis<br>(COMPxHYST[1:0]=11)   | All other power modes | 19  | 31  | 40                 |      |

1. Guaranteed by design.

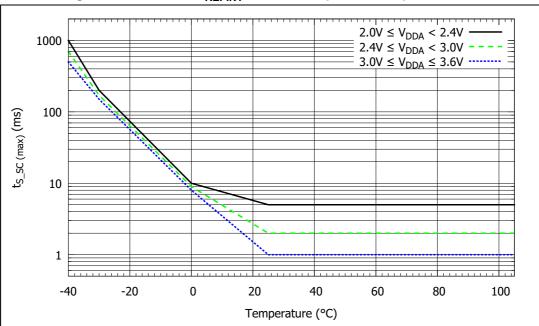

2. For more details and conditions see Figure 30: Maximum VREFINT scaler startup time from power down

| Symbol             | Parameter             |                   |          | Con                           | ditions                     |                                              | Min | Тур | Max | Unit | Note |

|--------------------|-----------------------|-------------------|----------|-------------------------------|-----------------------------|----------------------------------------------|-----|-----|-----|------|------|

|                    |                       |                   |          | f <sub>ADC</sub> =<br>1.5 MHz |                             | $V_{\text{REFSD}^+} = 3.3^{(3)}$             | 84  | 85  | -   |      |      |

|                    |                       | e                 | gain = 1 | f <sub>ADC</sub> =            |                             | V <sub>REFSD+</sub><br>= 1.2 <sup>(4)</sup>  | 86  | 88  | -   |      |      |

|                    |                       | Differential mode | 0,       | 6 MHz                         |                             | V <sub>REFSD+</sub><br>= 3.3                 | 88  | 92  | -   |      |      |

|                    |                       | ifferent          |          | f <sub>ADC</sub> =            |                             | $V_{\text{REFSD}^+}$<br>= 1.2 <sup>(4)</sup> | 76  | 78  | -   |      |      |

|                    |                       | Δ                 | gain = 8 | f <sub>ADC</sub> =<br>6 MHz   |                             | V <sub>REFSD+</sub><br>= 3.3                 | 82  | 86  | -   |      |      |

| SNR <sup>(5)</sup> | Signal to noise ratio |                   | 0,       | f <sub>ADC</sub> =<br>1.5 MHz | V <sub>DDSDx</sub><br>= 3.3 | $V_{\text{REFSD}^+}$<br>= 3.3 <sup>(3)</sup> | 76  | 80  | -   | dB   | -    |

|                    |                       |                   |          | f <sub>ADC</sub> =<br>1.5 MHz |                             | V <sub>REFSD+</sub><br>= 3.3                 | 80  | 84  | -   |      |      |

|                    |                       | mode              | gain = 1 | f <sub>ADC</sub> =            |                             | V <sub>REFSD+</sub><br>= 1.2 <sup>(4)</sup>  | 77  | 81  | -   |      |      |

|                    |                       | Single ended mode | ĵ        | 6 MHz                         |                             | V <sub>REFSD+</sub><br>= 3.3                 | 85  | 90  | -   |      |      |

|                    |                       | Single            | 1 = 8    | f <sub>ADC</sub> =            |                             | V <sub>REFSD+</sub><br>= 1.2 <sup>(4)</sup>  | 66  | 71  | -   |      |      |

|                    |                       |                   | gain =   | 6 MHz                         |                             | V <sub>REFSD+</sub><br>= 3.3                 | 74  | 78  | -   |      |      |

Table 74. SDADC characteristics (continued)<sup>(1)</sup>

| Querra la cal |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|---------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol        | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |

| D             | 6.950 | 7.000       | 7.050 | 0.2736 | 0.2756                | 0.2776 |

| D1            | 5.450 | 5.500       | 5.550 | 0.2146 | 0.2165                | 0.2185 |

| E             | 6.950 | 7.000       | 7.050 | 0.2736 | 0.2756                | 0.2776 |

| E1            | 5.450 | 5.500       | 5.550 | 0.2146 | 0.2165                | 0.2185 |

| е             | -     | 0.500       | -     | -      | 0.0197                | -      |

| F             | 0.700 | 0.750       | 0.800 | 0.0276 | 0.0295                | 0.0315 |

| ddd           | -     | -           | 0.100 | -      | -                     | 0.0039 |

| eee           | -     | -           | 0.150 | -      | -                     | 0.0059 |

| fff           | -     | -           | 0.050 | -      | -                     | 0.0020 |

## Table 76. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid arraypackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

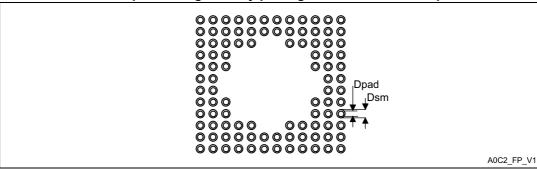

## Figure 33. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package recommended footprint

#### Table 77. UFBGA100 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Date                | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>21-Dec-2012 |          | Updated Table 2: Device overview, capacitive sensing<br>channels peripheral added.         Updated Table 3: Capacitive sensing GPIOs available on<br>STM32F373xx devices         Updated Section 3.19: Inter-integrated circuit interface (I2C)         Updated the function names in Table 11: STM32F373 pin<br>definitions         Updated Table 20: Current characteristics         Updated Table 30: Typical and maximum VDD consumption<br>in Stop and Standby modes         Updated Table 32: Typical and maximum current consumption<br>from VBAT supply         Added Figure 11: Typical VBAT current consumption (LSE<br>and RTC ON/LSEDRV[1:0]='00')         Updated Table 33: Typical current consumption in Run mode,<br>code with data processing running from Flash and Table 34:<br>Typical current consumption in Sleep mode, code running<br>from Flash or RAM         Added Table 36: Peripheral current consumption, Figure 16:<br>HSI oscillator accuracy characterization results         Updated Table 37: Low-power mode wakeup timings         Updated Table 51: I/O current injection susceptibility         Updated Table 52: I/O static characteristics         Updated Table 52: I/O static characteristics         Updated Table 53: Output voltage characteristics         Updated Table 55: NRST pin characteristics         Updated Table 55: NAC port and Figure 20: Five volt tolerant<br>(FT and FTf) I/O input character |

|                     |          | profile quad flat package outline, Figure 35: LQFP64 – 10 x<br>10 mm 64 pin low-profile quad flat package outline and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Table 83. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-Jun-2016 | 7        | <ul> <li>Updated:</li> <li>Table 3: Capacitive sensing GPIOs available on<br/>STM32F373xx devices</li> <li>Table 19: Voltage characteristics</li> <li>Table 27: Embedded internal reference voltage</li> <li>Table 27: Embedded internal reference voltage</li> <li>Table 41: LSE oscillator characteristics (fLSE = 32.768 kHz)</li> <li>Table 49: ESD absolute maximum ratings</li> <li>Table 60: ADC characteristics</li> <li>Table 63: DAC characteristics</li> <li>Table 65: Temperature sensor calibration values</li> <li>Table 74: SDADC characteristics</li> <li>Table 81: Package thermal characteristics</li> <li>Figure 17: TC and TTa I/O input characteristics - CMOS port</li> <li>Figure 18: Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port</li> <li>Figure 18: TC and TTa I/O input characteristics - TTL port</li> <li>Figure 20: Five volt tolerant (FT and FTf) I/O input characteristics - TTL port</li> </ul> |

| Table 83. Document revision history (continued) |

|-------------------------------------------------|

|-------------------------------------------------|