Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | 8051                                                                             |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 40MHz                                                                            |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                 |

| Number of I/O              | 36                                                                               |

| Program Memory Size        | 24KB (24K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | -                                                                                |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | 0°C ~ 70°C                                                                       |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e54rd2a-40-c-tqje |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Not Recommended for New Designs

### **Product Description**

The SST89E54RD2A/RDA and SST89E58RD2A/RDA are members of the FlashFlex family of 8-bit microcontroller products designed and manufactured with SST patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

The devices come with 24/40 KByte of on-chip flash EEPROM program memory which is partitioned into 2 independent program memory blocks. The primary Block 0 occupies 16/32 KByte of internal program memory space and the secondary Block 1 occupies 8 KByte of internal program memory space.

The 8-KByte secondary block can be mapped to the lowest location of the 16/32 KByte address space; it can also be hidden from the program counter and used as an independent EEPROM-like data memory.

In addition to the 24/40 KByte of EEPROM program memory on-chip and 1024 x8 bits of on-chip RAM, the devices can address up to 64 KByte of external program memory and up to 64 KByte of external RAM.

The flash memory blocks can be programmed via a standard 87C5x OTP EPROM programmer fitted with a special adapter and the firmware for SST devices. During power-on reset, the devices can be configured as either a slave to an external host for source code storage or a master to an external host for an in-application programming (IAP) operation. The devices are designed to be programmed in-system and in-application on the printed circuit board for maximum flexibility. The devices are pre-programmed with an example of the bootstrap loader in the memory, demonstrating the initial user program code loading or subsequent user code updating via the IAP operation. The sample bootstrap loader is available for the user's reference and convenience only; SST does not guarantee its functionality or usefulness. Chip-Erase or Block-Erase operations will erase the pre-programmed sample code.

Not Recommended for New Designs

### **Pin Descriptions**

| Symbol  | Type <sup>1</sup>             | Name and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[7:0] | I/O                           | <b>Port 0:</b> Port 0 is an 8-bit open drain bi-directional I/O port. As an output port each pin can sink several LS TTL inputs. Port 0 pins float that have '1's written to them, and in this state can be used as high-impedance inputs. In this application, it uses strong internal pull-ups when transitioning to $V_{OH}$ . Port 0 also receives the code bytes during the external host mode programming, and outputs the code bytes during the external host mode verification. External pull-ups are required during program verification.                                                                                                                                                                             |

| P1[7:0] | I/O with internal<br>pull-ups | <b>Port 1:</b> Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. The Port 1 output buffers can drive LS TTL inputs. Port 1 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. P1[5, 6, 7] have high current drive of 16 mA. Port 1 also receives the low-order address bytes during the external host mode programming and verification.                                                                                                                                                                                         |

| P1[0]   | I/O                           | T2: External count input to Timer/Counter 2 or Clock-out from Timer/Counter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P1[1]   | I                             | T2EX: Timer/Counter 2 capture/reload trigger and direction control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P1[2]   | I                             | <b>ECI:</b> PCA Timer/Counter External Input:<br>This signal is the external clock input for the PCA timer/counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1[3]   | I/O                           | <b>CEX0:</b> Compare/Capture Module External I/O<br>Each compare/capture module connects to a Port 1 pin for external I/O. When<br>not used by the PCA, this pin can handle standard I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P1[4]   | I/O                           | SS#: Master Input or Slave Output for SPI.<br>OR<br>CEX1: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P1[5]   | I/O                           | MOSI: Master Output line, Slave Input line for SPI<br>OR<br>CEX2: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P1[6]   | I/O                           | MISO: Master Input line, Slave Output line for SPI<br>OR<br>CEX3: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P1[7]   | I/O                           | SCK: Master clock output, slave clock input line for SPI<br>OR<br>CEX4: Compare/Capture Module External I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P2[7:0] | I/O with internal<br>pull-up  | <b>Port 2:</b> Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 sends the high-order address byte during fetches from external Program memory and during accesses to external Data Memory that use 16-bit address (MOVX@DPTR). In this application, it uses strong internal pull-ups when transitioning to V <sub>OH</sub> . Port 2 also receives some control signals and high-order address bits during the external host mode programming and verification. |

Table 1: Pin Descriptions (1 of 3)

Not Recommended for New Designs

| Symbol               | Type <sup>1</sup>             | Name and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3[7:0]              | I/O with internal<br>pull-up  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can drive LS TTL inputs. Port 3 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also receives some control signals and high-order address bits during the external host mode programming and verification.                                                                                           |

| P3[0]                | I                             | <b>RXD:</b> Universal Asynchronous Receiver/Transmitter (UART) - Receive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P3[1]                | 0                             | TXD: UART - Transmit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[2]                | I                             | INT0#: External Interrupt 0 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P3[3]                | I                             | INT1#: External Interrupt 1 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P3[4]                | I                             | T0: External count input to Timer/Counter 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[5]                | I                             | T1: External count input to Timer/Counter 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[6]                | 0                             | WR#: External Data Memory Write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P3[7]                | 0                             | RD#: External Data Memory Read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PSEN#                | I/O                           | <b>Program Store Enable:</b> PSEN# is the Read strobe to External Program Store. When the device is executing from Internal Program Memory, PSEN# is inactive ( $V_{OH}$ ). When the device is executing code from External Program Memory, PSEN# is activated twice each machine cycle, except when access to External Data Memory while one PSEN# activation is skipped in each machine cycle. A forced high-to-low input transition on the PSEN# pin while the RST input is continually held high for more than 20 machine cycles will cause the device to enter External Host mode for programming. |

| RST                  | I                             | <b>Reset:</b> While the oscillator is running, a high logic state on this pin for two machine cycles will reset the device. After a reset, if the PSEN# pin is driven by a high-to-low input transition while the RST input pin is held high, the device will enter the External Host mode, otherwise the device will enter the Normal operation mode.                                                                                                                                                                                                                                                  |

| EA#                  | I                             | <b>External Access Enable:</b> EA# must be driven to $V_{IL}$ in order to enable the device to fetch code from the External Program Memory. EA# must be driven to $V_{IH}$ for internal program execution. However, Security lock level 4 will disable EA#, and program execution is only possible from internal program memory.                                                                                                                                                                                                                                                                        |

| ALE/PROG#            | I/O                           | <b>Address Latch Enable:</b> ALE is the output signal for latching the low byte of the address during an access to external memory. This pin is also the programming pulse input (PROG#) for flash programming. Normally the ALE <sup>2</sup> is emitted at a constant rate of 1/6 the crystal frequency <sup>3</sup> and can be used for external timing and clocking. One ALE pulse is skipped during each access to external data memory. However, if AO is set to 1, ALE is disabled.                                                                                                               |

| P4[3:0] <sup>4</sup> | I/O with internal<br>pull-ups | <b>Port 4:</b> Port 4 is an 4-bit bi-directional I/O port with internal pull-ups. The port 4 output buffers can drive LS TTL inputs. Port 4 pins are pulled high by the inter nal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, port 4 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                           |

| P4[0]                | I/O                           | Bit 0 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P4[1]                | I/O                           | Bit 1 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P4[2] / INT3#        | I/O                           | Bit 2 of port 4 / INT3# External interrupt 3 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P4[3] / INT2#        | I/O                           | Bit 3 of port 4 / INT2# External interrupt 2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1: Pin Descriptions (Continued) (2 of 3)

#### Not Recommended for New Designs

| Symbol          | Type <sup>1</sup> | Name and Functions                                                                                                |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------|

| XTAL1           | I                 | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits. |

| XTAL2           | 0                 | Crystal 2: Output from the inverting oscillator amplifier                                                         |

| V <sub>DD</sub> | I                 | Power Supply                                                                                                      |

| V <sub>SS</sub> | I                 | Ground                                                                                                            |

|                 |                   | T0-0.0 25114                                                                                                      |

### Table 1: Pin Descriptions (Continued) (3 of 3)

1. I = Input; O = Output

2.ALE loading issue: When ALE pin experiences higher loading (>30pf) during the reset, the MCU may accidentally enter into modes other than normal working mode. The solution is to add a pull-up resistor of 3-50 K $\Omega$  to V<sub>DD</sub>, e.g. for ALE pin.

3. For 6 clock mode, ALE is emitted at 1/3 of crystal frequency.

4. Port 4 is not present on the PDIP package.

#### Not Recommended for New Designs

@DPTR generates a 16-bit address. This allows external addressing up the 64K. Port 2 provides the high-order eight address bits (DPH), and Port 0 multiplexes the low order eight address bits (DPL) with data. Both MOVX @Ri and MOVX @DPTR generates the necessary read and write signals (P3.6 - WR# and P3.7 - RD#) for external memory use. Table 4 shows external data memory RD#, WR# operation with EXTRAM bit.

The stack pointer (SP) can be located anywhere within the 256 bytes of internal RAM (lower 128 bytes and upper 128 bytes). The stack pointer may not be located in any part of the expanded RAM.

|            | MOVX @DPTR, A or       | MOVX @Ri, A or MOVX A, @Ri |                                     |

|------------|------------------------|----------------------------|-------------------------------------|

| AUXR       | ADDR < 0300H           | ADDR >= 0300H              | ADDR = Any                          |

| EXTRAM = 0 | RD# / WR# not asserted | RD# / WR# asserted         | RD# / WR# not asserted <sup>1</sup> |

| EXTRAM = 1 | RD# / WR# asserted     | RD# / WR# asserted         | RD# / WR# asserted                  |

### Table 4: External Data Memory RD#, WR# with EXTRAM bit

1. Access limited to ERAM address within 0 to 0FFH; cannot access 100H to 02FFH.

Not Recommended for New Designs

### **Dual Data Pointers**

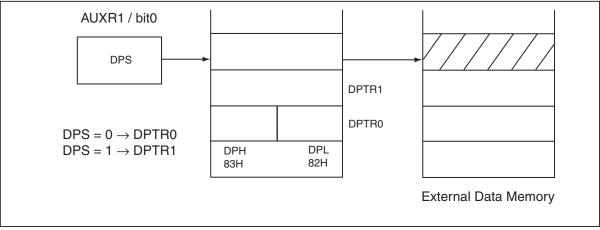

The device has two 16-bit data pointers. The DPTR Select (DPS) bit in AUXR1 determines which of the two data pointers is accessed. When DPS=0, DPTR0 is selected; when DPS=1, DPTR1 is selected. Quickly switching between the two data pointers can be accomplished by a single INC instruction on AUXR1. (See Figure 8)

Figure 8: Dual Data Pointer Organization

### **Special Function Registers**

Most of the unique features of the FlashFlex microcontroller family are controlled by bits in special function registers (SFRs) located in the SFR memory map shown in Table 5. Individual descriptions of each SFR are provided and reset values indicated in Tables 6 to 10.

|     |                    |       |        | 8 BY   | TES    |        |        |      |

|-----|--------------------|-------|--------|--------|--------|--------|--------|------|

| F8H | IP1 <sup>1</sup>   | СН    | CCAP0H | CCAP1H | CCAP2H | ССАРЗН | CCAP4H |      |

| F0H | B <sup>1</sup>     |       |        |        |        |        |        | IP1H |

| E8H | IEA <sup>1</sup>   | CL    | CCAP0L | CCAP1L | CCAP2L | CCAP3L | CCAP4L |      |

| E0H | ACC <sup>1</sup>   |       |        |        |        |        |        |      |

| D8H | CCON <sup>1</sup>  | CMOD  | CCAPM0 | CCAPM1 | CCAPM2 | CCAPM3 | CCAPM4 |      |

| D0H | PSW <sup>1</sup>   |       |        |        |        | SPCR   |        |      |

| C8H | T2CON <sup>1</sup> | T2MOD | RCAP2L | RCAP2H | TL2    | TH2    |        |      |

| C0H | WDTC <sup>1</sup>  |       |        |        |        |        |        |      |

| B8H | IP <sup>1</sup>    | SADEN |        |        |        |        |        |      |

| B0H | P3 <sup>1</sup>    | SFCF  | SFCM   | SFAL   | SFAH   | SFDT   | SFST   | IPH  |

| A8H | IE <sup>1</sup>    | SADDR | SPSR   |        |        |        | XICON  |      |

| A0H | P2 <sup>1</sup>    |       | AUXR1  |        |        | P4     |        |      |

| 98H | SCON <sup>1</sup>  | SBUF  |        |        |        |        |        |      |

| 90H | P1 <sup>1</sup>    |       |        |        |        |        |        |      |

| 88H | TCON <sup>1</sup>  | TMOD  | TL0    | TL1    | TH0    | TH1    | AUXR   |      |

| 80H | P0 <sup>1</sup>    | SP    | DPL    | DPH    |        | WDTD   | SPDR   | PCON |

Table 5:

FlashFlex SFR Memory Map

1. Bit addressable SFRs

#### Not Recommended for New Designs

|        |                             | Direct  | E     | Bit Addr                                                                                  | ess, Sy | /mbc | ol, or Alte | rnative Port Fu | unctio | n    | Reset     |  |  |  |

|--------|-----------------------------|---------|-------|-------------------------------------------------------------------------------------------|---------|------|-------------|-----------------|--------|------|-----------|--|--|--|

| Symbol | Description                 | Address | MSB   | MSB LSB                                                                                   |         |      |             |                 |        |      |           |  |  |  |

| SFCF   | SuperFlash<br>Configuration | B1H     | -     | IAPEN                                                                                     | -       | -    | -           | -               | SWR    | BSEL | x0xxxx00b |  |  |  |

| SFCM   | SuperFlash<br>Command       | B2H     | FIE   | FIE FCM[6:0]                                                                              |         |      |             |                 |        |      |           |  |  |  |

| SFAL   | SuperFlash<br>Address Low   | B3H     | Super | SuperFlash Low Order Byte Address Register - $A_7$ to $A_0$ (SFAL)                        |         |      |             |                 |        |      |           |  |  |  |

| SFAH   | SuperFlash<br>Address High  | B4H     | Su    | SuperFlash High Order Byte Address Register - A <sub>15</sub> to A <sub>8</sub><br>(SFAH) |         |      |             |                 |        |      |           |  |  |  |

| SFDT   | SuperFlash<br>Data          | B5H     |       | SuperFlash Data Register                                                                  |         |      |             |                 |        |      | 00H       |  |  |  |

| SFST   | SuperFlash<br>Status        | B6H     | SB1_i | SB2_i                                                                                     | SB3_i   | -    | EDC_i       | FLASH_BUSY      | -      | -    | 000x00xxb |  |  |  |

### Table 7: Flash Memory Programming SFRs

T0-0.0 25114

### Table 8: Watchdog Timer SFRs

|                   |                               | Direct  | В   | Bit Address, Symbol, or Alternative Port Function |   |       |      |      |     |      |           |  |

|-------------------|-------------------------------|---------|-----|---------------------------------------------------|---|-------|------|------|-----|------|-----------|--|

| Symbol            | Description                   | Address | MSB |                                                   |   |       |      |      |     | LSB  | Value     |  |

| WDTC <sup>1</sup> | Watchdog Timer<br>Control     | C0H     | -   | -                                                 | - | WDOUT | WDRE | WDTS | WDT | SWDT | xxx00x00b |  |

| WDTD              | Watchdog Timer<br>Data/Reload | 85H     |     | Watchdog Timer Data/Reload                        |   |       |      |      |     |      |           |  |

1. Bit Addressable SFRs

Not Recommended for New Designs

| SPI Control Register (SP | CR)      |                                              |                                                      |                         |                           |                        |                       |            | _                     |

|--------------------------|----------|----------------------------------------------|------------------------------------------------------|-------------------------|---------------------------|------------------------|-----------------------|------------|-----------------------|

| Location                 | 7        | 6                                            | 5                                                    | 4                       | 3                         | 2                      | 1                     | 0          | Reset Value           |

| D5H                      | SPIE     | SPE                                          | DORD                                                 | MSTR                    | CPOL                      | CPHA                   | SPR1                  | SPR0       | 00H                   |

| Symbol                   | Fu       | inction                                      |                                                      |                         |                           |                        |                       |            |                       |

| SPIE                     | lf       | both SPIE                                    | and ES a                                             | re set to o             | ne, SPI in                | terrupts ai            | re enablec            | ł.         |                       |

| SPE                      | 0:<br>1: | PI enable I<br>Disables<br>Enables S<br>I.7. | SPI.                                                 | onnects SS              | S#, MOSI,                 | MISO, an               | d SCK to <sub>I</sub> | pins P1.4, | P1.5, P1.6,           |

| DORD                     | 0:       | MSB first                                    | nission Or<br>in data tra<br>n data trai             | insmissior              |                           |                        |                       |            |                       |

| MSTR                     | 0:       |                                              | e select.<br>lave mode<br>laster moc                 |                         |                           |                        |                       |            |                       |

| CPOL                     | 0:       |                                              | ty<br>w when id<br>gh when id                        | •                       | • •                       |                        |                       |            |                       |

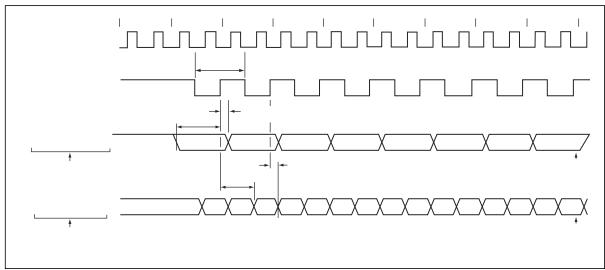

| CPHA                     | re<br>0: | lationship<br>Shift trigg                    | e control b<br>between r<br>ered on th<br>ered on th | naster and<br>e leading | d slave. Se<br>edge of th | ee Figures<br>e clock. |                       |            | ck and data           |

| SPR1, SP                 | cc       | nfigured a                                   | ate Select<br>is master.<br>K and the                | SPR1 and                | I SPR0 ha                 | ve no effe             | ct on the s           | lave. The  | evice<br>relationship |

| SPR1 | SPR0 | SCK = f <sub>OSC</sub> divided by |

|------|------|-----------------------------------|

| 0    | 0    | 4                                 |

| 0    | 1    | 16                                |

| 1    | 0    | 64                                |

| 1    | 1    | 128                               |

### **SPI Status Register (SPSR)**

| Location | 7          | 6                                                                                                                                                                           | 5          | 4 | 3            | 2           | 1        | 0 | Reset Value |  |  |  |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|--------------|-------------|----------|---|-------------|--|--|--|--|

| AAH      | SPIF       | WCOL                                                                                                                                                                        | -          | - | -            | -           | -        | - | 00xxxxxxb   |  |  |  |  |

| Symbol   | Function   |                                                                                                                                                                             |            |   |              |             |          |   |             |  |  |  |  |

| SPIF     | Up<br>If S | SPI Interrupt Flag.<br>Upon completion of data transfer, this bit is set to 1.<br>If SPIE =1 and ES =1, an interrupt is then generated.<br>This bit is cleared by software. |            |   |              |             |          |   |             |  |  |  |  |

| WCOL     | Se         | rite Collisi<br>et if the SF<br>his bit is clo                                                                                                                              | l data reg |   | itten to dui | ring data t | ransfer. |   |             |  |  |  |  |

Not Recommended for New Designs

| Location         7         6         5         4         3         2         1         0         Reset Value           86H         SPDR[7:0]         SPDR[7:0]         00H         0H         0H |       |  |  |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|--|--|--|--|--|--|

| 86H SPDR[7:0] 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Value |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Н     |  |  |  |  |  |  |  |  |  |  |  |  |

| Power Control Register (PCON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |  |  |  |  |  |  |  |

| Location         7         6         5         4         3         2         1         0         Reset Val                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Value |  |  |  |  |  |  |  |  |  |  |  |  |

| 87H SMOD1 SMOD0 BOF POF GF1 GF0 PD IDL 0001000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 000b  |  |  |  |  |  |  |  |  |  |  |  |  |

| Symbol Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |  |  |  |  |  |  |  |  |  |  |  |  |

| SMOD1 Double Baud rate bit. If SMOD1 = 1, Timer 1 is used to generate the baud rate, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | , and |  |  |  |  |  |  |  |  |  |  |  |  |

| the serial port is used in modes 1, 2, and 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |  |  |  |  |  |  |  |

| SMOD0 FE/SM0 Selection bit.<br>0: SCON[7] = SM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |  |  |  |  |  |  |  |  |  |  |  |  |

| 1: SCON[7] = FE,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |  |  |  |  |  |  |  |  |  |  |  |  |

| BOF Brown-out detection status bit, this bit will not be affected by any other reset. BOF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OF    |  |  |  |  |  |  |  |  |  |  |  |  |

| should be cleared by software. Power-on reset will also clear the BOF bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |  |  |  |  |  |  |  |  |  |  |  |  |

| 0: No brown-out.<br>1: Brown-out occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |  |  |  |  |  |  |  |  |  |  |  |  |

| POF Power-on reset status bit, this bit will not be affected by any other reset. POF should be affected by any other reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | hould |  |  |  |  |  |  |  |  |  |  |  |  |

| be cleared by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | louiu |  |  |  |  |  |  |  |  |  |  |  |  |

| 0: No Power-on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |  |  |  |  |  |  |  |  |  |  |  |  |

| 1: Power-on reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |  |  |  |  |  |  |  |  |  |  |  |  |

| GF1 General-purpose flag bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |  |  |  |  |  |  |  |

| GF0 General-purpose flag bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |  |  |  |  |  |  |  |

| PD Power-down bit, this bit is cleared by hardware after exiting from power-down mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | node. |  |  |  |  |  |  |  |  |  |  |  |  |

| 0: Power-down mode is not activated.<br>1: Activates Power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |  |  |  |  |  |  |  |  |  |  |  |  |

| IDL Idle mode bit, this bit is cleared by hardware after exiting from idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |  |  |  |  |  |  |  |  |  |  |  |  |

| 0: Idle mode is not activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |  |  |  |  |  |  |  |  |  |  |  |  |

| 1: Activates idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |  |  |  |  |  |  |  |  |  |  |  |  |

Not Recommended for New Designs

|                 |                                                         | T2CON                         |                               |

|-----------------|---------------------------------------------------------|-------------------------------|-------------------------------|

|                 | Mode                                                    | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|                 | 16-bit Auto-Reload                                      | 00H                           | 08H                           |

|                 | 16-bit Capture                                          | 01H                           | 09H                           |

| Used as Timer   | Baud rate generator receive and transmit same baud rate | 34H                           | 36H                           |

|                 | Receive only                                            | 24H                           | 26H                           |

|                 | Transmit only                                           | 14H                           | 16H                           |

|                 | 16-bit Auto-Reload                                      | 02H                           | 0AH                           |

| Used as Counter | 16-bit Capture                                          | 03H                           | 0BH                           |

### Table 16:Timer/Counter 2

1. Capture/Reload occurs only on timer/counter overflow.

T0-0.0 25114

2. Capture/Reload occurs on timer/counter overflow and a 1 to 0 transition on T2EX (P1.1) pin except when Timer 2 is used in the baud rate generating mode.

### **Programmable Clock-Out**

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

- 1. to input the external clock for Timer/Counter 2, or

- 2. to output a 50% duty cycle clock ranging from 122 Hz to 8 MHz at a 16 MHz operating frequency (61 Hz to 4 MHz in 12 clock mode).

To configure Timer/Counter 2 as a clock generator, bit

C/#T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

Oscillator Frequency n x (65536 - RCAP2H, RCAP2L)

n =2 (in 6 clock mode) 4 (in 12 clock mode)

Where (RCAP2H, RCAP2L) = the contents of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode, Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will not be the same.

Not Recommended for New Designs

### Watchdog Timer

The device offers a programmable Watchdog Timer (WDT) for fail safe protection against software deadlock and automatic recovery.

To protect the system against software deadlock, the user software must refresh the WDT within a user-defined time period. If the software fails to do this periodical refresh, an internal hardware reset will be initiated if enabled (WDRE= 1). The software can be designed such that the WDT times out if the program does not work properly.

The WDT in the device uses the system clock (XTAL1) as its time base. So strictly speaking, it is a watchdog counter rather than a watchdog timer. The WDT register will increment every 344,064 crystal clocks. The upper 8-bits of the time base register (WDTD) are used as the reload register of the WDT.

The WDTS flag bit is set by WDT overflow and is not changed by WDT reset. User software can clear WDTS by writing "1" to it.

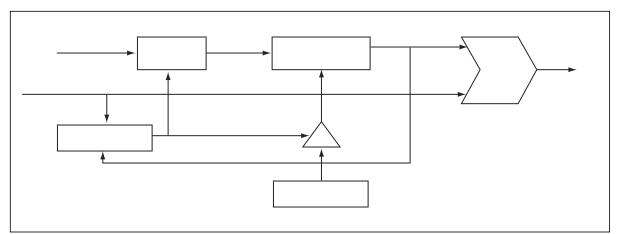

Figure 23 provides a block diagram of the WDT. Two SFRs (WDTC and WDTD) control watchdog timer operation. During idle mode, WDT operation is temporarily suspended, and resumes upon an interrupt exit from idle.

The time-out period of the WDT is calculated as follows:

Period = (255 - WDTD) \* 344064 \* 1/f<sub>CLK (XTAL1)</sub>

where WDTD is the value loaded into the WDTD register and f<sub>OSC</sub> is the oscillator frequency.

Figure 23: Block Diagram of Programmable Watchdog Timer

Not Recommended for New Designs

### 16-Bit Software Timer Mode

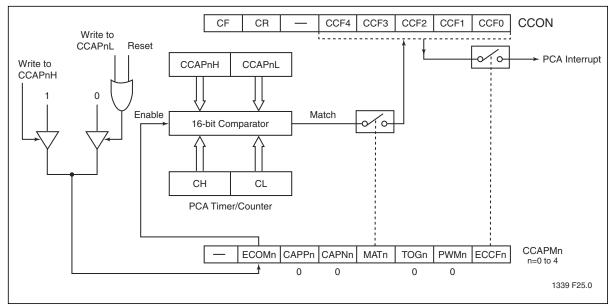

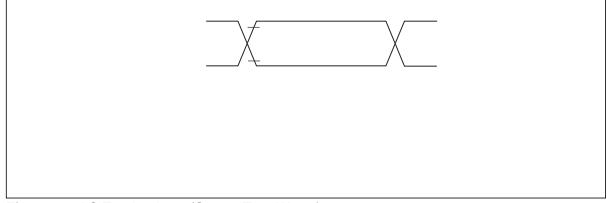

The 16-bit software timer mode is used to trigger interrupt routines, which must occur at periodic intervals. It is setup by setting both the ECOM and MAT bits in the module's CCAPMn register. The PCA timer will be compared to the module's capture registers (CCAPnL and CCAPnH) and when a match occurs, an interrupt will occur, if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

If necessary, a new 16-bit compare value can be loaded into CCAPnH and CCAPnL during the interrupt routine. The user should be aware that the hardware temporarily disables the comparator function while these registers are being updated so that an invalid match will not occur. Thus, it is recommended that the user write to the low byte first (CCAPnL) to disable the comparator, then write to the high byte (CCAPnH) to re-enable it. If any updates to the registers are done, the user may want to hold off any interrupts from occurring by clearing the EA bit. (See Figure 26)

Figure 26: PCA Compare Mode (Software Timer)

#### Not Recommended for New Designs

|       | Security Lock Bits <sup>1,2</sup> |        |                  | Security Status of: |           |           |                                                                                                                                                                                                                              |

|-------|-----------------------------------|--------|------------------|---------------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Level | SFST[7:5]                         | SB1    | SB2 <sup>1</sup> | SB3 <sup>1</sup>    | Block 1   | Block 0   | Security Type                                                                                                                                                                                                                |

| 1     | 000                               | U      | U                | U                   | Unlock    | Unlock    | No Security Features are<br>Enabled.                                                                                                                                                                                         |