#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                           |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 40MHz                                                                          |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                               |

| Number of I/O              | 32                                                                             |

| Program Memory Size        | 24KB (24K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · .                                                                            |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                    |

| Data Converters            | -                                                                              |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | 0°C ~ 70°C                                                                     |

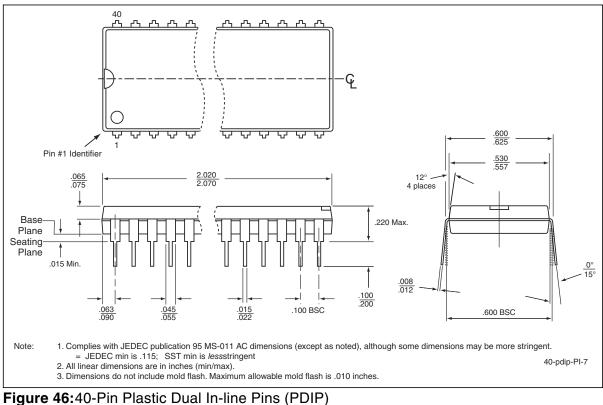

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                       |

| Supplier Device Package    | 40-PDIL                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e54rda-40-c-pie |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Not Recommended for New Designs

| Symbol               | Type <sup>1</sup>             | Name and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3[7:0]              | I/O with internal<br>pull-up  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can drive LS TTL inputs. Port 3 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also receives some control signals and high-order address bits during the external host mode programming and verification.                                                                                           |

| P3[0]                | I                             | <b>RXD:</b> Universal Asynchronous Receiver/Transmitter (UART) - Receive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P3[1]                | 0                             | TXD: UART - Transmit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[2]                | I                             | INT0#: External Interrupt 0 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P3[3]                | I                             | INT1#: External Interrupt 1 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P3[4]                | I                             | T0: External count input to Timer/Counter 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[5]                | I                             | T1: External count input to Timer/Counter 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[6]                | 0                             | WR#: External Data Memory Write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P3[7]                | 0                             | RD#: External Data Memory Read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PSEN#                | I/O                           | <b>Program Store Enable:</b> PSEN# is the Read strobe to External Program Store. When the device is executing from Internal Program Memory, PSEN# is inactive ( $V_{OH}$ ). When the device is executing code from External Program Memory, PSEN# is activated twice each machine cycle, except when access to External Data Memory while one PSEN# activation is skipped in each machine cycle. A forced high-to-low input transition on the PSEN# pin while the RST input is continually held high for more than 20 machine cycles will cause the device to enter External Host mode for programming. |

| RST                  | I                             | <b>Reset:</b> While the oscillator is running, a high logic state on this pin for two machine cycles will reset the device. After a reset, if the PSEN# pin is driven by a high-to-low input transition while the RST input pin is held high, the device will enter the External Host mode, otherwise the device will enter the Normal operation mode.                                                                                                                                                                                                                                                  |

| EA#                  | I                             | <b>External Access Enable:</b> EA# must be driven to $V_{IL}$ in order to enable the device to fetch code from the External Program Memory. EA# must be driven to $V_{IH}$ for internal program execution. However, Security lock level 4 will disable EA#, and program execution is only possible from internal program memory.                                                                                                                                                                                                                                                                        |

| ALE/PROG#            | I/O                           | <b>Address Latch Enable:</b> ALE is the output signal for latching the low byte of the address during an access to external memory. This pin is also the programming pulse input (PROG#) for flash programming. Normally the ALE <sup>2</sup> is emitted at a constant rate of 1/6 the crystal frequency <sup>3</sup> and can be used for external timing and clocking. One ALE pulse is skipped during each access to external data memory. However, if AO is set to 1, ALE is disabled.                                                                                                               |

| P4[3:0] <sup>4</sup> | I/O with internal<br>pull-ups | <b>Port 4:</b> Port 4 is an 4-bit bi-directional I/O port with internal pull-ups. The port 4 output buffers can drive LS TTL inputs. Port 4 pins are pulled high by the inter nal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, port 4 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                           |

| P4[0]                | I/O                           | Bit 0 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P4[1]                | I/O                           | Bit 1 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P4[2] / INT3#        | I/O                           | Bit 2 of port 4 / INT3# External interrupt 3 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P4[3] / INT2#        | I/O                           | Bit 3 of port 4 / INT2# External interrupt 2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1: Pin Descriptions (Continued) (2 of 3)

Not Recommended for New Designs

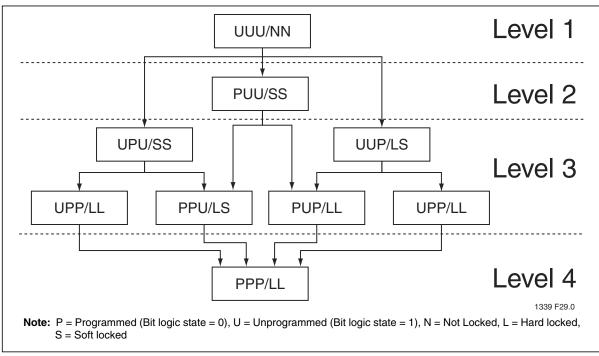

### **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0 and/or SC1. The SC0 and SC1 bits are programmed via an external host mode command or an IAP Mode command. See Table 13.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

|                  |                  |                               | State of SFCF[1:0] after:       |                |  |  |  |  |  |  |

|------------------|------------------|-------------------------------|---------------------------------|----------------|--|--|--|--|--|--|

| SC1 <sup>1</sup> | SC0 <sup>1</sup> | Power-on or External<br>Reset | WDT Reset or Brown-out<br>Reset | Software Reset |  |  |  |  |  |  |

| U (1)            | U (1)            | 00 (default)                  | x0                              | 10             |  |  |  |  |  |  |

| U (1)            | P (0)            | 01                            | x1                              | 11             |  |  |  |  |  |  |

| P (0)            | U (1)            | 10                            | 10                              | 10             |  |  |  |  |  |  |

| P (0)            | P (0)            | 11                            | 11                              | 11             |  |  |  |  |  |  |

|                  | •                | •                             |                                 | T0-0.0 251     |  |  |  |  |  |  |

#### Table 3: SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

### Data RAM Memory

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

#### Not Recommended for New Designs

| Cumh               |                                  | Direct<br>Addres | Bit       | Address   | , Symb | ol, or  | Alterna | tive Po | ort Functio | n    | Reset     |  |  |

|--------------------|----------------------------------|------------------|-----------|-----------|--------|---------|---------|---------|-------------|------|-----------|--|--|

| Symb<br>ol         | Description                      | Addres<br>S      | MSB       |           |        |         |         |         |             | LSB  | Value     |  |  |

| ACC <sup>1</sup>   | Accumulator                      | E0H              |           |           |        | ACC     | C[7:0]  |         |             |      | 00H       |  |  |

| B <sup>1</sup>     | B Register                       | F0H              | B[7:0]    |           |        |         |         |         |             |      |           |  |  |

| PSW <sup>1</sup>   | Program Status<br>Word           | D0H              | CY        | AC        | F0     | RS1     | RS0     | OV      | F1          | Р    | 00H       |  |  |

| SP                 | Stack Pointer                    | 81H              |           | SP[7:0]   |        |         |         |         |             |      |           |  |  |

| DPL                | Data Pointer<br>Low              | 82H              |           | DPL[7:0]  |        |         |         |         |             |      |           |  |  |

| DPH                | Data Pointer<br>High             | 83H              |           | DPH[7:0]  |        |         |         |         |             |      |           |  |  |

| IE <sup>1</sup>    | Interrupt Enable                 | A8H              | EA        | EC        | ET2    | ES      | ET1     | EX1     | ET0         | EX0  | 00H       |  |  |

| IEA <sup>1</sup>   | Interrupt<br>Enable A            | E8H              | -         | -         | -      | -       | EBO     | -       | -           | -    | xxxx0xxxb |  |  |

| IP <sup>1</sup>    | Interrupt Priority<br>Reg        | B8H              | -         | PPC       | PT2    | PS      | PT1     | PX1     | PT0         | PX0  | x0000000b |  |  |

| IPH                | Interrupt Priority<br>Reg High   | B7H              | -         | PPCH      | PT2H   | PSH     | PT1H    | PX1H    | PT0H        | PX0H | x0000000b |  |  |

| IP1 <sup>1</sup>   | Interrupt Priority<br>Reg A      | F8H              | -         | -         | -      | -       | PBO     | PX3     | PX2         | -    | xxxx0xxxb |  |  |

| IP1H               | Interrupt Priority<br>Reg A High | F7H              | -         | -         | -      | -       | PBOH    | PX3H    | PX3         | -    | xxxx0xxxb |  |  |

| PCON               | Power Control                    | 87H              | SMOD<br>1 | SMOD<br>0 | BOF    | PO<br>F | GF1     | GF0     | PD          | IDL  | 00010000b |  |  |

| AUXR               | Auxiliary Reg                    | 8EH              | -         | -         | -      | -       | -       | -       | EXTRAM      | AO   | xxxxxx00b |  |  |

| AUXR1              | Auxiliary Reg 1                  | A2H              | -         | -         | -      | -       | GF2     | 0       | -           | DPS  | xxxx00x0b |  |  |

| XICON <sup>2</sup> | External<br>Interrupt Control    | AEH              | х         | EX3       | IE3    | IT3     | 0       | EX2     | IE2         | IT2  | 00H       |  |  |

### Table 6: CPU related SFRs

1. Bit Addressable SFRs

2. X = Don't care

#### Not Recommended for New Designs

|                    |                              | Direct  | B    | it Addro    | ess, Sy | mbol, c | or Alterna | ative P | ort Fun | ction   | Reset        |

|--------------------|------------------------------|---------|------|-------------|---------|---------|------------|---------|---------|---------|--------------|

| Symbol             | Description                  | Address | MSB  |             |         |         |            |         |         | LSB     | Value        |

| TMOD               | Timer/Counter                | 89H     |      | Tim         | er 1    |         |            | Ti      | mer 0   |         | 00H          |

|                    | Mode Control                 |         | GATE | C/T#        | M1      | MO      | GATE       | C/T#    | M1      | MO      |              |

| TCON <sup>1</sup>  | Timer/Counter<br>Control     | 88H     | TF1  | TR1         | TF0     | TR0     | IE1        | IT1     | IE0     | IT0     | 00H          |

| TH0                | Timer 0 MSB                  | 8CH     |      |             |         | Tł      | H0[7:0]    |         |         |         | 00H          |

| TL0                | Timer 0 LSB                  | 8AH     |      | TL0[7:0]    |         |         |            |         |         |         | 00H          |

| TH1                | Timer 1 MSB                  | 8DH     |      | TH1[7:0]    |         |         |            |         |         |         | 00H          |

| TL1                | Timer 1 LSB                  | 8BH     |      | TL1[7:0]    |         |         |            |         |         |         | 00H          |

| T2CON <sup>1</sup> | Timer / Counter 2<br>Control | C8H     | TF2  | EXF2        | RCLK    | TCLK    | EXEN2      | TR2     | C/T2#   | CP/RL2# | 00H          |

| T2MOD <sup>2</sup> | Timer2<br>Mode Control       | C9H     | Х    | -           | -       | -       | -          | -       | T2OE    | DCEN    | xxxxxx00b    |

| TH2                | Timer 2 MSB                  | CDH     |      |             |         | Tł      | H2[7:0]    |         |         |         | 00H          |

| TL2                | Timer 2 LSB                  | ССН     |      |             |         | TI      | _2[7:0]    |         |         |         | 00H          |

| RCAP2H             | Timer 2<br>Capture MSB       | СВН     |      | RCAP2H[7:0] |         |         |            |         |         |         | 00H          |

| RCAP2L             | Timer 2<br>Capture LSB       | CAH     |      |             |         | RCA     | AP2L[7:0]  |         |         |         | 00H          |

|                    |                              |         |      |             |         |         |            |         |         |         | T0-0.0 25114 |

#### Table 9: Timer/Counters SFRs

1. Bit Addressable SFRs

2. X = Don't care

#### Table 10: Interface SFRs

|                   |                         | Direct  | Bit A   | ddress     | , Symbo | ol, or A | ternati | ve Port | Functi | on   | RESET |

|-------------------|-------------------------|---------|---------|------------|---------|----------|---------|---------|--------|------|-------|

| Symbol            | Description             | Address | MSB     |            |         |          |         |         |        | LSB  | Value |

| SBUF              | Serial Data Buffer      | 99H     |         | SBUF[7:0]  |         |          |         |         |        |      |       |

| SCON <sup>1</sup> | Serial Port Control     | 98H     | SM0/FE  | SM1        | SM2     | REN      | TB8     | RB8     | TI     | RI   | 00H   |

| SADDR             | Slave Address           | A9H     |         |            |         | SADDR    | [7:0]   |         |        |      | 00H   |

| SADEN             | Slave Address<br>Mask   | B9H     |         | SADEN[7:0] |         |          |         |         |        |      |       |

| SPCR              | SPI Control<br>Register | D5H     | SPIE    | SPE        | DORD    | MSTR     | CPOL    | CPHA    | SPR1   | SPR0 | 04H   |

| SPSR              | SPI Status<br>Register  | AAH     | SPIF    | WCOL       |         |          |         |         |        |      | 00H   |

| SPDR              | SPI Data Register       | 86H     |         |            | -       | SPDR[    | 7:0]    |         |        |      | 00H   |

| P0 <sup>1</sup>   | Port 0                  | 80H     |         |            |         | P0[7:    | 0]      |         |        |      | FFH   |

| P1 <sup>1</sup>   | Port 1                  | 90H     | -       | -          | -       | -        | -       | -       | T2EX   | T2   | FFH   |

| P2 <sup>1</sup>   | Port 2                  | A0H     | P2[7:0] |            |         |          |         |         |        | FFH  |       |

| P3 <sup>1</sup>   | Port 3                  | B0H     | RD#     | WR#        | T1      | Т0       | INT1#   | INT0#   | TXD    | RXD  | FFH   |

| P4 <sup>2</sup>   | Port 4                  | A5H     | 1       | 1          | 1       | 1        | P4.3    | P4.2    | P4.1   | P4.0 | FFH   |

1. Bit Addressable SFRs

2. P4 is similar to P1 and P3 ports

T0-0.0 25114

#### Not Recommended for New Designs

### SuperFlash Configuration Register (SFCF)

| -        | -  | • •                               |           |           |   |   |     |      |             |

|----------|----|-----------------------------------|-----------|-----------|---|---|-----|------|-------------|

| Location | 7  | 6                                 | 5         | 4         | 3 | 2 | 1   | 0    | Reset Value |

| B1H      | -  | IAPEN                             | -         | -         | - | - | SWR | BSEL | x0xxxx00b   |

| Symbol   | Fu | unction                           |           |           |   |   |     |      |             |

| IAPEN    | 0: | nable IAP<br>IAP comn<br>IAP comn | nands are |           |   |   |     |      |             |

| SWR      |    | oftware Re<br>ee Section          |           | re Reset" |   |   |     |      |             |

| BSEL     |    | rogram me<br>ee Figures           | -         |           | • |   |     |      |             |

#### SuperFlash Command Register (SFCM)

| Location | 7        | 6                                                     | 5                        | 4                   | 3    | 2         | 1        | 0    | Reset Value            |

|----------|----------|-------------------------------------------------------|--------------------------|---------------------|------|-----------|----------|------|------------------------|

| B2H      | FIE      | FCM6                                                  | FCM5                     | FCM4                | FCM3 | FCM2      | FCM1     | FCM0 | ] оон                  |

| Symbol   | Fu       | unction                                               |                          |                     |      |           |          |      |                        |

| FIE      | 0:       | ash Interru<br>INT1# is r<br>INT1# is r<br>External I | not reassi<br>re-assigne | gned.<br>d to signa |      | ation com | pletion. |      |                        |

| FCM[6:0] | 00       | ash opera<br>)0_0001b(<br>)0_1011b{                   | Chip-Erase               | Э                   |      |           |          |      |                        |

|          | 00       | 00_1101bE                                             | Block-Eras               | e                   |      |           |          |      |                        |

|          | 00       | 0_1110bE                                              | Prog-SB1                 | am                  |      |           |          |      |                        |

|          | 00       | )0_0011bF<br>)0_0101bF<br>)0_1001bF                   | Prog-SB3                 |                     |      |           |          |      |                        |

|          | 00<br>00 | 00_1001bF<br>00_1000bE                                | Prog-SC1<br>Enable-Clo   |                     |      |           |          |      |                        |

|          |          | , ,                                                   |                          |                     | •    |           |          |      | e.<br>ot regardless of |

### SuperFlash Address Registers (SFAL)

| Location              | 7 | 6                                         | 5            | 4           | 3            | 2           | 1         | 0         | Reset Value |

|-----------------------|---|-------------------------------------------|--------------|-------------|--------------|-------------|-----------|-----------|-------------|

| B3H                   |   | 5                                         | SuperFlash   | Low Order   | Byte Addre   | ess Registe | r         |           | 00H         |

| <b>Symbol</b><br>SFAL | M | <b>inction</b><br>ailbox regi<br>gister). | ster for int | terfacing v | vith flash n | nemory bl   | ock. (Low | order add | ress        |

#### Not Recommended for New Designs

| Location              | 7          | 6                         | 5           | 4               | 3           | 2          | 1           | 0          | Reset Value    |

|-----------------------|------------|---------------------------|-------------|-----------------|-------------|------------|-------------|------------|----------------|

| 85H                   |            |                           | Wa          | atchdog Tim     | er Data/Re  | load       | •           |            | 00H            |

| Symbol                | F          | unction                   |             |                 |             |            |             |            |                |

| WDTD                  | lı         | nitial/Reloa              | d value ir  | Watchdog        | g Timer. N  | ew value v | won't be e  | ffective u | ntil WDT is    |

|                       | S          | et.                       |             | -               | -           |            |             |            |                |

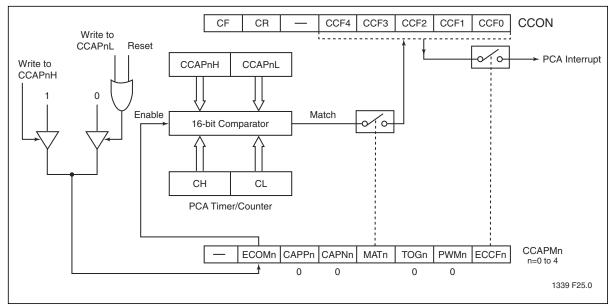

| CA Timer/Counter Cont | ol Pogi    | stor1 (CCC                |             |                 |             |            |             |            |                |

| Location              | 7          |                           | 5           | 4               | 3           | 2          | 1           | 0          | Reset Value    |

| D8H                   | CF         | CR                        | -           | CCF4            | CCF3        | CCF2       | CCF1        | CCF0       |                |

|                       | 1. Bit add |                           |             | 0014            | 0010        | 0012       | 0011        |            |                |

| Currence of           | -          |                           |             |                 |             |            |             |            |                |

| Symbol                |            | unction                   |             | -               |             |            |             |            |                |

| CF                    |            | CA Count                  |             | •               |             |            |             |            |                |

|                       |            |                           |             | n the coun      |             |            |             |            |                |

|                       |            | oftware.                  | et. CF may  | / be set by     | eitner naro | aware or s | offware, b  | ut can on  | ly cleared b   |

|                       | -          |                           | _           |                 |             |            |             |            |                |

| CR                    |            | CA Count                  |             |                 |             |            |             |            |                |

|                       |            | -                         |             | n the PCA       | counter o   | n. Must be | e cleared t | by softwar | re to turn the |

|                       |            | CA counte                 |             |                 |             |            |             |            |                |

| -                     |            | •                         | -           | served for f    |             |            |             |            |                |

|                       |            |                           |             | e '1's to reser |             |            |             |            |                |

| CCF4                  |            |                           |             | ıpt flag. Se    | t by hardw  | vare when  | a match o   | or capture | occurs.        |

|                       | N          | lust be cle               | ared by s   | oftware.        |             |            |             |            |                |

| CCF3                  |            |                           |             | ıpt flag. Se    | t by hardw  | vare when  | a match o   | or capture | occurs.        |

|                       | Ν          | lust be cle               | ared by s   | oftware.        |             |            |             |            |                |

| CCF2                  |            |                           |             | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |

|                       | Ν          | /lust be cle              | ared by s   | oftware.        |             |            |             |            |                |

|                       |            |                           |             |                 |             |            |             |            |                |

| CCF1                  | F          | CA Modul                  | e 1 interru | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |

| CCF1                  |            | PCA Modul<br>/lust be cle |             |                 | t by hardw  | are when   | a match o   | or capture | occurs.        |

| CCF1<br>CCF0          | Ν          | lust be cle               | ared by s   |                 | -           |            |             |            |                |

(max. rate =  $f_{OSC}/4$  in 6 clock mode,  $f_{OSC}/8$  in 12 clock mode)

#### Not Recommended for New Designs

|          | onogiotoi    | (0110)                                                                                                                                                 | •)             |                   |               |              |               |                | _            |  |  |  |  |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|---------------|--------------|---------------|----------------|--------------|--|--|--|--|

| Location | 7            | 6                                                                                                                                                      | 5              | 4                 | 3             | 2            | 1             | 0              | Reset Value  |  |  |  |  |

| D9H      | CIDL         | WDTE                                                                                                                                                   | -              | -                 | -             | CPS1         | CPS0          | ECF            | 00xxx000b    |  |  |  |  |

|          | 1. Not bit a | ddressable                                                                                                                                             | )              |                   | •             | •            | •             | •              | -            |  |  |  |  |

| Symbol   | Fu           | Function                                                                                                                                               |                |                   |               |              |               |                |              |  |  |  |  |

| CIDL     | Co           | Counter Idle Control:                                                                                                                                  |                |                   |               |              |               |                |              |  |  |  |  |

|          |              | <ul><li>0: Programs the PCA Counter to continue functioning during idle mode</li><li>1: Programs the PCA Counter to be gated off during idle</li></ul> |                |                   |               |              |               |                |              |  |  |  |  |

| WDTE     |              | •                                                                                                                                                      | Timer Enat     |                   |               |              |               |                |              |  |  |  |  |

|          |              | 0: Disables Watchdog Timer function on PCA module 4                                                                                                    |                |                   |               |              |               |                |              |  |  |  |  |

|          |              | 1: Enables Watchdog Timer function on PCA module 4                                                                                                     |                |                   |               |              |               |                |              |  |  |  |  |

| -        |              | •                                                                                                                                                      | ented, res     |                   |               |              |               |                |              |  |  |  |  |

|          | Not          | e: User sh                                                                                                                                             | ould not write | e '1's to reser   | ved bits. The | e value read | from a reserv | ved bit is ind | leterminate. |  |  |  |  |

| CPS1     | PC           | A Count                                                                                                                                                | Pulse Sel      | ect bit 1         |               |              |               |                |              |  |  |  |  |

| CPS0     | PC           | A Count                                                                                                                                                | Pulse Sel      | ect bit 2         |               |              |               |                |              |  |  |  |  |

|          |              |                                                                                                                                                        |                |                   |               |              |               |                |              |  |  |  |  |

|          |              |                                                                                                                                                        | Selec          | ted               |               |              |               |                |              |  |  |  |  |

|          | CI           | PS1 CP                                                                                                                                                 | S0 PCA Ir      | nput <sup>1</sup> |               |              |               |                |              |  |  |  |  |

|          |              | 0 0 0 Internal clock, f <sub>OSC</sub> /6 in 6 clock mode (f <sub>OSC</sub> /12 in 12 clock mode)                                                      |                |                   |               |              |               |                |              |  |  |  |  |

|          |              | 0 1 1 Internal clock, f <sub>OSC</sub> /2 in 6 clock mode (f <sub>OSC</sub> /4 in 12 clock mode)                                                       |                |                   |               |              |               |                |              |  |  |  |  |

|          |              | 1 0 2 Timer 0 overflow                                                                                                                                 |                |                   |               |              |               |                |              |  |  |  |  |

|          |              | 1 1                                                                                                                                                    | 3              | Exte              | rnal clock at | ECI/P1.2 pir | 1             |                |              |  |  |  |  |

#### PCA Timer/Counter Mode Register<sup>1</sup> (CMOD)

ECF

1. f<sub>OSC</sub> = oscillator frequency

PCA Enable Counter Overflow interrupt:

0: Disables the CF bit in CCON

1: Enables CF bit in CCON to generate an interrupt

Not Recommended for New Designs

| Location         7         6         5         4         3         2         1         0         Reset Value           86H         SPDR[7:0]         SPDR[7:0]         00H         0H         0H |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 86H SPDR[7:0] 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Value |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Н     |

| Power Control Register (PCON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Location         7         6         5         4         3         2         1         0         Reset Val                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Value |

| 87H SMOD1 SMOD0 BOF POF GF1 GF0 PD IDL 0001000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 000b  |

| Symbol Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| SMOD1 Double Baud rate bit. If SMOD1 = 1, Timer 1 is used to generate the baud rate, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | , and |

| the serial port is used in modes 1, 2, and 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| SMOD0 FE/SM0 Selection bit.<br>0: SCON[7] = SM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| 1: SCON[7] = FE,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| BOF Brown-out detection status bit, this bit will not be affected by any other reset. BOF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OF    |

| should be cleared by software. Power-on reset will also clear the BOF bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 0: No brown-out.<br>1: Brown-out occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| POF Power-on reset status bit, this bit will not be affected by any other reset. POF should be affected by any other reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | hould |

| be cleared by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | louiu |

| 0: No Power-on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| 1: Power-on reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| GF1 General-purpose flag bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| GF0 General-purpose flag bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| PD Power-down bit, this bit is cleared by hardware after exiting from power-down mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | node. |

| 0: Power-down mode is not activated.<br>1: Activates Power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| IDL Idle mode bit, this bit is cleared by hardware after exiting from idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 0: Idle mode is not activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 1: Activates idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

Not Recommended for New Designs

### Sector-Erase

The Sector-Erase command erases all of the bytes in a sector. The sector size for the flash memory blocks is 128 Bytes. The selection of the sector to be erased is determined by the contents of SFAH and SFAL.

Figure 11:Sector-Erase

Not Recommended for New Designs

### Prog-SB3, Prog-SB2, Prog-SB1

Prog-SB3, Prog-SB2, Prog-SB1 commands are used to program the security bits (see Table 24). Completion of any of these commands, the security options will be updated immediately.

Security bits previously in un-programmed state can be programmed by these commands. Prog-SB3, Prog-SB2 and Prog-SB1 commands should only reside in Block 1 or external code memory.

Figure 14: Prog-SB3, Prog-SB2, Prog-SB1

Not Recommended for New Designs

| W  | Without Interrupt enabled |                    |                    |                   |                     |                   |                    |                                                              |  |  |

|----|---------------------------|--------------------|--------------------|-------------------|---------------------|-------------------|--------------------|--------------------------------------------------------------|--|--|

| _1 | ECOMy <sup>2</sup>        | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>   | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                  |  |  |

| -  | 0                         | 0                  | 0                  | 0                 | 0                   | 0                 | 0                  | No Operation                                                 |  |  |

| -  | 0                         | 1                  | 0                  | 0                 | 0                   | 0                 | 0                  | 16-bit capture on positive-edge trigger at CEX[4:0]          |  |  |

| -  | 0                         | 0                  | 1                  | 0                 | 0                   | 0                 | 0                  | 16-bit capture on negative-edge trigger at CEX[4:0]          |  |  |

| -  | 0                         | 1                  | 1                  | 0                 | 0                   | 0                 | 0                  | 16-bit capture on positive/negative-edge trigger at CEX[4:0] |  |  |

| -  | 1                         | 0                  | 0                  | 1                 | 0                   | 0                 | 0                  | Compare: software timer                                      |  |  |

| -  | 1                         | 0                  | 0                  | 1                 | 1                   | 0                 | 0                  | Compare: high-speed output                                   |  |  |

| -  | 1                         | 0                  | 0                  | 0                 | 0                   | 1                 | 0                  | Compare: 8-bit PWM                                           |  |  |

| -  | 1                         | 0                  | 0                  | 1                 | 0 or 1 <sup>3</sup> | 0                 | 0                  | Compare: PCA WDT (CCAPM4 only) <sup>4</sup>                  |  |  |

|    |                           | •                  | •                  | •                 | •                   |                   |                    | T0-0.0 25114                                                 |  |  |

### Table 21: PCA Module Modes

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

4. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

#### Table 22:PCA Module Modes

| W  | With Interrupt enabled |                    |                    |                   |                     |                   |                    |                                                              |  |  |

|----|------------------------|--------------------|--------------------|-------------------|---------------------|-------------------|--------------------|--------------------------------------------------------------|--|--|

| _1 | ECOMy <sup>2</sup>     | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>   | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                  |  |  |

| -  | 0                      | 1                  | 0                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive-edge trigger at CEX[4:0]          |  |  |

| -  | 0                      | 0                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on negative-edge trigger at CEX[4:0]          |  |  |

| -  | 0                      | 1                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive/negative-edge trigger at CEX[4:0] |  |  |

| -  | 1                      | 0                  | 0                  | 1                 | 0                   | 0                 | 1                  | Compare: software timer                                      |  |  |

| -  | 1                      | 0                  | 0                  | 1                 | 1                   | 0                 | 1                  | Compare: high-speed output                                   |  |  |

| -  | 1                      | 0                  | 0                  | 0                 | 0                   | 1                 | X <sup>3</sup>     | Compare: 8-bit PWM                                           |  |  |

| -  | 1                      | 0                  | 0                  | 1                 | 0 or 1 <sup>4</sup> | 0                 | X <sup>5</sup>     | Compare: PCA WDT (CCAPM4 only) <sup>6</sup>                  |  |  |

|    | T0-0.0 25114           |                    |                    |                   |                     |                   |                    |                                                              |  |  |

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. No PCA interrupt is needed to generate the PWM.