Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | 8051                                                                            |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 40MHz                                                                           |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 40KB (40K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | -                                                                               |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e58rd2-40-c-tqje |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Not Recommended for New Designs

## **Product Description**

The SST89E54RD2A/RDA and SST89E58RD2A/RDA are members of the FlashFlex family of 8-bit microcontroller products designed and manufactured with SST patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

The devices come with 24/40 KByte of on-chip flash EEPROM program memory which is partitioned into 2 independent program memory blocks. The primary Block 0 occupies 16/32 KByte of internal program memory space and the secondary Block 1 occupies 8 KByte of internal program memory space.

The 8-KByte secondary block can be mapped to the lowest location of the 16/32 KByte address space; it can also be hidden from the program counter and used as an independent EEPROM-like data memory.

In addition to the 24/40 KByte of EEPROM program memory on-chip and 1024 x8 bits of on-chip RAM, the devices can address up to 64 KByte of external program memory and up to 64 KByte of external RAM.

The flash memory blocks can be programmed via a standard 87C5x OTP EPROM programmer fitted with a special adapter and the firmware for SST devices. During power-on reset, the devices can be configured as either a slave to an external host for source code storage or a master to an external host for an in-application programming (IAP) operation. The devices are designed to be programmed in-system and in-application on the printed circuit board for maximum flexibility. The devices are pre-programmed with an example of the bootstrap loader in the memory, demonstrating the initial user program code loading or subsequent user code updating via the IAP operation. The sample bootstrap loader is available for the user's reference and convenience only; SST does not guarantee its functionality or usefulness. Chip-Erase or Block-Erase operations will erase the pre-programmed sample code.

Not Recommended for New Designs

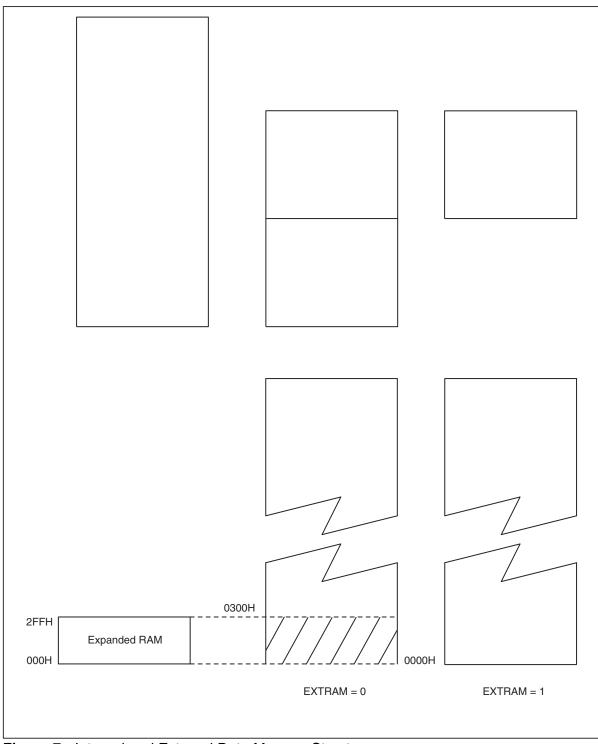

### Expanded Data RAM Addressing

The SST89E/V5xRDxA both have the capability of 1K of RAM. See Figure 7.

The device has four sections of internal data memory:

- 1. The lower 128 Bytes of RAM (00H to 7FH) are directly and indirectly addressable.

- 2. The higher 128 Bytes of RAM (80H to FFH) are indirectly addressable.

- 3. The special function registers (80H to FFH) are directly addressable only.

- 4. The expanded RAM of 768 Bytes (00H to 2FFH) is indirectly addressable by the move external instruction (MOVX) and clearing the EXTRAM bit. (See "Auxiliary Register (AUXR)" in Section , "Special Function Registers")

Since the upper 128 bytes occupy the same addresses as the SFRs, the RAM must be accessed indirectly. The RAM and SFRs space are physically separate even though they have the same addresses.

When instructions access addresses in the upper 128 bytes (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

#### Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in "#data" is written to RAM location 90H rather than port 1.

#### **Direct Access:**

MOV90H, #data; write data to P1

Data in "#data" is written to port 1. Instructions that write directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 bytes of memory is physically located on the chip and logically occupies the first 768 bytes of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 (WR#), P3.7 (RD#), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

#### Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A; DPTR contains 0A0H

DPTR points to 0A0H and data in "A" is written to address 0A0H of the expanded RAM rather than external memory. Access to external memory higher than 2FFH using the MOVX instruction will access external memory (0300H to FFFFH) and will perform in the same way as the standard 8051, with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 8051. Using MOVX @Ri provides an 8-bit address with multiplexed data on Port 0. Other output port pins can be used to output higher order address bits. This provides external paging capabilities. Using MOVX

Not Recommended for New Designs

Figure 7: Internal and External Data Memory Structure

Not Recommended for New Designs

| Location               | 7         | 6                                                                                                                     | 5             | 4          | 3          | 2              | 1          | 0        | Reset Valu |  |  |

|------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------|---------------|------------|------------|----------------|------------|----------|------------|--|--|

| B4H                    |           | SuperFlash High Order Byte Address Register                                                                           |               |            |            |                |            |          |            |  |  |

| Symbol                 | F         | unction                                                                                                               |               |            |            |                |            |          |            |  |  |

| SFAH                   |           |                                                                                                                       | ister for in  | terfacing  | with flash | memory blo     | ck (Hiah   | order ad | Idress     |  |  |

| OF ALL                 |           | egister).                                                                                                             |               | ternaoling | with haon  | memory bio     | ok. (Engli | order at |            |  |  |

| SuperFlash Data Regist | er (SFDT) |                                                                                                                       |               |            |            |                |            |          |            |  |  |

| Location               | 7         | 6                                                                                                                     | 5             | 4          | 3          | 2              | 1          | 0        | Reset Valu |  |  |

| B5H                    |           |                                                                                                                       | S             | uperFlash  | Data Regi  | ster           |            |          | 00H        |  |  |

| Symbol                 | F         | unction                                                                                                               |               |            |            |                |            |          |            |  |  |

| SFDT                   |           |                                                                                                                       | uister for in | terfacina  | with flash | memory blo     | ck (Data   | reaister | )          |  |  |

| 0101                   | IV.       |                                                                                                                       |               | terraeing  | with hash  | memory bio     | ck. (Data  | register | ).         |  |  |

| SuperFlash Status Regi | ster (SFS | T) (Read (                                                                                                            | Only Regi     | ster)      |            |                |            |          | _          |  |  |

| Location               | 7         | 6                                                                                                                     | 5             | 4          | 3          | 2              | 1          | 0        | Reset Valu |  |  |

| B6H                    | SB1_i     | SB2_i                                                                                                                 | SB3_i         | -          | EDC_i      | FLASH_BU<br>SY | -          | -        | xxxxx0xxt  |  |  |

| Symbol                 | E         | unction                                                                                                               | 11            |            | 1          | 11             |            |          |            |  |  |

| SB1_i                  |           |                                                                                                                       |               |            |            |                |            |          |            |  |  |

| SB1_i<br>SB2_i         |           | Security Bit 1 status (inverse of SB1 bit)<br>Security Bit 2 status (inverse of SB2 bit)                              |               |            |            |                |            |          |            |  |  |

| SB2_i                  |           | -                                                                                                                     | : 3 status (  |            |            |                |            |          |            |  |  |

| 000_1                  |           | -                                                                                                                     | r to Table    |            |            | options.       |            |          |            |  |  |

| EDC_i                  | D         | ouble Clo                                                                                                             | ck Status     |            |            |                |            |          |            |  |  |

|                        |           | 0: 12 clocks per machine cycle<br>1: 6 clocks per machine cycle                                                       |               |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       |               | •          | P          |                |            |          |            |  |  |

| FLASH_I                |           |                                                                                                                       | ation comp    |            |            | P command      |            |          |            |  |  |

|                        |           | <ul><li>0: Device has fully completed the last IAP command.</li><li>1: Device is busy with flash operation.</li></ul> |               |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       | -             |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       |               |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       |               |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       |               |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       |               |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       |               |            |            |                |            |          |            |  |  |

|                        |           |                                                                                                                       |               |            |            |                |            |          |            |  |  |

### Not Recommended for New Designs

| Interrupt Enable (IE) |                       |                                                       |             |        |     |     |     |     |             |  |  |

|-----------------------|-----------------------|-------------------------------------------------------|-------------|--------|-----|-----|-----|-----|-------------|--|--|

| Location              | 7                     | 6                                                     | 5           | 4      | 3   | 2   | 1   | 0   | Reset Value |  |  |

| A8H                   | EA                    | EC                                                    | ET2         | ES     | ET1 | EX1 | ET0 | EX0 | 00H         |  |  |

| Symbol                | Function              |                                                       |             |        |     |     |     |     |             |  |  |

| EA                    | 0                     | Global Interrupt Enable.<br>0 = Disable<br>1 = Enable |             |        |     |     |     |     |             |  |  |

| EC                    | PCA Interrupt Enable. |                                                       |             |        |     |     |     |     |             |  |  |

| ET2                   | T                     | Timer 2 Interrupt Enable.                             |             |        |     |     |     |     |             |  |  |

| ES                    | S                     | erial Interr                                          | upt Enable  | ).     |     |     |     |     |             |  |  |

| ET1                   | T                     | mer 1 Inte                                            | rrupt Enab  | ole.   |     |     |     |     |             |  |  |

| EX1                   | E                     | xternal 1 Ir                                          | nterrupt Er | nable. |     |     |     |     |             |  |  |

| ET0                   | T                     | mer 0 Inte                                            | rrupt Enab  | ole.   |     |     |     |     |             |  |  |

| EX0                   | E                     | xternal 0 Ir                                          | nterrupt Er | nable. |     |     |     |     |             |  |  |

## Interrupt Enable A (IEA)

| Location | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 | Reset Value |

|----------|---|---|---|---|-----|---|---|---|-------------|

| E8H      | - | - | - | - | EBO | - | - | - | xxxx0xxxb   |

| Symbol | Function                                                |

|--------|---------------------------------------------------------|

| EBO    | Brown-out Interrupt Enable.<br>1 = Enable the interrupt |

|        | 0 = Disable the interrupt                               |

### Interrupt Priority (IP)

| Location | 7 | 6   | 5   | 4  | 3   | 2   | 1   | 0   | Reset Value |

|----------|---|-----|-----|----|-----|-----|-----|-----|-------------|

| B8H      | - | PPC | PT2 | PS | PT1 | PX1 | PT0 | PX0 | x0000000b   |

| Symbol | Function                           |

|--------|------------------------------------|

| PPC    | PCA interrupt priority bit         |

| PT2    | Timer 2 interrupt priority bit     |

| PS     | Serial Port interrupt priority bit |

| PT1    | Timer 1 interrupt priority bit     |

| PX1    | External interrupt 1 priority bit  |

| PT0    | Timer 0 interrupt priority bit     |

| PX0    | External interrupt 0 priority bit  |

(max. rate =  $f_{OSC}/4$  in 6 clock mode,  $f_{OSC}/8$  in 12 clock mode)

### Not Recommended for New Designs

|          | onogiotoi    | (0110)                                                                                                                                                 | •)             |                   |                            |                            |                          |                | _            |  |  |  |  |  |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|----------------------------|----------------------------|--------------------------|----------------|--------------|--|--|--|--|--|

| Location | 7            | 6                                                                                                                                                      | 5              | 4                 | 3                          | 2                          | 1                        | 0              | Reset Value  |  |  |  |  |  |

| D9H      | CIDL         | WDTE                                                                                                                                                   | -              | -                 | -                          | CPS1                       | CPS0                     | ECF            | 00xxx000b    |  |  |  |  |  |

|          | 1. Not bit a | 1. Not bit addressable                                                                                                                                 |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

| Symbol   | Fu           | nction                                                                                                                                                 |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

| CIDL     | Co           | Counter Idle Control:                                                                                                                                  |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

|          |              | <ul><li>0: Programs the PCA Counter to continue functioning during idle mode</li><li>1: Programs the PCA Counter to be gated off during idle</li></ul> |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

| WDTE     |              | Watchdog Timer Enable:                                                                                                                                 |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

|          |              | 0: Disables Watchdog Timer function on PCA module 4                                                                                                    |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

|          |              | 1: Enables Watchdog Timer function on PCA module 4                                                                                                     |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

| -        |              | Not implemented, reserved for future use.                                                                                                              |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

|          | Not          | e: User sh                                                                                                                                             | ould not write | e '1's to reser   | ved bits. The              | e value read               | from a reserv            | ved bit is ind | leterminate. |  |  |  |  |  |

| CPS1     | PC           | A Count                                                                                                                                                | Pulse Sel      | ect bit 1         |                            |                            |                          |                |              |  |  |  |  |  |

| CPS0     | PC           | A Count                                                                                                                                                | Pulse Sel      | ect bit 2         |                            |                            |                          |                |              |  |  |  |  |  |

|          |              |                                                                                                                                                        |                |                   |                            |                            |                          |                |              |  |  |  |  |  |

|          |              |                                                                                                                                                        | Selec          | ted               |                            |                            |                          |                |              |  |  |  |  |  |

|          | CI           | PS1 CP                                                                                                                                                 | S0 PCA Ir      | nput <sup>1</sup> |                            |                            |                          |                |              |  |  |  |  |  |

|          |              | 0 0                                                                                                                                                    | 0              | Inter             | nal clock, f <sub>Os</sub> | <sub>SC</sub> /6 in 6 cloc | k mode (f <sub>OSC</sub> | c/12 in 12 cl  | ock mode)    |  |  |  |  |  |

|          |              | 0 1                                                                                                                                                    | 1              | Inter             | nal clock, for             | <sub>SC</sub> /2 in 6 cloc | k mode (f <sub>OSC</sub> | c/4 in 12 clo  | ck mode)     |  |  |  |  |  |

|          |              | 1 C                                                                                                                                                    | 2              | Time              | er 0 overflow              |                            |                          |                |              |  |  |  |  |  |

|          |              | 1 1                                                                                                                                                    | 3              | Exte              | rnal clock at              | ECI/P1.2 pir               | 1                        |                |              |  |  |  |  |  |

### PCA Timer/Counter Mode Register<sup>1</sup> (CMOD)

ECF

1. f<sub>OSC</sub> = oscillator frequency

PCA Enable Counter Overflow interrupt:

0: Disables the CF bit in CCON

1: Enables CF bit in CCON to generate an interrupt

Not Recommended for New Designs

| SPI Control Register (SP | CR)      |                                              |                                                      |                         |                           |                        |                       |            | _                     |

|--------------------------|----------|----------------------------------------------|------------------------------------------------------|-------------------------|---------------------------|------------------------|-----------------------|------------|-----------------------|

| Location                 | 7        | 6                                            | 5                                                    | 4                       | 3                         | 2                      | 1                     | 0          | Reset Value           |

| D5H                      | SPIE     | SPE                                          | DORD                                                 | MSTR                    | CPOL                      | CPHA                   | SPR1                  | SPR0       | 00H                   |

| Symbol                   | Fu       | inction                                      |                                                      |                         |                           |                        |                       |            |                       |

| SPIE                     | lf       | both SPIE                                    | and ES a                                             | re set to o             | ne, SPI in                | terrupts ai            | re enablec            | ł.         |                       |

| SPE                      | 0:<br>1: | PI enable I<br>Disables<br>Enables S<br>I.7. | SPI.                                                 | onnects SS              | S#, MOSI,                 | MISO, an               | d SCK to <sub>I</sub> | pins P1.4, | P1.5, P1.6,           |

| DORD                     | 0:       | MSB first                                    | nission Or<br>in data tra<br>n data trai             | insmissior              |                           |                        |                       |            |                       |

| MSTR                     | 0:       |                                              | e select.<br>lave mode<br>laster moc                 |                         |                           |                        |                       |            |                       |

| CPOL                     | 0:       |                                              | ty<br>w when id<br>gh when id                        | •                       | • •                       |                        |                       |            |                       |

| CPHA                     | re<br>0: | lationship<br>Shift trigg                    | e control b<br>between r<br>ered on th<br>ered on th | naster and<br>e leading | d slave. Se<br>edge of th | ee Figures<br>e clock. |                       |            | ck and data           |

| SPR1, SP                 | cc       | nfigured a                                   | ate Select<br>is master.<br>K and the                | SPR1 and                | I SPR0 ha                 | ve no effe             | ct on the s           | lave. The  | evice<br>relationship |

| SPR1 | SPR0 | SCK = f <sub>OSC</sub> divided by |

|------|------|-----------------------------------|

| 0    | 0    | 4                                 |

| 0    | 1    | 16                                |

| 1    | 0    | 64                                |

| 1    | 1    | 128                               |

### **SPI Status Register (SPSR)**

| Location | 7          | 6                                              | 5                        | 4          | 3                             | 2           | 1        | 0 | Reset Value |

|----------|------------|------------------------------------------------|--------------------------|------------|-------------------------------|-------------|----------|---|-------------|

| AAH      | SPIF       | WCOL                                           | -                        | -          | -                             | -           | -        | - | 00xxxxxxb   |

| Symbol   | Fu         | unction                                        |                          |            |                               |             |          |   |             |

| SPIF     | Up<br>If S |                                                | etion of da<br>nd ES =1, | an interru | r, this bit is<br>ıpt is then |             |          |   |             |

| WCOL     | Se         | rite Collisi<br>et if the SF<br>his bit is clo | l data reg               |            | itten to dui                  | ring data t | ransfer. |   |             |

#### Not Recommended for New Designs

| Serial Port Control Register (SCO | N) |  |

|-----------------------------------|----|--|

|-----------------------------------|----|--|

| Location     | 7                                                                                                                                                                                                   | 6                                           | 5                          | 4                       | 3                     | 2                         | 1                            | 0                          | Reset Value                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------|-------------------------|-----------------------|---------------------------|------------------------------|----------------------------|-----------------------------------------------------------|

| 98H          | SM0/FE                                                                                                                                                                                              | SM1                                         | SM2                        | REN                     | TB8                   | RB8                       | TI                           | RI                         | 0000000b                                                  |

| Symbol<br>FE |                                                                                                                                                                                                     | Function<br>Set SMOD0 = 1 to access FE bit. |                            |                         |                       |                           |                              |                            |                                                           |

|              | 0:<br>1:                                                                                                                                                                                            | No framin                                   | g error<br>Error. Set b    | y receive               |                       | n invalid st              | op bit is de                 | tected. Th                 | nis bit needs                                             |

| SM0          | -                                                                                                                                                                                                   | MOD0 = 0<br>erial Port N                    |                            | SM0 bit.                |                       |                           |                              |                            |                                                           |

| SM1          | Se                                                                                                                                                                                                  | erial Port N                                | lode Bit 1                 |                         |                       |                           |                              |                            |                                                           |

|              |                                                                                                                                                                                                     | SM0                                         | SM1                        | Moc                     | e De                  | scription                 | Baud Rate                    | e <sup>1</sup>             |                                                           |

|              |                                                                                                                                                                                                     | 0                                           | 0                          | 0                       |                       | ft Register               |                              | clock mode<br>2 clock mo   |                                                           |

|              |                                                                                                                                                                                                     | 0                                           | 1                          | 1                       |                       | it UART                   | Variable                     |                            |                                                           |

|              |                                                                                                                                                                                                     | 1                                           | 0                          | 2                       | 9-b                   | it UART                   | or                           |                            | clock mode)<br>2 clock mode                               |

|              |                                                                                                                                                                                                     | 1                                           | 1<br>scillator frequ       | 3                       | 9-b                   | it UART                   | Variable                     |                            |                                                           |

| SM2          | RI<br>an                                                                                                                                                                                            | will not be                                 | e set unles<br>ived byte i | s the rece<br>s a given | ived 9th<br>or broadd | data bit (F<br>cast addre | 88) is 1, ir<br>ss. In Mode  | ndicating a<br>e 1, if SM2 | M2 = 1 ther<br>an address,<br>2 = 1 then R<br>2 should be |

| REN          | 0:                                                                                                                                                                                                  | nables seri<br>to disable<br>to enable      | reception                  |                         |                       |                           |                              |                            |                                                           |

| TB8          |                                                                                                                                                                                                     | ne 9th data<br>sired.                       | bit that wi                | ll be trans             | mitted in             | Modes 2 a                 | ind 3. Set c                 | or clear by                | software as                                               |

| RB8          | In Modes 2 and 3, the 9th data bit that was received. In Mode 1, if $SM2 = 0$ , RB8 is the stop bit that was received. In Mode 0, RB8 is not used.                                                  |                                             |                            |                         |                       |                           |                              |                            |                                                           |

| TI           | Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission, Must be cleared by software. |                                             |                            |                         |                       |                           |                              |                            |                                                           |

| RI           | ha                                                                                                                                                                                                  |                                             | ugh the st                 | op bit time             | in the of             |                           | of the8th bi<br>s, in any se |                            | lode 0, or<br>tion (excep                                 |

### Not Recommended for New Designs

|          | inegietei | (                                                                                                                                                                                                                                                                                                                                       |                         |                       |                         |                          |             |                        | -                                                     |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------------------------|--------------------------|-------------|------------------------|-------------------------------------------------------|

| Location | 7         | 6                                                                                                                                                                                                                                                                                                                                       | 5                       | 4                     | 3                       | 2                        | 1           | 0                      | Reset Value                                           |

| C8H      | TF2       | EXF2                                                                                                                                                                                                                                                                                                                                    | RCLK                    | TCLK                  | EXEN2                   | TR2                      | C/T2#       | CP/<br>RL2#            | 00Н                                                   |

| Symbol   | Fu        | unction                                                                                                                                                                                                                                                                                                                                 |                         |                       |                         |                          |             |                        |                                                       |

| TF2      |           |                                                                                                                                                                                                                                                                                                                                         | •                       |                       | imer 2 ove<br>RCLK or T |                          | must be c   | leared by              | software.                                             |

| EXF2     | tra<br>ca | Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and EXEN2 = 1. When Timer 2 interrupt is enabled, $EXF2 = 1$ will cause the CPU to vector to the Timer 2 interrupt routine. EXF2 must be cleared by software. EXF2 does not cause an interrupt in up/down counter mode (DCEN = 1). |                         |                       |                         |                          |             |                        |                                                       |

| RCLK     | fo        | Receive clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its receive clock in modes 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the receive clock.                                                                                                                                          |                         |                       |                         |                          |             |                        |                                                       |

| TCLK     | fo        |                                                                                                                                                                                                                                                                                                                                         | nit clock in            |                       |                         |                          |             |                        | rflow pulses<br>w to be used                          |

| EXEN2    | re        | sult of a n                                                                                                                                                                                                                                                                                                                             | egative tra             | nsition on            |                         | mer 2 is n               | -           |                        | ccur as a<br>ck the serial                            |

| TR2      | St        | art/stop co                                                                                                                                                                                                                                                                                                                             | ontrol for T            | imer 2. A             | logic 1 sta             | rts the tim              | ner.        |                        |                                                       |

| C/T2#    | 0:        | Internal ti                                                                                                                                                                                                                                                                                                                             | · ·                     | /6 in 6 clo           | ,                       |                          | 12 clock    | mode)                  |                                                       |

| CP/RL2#  | E)<br>ne  | XEN2 = 1.<br>egative tra                                                                                                                                                                                                                                                                                                                | When cle<br>nsitions at | ared, auto<br>T2EX wh | -reloads w<br>en EXEN2  | /ill occur e<br>= 1. Whe | either with | Timer 2 o<br>CLK = 1 o | ns at T2EX if<br>verflows or<br>or TCLK = 1,<br>flow. |

### Timer/Counter 2 Control Register (T2CON)

### Timer/Counter 2 Mode Control (T2MOD)

| Location | 7  | 6                                                                                                                                                    | 5 | 4 | 3 | 2 | 1    | 0    | Reset Value |  |

|----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|------|------|-------------|--|

| C9H      | Х  | -                                                                                                                                                    | - | - | - | - | T2OE | DCEN | xxxxxx00b   |  |

| Symbol   | Fu | unction                                                                                                                                              |   |   |   |   |      |      |             |  |

| Х        | D  | on't Care                                                                                                                                            |   |   |   |   |      |      |             |  |

| -        |    | Not implemented, reserved for future use.<br>Note: User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate. |   |   |   |   |      |      |             |  |

| T2OE     |    | Timer 2 Output Enable bit.                                                                                                                           |   |   |   |   |      |      |             |  |

| DCEN     |    | Down Count Enable bit. When set, this allows Timer 2 to be configured as an up/<br>down counter.                                                     |   |   |   |   |      |      |             |  |

Not Recommended for New Designs

### **Byte-Program**

The Byte-Program command programs data into a single byte. The address is determined by the contents of SFAH and SFAL. The data byte is in SFDT.

Figure 12: Byte-Program

Not Recommended for New Designs

### Interrupt Termination

If interrupt termination is selected, (SFCM[7] is set), then an interrupt (INT1) will be generated to indicate flash operation completion. Under this condition, the INT1 becomes an internal interrupt source. The INT1# pin can now be used as a general purpose port pin and it cannot be the source of External Interrupt 1 during in-application programming.

In order to use an interrupt to signal flash operation termination. EX1 and EA bits of IE register must be set. The IT1 bit of TCON register must also be set for edge trigger detection.

| Operation                        | SFCM [6:0] <sup>1</sup> | SFDT [7:0]      | SFAH [7:0]      | SFAL [7:0]      |

|----------------------------------|-------------------------|-----------------|-----------------|-----------------|

| Chip-Erase <sup>2</sup>          | 01H                     | 55H             | X <sup>3</sup>  | X               |

| Block-Erase                      | 0DH                     | 55H             | AH <sup>4</sup> | X               |

| Sector-Erase                     | 0BH                     | X               | AH              | AL <sup>5</sup> |

| Byte-Program                     | 0EH                     | DI <sup>6</sup> | AH              | AL              |

| Byte-Verify (Read) <sup>7</sup>  | 0CH                     | DO <sup>6</sup> | AH              | AL              |

| Prog-SB1 <sup>8</sup>            | 0FH                     | AAH             | Х               | X               |

| Prog-SB2 <sup>8</sup>            | 03H                     | AAH             | X               | X               |

| Prog-SB3 <sup>8</sup>            | 05H                     | AAH             | Х               | Х               |

| Prog-SC0 <sup>8</sup>            | 09H                     | AAH             | 5AH             | Х               |

| Prog-SC1 <sup>8</sup>            | 09H                     | AAH             | AAH             | Х               |

| Enable-Clock-Double <sup>8</sup> | 08H                     | AAH             | 55H             | Х               |

|                                  |                         |                 |                 | T0-0.0 251      |

### Table 13: IAP Commands

1. Interrupt/Polling enable for flash operation completion

SFCM[7] = 1: Interrupt enable for flash operation completion

0: polling enable for flash operation completion

2. Chip-Erase only functions in IAP mode when EA#=0 (external memory execution) and device is not in level 4 locking.

3. X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

- 4. AH = Address high order byte

- 5. AL = Address low order byte

- 6. DI = Data Input, DO = Data Output, all other values are in hex.

- 7. SFAH[7:5] = 111b selects Block 1, SFAH[7] = 0b selects Block 0

8. Instruction must be located in Block 1 or external code memory.

Note: DISIAPL pin in PLCC or TQFP will also disable IAP commands if it is externally pulled low when reset.

Not Recommended for New Designs

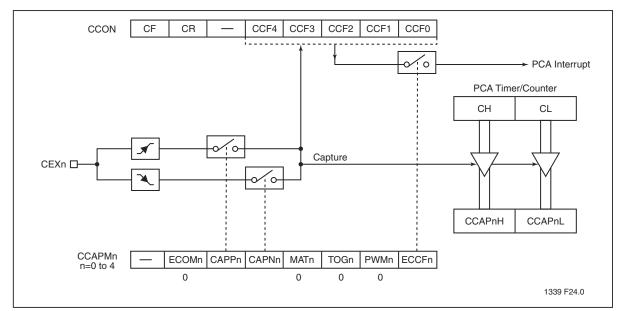

### **Capture Mode**

Capture mode is used to capture the PCA timer/counter value into a module's capture registers (CCAPnH and CCAPnL). The capture will occur on a positive edge, negative edge, or both on the corresponding module's pin. To use one of the PCA modules in the capture mode, either one or both the CCAPM bits CAPN and CAPP for that module must be set. When a valid transition occurs on the CEX pin corresponding to the module used, the PCA hardware loads the 16-bit value of the PCA counter register (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set, then an interrupt will be generated. In the interrupt service routine, the 16-bit capture value must be saved in RAM before the next event capture occurs. If a subsequent capture occurred, the original capture values would be lost. After flag event flag has been set by hardware, the user must clear the flag in software. (See Figure 25)

Figure 25: PCA Capture Mode

### Not Recommended for New Designs

|       | Sec        | urity Lo | ck Bits <sup>1,2</sup> | 2                | Security  | Status of: |                                                                                                                                                                                                                              |

|-------|------------|----------|------------------------|------------------|-----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Level | SFST[7:5]  | SB1      | SB2 <sup>1</sup>       | SB3 <sup>1</sup> | Block 1   | Block 0    | Security Type                                                                                                                                                                                                                |

| 1     | 000        | U        | U                      | U                | Unlock    | Unlock     | No Security Features are<br>Enabled.                                                                                                                                                                                         |

| 2     | 100        | Ρ        | U                      | U                | SoftLock  | SoftLock   | MOVC instructions executed from<br>external program memory are<br>disabled from fetching code bytes<br>from internal memory, EA# is<br>sampled and latched on Reset,<br>and further programming of the<br>flash is disabled. |

| 3     | 011<br>101 | U<br>P   | P<br>U                 | P<br>P           | Hard Lock | Hard Lock  | Level 2 plus Verify disabled, both blocks locked.                                                                                                                                                                            |

|       | 010        | U        | Р                      | U                | SoftLock  | SoftLock   | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0<br>and vice versa.                                                                                                                                      |

|       | 110<br>001 | P<br>U   | P<br>U                 | U<br>P           | Hard Lock | SoftLock   | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0.                                                                                                                                                        |

| 4     | 111        | Р        | Р                      | Ρ                | Hard Lock | Hard Lock  | Same as Level 3 hard lock/hard<br>lock, but MCU will start code exe-<br>cution from the internal memory<br>regardless of EA#.                                                                                                |

### Table 24: Security Lock Options

P = Programmed (Bit logic state = 0), U = Unprogrammed (Bit logic state = 1).

SFST[7:5] = Security Lock Status Bits (SB1\_i, SB2\_i, SB3\_i)

T0-0.0 25114

## Read Operation Under Lock Condition

The status of security bits SB1, SB2, and SB3 can be read when the read command is disabled by security lock. There are three ways to read the status.

- 1. External host mode: Read-back = 00H (locked)

- 2. IAP command: Read-back = previous SFDT data

- 3. MOVC: Read-back = FFH (blank)

#### Not Recommended for New Designs

|       |                                           | Source               | Target               | Byte-Verify Allo           | wed | MOVC Allowed |

|-------|-------------------------------------------|----------------------|----------------------|----------------------------|-----|--------------|

| Level | SFST[7:5]                                 | Address <sup>1</sup> | Address <sup>2</sup> | External Host <sup>3</sup> | IAP | 5xRDx        |

|       |                                           | Block 0/1            | Block 0/1            | N                          | N   | Y            |

| 4     | 111b<br>(hard lock on both blocks)        | BIOCK 0/ I           | External             | N/A                        | N/A | Y            |

| 4     |                                           | External             | Block 0/1            | N                          | N   | N            |

|       |                                           | External             | External             | N/A                        | N/A | Y            |

|       |                                           | Dia al ( 0/1         | Block 0/1            | N                          | N   | Y            |

|       | 011b/101b                                 | Block 0/1            | External             | N/A                        | N/A | Y            |

|       | (hard lock on both blocks)                | E de mart            | Block 0/1            | N                          | N   | N            |

|       |                                           | External             | External             | N/A                        | N/A | Y            |

|       |                                           |                      | Block 0              | N                          | N   | Y            |

|       |                                           | Block 0              | Block 1              | N                          | N   | N            |

|       |                                           |                      | External             | N/A                        | N/A | Y            |

|       | 001b/110b                                 |                      | Block 0              | N                          | Y   | Y            |

|       | (Block 0 = SoftLock, Block 1 = bard lock) | Block 1              | Block 1              | N                          | N   | Y            |

|       | Block 1 = hard lock)                      |                      | External             | N/A                        | N/A | Y            |

| 3     |                                           |                      | Block 0/1            | N                          | N   | N            |

|       |                                           | External             | External             | N/A                        | N/A | Y            |

|       | 010b<br>(SoftLock on both blocks)         | Block 0              | Block 0              | N                          | N   | Y            |

|       |                                           |                      | Block 1              | N                          | Y   | Y            |

|       |                                           |                      | External             | N/A                        | N/A | Y            |

|       |                                           | Block 1<br>External  | Block 0              | N                          | Y   | Y            |

|       |                                           |                      | Block 1              | N                          | N   | Ý            |

|       | 、                                         |                      | External             | N/A                        | N/A | Y            |

|       |                                           |                      | Block 0/1            | N                          | N   | N            |

|       |                                           |                      | External             | N/A                        | N/A | Y            |

|       |                                           |                      | Block 0              | Y                          | N   | Y            |

|       |                                           | Block 0              | Block 1              | Y                          | Y   | Y            |

|       |                                           |                      | External             | N/A                        | N/A | Y            |

|       | 100b                                      |                      | Block 0              | Y                          | Y   | Y            |

| 2     | (SoftLock on both blocks)                 | Block 1              | Block 1              | Y                          | N   | Ŷ            |

|       | (                                         |                      | External             | N/A                        | N/A | Y            |

|       |                                           |                      | Block 0/1            | Y                          | N   | N            |

|       |                                           | External             | External             | N/A                        | N/A | Y            |

|       |                                           |                      | Block 0              | Y                          | N   | Y            |

|       |                                           | Block 0              | Block 1              | Y                          | Y   | Y            |

|       |                                           |                      | External             | N/A                        | N/A | Y            |

|       | 000b                                      |                      | Block 0              | Y                          | Y   | Y            |

| 1     | (unlock)                                  | Block 1              | Block 1              | Y                          | N.  | Y            |

|       |                                           |                      | External             | N/A                        | N/A | Y            |

|       |                                           |                      | Block 0/1            | Y                          | Y   | Y            |

|       |                                           | External             | External             | N/A                        | N/A | Y            |

### Table 25: Security Lock Access Table

1. Location of MOVC or IAP instruction

2. Target address is the location of the byte being read

3. External host Byte-Verify access does not depend on a source address.

T0-0.0 25114

Not Recommended for New Designs

## **System Clock and Clock Options**

### **Clock Input Options and Recommended Capacitor Values for Oscillator**

Shown in Figure 33 are the input and output of an internal inverting amplifier (XTAL1, XTAL2), which can be configured for use as an on-chip oscillator.

When driving the device from an external clock source, XTAL2 should be left disconnected and XTAL1 should be driven.

At start-up, the external oscillator may encounter a higher capacitive load at XTAL1 due to interaction between the amplifier and its feedback capacitance. However, the capacitance will not exceed 15 pF once the external signal meets the  $V_{IL}$  and  $V_{IH}$  specifications.

Crystal manufacturer, supply voltage, and other factors may cause circuit performance to differ from one application to another. C1 and C2 should be adjusted appropriately for each design. Table 28, shows the typical values for C1 and C2 vs. crystal type for various frequencies

### Table 28: Recommended Values for C1 and C2 by Crystal Type

| Crystal | C1 = C2 |

|---------|---------|

| Quartz  | 20-30pF |

| Ceramic | 40-50pF |

T0-0.0 25114

More specific information about on-chip oscillator design can be found in the *FlashFlex Oscillator Circuit Design Considerations* application note.

Not Recommended for New Designs

## **Electrical Specification**

**Absolute Maximum Stress Ratings** (Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| Ambient Temperature Under Bias                                |                               |

|---------------------------------------------------------------|-------------------------------|

| Storage Temperature                                           | 65°C to +150°C                |

| Voltage on EA# Pin to V <sub>SS</sub>                         | 0.5V to +14.0V                |

| D.C. Voltage on Any Pin to Ground Potential                   |                               |

| Transient Voltage (<20ns) on Any Other Pin to V <sub>SS</sub> | 1.0V to V <sub>DD</sub> +1.0V |

| Maximum I <sub>OL</sub> per I/O Pins P1.5, P1.6, P1.7         |                               |

| Maximum I <sub>OL</sub> per I/O for All Other Pins            | 15mA                          |

| Package Power Dissipation Capability (T <sub>A</sub> = 25°C)  | 1.5W                          |

| Through Hole Lead Soldering Temperature (10 Seconds)          | 300°C                         |

| Surface Mount Solder Reflow Temperature <sup>1</sup>          | 260°C for 10 seconds          |

| Output Short Circuit Current <sup>2</sup>                     | 50 mA                         |

1. Excluding certain with-Pb 32-PLCC units, all packages are 260°C capable in both non-Pb and with-Pb solder versions. Certain with-Pb 32-PLCC package types are capable of 240°C for 10 seconds; please consult the factory for the latest information.

2. Outputs shorted for no more than one second. No more than one output shorted at a time.

(Based on package heat transfer limitations, not device power consumption. **Note:** This specification contains preliminary information on new products in production.

Specifications are subject to change without notice.

| Table | <b>30:</b> Operating | Range |

|-------|----------------------|-------|

|-------|----------------------|-------|

| Symbol          | Description                    | Min. | Max | Unit |

|-----------------|--------------------------------|------|-----|------|

| T <sub>A</sub>  | Ambient Temperature Under Bias |      |     |      |

|                 | Standard                       | 0    | +70 | °C   |

| V <sub>DD</sub> | Supply Voltage                 |      |     |      |

|                 | SST89E5xRD2A/RDA               | 4.5  | 5.5 | V    |

| fosc            | Oscillator Frequency           |      |     |      |

|                 | SST89E5xRD2A/RDA               | 0    | 40  | MHz  |

|                 | Oscillator Frequency for IAP   |      |     |      |

|                 | SST89E5xRD2A/RDA               | 0.25 | 40  | MHz  |

T0-0.0 25114

### Table 31: Reliability Characteristics

| Symbol                        | Parameter      | Minimum Specification | Units  | Test Method         |

|-------------------------------|----------------|-----------------------|--------|---------------------|

| N <sub>END</sub> <sup>1</sup> | Endurance      | 10,000                | Cycles | JEDEC Standard A117 |

| T <sub>DR</sub> <sup>1</sup>  | Data Retention | 100                   | Years  | JEDEC Standard A103 |

| ILTH <sup>1</sup>             | Latch Up       | 100 + I <sub>DD</sub> | mA     | JEDEC Standard 78   |

|                               |                |                       |        | T0-0.0 25114        |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

### Not Recommended for New Designs

### Table 32: AC Conditions of Test<sup>1</sup>

| Input Rise/Fall Time | Output Load             |  |  |

|----------------------|-------------------------|--|--|

| 10ns                 | C <sub>L</sub> = 100 pF |  |  |

1. See Figures 40 and 42

T32.1 25114

#### Table 33: Recommended System Power-up Timings

| Symbol                             | Parameter                   | Minimum | Units |

|------------------------------------|-----------------------------|---------|-------|

| T <sub>PU-READ</sub> <sup>1</sup>  | Power-up to Read Operation  | 100     | μs    |

| T <sub>PU-WRITE</sub> <sup>1</sup> | Power-up to Write Operation | 100     | μs    |

T0-0.2 25114

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter

### Table 34: Pin Impedance (VDD=3.3V, TA=25 °C, f=1 Mhz, other pins open)

| Parameter                     | Description         | Test Condition | Maximum      |

|-------------------------------|---------------------|----------------|--------------|

| CI/O <sup>1</sup>             | I/O Pin Capacitance | $V_{I/O} = 0V$ | 15 pF        |

| C <sub>IN</sub> <sup>1</sup>  | Input Capacitance   | $V_{IN} = 0V$  | 12 pF        |

| L <sub>PIN</sub> <sup>2</sup> | Pin Inductance      |                | 20 nH        |

|                               |                     |                | T0-0.4 25114 |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

2. Refer to PCI spec.

## **DC Electrical Characteristics**

Not Recommended for New Designs

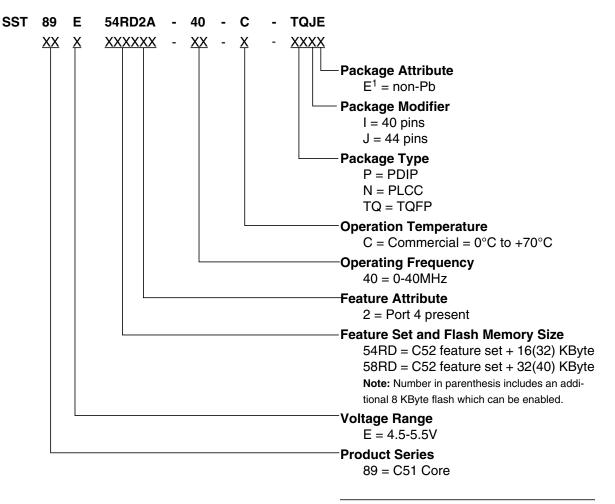

## **Product Ordering Information**

Environmental suffix "E" denotes non-Pb solder. SST non-Pb solder devices are "RoHS Compliant".

Not Recommended for New Designs

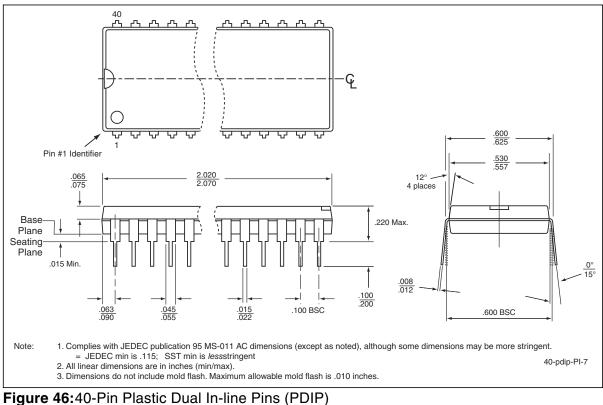

## **Packaging Diagrams**

SST Package Code: PI

Not Recommended for New Designs

| Revision |                                                | Description                                      | Date     |

|----------|------------------------------------------------|--------------------------------------------------|----------|

| 00       | <ul> <li>Initial Releas</li> </ul>             | e                                                | Dec 2006 |

| 01       | <ul> <li>Changed Fla</li> </ul>                | shFlex51 to FlashFlex globally                   | Jan 2007 |

| 02       | <ul> <li>Removed all<br/>ally</li> </ul>       | 3V parts (89V58RD2A/RDA and 89V54RD2A/RDA) glob- | Feb 2008 |

|          | Removed WQFN/ QIF package information globally |                                                  |          |

|          | <ul> <li>Remove all I-</li> </ul>              | -grade part information globally                 |          |

| А        | <ul> <li>Applied new</li> </ul>                | document format                                  | Dec 2011 |

|          | <ul> <li>Released do</li> </ul>                | cument under letter revision system              |          |

|          | <ul> <li>Updated Spectrum</li> </ul>           | ec number from S71339 to DS25114                 |          |

ISBN:978-1-61341-895-6

© 2011 Silicon Storage Technology, Inc-a Microchip Technology Company. All rights reserved.

SST, Silicon Storage Technology, the SST logo, SuperFlash, MTP, and FlashFlex are registered trademarks of Silicon Storage Technology, Inc. MPF, SQI, Serial Quad I/O, and Z-Scale are trademarks of Silicon Storage Technology, Inc. All other trademarks and registered trademarks mentioned herein are the property of their respective owners.

Specifications are subject to change without notice. Refer to www.microchip.com for the most recent documentation. For the most current package drawings, please see the Packaging Specification located at http://www.microchip.com/packaging.

Memory sizes denote raw storage capacity; actual usable capacity may be less.

SST makes no warranty for the use of its products other than those expressly contained in the Standard Terms and Conditions of Sale.

For sales office locations and information, please see www.microchip.com.

#### Silicon Storage Technology, Inc. A Microchip Technology Company www.microchip.com