Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | 8051                                                                            |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 40MHz                                                                           |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 40KB (40K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | -                                                                               |

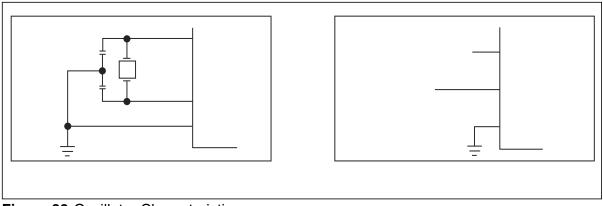

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e58rd2-40-i-tqje |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Not Recommended for New Designs

### Expanded Data RAM Addressing

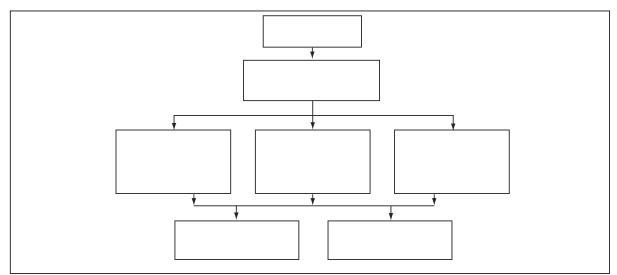

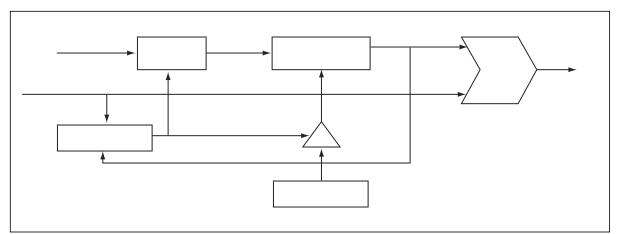

The SST89E/V5xRDxA both have the capability of 1K of RAM. See Figure 7.

The device has four sections of internal data memory:

- 1. The lower 128 Bytes of RAM (00H to 7FH) are directly and indirectly addressable.

- 2. The higher 128 Bytes of RAM (80H to FFH) are indirectly addressable.

- 3. The special function registers (80H to FFH) are directly addressable only.

- 4. The expanded RAM of 768 Bytes (00H to 2FFH) is indirectly addressable by the move external instruction (MOVX) and clearing the EXTRAM bit. (See "Auxiliary Register (AUXR)" in Section , "Special Function Registers")

Since the upper 128 bytes occupy the same addresses as the SFRs, the RAM must be accessed indirectly. The RAM and SFRs space are physically separate even though they have the same addresses.

When instructions access addresses in the upper 128 bytes (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

#### Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in "#data" is written to RAM location 90H rather than port 1.

#### **Direct Access:**

MOV90H, #data; write data to P1

Data in "#data" is written to port 1. Instructions that write directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 bytes of memory is physically located on the chip and logically occupies the first 768 bytes of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 (WR#), P3.7 (RD#), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

#### Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A; DPTR contains 0A0H

DPTR points to 0A0H and data in "A" is written to address 0A0H of the expanded RAM rather than external memory. Access to external memory higher than 2FFH using the MOVX instruction will access external memory (0300H to FFFFH) and will perform in the same way as the standard 8051, with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 8051. Using MOVX @Ri provides an 8-bit address with multiplexed data on Port 0. Other output port pins can be used to output higher order address bits. This provides external paging capabilities. Using MOVX

#### Not Recommended for New Designs

| Location              | 7          | 6                                                                                                                                                                   | 5           | 4               | 3           | 2          | 1           | 0          | Reset Value    |  |  |  |

|-----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|-------------|------------|-------------|------------|----------------|--|--|--|

| 85H                   |            |                                                                                                                                                                     | Wa          | atchdog Tim     | er Data/Re  | load       | •           |            | 00H            |  |  |  |

| Symbol                | F          | unction                                                                                                                                                             |             |                 |             |            |             |            |                |  |  |  |

| WDTD                  | lı         | nitial/Reloa                                                                                                                                                        | d value ir  | Watchdog        | g Timer. N  | ew value v | won't be e  | ffective u | ntil WDT is    |  |  |  |

|                       | S          | et.                                                                                                                                                                 |             | -               | -           |            |             |            |                |  |  |  |

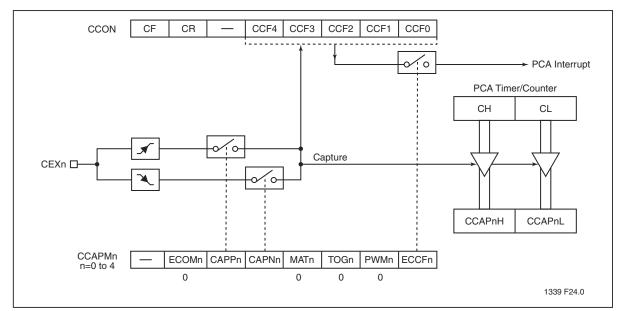

| CA Timer/Counter Cont | ol Pogi    | stor1 (CCC                                                                                                                                                          |             |                 |             |            |             |            |                |  |  |  |

| Location              | 7          |                                                                                                                                                                     | 5           | 4               | 3           | 2          | 1           | 0          | Reset Value    |  |  |  |

| D8H                   | CF         | CR                                                                                                                                                                  | -           | CCF4            | CCF3        | CCF2       | CCF1        | CCF0       |                |  |  |  |

| Don                   | 1. Bit add |                                                                                                                                                                     |             | 0014            | 0010        | 0012       |             |            |                |  |  |  |

| Currence of           | -          |                                                                                                                                                                     |             |                 |             |            |             |            |                |  |  |  |

| Symbol                |            | Function PCA Counter Overflow Flag                                                                                                                                  |             |                 |             |            |             |            |                |  |  |  |

| CF                    |            |                                                                                                                                                                     |             | •               |             |            |             |            |                |  |  |  |

|                       |            | Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is set. CF may be set by either hardware or software, but can only cleared by |             |                 |             |            |             |            |                |  |  |  |

|                       |            | oftware.                                                                                                                                                            | et. CF may  | / be set by     | eitner naro | aware or s | offware, b  | ut can on  | ly cleared b   |  |  |  |

|                       | -          |                                                                                                                                                                     | _           |                 |             |            |             |            |                |  |  |  |

| CR                    |            | CA Count                                                                                                                                                            |             |                 |             |            |             |            |                |  |  |  |

|                       |            | -                                                                                                                                                                   |             | n the PCA       | counter o   | n. Must be | e cleared t | by softwar | re to turn the |  |  |  |

|                       |            | CA counte                                                                                                                                                           |             |                 |             |            |             |            |                |  |  |  |

| -                     |            | •                                                                                                                                                                   | -           | served for f    |             |            |             |            |                |  |  |  |

|                       |            |                                                                                                                                                                     |             | e '1's to reser |             |            |             |            |                |  |  |  |

| CCF4                  |            |                                                                                                                                                                     |             | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |  |  |  |

|                       | N          | lust be cle                                                                                                                                                         | ared by s   | oftware.        |             |            |             |            |                |  |  |  |

| CCF3                  |            |                                                                                                                                                                     |             | ıpt flag. Se    | t by hardw  | vare when  | a match o   | or capture | occurs.        |  |  |  |

|                       | Ν          | lust be cle                                                                                                                                                         | ared by s   | oftware.        |             |            |             |            |                |  |  |  |

| CCF2                  |            |                                                                                                                                                                     |             | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |  |  |  |

|                       | Ν          | /lust be cle                                                                                                                                                        | ared by s   | oftware.        |             |            |             |            |                |  |  |  |

|                       |            |                                                                                                                                                                     |             |                 |             |            |             |            |                |  |  |  |

| CCF1                  | F          | CA Modul                                                                                                                                                            | e 1 interru | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |  |  |  |

| CCF1                  |            | PCA Modul<br>/lust be cle                                                                                                                                           |             |                 | t by hardw  | are when   | a match o   | or capture | occurs.        |  |  |  |

| CCF1<br>CCF0          | Ν          | lust be cle                                                                                                                                                         | ared by s   |                 | -           |            |             |            |                |  |  |  |

#### Not Recommended for New Designs

### PCA Compare/Capture Module Mode Register<sup>1</sup> (CCAPMn)

| omparo, capturo n |              | ao nogio                                                                                      |               |              |               |                |              |                |             |  |  |

|-------------------|--------------|-----------------------------------------------------------------------------------------------|---------------|--------------|---------------|----------------|--------------|----------------|-------------|--|--|

| Location          | 7            | 6                                                                                             | 5             | 4            | 3             | 2              | 1            | 0              | Reset Value |  |  |

| DAH               | -            | ECOM0                                                                                         | CAPP0         | CAPN0        | MAT0          | TOG0           | PWM0         | ECCF0          | 00xxx000b   |  |  |

| DBH               | -            | ECOM1                                                                                         | CAPP1         | CAPN1        | MAT1          | TOG1           | PWM1         | ECCF1          | 00xxx000b   |  |  |

| DCH               | -            | ECOM2                                                                                         | CAPP2         | CAPN2        | MAT2          | TOG2           | PWM2         | ECCF2          | 00xxx000b   |  |  |

| DDH               | -            | ECOM3                                                                                         | CAPP3         | CAPN3        | MAT3          | TOG3           | PWM3         | ECCF3          | 00xxx000b   |  |  |

| DEH               | -            | ECOM4                                                                                         | CAPP4         | CAPN4        | MAT4          | TOG4           | PWM4         | ECCF4          | 00xxx000b   |  |  |

|                   | 1. Not bit a | addressable                                                                                   |               | •            |               | •              |              |                |             |  |  |

| Symbol            | Fu           | unction                                                                                       |               |              |               |                |              |                |             |  |  |

| -                 | N            | ot impleme                                                                                    | ented, rese   | erved for f  | uture use.    |                |              |                |             |  |  |

|                   | No           | ote: User sho                                                                                 | uld not write | 1's to reser | ved bits. The | e value read   | from a reser | ved bit is ind | eterminate. |  |  |

| ECOMn             |              | hable Com                                                                                     |               |              |               |                |              |                |             |  |  |

|                   |              | Disables t                                                                                    |               |              |               |                |              |                |             |  |  |

|                   |              | Enables t                                                                                     |               | rator funct  | ion           |                |              |                |             |  |  |

| CAPPn             |              | Capture Positive<br>0: Disables positive edge capture on CEX[4:0]                             |               |              |               |                |              |                |             |  |  |

|                   |              | 0: Disables positive edge capture on CEX[4:0]<br>1: Enables positive edge capture on CEX[4:0] |               |              |               |                |              |                |             |  |  |

| CAPNn             |              | Capture Negative                                                                              |               |              |               |                |              |                |             |  |  |

| CALINI            |              | Disables I                                                                                    | ,             | dae captu    | ire on CEX    | <b>(</b> [4:0] |              |                |             |  |  |

|                   |              | Enables r                                                                                     |               |              |               |                |              |                |             |  |  |

| MATn              | М            | atch: Set E                                                                                   | ECOM[4:0      | ] and MAT    | [4:0] to im   | nplement t     | he softwai   | re timer m     | ode         |  |  |

|                   |              | Disables                                                                                      |               |              |               |                |              |                |             |  |  |

|                   |              |                                                                                               |               |              |               |                |              | oture regis    | ster causes |  |  |

|                   |              | e CCFn bi                                                                                     |               | I to be set, | , flagging a  | an interrup    | DT.          |                |             |  |  |

| TOGn              |              | oggle<br>Disables t                                                                           | ogalo fun     | otion        |               |                |              |                |             |  |  |

|                   |              |                                                                                               |               |              | vith this m   | odule's co     | mpare/ca     | oture regis    | ster causes |  |  |

|                   |              | e the CEX                                                                                     |               |              |               |                | inpaio, ca   | otare regic    |             |  |  |

| PWMn              | Pu           | ulse Width                                                                                    | Modulatio     | on mode      |               |                |              |                |             |  |  |

|                   | 0:           | Disables                                                                                      | PWM mod       | le           |               |                |              |                |             |  |  |

|                   | 1:           | Enables (                                                                                     | CEXn pin t    | o be used    | as a puls     | e width mo     | odulated o   | utput          |             |  |  |

| ECCFn             |              | hable CCF                                                                                     |               |              |               |                |              |                |             |  |  |

|                   |              | Disables of terrupt req                                                                       |               | apture flag  | g CCF[4:0     | ) in the CO    | CON regis    | ter to gene    | erate an    |  |  |

|                   |              | Enables c                                                                                     |               | apture flag  | g CCF[4:0]    | ] in the CC    | ON regist    | er to gene     | rate an     |  |  |

|                   | in           | terrupt req                                                                                   | uest.         |              |               |                |              |                |             |  |  |

|                   |              |                                                                                               |               |              |               |                |              |                |             |  |  |

Not Recommended for New Designs

| SPI Control Register (SP | CR)      |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         |                           |                        |                       |            | _                     |  |  |  |

|--------------------------|----------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------|------------------------|-----------------------|------------|-----------------------|--|--|--|

| Location                 | 7        | 6                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                       | 3                         | 2                      | 1                     | 0          | Reset Value           |  |  |  |

| D5H                      | SPIE     | SPE                                          | DORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSTR                    | CPOL                      | CPHA                   | SPR1                  | SPR0       | 00H                   |  |  |  |

| Symbol                   | Fu       | inction                                      | DORD       MSTR       CPOL       CPHA       SPR1       SPR0       00H         E and ES are set to one, SPI interrupts are enabled.       6       6       6       6       6       6       6       6       6       6       6       6       6       6       6       7       6       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7 |                         |                           |                        |                       |            |                       |  |  |  |

| SPIE                     | lf       | both SPIE                                    | and ES a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | re set to o             | ne, SPI in                | terrupts ai            | re enablec            | ł.         |                       |  |  |  |

| SPE                      | 0:<br>1: | PI enable I<br>Disables<br>Enables S<br>I.7. | SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | onnects SS              | S#, MOSI,                 | MISO, an               | d SCK to <sub>I</sub> | pins P1.4, | P1.5, P1.6,           |  |  |  |

| DORD                     | 0:       | MSB first                                    | in data tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | insmissior              |                           |                        |                       |            |                       |  |  |  |

| MSTR                     | 0:       |                                              | lave mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |                           |                        |                       |            |                       |  |  |  |

| CPOL                     | 0:       |                                              | ty<br>w when id<br>gh when id                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                       | • •                       |                        |                       |            |                       |  |  |  |

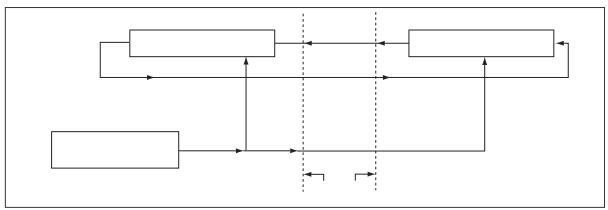

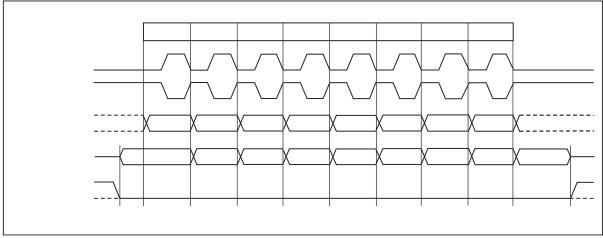

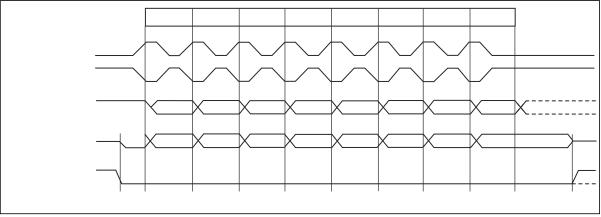

| CPHA                     | re<br>0: | lationship<br>Shift trigg                    | e control b<br>between r<br>ered on th<br>ered on th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | naster and<br>e leading | d slave. Se<br>edge of th | ee Figures<br>e clock. |                       |            | ck and data           |  |  |  |

| SPR1, SP                 | cc       | nfigured a                                   | ate Select<br>is master.<br>K and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SPR1 and                | I SPR0 ha                 | ve no effe             | ct on the s           | lave. The  | evice<br>relationship |  |  |  |

| SPR1 | SPR0 | SCK = f <sub>OSC</sub> divided by |

|------|------|-----------------------------------|

| 0    | 0    | 4                                 |

| 0    | 1    | 16                                |

| 1    | 0    | 64                                |

| 1    | 1    | 128                               |

#### SPI Status Register (SPSR)

| Location | 7          | 6                                              | 5                        | 4          | 3                             | 2           | 1        | 0 | Reset Value |

|----------|------------|------------------------------------------------|--------------------------|------------|-------------------------------|-------------|----------|---|-------------|

| AAH      | SPIF       | WCOL                                           | -                        | -          | -                             | -           | -        | - | 00xxxxxxb   |

| Symbol   | Fu         | unction                                        |                          |            |                               |             |          |   |             |

| SPIF     | Up<br>If S |                                                | etion of da<br>nd ES =1, | an interru | r, this bit is<br>ıpt is then |             |          |   |             |

| WCOL     | Se         | rite Collisi<br>et if the SF<br>his bit is clo | l data reg               |            | itten to dui                  | ring data t | ransfer. |   |             |

Not Recommended for New Designs

| Location         7         6         5         4         3         2         1         0         Reset Value           86H         SPDR[7:0]         SPDR[7:0]         00H         0H         0H |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 86H SPDR[7:0] 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Value |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Н     |

| Power Control Register (PCON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Location         7         6         5         4         3         2         1         0         Reset Val                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Value |

| 87H SMOD1 SMOD0 BOF POF GF1 GF0 PD IDL 0001000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 000b  |

| Symbol Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| SMOD1 Double Baud rate bit. If SMOD1 = 1, Timer 1 is used to generate the baud rate, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | , and |

| the serial port is used in modes 1, 2, and 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| SMOD0 FE/SM0 Selection bit.<br>0: SCON[7] = SM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| 1: SCON[7] = FE,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| BOF Brown-out detection status bit, this bit will not be affected by any other reset. BOF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OF    |

| should be cleared by software. Power-on reset will also clear the BOF bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 0: No brown-out.<br>1: Brown-out occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| POF Power-on reset status bit, this bit will not be affected by any other reset. POF should be affected by any other reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | hould |

| be cleared by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | louiu |

| 0: No Power-on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| 1: Power-on reset occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| GF1 General-purpose flag bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| GF0 General-purpose flag bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| PD Power-down bit, this bit is cleared by hardware after exiting from power-down mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | node. |

| 0: Power-down mode is not activated.<br>1: Activates Power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| IDL Idle mode bit, this bit is cleared by hardware after exiting from idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 0: Idle mode is not activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 1: Activates idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

#### Not Recommended for New Designs

|          |           | (                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                       |                          |                          |             |                         | -                                                     |  |  |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|--------------------------|--------------------------|-------------|-------------------------|-------------------------------------------------------|--|--|

| Location | 7         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                       | 4                     | 3                        | 2                        | 1           | 0                       | Reset Value                                           |  |  |

| C8H      | TF2       | EXF2                                                                                                                                                                                                                                                                                                                                                                                                                                                | RCLK                    | TCLK                  | EXEN2                    | TR2                      | C/T2#       | CP/<br>RL2#             | 00Н                                                   |  |  |

| Symbol   | Fu        | unction                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |                       |                          |                          |             |                         |                                                       |  |  |

| TF2      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                       |                       | imer 2 ove<br>RCLK or T  |                          | must be c   | leared by               | software.                                             |  |  |

| EXF2     | tra<br>ca | ansition or<br>ause the C                                                                                                                                                                                                                                                                                                                                                                                                                           | T2EX and<br>PU to vec   | d EXEN2 =             | = 1. When<br>Timer 2 int | Timer 2 in<br>errupt rou | itine. EXF2 | enabled, E<br>2 must be | negative<br>EXF2 = 1 will<br>cleared by<br>DCEN = 1). |  |  |

| RCLK     | fo        | Receive clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its receive clock in modes 1 and 3. $RCLK = 0$ causes Timer 1 overflow to be used for the receive clock.                                                                                                                                                                                                                                                    |                         |                       |                          |                          |             |                         |                                                       |  |  |

| TCLK     | fo        | Transmit clock flag. When set, causes the serial port to use Timer 2 overflow pulses<br>for its transmit clock in modes 1 and 3. TCLK = 0 causes Timer 1 overflow to be used<br>for the transmit clock.<br>Timer 2 external enable flag. When set, allows a capture or reload to occur as a<br>result of a negative transition on T2EX if Timer 2 is not being used to clock the serial<br>port. EXEN2 = 0 causes Timer 2 to ignore events at T2EX. |                         |                       |                          |                          |             |                         |                                                       |  |  |

| EXEN2    | re        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                       |                          |                          |             |                         |                                                       |  |  |

| TR2      | St        | art/stop co                                                                                                                                                                                                                                                                                                                                                                                                                                         | ontrol for T            | imer 2. A             | logic 1 sta              | rts the tim              | ner.        |                         |                                                       |  |  |

| C/T2#    | 0:        | Internal ti                                                                                                                                                                                                                                                                                                                                                                                                                                         | · ·                     | /6 in 6 clo           | ,                        |                          | 12 clock    | mode)                   |                                                       |  |  |

| CP/RL2#  | E)<br>ne  | XEN2 = 1.<br>egative tra                                                                                                                                                                                                                                                                                                                                                                                                                            | When cle<br>nsitions at | ared, auto<br>T2EX wh | -reloads w<br>en EXEN2   | /ill occur e<br>= 1. Whe | either with | Timer 2 o<br>CLK = 1 o  | ns at T2EX if<br>verflows or<br>or TCLK = 1,<br>flow. |  |  |

### Timer/Counter 2 Control Register (T2CON)

### Timer/Counter 2 Mode Control (T2MOD)

| Location | 7  | 6                           | 5 | 4          | 3             | 2            | 1             | 0              | Reset Value                                 |

|----------|----|-----------------------------|---|------------|---------------|--------------|---------------|----------------|---------------------------------------------|

| C9H      | Х  | -                           | - | -          | -             | -            | T2OE          | DCEN           | xxxxxx00b                                   |

| Symbol   | Fu | unction                     |   |            |               |              |               |                |                                             |