Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | 8051                                                                            |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 40MHz                                                                           |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 40KB (40K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | -                                                                               |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | 0°C ~ 70°C                                                                      |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-LCC (J-Lead)                                                                 |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e58rd2a-40-c-nje |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Not Recommended for New Designs

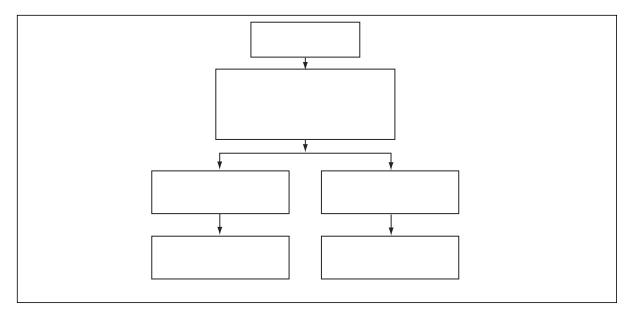

### Expanded Data RAM Addressing

The SST89E/V5xRDxA both have the capability of 1K of RAM. See Figure 7.

The device has four sections of internal data memory:

- 1. The lower 128 Bytes of RAM (00H to 7FH) are directly and indirectly addressable.

- 2. The higher 128 Bytes of RAM (80H to FFH) are indirectly addressable.

- 3. The special function registers (80H to FFH) are directly addressable only.

- 4. The expanded RAM of 768 Bytes (00H to 2FFH) is indirectly addressable by the move external instruction (MOVX) and clearing the EXTRAM bit. (See "Auxiliary Register (AUXR)" in Section , "Special Function Registers")

Since the upper 128 bytes occupy the same addresses as the SFRs, the RAM must be accessed indirectly. The RAM and SFRs space are physically separate even though they have the same addresses.

When instructions access addresses in the upper 128 bytes (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

#### Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in "#data" is written to RAM location 90H rather than port 1.

#### **Direct Access:**

MOV90H, #data; write data to P1

Data in "#data" is written to port 1. Instructions that write directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 bytes of memory is physically located on the chip and logically occupies the first 768 bytes of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 (WR#), P3.7 (RD#), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

#### Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A; DPTR contains 0A0H

DPTR points to 0A0H and data in "A" is written to address 0A0H of the expanded RAM rather than external memory. Access to external memory higher than 2FFH using the MOVX instruction will access external memory (0300H to FFFFH) and will perform in the same way as the standard 8051, with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 8051. Using MOVX @Ri provides an 8-bit address with multiplexed data on Port 0. Other output port pins can be used to output higher order address bits. This provides external paging capabilities. Using MOVX

#### Not Recommended for New Designs

@DPTR generates a 16-bit address. This allows external addressing up the 64K. Port 2 provides the high-order eight address bits (DPH), and Port 0 multiplexes the low order eight address bits (DPL) with data. Both MOVX @Ri and MOVX @DPTR generates the necessary read and write signals (P3.6 - WR# and P3.7 - RD#) for external memory use. Table 4 shows external data memory RD#, WR# operation with EXTRAM bit.

The stack pointer (SP) can be located anywhere within the 256 bytes of internal RAM (lower 128 bytes and upper 128 bytes). The stack pointer may not be located in any part of the expanded RAM.

|            | MOVX @DPTR, A or       | MOVX @Ri, A or MOVX A, @Ri |                                     |

|------------|------------------------|----------------------------|-------------------------------------|

| AUXR       | ADDR < 0300H           | ADDR >= 0300H              | ADDR = Any                          |

| EXTRAM = 0 | RD# / WR# not asserted | RD# / WR# asserted         | RD# / WR# not asserted <sup>1</sup> |

| EXTRAM = 1 | RD# / WR# asserted     | RD# / WR# asserted         | RD# / WR# asserted                  |

#### Table 4: External Data Memory RD#, WR# with EXTRAM bit

1. Access limited to ERAM address within 0 to 0FFH; cannot access 100H to 02FFH.

T0-0.0 25114

#### Not Recommended for New Designs

| Cumh               |                                  | Direct<br>Addres | Bit       | Address   | , Symb | ol, or  | Alterna | tive Po | ort Functio | n    | Reset     |

|--------------------|----------------------------------|------------------|-----------|-----------|--------|---------|---------|---------|-------------|------|-----------|

| Symb<br>ol         | Description                      | Addres<br>S      | MSB       |           |        |         |         |         |             | LSB  | Value     |

| ACC <sup>1</sup>   | Accumulator                      | E0H              |           |           |        | ACC     | C[7:0]  |         |             |      | 00H       |

| B <sup>1</sup>     | B Register                       | F0H              |           |           |        | B[      | 7:0]    |         |             |      | 00H       |

| PSW <sup>1</sup>   | Program Status<br>Word           | D0H              | CY        | AC        | F0     | RS1     | RS0     | OV      | F1          | Р    | 00H       |

| SP                 | Stack Pointer                    | 81H              |           |           |        | SP      | [7:0]   |         |             |      | 07H       |

| DPL                | Data Pointer<br>Low              | 82H              |           |           |        | DPI     | _[7:0]  |         |             |      | 00H       |

| DPH                | Data Pointer<br>High             | 83H              |           |           |        | DPH     | H[7:0]  |         |             |      | 00H       |

| IE <sup>1</sup>    | Interrupt Enable                 | A8H              | EA        | EC        | ET2    | ES      | ET1     | EX1     | ET0         | EX0  | 00H       |

| IEA <sup>1</sup>   | Interrupt<br>Enable A            | E8H              | -         | -         | -      | -       | EBO     | -       | -           | -    | xxxx0xxxb |

| IP <sup>1</sup>    | Interrupt Priority<br>Reg        | B8H              | -         | PPC       | PT2    | PS      | PT1     | PX1     | PT0         | PX0  | x0000000b |

| IPH                | Interrupt Priority<br>Reg High   | B7H              | -         | PPCH      | PT2H   | PSH     | PT1H    | PX1H    | PT0H        | PX0H | x0000000b |

| IP1 <sup>1</sup>   | Interrupt Priority<br>Reg A      | F8H              | -         | -         | -      | -       | PBO     | PX3     | PX2         | -    | xxxx0xxxb |

| IP1H               | Interrupt Priority<br>Reg A High | F7H              | -         | -         | -      | -       | PBOH    | PX3H    | PX3         | -    | xxxx0xxxb |

| PCON               | Power Control                    | 87H              | SMOD<br>1 | SMOD<br>0 | BOF    | PO<br>F | GF1     | GF0     | PD          | IDL  | 00010000b |

| AUXR               | Auxiliary Reg                    | 8EH              | -         | -         | -      | -       | -       | -       | EXTRAM      | AO   | xxxxxx00b |

| AUXR1              | Auxiliary Reg 1                  | A2H              | -         | -         | -      | -       | GF2     | 0       | -           | DPS  | xxxx00x0b |

| XICON <sup>2</sup> | External<br>Interrupt Control    | AEH              | х         | EX3       | IE3    | IT3     | 0       | EX2     | IE2         | IT2  | 00H       |

### Table 6: CPU related SFRs

1. Bit Addressable SFRs

2. X = Don't care

#### Not Recommended for New Designs

|        |                             | Direct  | E     | Bit Addr                 | ess, Sy  | /mbc  | ol, or Alte        | rnative Port Fu             | unctio              | n              | Reset     |

|--------|-----------------------------|---------|-------|--------------------------|----------|-------|--------------------|-----------------------------|---------------------|----------------|-----------|

| Symbol | Description                 | Address | MSB   |                          |          |       |                    |                             |                     | LSB            | Value     |

| SFCF   | SuperFlash<br>Configuration | B1H     | -     | IAPEN                    | -        | -     | -                  | -                           | SWR                 | BSEL           | x0xxxx00b |

| SFCM   | SuperFlash<br>Command       | B2H     | FIE   |                          |          |       | FCM                | [6:0]                       |                     |                | 00H       |

| SFAL   | SuperFlash<br>Address Low   | B3H     | Super | Flash Lo                 | ow Orde  | er By | te Addres          | s Register - A <sub>7</sub> | to A <sub>0</sub> ( | SFAL)          | 00H       |

| SFAH   | SuperFlash<br>Address High  | B4H     | Su    | perFlash                 | n High ( | Ordei | Byte Add<br>(SFAH) | lress Register -            | A <sub>15</sub> to  | A <sub>8</sub> | 00H       |

| SFDT   | SuperFlash<br>Data          | B5H     |       | SuperFlash Data Register |          |       |                    |                             |                     | 00H            |           |

| SFST   | SuperFlash<br>Status        | B6H     | SB1_i | SB2_i                    | SB3_i    | -     | EDC_i              | FLASH_BUSY                  | -                   | -              | 000x00xxb |

### Table 7: Flash Memory Programming SFRs

T0-0.0 25114

### Table 8: Watchdog Timer SFRs

|                   |                               | Direct  | В   | Bit Address, Symbol, or Alternative Port Function |   |            |           |          |     |      |           |

|-------------------|-------------------------------|---------|-----|---------------------------------------------------|---|------------|-----------|----------|-----|------|-----------|

| Symbol            | Description                   | Address | MSB |                                                   |   |            |           |          |     | LSB  | Value     |

| WDTC <sup>1</sup> | Watchdog Timer<br>Control     | C0H     | -   | -                                                 | - | WDOUT      | WDRE      | WDTS     | WDT | SWDT | xxx00x00b |

| WDTD              | Watchdog Timer<br>Data/Reload | 85H     |     |                                                   | ۷ | Vatchdog T | imer Data | a/Reload |     |      | 00H       |

1. Bit Addressable SFRs

T0-0.0 25114

#### Not Recommended for New Designs

|                   |                                       | Direct     | В                                        | it Addre    | ss, Sym | bol, or A    | Alternat | tive Po | rt Funct | ion      | RESET      |

|-------------------|---------------------------------------|------------|------------------------------------------|-------------|---------|--------------|----------|---------|----------|----------|------------|

| Symbol            | Description                           | Address    | MSB                                      |             |         |              |          |         |          | LSB      | Value      |

| CH<br>CL          | PCA Timer/Counter                     | F9H<br>E9H |                                          |             |         | CH[7<br>CL[7 | -        |         |          |          | 00H<br>00H |

| CCON <sup>1</sup> | PCA Timer/Counter<br>Control Register | D8H        | CF                                       | CR          | -       | CCF4         | CCF3     | CCF2    | CCF1     | CCF0     | 00x00000b  |

| CMOD              | PCA Timer/Counter<br>Mode Register    | D9H        | CIDL                                     | WDTE        | -       | -            | -        | CPS1    | CPS0     | ECF      | 00xxx000b  |

| CCAP0H            | PCA Module 0                          | FAH        |                                          | CCAP0H[7:0] |         |              |          |         |          |          | 00H        |

| CCAPOL            | Compare/Capture<br>Registers          | EAH        |                                          | CCAP0L[7:0] |         |              |          |         |          |          | 00H        |

| CCAP1H            | PCA Module 1                          | FBH        |                                          | CCAP1H[7:0] |         |              |          |         |          |          | 00H        |

| CCAP1L            | Compare/Capture<br>Registers          | EBH        |                                          | CCAP1L[7:0] |         |              |          |         |          |          |            |

| CCAP2H            | PCA Module 2                          | FCH        |                                          | CCAP2H[7:0] |         |              |          |         |          |          |            |

| CCAP2L            | Compare/Capture<br>Registers          | ECH        |                                          |             |         | CCAP2        | 2L[7:0]  |         |          |          | 00H        |

| ССАРЗН            | PCA Module 3                          | FDH        |                                          |             |         | CCAP3        | H[7:0]   |         |          |          | 00H        |

| CCAP3L            | Compare/Capture<br>Registers          | EDH        |                                          |             |         | CCAP3        | BL[7:0]  |         |          |          | 00H        |

| CCAP4H            | PCA Module 4                          | FEH        |                                          |             |         | CCAP4        | H[7:0]   |         |          |          | 00H        |

| CCAP4L            | Compare/Capture<br>Registers          | EEH        |                                          |             |         | CCAP4        | IL[7:0]  | _       |          |          | 00H        |

| CCAPM0            | PCA                                   | DAH        | -                                        | ECOM0       | CAPP0   | CAPN0        | MAT0     | TOG0    | PWM0     | ECCF0    | x0000000b  |

| CCAPM1            | Compare/Capture                       | DBH        | -                                        | ECOM1       | CAPP1   | CAPN1        | MAT1     | TOG1    | PWM1     | ECCF1    | x000000b   |

| CCAPM2            | Module Mode<br>Registers              | DCH        | - ECOM2 CAPP2 CAPN2 MAT2 TOG2 PWM2 ECCF2 |             |         |              |          |         |          | x000000b |            |

| CCAPM3            | 1 109101010                           | DDH        | -                                        | ECOM3       | CAPP3   | CAPN3        | MAT3     | TOG3    | PWM3     | ECCF3    | x0000000b  |

| CCAPM4            |                                       | DEH        | -                                        | ECOM4       | CAPP4   | CAPN4        | MAT4     | TOG4    | PWM4     | ECCF4    | x000000b   |

### Table 11:PCA SFRs

1. Bit Addressable SFRs

T0-0.0 25114

#### Not Recommended for New Designs

| Interrupt Enable (IE) |    |                                      |             |        |     |     |     |     |             |

|-----------------------|----|--------------------------------------|-------------|--------|-----|-----|-----|-----|-------------|

| Location              | 7  | 6                                    | 5           | 4      | 3   | 2   | 1   | 0   | Reset Value |

| A8H                   | EA | EC                                   | ET2         | ES     | ET1 | EX1 | ET0 | EX0 | 00H         |

| Symbol                | F  | unction                              |             |        |     |     |     |     |             |

| EA                    | 0  | lobal Inter<br>= Disable<br>= Enable | rupt Enabl  | е.     |     |     |     |     |             |

| EC                    | Р  | CA Interru                           | pt Enable.  |        |     |     |     |     |             |

| ET2                   | T  | mer 2 Inte                           | rrupt Enab  | ole.   |     |     |     |     |             |

| ES                    | S  | erial Interr                         | upt Enable  | ).     |     |     |     |     |             |

| ET1                   | T  | mer 1 Inte                           | rrupt Enab  | ole.   |     |     |     |     |             |

| EX1                   | E  | xternal 1 Ir                         | nterrupt Er | nable. |     |     |     |     |             |

| ET0                   | T  | mer 0 Inte                           | rrupt Enab  | ole.   |     |     |     |     |             |

| EX0                   | E  | xternal 0 Ir                         | nterrupt Er | nable. |     |     |     |     |             |

## Interrupt Enable A (IEA)

| Location | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 | Reset Value |

|----------|---|---|---|---|-----|---|---|---|-------------|

| E8H      | - | - | - | - | EBO | - | - | - | xxxx0xxxb   |

| Symbol | Function                                                |

|--------|---------------------------------------------------------|

| EBO    | Brown-out Interrupt Enable.<br>1 = Enable the interrupt |

|        | 0 = Disable the interrupt                               |

### Interrupt Priority (IP)

| Location | 7 | 6   | 5   | 4  | 3   | 2   | 1   | 0   | Reset Value |

|----------|---|-----|-----|----|-----|-----|-----|-----|-------------|

| B8H      | - | PPC | PT2 | PS | PT1 | PX1 | PT0 | PX0 | x0000000b   |

| Symbol | Function                           |

|--------|------------------------------------|

| PPC    | PCA interrupt priority bit         |

| PT2    | Timer 2 interrupt priority bit     |

| PS     | Serial Port interrupt priority bit |

| PT1    | Timer 1 interrupt priority bit     |

| PX1    | External interrupt 1 priority bit  |

| PT0    | Timer 0 interrupt priority bit     |

| PX0    | External interrupt 0 priority bit  |

#### Not Recommended for New Designs

| Location              | 7          | 6                         | 5           | 4               | 3           | 2          | 1           | 0          | Reset Value    |

|-----------------------|------------|---------------------------|-------------|-----------------|-------------|------------|-------------|------------|----------------|

| 85H                   |            |                           | Wa          | atchdog Tim     | er Data/Re  | load       | •           |            | 00H            |

| Symbol                | F          | unction                   |             |                 |             |            |             |            |                |

| WDTD                  | lı         | nitial/Reloa              | d value ir  | Watchdog        | g Timer. N  | ew value v | won't be e  | ffective u | ntil WDT is    |

|                       | S          | et.                       |             | -               | -           |            |             |            |                |

| CA Timer/Counter Cont | ol Pogi    | stor1 (CCC                |             |                 |             |            |             |            |                |

| Location              | 7          |                           | 5           | 4               | 3           | 2          | 1           | 0          | Reset Value    |

| D8H                   | CF         | CR                        | -           | CCF4            | CCF3        | CCF2       | CCF1        | CCF0       |                |

|                       | 1. Bit add |                           |             | 0014            | 0010        | 0012       | 0011        |            |                |

| Currence of           | -          |                           |             |                 |             |            |             |            |                |

| Symbol                |            | unction                   |             | -               |             |            |             |            |                |

| CF                    |            | CA Count                  |             | •               |             |            |             |            |                |

|                       |            |                           |             | n the coun      |             |            |             |            |                |

|                       |            | oftware.                  | et. CF may  | / be set by     | eitner naro | aware or s | offware, b  | ut can on  | ly cleared b   |

|                       | -          |                           | _           |                 |             |            |             |            |                |

| CR                    |            | CA Count                  |             |                 |             |            |             |            |                |

|                       |            | -                         |             | n the PCA       | counter o   | n. Must be | e cleared t | by softwar | re to turn the |

|                       |            | CA counte                 |             |                 |             |            |             |            |                |

| -                     |            | •                         | -           | served for f    |             |            |             |            |                |

|                       |            |                           |             | e '1's to reser |             |            |             |            |                |

| CCF4                  |            |                           |             | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |

|                       | N          | lust be cle               | ared by s   | oftware.        |             |            |             |            |                |

| CCF3                  |            |                           |             | ıpt flag. Se    | t by hardw  | vare when  | a match o   | or capture | occurs.        |

|                       | Ν          | lust be cle               | ared by s   | oftware.        |             |            |             |            |                |

| CCF2                  |            |                           |             | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |

|                       | Ν          | /lust be cle              | ared by s   | oftware.        |             |            |             |            |                |

|                       |            |                           |             |                 |             |            |             |            |                |

| CCF1                  | F          | CA Modul                  | e 1 interru | ıpt flag. Se    | t by hardw  | are when   | a match o   | or capture | occurs.        |

| CCF1                  |            | PCA Modul<br>/lust be cle |             |                 | t by hardw  | are when   | a match o   | or capture | occurs.        |

| CCF1<br>CCF0          | Ν          | lust be cle               | ared by s   |                 | -           |            |             |            |                |

Not Recommended for New Designs

### Sector-Erase

The Sector-Erase command erases all of the bytes in a sector. The sector size for the flash memory blocks is 128 Bytes. The selection of the sector to be erased is determined by the contents of SFAH and SFAL.

Figure 11:Sector-Erase

Not Recommended for New Designs

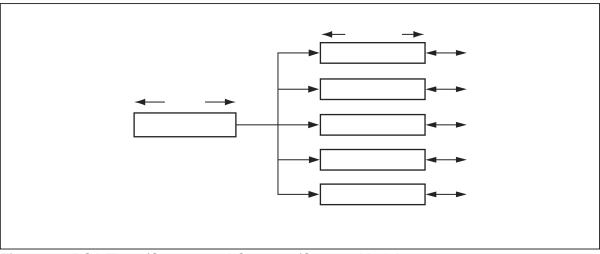

### Automatic Address Recognition

Automatic Address Recognition helps to reduce the MCU time and power required to talk to multiple serial devices. Each device is hooked together sharing the same serial link with its own address. In this configuration, a device is only interrupted when it receives its own address, thus eliminating the software overhead to compare addresses.

This same feature helps to save power because it can be used in conjunction with idle mode to reduce the system's overall power consumption. Since there may be multiple slaves hooked up serial to one master, only one slave would have to be interrupted from idle mode to respond to the master's transmission. Automatic Address Recognition (AAR) allows the other slaves to remain in idle mode while only one is interrupted. By limiting the number of interruptions, the total current draw on the system is reduced.

There are two ways to communicate with slaves: a group of them at once, or all of them at once. To communicate with a group of slaves, the master sends out an address called the given address. To communicate with all the slaves, the master sends out an address called the "broadcast" address.

AAR can be configured as mode 2 or 3 (9-bit modes) and setting the SM2 bit in SCON. Each slave has its own SM2 bit set waiting for an address byte (9th bit = 1). The Receive Interrupt (RI) flag will only be set when the received byte matches either the given address or the broadcast address. Next, the slave then clears its SM2 bit to enable reception of the data bytes (9th bit = 0) from the master. When the 9th bit = 1, the master is sending an address. When the 9th bit = 0, the master is sending actual data.

If mode 1 is used, the stop bit takes the place of the 9th bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit. Note that mode 0 cannot be used. Setting SM2 bit in the SCON register in mode 0 will have no effect.

Each slave's individual address is specified by SFR SADDR. SFR SADEN is a mask byte that defines "don't care" bits to form the given address when combined with SADDR. See the example below:

#### Slave 1 SADDR = 1111 0001

| ••••• |   |           |

|-------|---|-----------|

| SADEN | = | 1111 1010 |

| GIVEN | = | 1111 0X0X |

#### Slave 2

| SADDR | = | 1111 0011 |

|-------|---|-----------|

| SADEN | = | 1111 1001 |

| GIVEN | = | 1111 0XX1 |

Not Recommended for New Designs

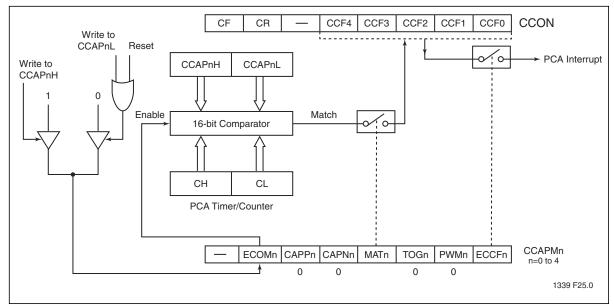

#### Figure 24: PCA Timer/Counter and Compare/Capture Modules

The table below summarizes various clock inputs at two common frequencies.

|                                        | Clock Increments |                  |  |  |

|----------------------------------------|------------------|------------------|--|--|

| PCA Timer/Counter Mode                 | 12 MHz           | 16 MHz           |  |  |

| Mode 0: f <sub>OSC</sub> /12           | 1 µsec           | 0.75 µsec        |  |  |

| Mode 1:                                | 330 nsec         | 250 nsec         |  |  |

| Mode 2: Timer 0 Overflows <sup>1</sup> |                  |                  |  |  |

| Timer 0 programmed in:                 |                  |                  |  |  |

| 8-bit mode                             | 256 µsec         | 192 µsec         |  |  |

| 16-bit mode                            | 65 msec          | 49 µsec          |  |  |

| 8-bit auto-reload                      | 1 to 255 µsec    | 0.75 to 191 µsec |  |  |

| Mode 3: External Input MAX             | 0.66 µsec        | 0.50 µsec        |  |  |

|                                        |                  | T0-0.0 251       |  |  |

1. In Mode 2, the overflow interrupt for Timer 0 does not need to be enabled.

The four possible CMOD timer modes with and without the overflow interrupt enabled are shown below. This list assumes that PCA will be left running during idle mode.

#### Table 19:CMOD Values

|                                      | CMOD Value                |                        |  |  |

|--------------------------------------|---------------------------|------------------------|--|--|

| PCA Count Pulse Selected             | Without Interrupt Enabled | With Interrupt Enabled |  |  |

| Internal clock, f <sub>OSC</sub> /12 | 00H                       | 01H                    |  |  |

| Internal clock, f <sub>OSC</sub> /4  | 02H                       | 03H                    |  |  |

| Timer 0 overflow                     | 04H                       | 05H                    |  |  |

| External clock at P1.2               | 06H                       | 07H                    |  |  |

T0-0.0 25114

Not Recommended for New Designs

### 16-Bit Software Timer Mode

The 16-bit software timer mode is used to trigger interrupt routines, which must occur at periodic intervals. It is setup by setting both the ECOM and MAT bits in the module's CCAPMn register. The PCA timer will be compared to the module's capture registers (CCAPnL and CCAPnH) and when a match occurs, an interrupt will occur, if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

If necessary, a new 16-bit compare value can be loaded into CCAPnH and CCAPnL during the interrupt routine. The user should be aware that the hardware temporarily disables the comparator function while these registers are being updated so that an invalid match will not occur. Thus, it is recommended that the user write to the low byte first (CCAPnL) to disable the comparator, then write to the high byte (CCAPnH) to re-enable it. If any updates to the registers are done, the user may want to hold off any interrupts from occurring by clearing the EA bit. (See Figure 26)

Figure 26: PCA Compare Mode (Software Timer)

Not Recommended for New Designs

### **Software Reset**

The software reset is executed by changing SFCF[1] (SWR) from "0" to "1". A software reset will reset the program counter to address 0000H. All SFR registers will be set to their reset values, except SFCF[1] (SWR), WDTC[2] (WDTS), and RAM data will not be altered.

### **Brown-out Detection Reset**

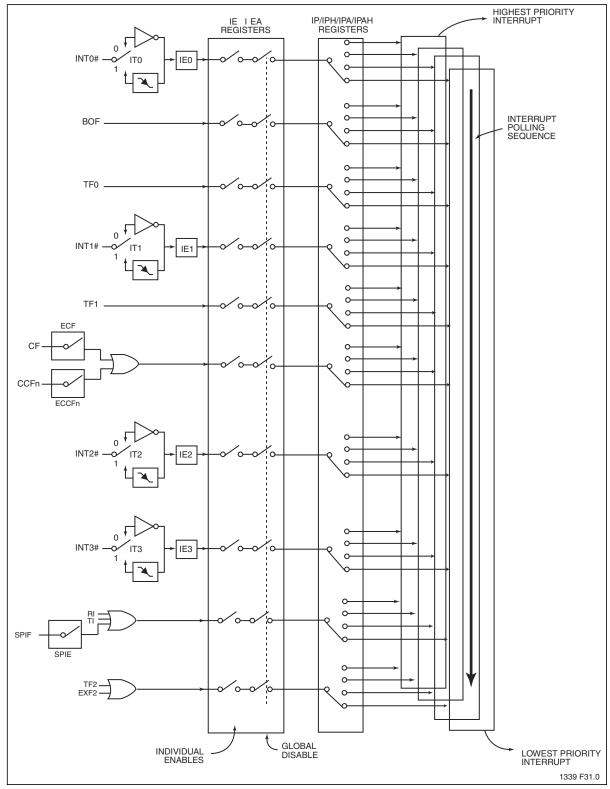

The device includes a brown-out detection circuit to protect the system from severed supplied voltage  $V_{DD}$  fluctuations. SST89E5xRD2A/RDA internal brown-out detection threshold is 3.85V. For brown-out voltage parameters, please refer to Tables 35 and 36.

When  $V_{DD}$  drops below this voltage threshold, the brown-out detector triggers the circuit to generate a brown-out interrupt but the CPU still runs until the supplied voltage returns to the brown-out detection voltage  $V_{BOD}$ . The default operation for a brown-out detection is to cause a processor reset.

$V_{\text{DD}}$  must stay below  $V_{\text{BOD}}$  at least four oscillator clock periods before the brown-out detection circuit will respond.

Brown-out interrupt can be enabled by setting the EBO bit in IEA register (address E8H, bit 3). If EBO bit is set and a brown-out condition occurs, a brown-out interrupt will be generated to execute the program at location 004BH. It is required that the EBO bit be cleared by software after the brown-out interrupt is serviced. Clearing EBO bit when the brown-out condition is active will properly reset the device. If brown-out interrupt is not enabled, a brown-out condition will reset the program to resume execution at location 0000H.

#### Not Recommended for New Designs

Figure 32: Interrupt Structure

Not Recommended for New Designs

### **Table 35:**DC Electrical Characteristics for SST89E5xRD2A/RDA $T_A = -40^{\circ}$ C to $+85^{\circ}$ C; $V_{DD} = 4.5-5.5$ V; $V_{SS} = 0$ V

| Symbol                                                                       | Parameter                                                      | <b>Test Conditions</b>                            | Min                      | Max                         | Units |

|------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------|--------------------------|-----------------------------|-------|

| V <sub>IL</sub>                                                              | Input Low Voltage                                              | 4.5 < V <sub>DD</sub> < 5.5                       | -0.5                     | 0.2V <sub>DD</sub> -<br>0.1 | V     |

| VIH                                                                          | Input High Voltage                                             | 4.5 < V <sub>DD</sub> < 5.5                       | 0.2V <sub>DD</sub> + 0.9 | V <sub>DD</sub> + 0.5       | V     |

| V <sub>IH1</sub>                                                             | Input High Voltage (XTAL1, RST)                                | 4.5 < V <sub>DD</sub> < 5.5                       | 0.7V <sub>DD</sub>       | V <sub>DD</sub> + 0.5       | V     |

| V <sub>OL</sub> Output Low Voltage (Ports 1.5, 1.6, 1.7)                     | $V_{DD} = 4.5V$                                                |                                                   |                          |                             |       |

|                                                                              |                                                                | I <sub>OL</sub> = 16mA                            |                          | 1.0                         | V     |

| V <sub>OL</sub> Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>              | $V_{DD} = 4.5V$                                                |                                                   |                          |                             |       |

|                                                                              | $I_{OL} = 100 \mu A^2$                                         |                                                   | 0.3                      | V                           |       |

|                                                                              |                                                                | $I_{OL} = 1.6 \text{mA}^2$                        |                          | 0.45                        | V     |

|                                                                              |                                                                | $I_{OL} = 3.5 \text{mA}^2$                        |                          | 1.0                         | V     |

| V <sub>OL1</sub> Output Low Voltage (Port 0, ALE, PSEN#) <sup>1,3</sup>      | $V_{DD} = 4.5V$                                                |                                                   |                          |                             |       |

|                                                                              |                                                                | $I_{OL} = 200 \mu A^2$                            |                          | 0.3                         | V     |

|                                                                              |                                                                | $I_{OL} = 3.2 m A^2$                              |                          | 0.45                        | V     |

| V <sub>OH</sub> Output High Voltage (Ports 1, 2, 3, ALE, PSEN#) <sup>4</sup> | $V_{DD} = 4.5V$                                                |                                                   |                          |                             |       |

|                                                                              |                                                                | I <sub>OH</sub> = -10μA                           | V <sub>DD</sub> - 0.3    |                             | V     |

|                                                                              |                                                                | I <sub>OH</sub> = -30μA                           | V <sub>DD</sub> - 0.7    |                             | V     |

|                                                                              |                                                                | I <sub>OH</sub> = -60μA                           | V <sub>DD</sub> - 1.5    |                             | V     |

| V <sub>OH1</sub>                                                             | Output High Voltage (Port 0 in External Bus                    | $V_{DD} = 4.5V$                                   |                          |                             |       |

|                                                                              | Mode) <sup>4</sup>                                             | I <sub>OH</sub> = -200μA                          | V <sub>DD</sub> - 0.3    |                             | V     |

|                                                                              |                                                                | I <sub>OH</sub> = -3.2mA                          | V <sub>DD</sub> - 0.7    |                             | V     |

| V <sub>BOD</sub>                                                             | Brown-out Detection Voltage                                    |                                                   | 3.85                     | 4.15                        | V     |

| IIL                                                                          | Logical 0 Input Current (Ports 1, 2, 3)                        | $V_{IN} = 0.4V$                                   |                          | -75                         | μA    |

| I <sub>TL</sub>                                                              | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | $V_{IN} = 2V$                                     |                          | -650                        | μA    |

| ILI                                                                          | Input Leakage Current (Port 0)                                 | 0.45 < V <sub>IN</sub> < V <sub>DD</sub> -<br>0.3 |                          | ±10                         | μA    |

| R <sub>RST</sub>                                                             | RST Pull-down Resistor                                         |                                                   | 40                       | 225                         | KΩ    |

| C <sub>IO</sub>                                                              | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                                     |                          | 15                          | pF    |

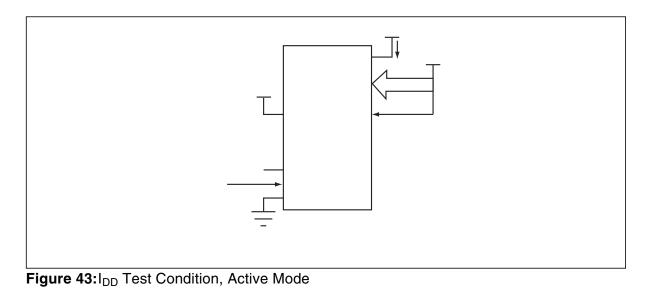

| I <sub>DD</sub>                                                              | Power Supply Current                                           |                                                   |                          |                             |       |

|                                                                              | IAP Mode                                                       |                                                   |                          |                             |       |

|                                                                              | @ 40 MHz                                                       |                                                   |                          | 88                          | mA    |

|                                                                              | Active Mode                                                    |                                                   |                          |                             |       |

|                                                                              | @ 40 MHz                                                       |                                                   |                          | 50                          | mA    |

|                                                                              | Idle Mode                                                      |                                                   |                          |                             |       |

|                                                                              | @ 40 MHz                                                       |                                                   |                          | 42                          | mA    |

|                                                                              | Power-down Mode                                                | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$       |                          | 80                          | μA    |

|                                                                              |                                                                | $T_A = -40^{\circ}C$ to $+85^{\circ}C$            |                          | 90                          | μA    |

T0-0.2 25114

Not Recommended for New Designs

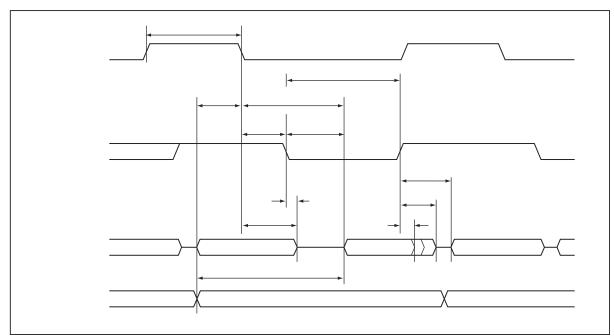

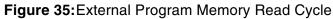

Figure 36: External Data Memory Read Cycle

Not Recommended for New Designs

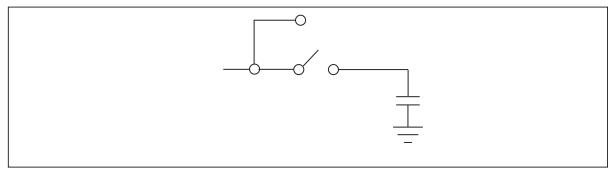

## Figure 41: Float Waveform

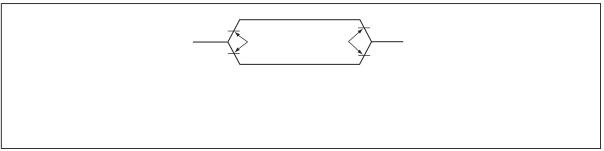

### Figure 42: A Test Load Example

Not Recommended for New Designs

## **Valid Combinations**

#### Valid combinations for SST89E54RD2A

SST89E54RD2A-40-C-NJE SST89E54RD2A-40-C-TQJE

### Valid combinations for SST89E58RD2A

SST89E58RD2A-40-C-NJE SST89E58RD2A-40-C-TQJE

### Valid combinations for SST89E54RDA

SST89E54RDA-40-C-PIE

#### Valid combinations for SST89E58RDA

SST89E58RDA-40-C-PIE

**Note:**Valid combinations are those products in mass production or will be in mass production. Consult your SST sales representative to confirm availability of valid combinations and to determine availability of new combinations.

Not Recommended for New Designs

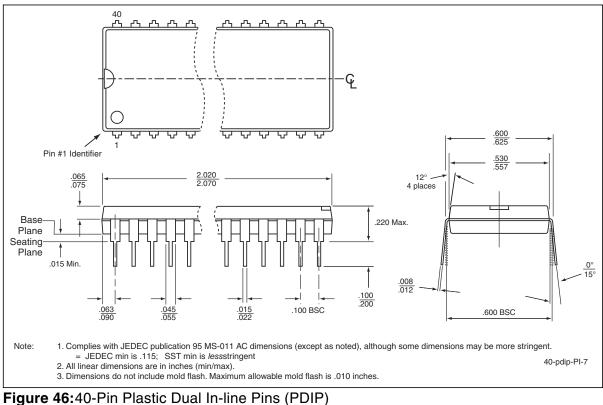

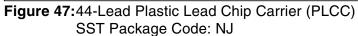

## **Packaging Diagrams**

SST Package Code: PI

Not Recommended for New Designs

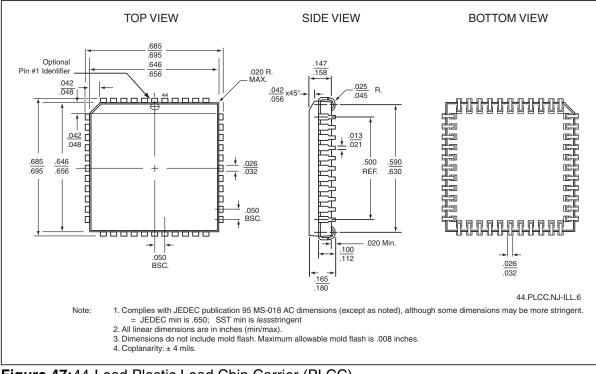

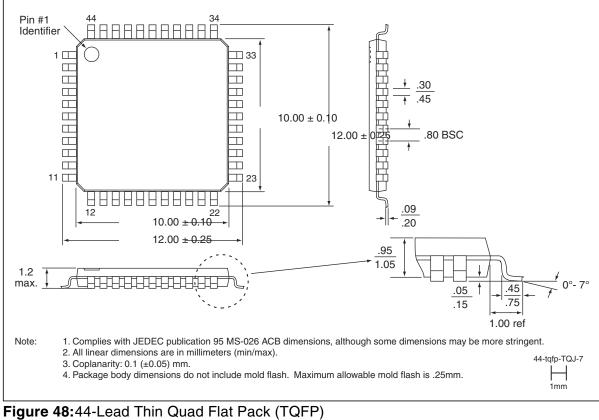

#### Not Recommended for New Designs

SST Package Code: TQJ