Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | 8051                                                                             |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 40MHz                                                                            |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                 |

| Number of I/O              | 36                                                                               |

| Program Memory Size        | 40KB (40K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | -                                                                                |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | 0°C ~ 70°C                                                                       |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e58rd2a-40-c-tqje |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Not Recommended for New Designs

## **Product Description**

The SST89E54RD2A/RDA and SST89E58RD2A/RDA are members of the FlashFlex family of 8-bit microcontroller products designed and manufactured with SST patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

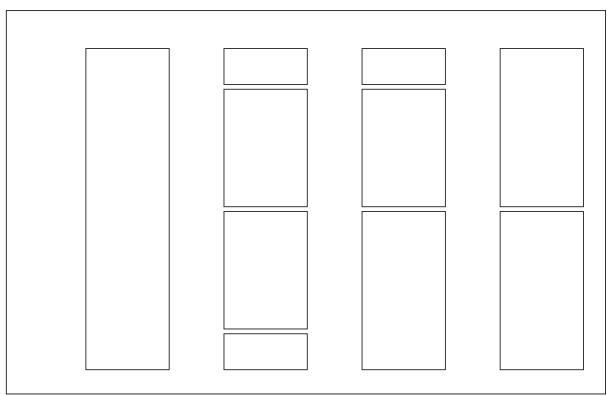

The devices come with 24/40 KByte of on-chip flash EEPROM program memory which is partitioned into 2 independent program memory blocks. The primary Block 0 occupies 16/32 KByte of internal program memory space and the secondary Block 1 occupies 8 KByte of internal program memory space.

The 8-KByte secondary block can be mapped to the lowest location of the 16/32 KByte address space; it can also be hidden from the program counter and used as an independent EEPROM-like data memory.

In addition to the 24/40 KByte of EEPROM program memory on-chip and 1024 x8 bits of on-chip RAM, the devices can address up to 64 KByte of external program memory and up to 64 KByte of external RAM.

The flash memory blocks can be programmed via a standard 87C5x OTP EPROM programmer fitted with a special adapter and the firmware for SST devices. During power-on reset, the devices can be configured as either a slave to an external host for source code storage or a master to an external host for an in-application programming (IAP) operation. The devices are designed to be programmed in-system and in-application on the printed circuit board for maximum flexibility. The devices are pre-programmed with an example of the bootstrap loader in the memory, demonstrating the initial user program code loading or subsequent user code updating via the IAP operation. The sample bootstrap loader is available for the user's reference and convenience only; SST does not guarantee its functionality or usefulness. Chip-Erase or Block-Erase operations will erase the pre-programmed sample code.

#### Not Recommended for New Designs

| Symbol          | Type <sup>1</sup> | Name and Functions                                                                                                |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------|

| XTAL1           | I                 | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits. |

| XTAL2           | 0                 | Crystal 2: Output from the inverting oscillator amplifier                                                         |

| V <sub>DD</sub> | I                 | Power Supply                                                                                                      |

| V <sub>SS</sub> | I                 | Ground                                                                                                            |

|                 |                   | T0-0.0 25114                                                                                                      |

#### Table 1: Pin Descriptions (Continued) (3 of 3)

1. I = Input; O = Output

2.ALE loading issue: When ALE pin experiences higher loading (>30pf) during the reset, the MCU may accidentally enter into modes other than normal working mode. The solution is to add a pull-up resistor of 3-50 K $\Omega$  to V<sub>DD</sub>, e.g. for ALE pin.

3. For 6 clock mode, ALE is emitted at 1/3 of crystal frequency.

4. Port 4 is not present on the PDIP package.

Not Recommended for New Designs

### **Program Memory Block Switching**

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

| SFCF[1:0] | Program Memory Block Switching                                                                                                                                                                                                                                                                                                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10, 11    | Block 1 is not visible to the PC;<br>Block 1 is reachable only via in-application programming from E000H - FFFFH.                                                                                                                                                                                                                                                    |

| 01        | Both Block 0 and Block 1 are visible to the PC.<br>Block 0 is occupied from 0000H - 7FFFH. Block 1 is occupied from E000H - FFFFH.                                                                                                                                                                                                                                   |

| 00        | Block 1 is overlaid onto the low 8K of the program address space; occupying address locations<br>0000H - 1FFFH.<br>When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of<br>Block 0.<br>Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable<br>through in-application programming. |

| Table 2: SFCF Val | llues for Program Memor | v Block Switching |

|-------------------|-------------------------|-------------------|

|-------------------|-------------------------|-------------------|

T0-0.0 25114

Not Recommended for New Designs

#### **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0 and/or SC1. The SC0 and SC1 bits are programmed via an external host mode command or an IAP Mode command. See Table 13.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

| SC1 <sup>1</sup> | SC0 <sup>1</sup> | Power-on or External<br>Reset | WDT Reset or Brown-out<br>Reset | Software Reset |

|------------------|------------------|-------------------------------|---------------------------------|----------------|

| U (1)            | U (1)            | 00 (default)                  | x0                              | 10             |

| U (1)            | P (0)            | 01                            | x1                              | 11             |

| P (0)            | U (1)            | 10                            | 10                              | 10             |

| P (0)            | P (0)            | 11                            | 11                              | 11             |

|                  | •                | •                             |                                 | T0-0.0 251     |

#### Table 3: SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

#### Data RAM Memory

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

Not Recommended for New Designs

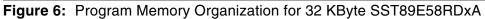

### Expanded Data RAM Addressing

The SST89E/V5xRDxA both have the capability of 1K of RAM. See Figure 7.

The device has four sections of internal data memory:

- 1. The lower 128 Bytes of RAM (00H to 7FH) are directly and indirectly addressable.

- 2. The higher 128 Bytes of RAM (80H to FFH) are indirectly addressable.

- 3. The special function registers (80H to FFH) are directly addressable only.

- 4. The expanded RAM of 768 Bytes (00H to 2FFH) is indirectly addressable by the move external instruction (MOVX) and clearing the EXTRAM bit. (See "Auxiliary Register (AUXR)" in Section , "Special Function Registers")

Since the upper 128 bytes occupy the same addresses as the SFRs, the RAM must be accessed indirectly. The RAM and SFRs space are physically separate even though they have the same addresses.

When instructions access addresses in the upper 128 bytes (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

#### Indirect Access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in "#data" is written to RAM location 90H rather than port 1.

#### **Direct Access:**

MOV90H, #data; write data to P1

Data in "#data" is written to port 1. Instructions that write directly to the address write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 bytes of memory is physically located on the chip and logically occupies the first 768 bytes of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 (WR#), P3.7 (RD#), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

#### Expanded RAM Access (Indirect Addressing only):

MOVX@DPTR, A; DPTR contains 0A0H

DPTR points to 0A0H and data in "A" is written to address 0A0H of the expanded RAM rather than external memory. Access to external memory higher than 2FFH using the MOVX instruction will access external memory (0300H to FFFFH) and will perform in the same way as the standard 8051, with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals.

When EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 8051. Using MOVX @Ri provides an 8-bit address with multiplexed data on Port 0. Other output port pins can be used to output higher order address bits. This provides external paging capabilities. Using MOVX

#### Not Recommended for New Designs

#### PCA Compare/Capture Module Mode Register<sup>1</sup> (CCAPMn)

| omparo, capturo n |                                                                        | ao nogio                                                                                                        |               |              |               |              |              |                |             |

|-------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------|--------------|---------------|--------------|--------------|----------------|-------------|

| Location          | 7                                                                      | 6                                                                                                               | 5             | 4            | 3             | 2            | 1            | 0              | Reset Value |

| DAH               | -                                                                      | ECOM0                                                                                                           | CAPP0         | CAPN0        | MAT0          | TOG0         | PWM0         | ECCF0          | 00xxx000b   |

| DBH               | -                                                                      | ECOM1                                                                                                           | CAPP1         | CAPN1        | MAT1          | TOG1         | PWM1         | ECCF1          | 00xxx000b   |

| DCH               | -                                                                      | ECOM2                                                                                                           | CAPP2         | CAPN2        | MAT2          | TOG2         | PWM2         | ECCF2          | 00xxx000b   |

| DDH               | -                                                                      | ECOM3                                                                                                           | CAPP3         | CAPN3        | MAT3          | TOG3         | PWM3         | ECCF3          | 00xxx000b   |

| DEH               | -                                                                      | ECOM4                                                                                                           | CAPP4         | CAPN4        | MAT4          | TOG4         | PWM4         | ECCF4          | 00xxx000b   |

|                   | 1. Not bit a                                                           | addressable                                                                                                     |               | •            |               | •            |              |                |             |

| Symbol            | Function                                                               |                                                                                                                 |               |              |               |              |              |                |             |

| -                 | N                                                                      | ot impleme                                                                                                      | ented, rese   | erved for f  | uture use.    |              |              |                |             |

|                   | No                                                                     | ote: User sho                                                                                                   | uld not write | 1's to reser | ved bits. The | e value read | from a reser | ved bit is ind | eterminate. |

| ECOMn             |                                                                        | hable Com                                                                                                       |               |              |               |              |              |                |             |

|                   |                                                                        | Disables t                                                                                                      |               |              |               |              |              |                |             |

|                   |                                                                        | Enables t                                                                                                       |               | rator funct  | ion           |              |              |                |             |

| CAPPn             |                                                                        | apture Pos                                                                                                      |               |              |               | [4.0]        |              |                |             |

|                   |                                                                        | Disables                                                                                                        |               | - ·          |               |              |              |                |             |

| CAPNn             |                                                                        | 1: Enables positive edge capture on CEX[4:0]                                                                    |               |              |               |              |              |                |             |

| CALINI            |                                                                        | Capture Negative<br>0: Disables negative edge capture on CEX[4:0]                                               |               |              |               |              |              |                |             |

|                   | 1: Enables negative edge capture on CEX[4:0]                           |                                                                                                                 |               |              |               |              |              |                |             |

| MATn              | Match: Set ECOM[4:0] and MAT[4:0] to implement the software timer mode |                                                                                                                 |               |              |               |              |              |                |             |

|                   |                                                                        | 0: Disables software timer mode                                                                                 |               |              |               |              |              |                |             |

|                   |                                                                        | 1: A match of the PCA counter with this module's compare/capture register causes                                |               |              |               |              |              |                |             |

|                   | the CCFn bit in CCON to be set, flagging an interrupt.                 |                                                                                                                 |               |              |               |              |              |                |             |

| TOGn              | Toggle                                                                 |                                                                                                                 |               |              |               |              |              |                |             |

|                   |                                                                        | 0: Disables toggle function<br>1: A match of the PCA counter with this module's compare/capture register causes |               |              |               |              |              | ter causes     |             |

|                   | the the CEXn pin to toggle.                                            |                                                                                                                 |               |              |               |              |              |                |             |

| PWMn              | Pu                                                                     | ulse Width                                                                                                      | Modulatio     | on mode      |               |              |              |                |             |

|                   | 0:                                                                     | Disables                                                                                                        | PWM mod       | le           |               |              |              |                |             |

|                   | 1:                                                                     | Enables (                                                                                                       | CEXn pin t    | o be used    | as a puls     | e width mo   | odulated o   | utput          |             |

| ECCFn             |                                                                        | hable CCF                                                                                                       |               |              |               |              |              |                |             |

|                   |                                                                        | Disables of terrupt req                                                                                         |               | apture flag  | g CCF[4:0     | ) in the CO  | CON regis    | ter to gene    | erate an    |

|                   |                                                                        | Enables c                                                                                                       |               | apture flag  | g CCF[4:0]    | ] in the CC  | ON regist    | er to gene     | rate an     |

|                   | in                                                                     | terrupt req                                                                                                     | uest.         |              |               |              |              |                |             |

|                   |                                                                        |                                                                                                                 |               |              |               |              |              |                |             |

#### Not Recommended for New Designs

| Serial Port Control Register (SCO | N) |  |

|-----------------------------------|----|--|

|-----------------------------------|----|--|

| Location     | 7                                                                                                                                                                                                                                                                                                                                                      | 6                        | 5                    | 4        | 3    | 2           | 1         | 0                        | Reset Value |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|----------|------|-------------|-----------|--------------------------|-------------|

| 98H          | SM0/FE                                                                                                                                                                                                                                                                                                                                                 | SM1                      | SM2                  | REN      | TB8  | RB8         | TI        | RI                       | 0000000b    |

| Symbol<br>FE | <b>Function</b><br>Set SMOD0 = 1 to access FE bit.                                                                                                                                                                                                                                                                                                     |                          |                      |          |      |             |           |                          |             |

|              | 0: No framing error<br>1: Framing Error. Set by receiver when an invalid stop bit is detected. This bit needs<br>to be cleared by software.                                                                                                                                                                                                            |                          |                      |          |      |             |           |                          |             |

| SM0          | -                                                                                                                                                                                                                                                                                                                                                      | MOD0 = 0<br>erial Port N |                      | SM0 bit. |      |             |           |                          |             |

| SM1          | Se                                                                                                                                                                                                                                                                                                                                                     | erial Port N             | lode Bit 1           |          |      |             |           |                          |             |

|              |                                                                                                                                                                                                                                                                                                                                                        | SM0                      | SM1                  | Moc      | e De | scription   | Baud Rate | e <sup>1</sup>           |             |

|              |                                                                                                                                                                                                                                                                                                                                                        | 0                        | 0                    | 0        |      | ft Register |           | clock mode<br>2 clock mo |             |

|              |                                                                                                                                                                                                                                                                                                                                                        | 0                        | 1                    | 1        |      | it UART     | Variable  |                          |             |

|              | 1 0 2 9-bit UART f <sub>OSC</sub> /32 or f <sub>OSC</sub> /16 (6 clock m<br>or<br>f <sub>OSC</sub> /64 or f <sub>OSC</sub> /32 (12 clock r                                                                                                                                                                                                             |                          |                      |          |      |             |           |                          |             |

|              |                                                                                                                                                                                                                                                                                                                                                        | 1                        | 1<br>scillator frequ | 3        | 9-b  | it UART     | Variable  |                          |             |

| SM2          | Enables the Automatic Address Recognition feature in Modes 2 or 3. If SM2 = 1 then RI will not be set unless the received 9th data bit (RB8) is 1, indicating an address, and the received byte is a given or broadcast address. In Mode 1, if SM2 = 1 then RI will not be activated unless a valid stop bit was received. In Mode 0, SM2 should be 0. |                          |                      |          |      |             |           |                          |             |

| REN          | Enables serial reception.<br>0: to disable reception.<br>1: to enable reception.                                                                                                                                                                                                                                                                       |                          |                      |          |      |             |           |                          |             |

| TB8          | The 9th data bit that will be transmitted in Modes 2 and 3. Set or clear by software as desired.                                                                                                                                                                                                                                                       |                          |                      |          |      |             |           |                          |             |

| RB8          | In Modes 2 and 3, the 9th data bit that was received. In Mode 1, if $SM2 = 0$ , RB8 is the stop bit that was received. In Mode 0, RB8 is not used.                                                                                                                                                                                                     |                          |                      |          |      |             |           |                          |             |

| TI           | Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission, Must be cleared by software.                                                                                                                                                    |                          |                      |          |      |             |           |                          |             |

| RI           | Receive interrupt flag. Set by hardware at the end of the8th bit time in Mode 0, or halfway through the stop bit time in the other modes, in any serial reception (except see SM2). Must be cleared by software.                                                                                                                                       |                          |                      |          |      |             |           |                          |             |

Not Recommended for New Designs

## **Flash Memory Programming**

The device internal flash memory can be programmed or erased using the In-Application Programming (IAP) mode.

### **Product Identification**

The Read-ID command accesses the Signature Bytes that identify the device and the manufacturer as SST. External programmers primarily use these Signature Bytes in the selection of programming algorithms.

#### Table 12: Product Identification

|                   | Address | Data |

|-------------------|---------|------|

| Manufacturer's ID | 30H     | BFH  |

| Device ID         |         |      |

| SST89E54RD2A/RDA  | 31H     | 9FH  |

| SST89E58RD2A/RDA  | 31H     | 9BH  |

T0-0.2 25114

### In-Application Programming Mode

The device offers either 24/40 KByte of in-application programmable flash memory. During in-application programming, the CPU of the microcontroller enters IAP mode. The two blocks of flash memory allow the CPU to execute user code from one block, while the other is being erased or reprogrammed concurrently. The CPU may also fetch code from an external memory while all internal flash is being reprogrammed. The mailbox registers (SFST, SFCM, SFAL, SFAH, SFDT and SFCF) located in the special function register (SFR), control and monitor the device's erase and program process.

Table 13 outline the commands and their associated mailbox register settings.

#### In-Application Programming Mode Clock Source

During IAP mode, both the CPU core and the flash controller unit are driven off the external clock. However, an internal oscillator will provide timing references for Program and Erase operations. The internal oscillator is only turned on when required, and is turned off as soon as the flash operation is completed.

#### Memory Bank Selection for In-Application Programming Mode

With the addressing range limited to 16 bit, only 64 KByte of program address space is "visible" at any one time. The bank selection (the configuration of EA# and SFCF[1:0]), allows Block 1 memory to be overlaid on the lowest 8 KByte of Block 0 memory, making Block 1 reachable. The same concept is employed to allow both Block 0 and Block 1 flash to be accessible to IAP operations. Code from a block that is not visible may not be used as a source to program another address. However, a block that is not "visible" may be programmed by code from the other block through mailbox registers.

The device allows IAP code in one block of memory to program the other block of memory, but may not program any location in the same block. If an IAP operation originates physically from Block 0, the target of this operation is implicitly defined to be in Block 1. If the IAP operation originates physically from

Not Recommended for New Designs

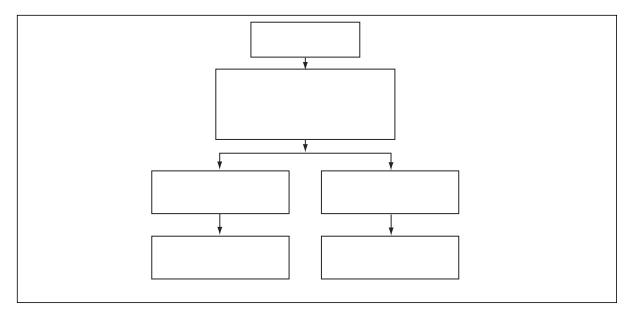

#### Sector-Erase

The Sector-Erase command erases all of the bytes in a sector. The sector size for the flash memory blocks is 128 Bytes. The selection of the sector to be erased is determined by the contents of SFAH and SFAL.

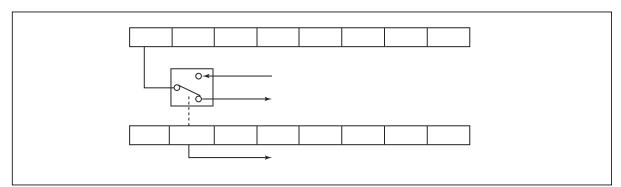

Figure 11:Sector-Erase

Not Recommended for New Designs

|                  |                                                         | T20                           | CON                           |

|------------------|---------------------------------------------------------|-------------------------------|-------------------------------|

|                  | Mode                                                    | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|                  | 16-bit Auto-Reload                                      | 00H                           | 08H                           |

|                  | 16-bit Capture                                          | 01H                           | 09H                           |

| Used as Timer    | Baud rate generator receive and transmit same baud rate | 34H                           | 36H                           |

|                  | Receive only                                            | 24H                           | 26H                           |

|                  | Transmit only                                           | 14H                           | 16H                           |

| Lload on Counter | 16-bit Auto-Reload                                      | 02H                           | 0AH                           |

| Used as Counter  | 16-bit Capture                                          | 03H                           | 0BH                           |

#### Table 16:Timer/Counter 2

1. Capture/Reload occurs only on timer/counter overflow.

T0-0.0 25114

2. Capture/Reload occurs on timer/counter overflow and a 1 to 0 transition on T2EX (P1.1) pin except when Timer 2 is used in the baud rate generating mode.

### **Programmable Clock-Out**

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

- 1. to input the external clock for Timer/Counter 2, or

- 2. to output a 50% duty cycle clock ranging from 122 Hz to 8 MHz at a 16 MHz operating frequency (61 Hz to 4 MHz in 12 clock mode).

To configure Timer/Counter 2 as a clock generator, bit

C/#T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

Oscillator Frequency n x (65536 - RCAP2H, RCAP2L)

n =2 (in 6 clock mode) 4 (in 12 clock mode)

Where (RCAP2H, RCAP2L) = the contents of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode, Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will not be the same.

Not Recommended for New Designs

## Serial I/O

### Full-Duplex, Enhanced UART

The device serial I/O port is a full-duplex port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The transmit and receive registers are both located in the Serial Data Buffer (SBUF) special function register. Writing to the SBUF register loads the transmit register, and reading from the SBUF register obtains the contents of the receive register.

The UART has four modes of operation which are selected by the Serial Port Mode Specifier (SM0 and SM1) bits of the Serial Port Control (SCON) special function register. In all four modes, transmission is initiated by any instruction that uses the SBUF register as a destination register. Reception is initiated in mode 0 when the Receive Interrupt (RI) flag bit of the Serial Port Control (SCON) SFR is cleared and the Reception Enable/ Disable (REN) bit of the SCON register is set. Reception is initiated in the other modes by the incoming start bit if the REN bit of the SCON register is set.

#### **Framing Error Detection**

Framing Error Detection is a feature, which allows the receiving controller to check for valid stop bits in modes 1, 2, or 3. Missing stops bits can be caused by noise in serial lines or from simultaneous transmission by two CPUs.

Framing Error Detection is selected by going to the PCON register and changing SMOD0 = 1 (see Figure 17). If a stop bit is missing, the Framing Error bit (FE) will be set. Software may examine the FE bit after each reception to check for data errors. After the FE bit has been set, it can only be cleared by software. Valid stop bits do not clear FE. When FE is enabled, RI rises on the stop bit, instead of the last data bit (see Figure 18 and Figure 19).

Figure 17: Framing Error Block Diagram

Not Recommended for New Designs

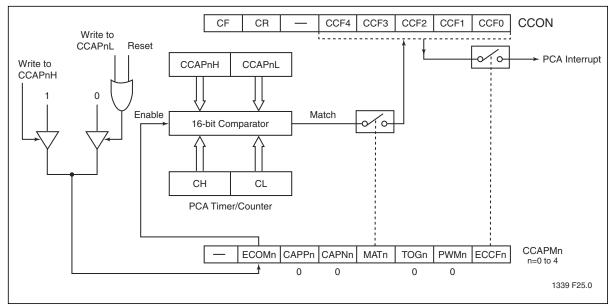

## **Programmable Counter Array**

The Programmable Counter Array (PCA) present on the SST89E/V5xRD2A/RDA is a special 16-bit timer that has five 16-bit capture/compare modules. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. The 5th module can be programmed as a Watchdog Timer in addition to the other four modes. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3 (CEX0), module 1 to P1[4] (CEX1), module 2 to P1[5] (CEX2), module 3 to P1[6] (CEX3), and module 4 to P1[7] (CEX4). PCA configuration is shown in Figure 24.

### **PCA** Overview

PCA provides more timing capabilities with less CPU intervention than the standard timer/counter. Its advantages include reduced software overhead and improved accuracy.

The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Figure 24 shows a block diagram of the PCA. External events associated with modules are shared with corresponding Port 1 pins. Modules not using the port pins can still be used for standard I/O.

Each of the five modules can be programmed in any of the following modes:

- Rising and/or falling edge capture

- Software timer

- High speed output

- Watchdog Timer (Module 4 only)

- Pulse Width Modulator (PWM)

### PCA Timer/Counter

The PCA timer is a free-running 16-bit timer consisting of registers CH and CL (the high and low bytes of the count values). The PCA timer is common time base for all five modules and can be programmed to run at: 1/6 the oscillator frequency, 1/2 the oscillator frequency, Timer 0 overflow, or the input on the ECI pin (P1.2). The timer/counter source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see "PCA Timer/Counter Mode Register (CMOD)" on page 27):

| CPS1 | CPS0 | 12 Clock Mode        | 6 Clock Mode                                                      |  |  |

|------|------|----------------------|-------------------------------------------------------------------|--|--|

| 0    | 0    | f <sub>OSC</sub> /12 | f <sub>OSC</sub> /6                                               |  |  |

| 0    | 1    | f <sub>OSC</sub> /4  | f <sub>OSC</sub> /2                                               |  |  |

| 1    | 0    | Timer 0 overflow     | Timer 0 overflow                                                  |  |  |

| 1    |      |                      | External clock at ECI pin<br>(maximum rate = f <sub>OSC</sub> /4) |  |  |

T0-0.0 25114

Not Recommended for New Designs

#### 16-Bit Software Timer Mode

The 16-bit software timer mode is used to trigger interrupt routines, which must occur at periodic intervals. It is setup by setting both the ECOM and MAT bits in the module's CCAPMn register. The PCA timer will be compared to the module's capture registers (CCAPnL and CCAPnH) and when a match occurs, an interrupt will occur, if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

If necessary, a new 16-bit compare value can be loaded into CCAPnH and CCAPnL during the interrupt routine. The user should be aware that the hardware temporarily disables the comparator function while these registers are being updated so that an invalid match will not occur. Thus, it is recommended that the user write to the low byte first (CCAPnL) to disable the comparator, then write to the high byte (CCAPnH) to re-enable it. If any updates to the registers are done, the user may want to hold off any interrupts from occurring by clearing the EA bit. (See Figure 26)

Figure 26: PCA Compare Mode (Software Timer)

#### Not Recommended for New Designs

|       |                                              | Source               | Target               | Byte-Verify Allowed        |     | MOVC Allowed |  |

|-------|----------------------------------------------|----------------------|----------------------|----------------------------|-----|--------------|--|

| Level | SFST[7:5]                                    | Address <sup>1</sup> | Address <sup>2</sup> | External Host <sup>3</sup> | IAP | 5xRDx        |  |

| 4     |                                              | Block 0/1            | Block 0/1            | N                          | N   | Y            |  |

|       | 111b                                         | BIOCK U/ I           | External             | N/A                        | N/A | Y            |  |

|       | (hard lock on both blocks)                   | Esternel             | Block 0/1            | N                          | N   | N            |  |

|       |                                              | External             | External             | N/A                        | N/A | Y            |  |

|       | 011b/101b<br>(hard lock on both blocks)      | Block 0/1            | Block 0/1            | N                          | N   | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | ) External           | Block 0/1            | N                          | N   | N            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | Block 0              | Block 0              | N                          | N   | Y            |  |

|       |                                              |                      | Block 1              | N                          | N   | N            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       | 001b/110b                                    | Block 1              | Block 0              | N                          | Y   | Y            |  |

|       | (Block 0 = SoftLock,<br>Block 1 = hard lock) |                      | Block 1              | N                          | N   | Y            |  |

| -     |                                              |                      | External             | N/A                        | N/A | Y            |  |

| 3     |                                              |                      | Block 0/1            | N                          | N   | N            |  |

| -     |                                              | External             | External             | N/A                        | N/A | Y            |  |

|       | 010b<br>(SoftLock on both blocks)            | Block 0              | Block 0              | N                          | N   | Y            |  |

|       |                                              |                      | Block 1              | N                          | Y   | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | Block 1              | Block 0              | N                          | Y   | Y            |  |

|       |                                              |                      | Block 1              | N                          | N   | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | External             | Block 0/1            | N                          | N   | N            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

| 2     | 100b<br>(SoftLock on both blocks)            | Block 0              | Block 0              | Y                          | N   | Y            |  |

|       |                                              |                      | Block 1              | Y                          | Y   | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | Block 1              | Block 0              | Y                          | Y   | Y            |  |

|       |                                              |                      | Block 1              | Y                          | N   | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | External             | Block 0/1            | Y                          | N   | N            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       | 000b<br>(unlock)                             | Block 0              | Block 0              | Y                          | N   | Y            |  |

|       |                                              |                      | Block 1              | Y                          | Y   | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | Block 1              | Block 0              | Y                          | Y   | Y            |  |

| 1     |                                              |                      | Block 1              | Y                          | N.  | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

|       |                                              | External             | Block 0/1            | Y                          | Y   | Y            |  |

|       |                                              |                      | External             | N/A                        | N/A | Y            |  |

#### Table 25: Security Lock Access Table

1. Location of MOVC or IAP instruction

2. Target address is the location of the byte being read

3. External host Byte-Verify access does not depend on a source address.

T0-0.0 25114

Not Recommended for New Designs

#### **Software Reset**

The software reset is executed by changing SFCF[1] (SWR) from "0" to "1". A software reset will reset the program counter to address 0000H. All SFR registers will be set to their reset values, except SFCF[1] (SWR), WDTC[2] (WDTS), and RAM data will not be altered.

#### **Brown-out Detection Reset**

The device includes a brown-out detection circuit to protect the system from severed supplied voltage  $V_{DD}$  fluctuations. SST89E5xRD2A/RDA internal brown-out detection threshold is 3.85V. For brown-out voltage parameters, please refer to Tables 35 and 36.

When  $V_{DD}$  drops below this voltage threshold, the brown-out detector triggers the circuit to generate a brown-out interrupt but the CPU still runs until the supplied voltage returns to the brown-out detection voltage  $V_{BOD}$ . The default operation for a brown-out detection is to cause a processor reset.

$V_{\text{DD}}$  must stay below  $V_{\text{BOD}}$  at least four oscillator clock periods before the brown-out detection circuit will respond.

Brown-out interrupt can be enabled by setting the EBO bit in IEA register (address E8H, bit 3). If EBO bit is set and a brown-out condition occurs, a brown-out interrupt will be generated to execute the program at location 004BH. It is required that the EBO bit be cleared by software after the brown-out interrupt is serviced. Clearing EBO bit when the brown-out condition is active will properly reset the device. If brown-out interrupt is not enabled, a brown-out condition will reset the program to resume execution at location 0000H.

Not Recommended for New Designs

## **System Clock and Clock Options**

### **Clock Input Options and Recommended Capacitor Values for Oscillator**

Shown in Figure 33 are the input and output of an internal inverting amplifier (XTAL1, XTAL2), which can be configured for use as an on-chip oscillator.

When driving the device from an external clock source, XTAL2 should be left disconnected and XTAL1 should be driven.

At start-up, the external oscillator may encounter a higher capacitive load at XTAL1 due to interaction between the amplifier and its feedback capacitance. However, the capacitance will not exceed 15 pF once the external signal meets the  $V_{IL}$  and  $V_{IH}$  specifications.

Crystal manufacturer, supply voltage, and other factors may cause circuit performance to differ from one application to another. C1 and C2 should be adjusted appropriately for each design. Table 28, shows the typical values for C1 and C2 vs. crystal type for various frequencies

#### Table 28: Recommended Values for C1 and C2 by Crystal Type

| Crystal | C1 = C2 |

|---------|---------|

| Quartz  | 20-30pF |

| Ceramic | 40-50pF |

T0-0.0 25114

More specific information about on-chip oscillator design can be found in the *FlashFlex Oscillator Circuit Design Considerations* application note.

Not Recommended for New Designs

## **Electrical Specification**

**Absolute Maximum Stress Ratings** (Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| Ambient Temperature Under Bias                                |                                                    |

|---------------------------------------------------------------|----------------------------------------------------|

| Storage Temperature                                           | 65°C to +150°C                                     |

| Voltage on EA# Pin to V <sub>SS</sub>                         | 0.5V to +14.0V                                     |

| D.C. Voltage on Any Pin to Ground Potential                   | $\dots \dots \dots$ -0.5V to V <sub>DD</sub> +0.5V |

| Transient Voltage (<20ns) on Any Other Pin to V <sub>SS</sub> | 1.0V to V <sub>DD</sub> +1.0V                      |

| Maximum I <sub>OL</sub> per I/O Pins P1.5, P1.6, P1.7         | 20mA                                               |

| Maximum I <sub>OL</sub> per I/O for All Other Pins            | 15mA                                               |

| Package Power Dissipation Capability (T <sub>A</sub> = 25°C)  | 1.5W                                               |

| Through Hole Lead Soldering Temperature (10 Seconds)          | 300°C                                              |

| Surface Mount Solder Reflow Temperature <sup>1</sup>          | 260°C for 10 seconds                               |

| Output Short Circuit Current <sup>2</sup>                     | 50 mA                                              |

1. Excluding certain with-Pb 32-PLCC units, all packages are 260°C capable in both non-Pb and with-Pb solder versions. Certain with-Pb 32-PLCC package types are capable of 240°C for 10 seconds; please consult the factory for the latest information.

2. Outputs shorted for no more than one second. No more than one output shorted at a time.

(Based on package heat transfer limitations, not device power consumption. **Note:** This specification contains preliminary information on new products in production.

Specifications are subject to change without notice.

| Table | <b>30:</b> Operating | Range |

|-------|----------------------|-------|

|-------|----------------------|-------|

| Symbol           | Description                    | Min. | Max | Unit |

|------------------|--------------------------------|------|-----|------|

| T <sub>A</sub>   | Ambient Temperature Under Bias |      |     |      |

|                  | Standard                       | 0    | +70 | °C   |

| V <sub>DD</sub>  | Supply Voltage                 |      |     |      |

|                  | SST89E5xRD2A/RDA               | 4.5  | 5.5 | V    |

| f <sub>OSC</sub> | Oscillator Frequency           |      |     |      |

|                  | SST89E5xRD2A/RDA               | 0    | 40  | MHz  |

|                  | Oscillator Frequency for IAP   |      |     |      |

|                  | SST89E5xRD2A/RDA               | 0.25 | 40  | MHz  |

T0-0.0 25114

#### Table 31: Reliability Characteristics

| Symbol                        | Parameter      | Minimum Specification | Units  | Test Method         |

|-------------------------------|----------------|-----------------------|--------|---------------------|

| N <sub>END</sub> <sup>1</sup> | Endurance      | 10,000                | Cycles | JEDEC Standard A117 |

| T <sub>DR</sub> <sup>1</sup>  | Data Retention | 100                   | Years  | JEDEC Standard A103 |

| ILTH <sup>1</sup>             | Latch Up       | 100 + I <sub>DD</sub> | mA     | JEDEC Standard 78   |

|                               |                |                       |        | T0-0.0 25114        |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

#### Not Recommended for New Designs

- $1. Under steady state (non-transient) conditions, I_{OL} must be externally limited as follows: Maximum I_{OL} per port pin: 15mA Maximum I_{OL} per 8-bit port:26mA Maximum I_{OL} total for all outputs:71mA If I_{OL} exceeds the test condition, V_{OL} may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.$

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise due to external bus capacitance discharging into the Port 0 and 2 pins when the pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

- 3. Load capacitance for Port 0, ALE and PSEN#= 100pF, load capacitance for all other outputs = 80pF.

- 4. Capacitive loading on Ports 0 and 2 may cause the  $V_{OH}$  on ALE and PSEN# to momentarily fall below the  $V_{DD}$  0.7 specification when the address bits are stabilizing.

- 5. Pins of Ports 1, 2, and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2V.

- 6. Pin capacitance is characterized but not tested. EA# is 25pF (max).

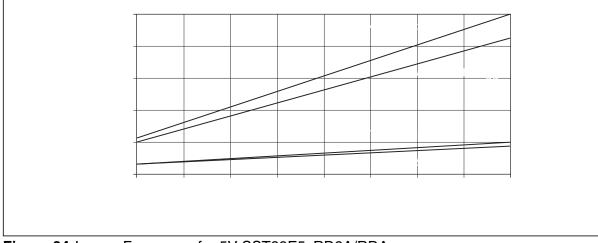

Figure 34:I<sub>DD</sub> vs. Frequency for 5V SST89E5xRD2A/RDA

Not Recommended for New Designs

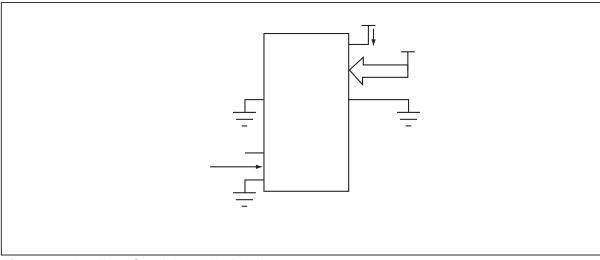

### Figure 45:I<sub>DD</sub> Test Condition, Power-down Mode

| Parameter <sup>2</sup>              | Мах | Units |

|-------------------------------------|-----|-------|

| Chip-Erase Time                     | 150 | ms    |

| Block-Erase Time                    | 100 | ms    |

| Sector-Erase Time                   | 30  | ms    |

| Byte-Program Time <sup>3</sup>      | 50  | μs    |

| Re-map or Security bit Program Time | 80  | μs    |

T0-0.0 25114

1. For IAP operations, the program execution overhead must be added to the above timing parameters.

2. Program and Erase times will scale inversely proportional to programming clock frequency.

3. Each byte must be erased before programming.

Not Recommended for New Designs

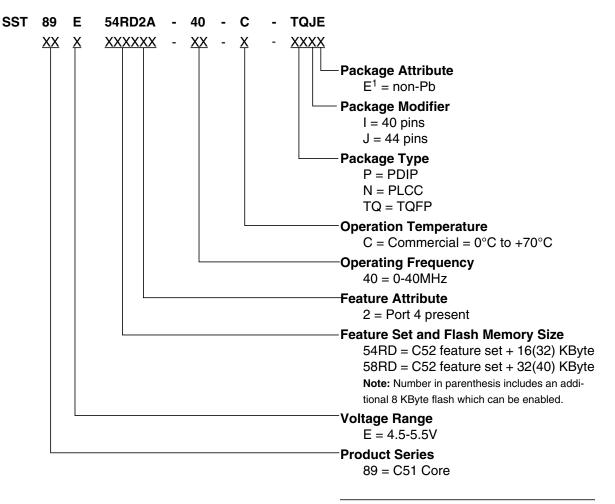

## **Product Ordering Information**

Environmental suffix "E" denotes non-Pb solder. SST non-Pb solder devices are "RoHS Compliant".