Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                               |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051c4t6 |

|   |       | 3.14.6   | SysTick timer                                                                    | . 23 |

|---|-------|----------|----------------------------------------------------------------------------------|------|

|   | 3.15  | Real-tir | me clock (RTC) and backup registers                                              | . 23 |

|   | 3.16  | Inter-in | tegrated circuit interface (I <sup>2</sup> C)                                    | . 24 |

|   | 3.17  | Univers  | sal synchronous/asynchronous receiver/transmitter (USART)                        | . 25 |

|   | 3.18  |          | peripheral interface (SPI) / Inter-integrated sound interface (I <sup>2</sup> S) |      |

|   | 3.19  | High-de  | efinition multimedia interface (HDMI) - consumer nics control (CEC)              |      |

|   | 3.20  | Serial v | wire debug port (SW-DP)                                                          | . 26 |

| 4 | Pino  | uts and  | pin descriptions                                                                 | . 27 |

| 5 | Mem   | ory map  | oping                                                                            | . 39 |

| 6 | Elect | rical ch | aracteristics                                                                    | . 42 |

|   | 6.1   | Parame   | eter conditions                                                                  | . 42 |

|   |       | 6.1.1    | Minimum and maximum values                                                       | . 42 |

|   |       | 6.1.2    | Typical values                                                                   | . 42 |

|   |       | 6.1.3    | Typical curves                                                                   | . 42 |

|   |       | 6.1.4    | Loading capacitor                                                                | . 42 |

|   |       | 6.1.5    | Pin input voltage                                                                | . 42 |

|   |       | 6.1.6    | Power supply scheme                                                              | . 43 |

|   |       | 6.1.7    | Current consumption measurement                                                  | . 44 |

|   | 6.2   | Absolu   | te maximum ratings                                                               | . 45 |

|   | 6.3   | Operati  | ing conditions                                                                   | . 47 |

|   |       | 6.3.1    | General operating conditions                                                     | . 47 |

|   |       | 6.3.2    | Operating conditions at power-up / power-down                                    | . 47 |

|   |       | 6.3.3    | Embedded reset and power control block characteristics                           | . 48 |

|   |       | 6.3.4    | Embedded reference voltage                                                       | . 49 |

|   |       | 6.3.5    | Supply current characteristics                                                   | . 49 |

|   |       | 6.3.6    | Wakeup time from low-power mode                                                  | . 59 |

|   |       | 6.3.7    | External clock source characteristics                                            | . 59 |

|   |       | 6.3.8    | Internal clock source characteristics                                            | . 63 |

|   |       | 6.3.9    | PLL characteristics                                                              | . 66 |

|   |       | 6.3.10   | Memory characteristics                                                           | . 66 |

|   |       | 6.3.11   | EMC characteristics                                                              | . 67 |

|   |       | 6.3.12   | Electrical sensitivity characteristics                                           | . 68 |

|   |       | 6.3.13   | I/O current injection characteristics                                            | . 69 |

|   |       |          |                                                                                  |      |

# List of tables

| Table 1.  | Device summary                                                                                | 1  |

|-----------|-----------------------------------------------------------------------------------------------|----|

| Table 2.  | STM32F051xx family device features and peripheral count                                       | 11 |

| Table 3.  | Temperature sensor calibration values                                                         | 18 |

| Table 4.  | Internal voltage reference calibration values                                                 |    |

| Table 5.  | Capacitive sensing GPIOs available on STM32F051xx devices                                     | 20 |

| Table 6.  | Effective number of capacitive sensing channels on STM32F051xx                                | 20 |

| Table 7.  | Timer feature comparison                                                                      |    |

| Table 8.  | Comparison of I <sup>2</sup> C analog and digital filters                                     | 24 |

| Table 9.  | STM32F051xx I <sup>2</sup> C implementation                                                   | 24 |

| Table 10. | STM32F051xx USART implementation                                                              | 25 |

| Table 11. | STM32F051xx SPI/I <sup>2</sup> S implementation                                               | 26 |

| Table 12. | Legend/abbreviations used in the pinout table                                                 | 31 |

| Table 13. | Pin definitions                                                                               | 31 |

| Table 14. | Alternate functions selected through GPIOA_AFR registers for port A                           |    |

| Table 15. | Alternate functions selected through GPIOB_AFR registers for port B                           | 38 |

| Table 16. | STM32F051xx peripheral register boundary addresses                                            | 40 |

| Table 17. | Voltage characteristics                                                                       | 45 |

| Table 18. | Current characteristics                                                                       | 46 |

| Table 19. | Thermal characteristics                                                                       |    |

| Table 20. | General operating conditions                                                                  |    |

| Table 21. | Operating conditions at power-up / power-down                                                 | 48 |

| Table 22. | Embedded reset and power control block characteristics                                        | 48 |

| Table 23. | Programmable voltage detector characteristics                                                 | 48 |

| Table 24. | Embedded internal reference voltage                                                           | 49 |

| Table 25. | Typical and maximum current consumption from V <sub>DD</sub> at 3.6 V                         | 50 |

| Table 26. | Typical and maximum current consumption from the V <sub>DDA</sub> supply                      | 51 |

| Table 27. | Typical and maximum current consumption in Stop and Standby modes                             | 52 |

| Table 28. | Typical and maximum current consumption from the V <sub>BAT</sub> supply                      | 53 |

| Table 29. | Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal | 54 |

| Table 30. | Switching output I/O current consumption                                                      |    |

| Table 31. | Peripheral current consumption                                                                |    |

| Table 32. | Low-power mode wakeup timings                                                                 |    |

| Table 33. | High-speed external user clock characteristics                                                |    |

| Table 34. | Low-speed external user clock characteristics                                                 |    |

| Table 35. | HSE oscillator characteristics                                                                |    |

| Table 36. | LSE oscillator characteristics (f <sub>LSF</sub> = 32.768 kHz)                                | 62 |

| Table 37. | HSI oscillator characteristics                                                                | 64 |

| Table 38. | HSI14 oscillator characteristics                                                              | 65 |

| Table 39. | LSI oscillator characteristics                                                                | 66 |

| Table 40. | PLL characteristics                                                                           | 66 |

| Table 41. | Flash memory characteristics                                                                  | 66 |

| Table 42. | Flash memory endurance and data retention                                                     | 67 |

| Table 43. | EMS characteristics                                                                           |    |

| Table 44. | EMI characteristics                                                                           |    |

| Table 45. | ESD absolute maximum ratings                                                                  | 69 |

| Table 46. | Electrical sensitivities                                                                      | 69 |

| Table 47  | I/O current injection susceptibility                                                          | 70 |

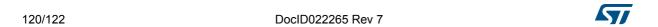

Figure 1. Block diagram

can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

## 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, or at wake up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop and Standby mode capability

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- two anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

Table 9. STM32F051xx I<sup>2</sup>C implementation (continued)

| I <sup>2</sup> C features <sup>(1)</sup> | I2C1 | I2C2 |

|------------------------------------------|------|------|

| SMBus                                    | Х    | -    |

| Wakeup from STOP                         | Х    | -    |

<sup>1.</sup> X = supported.

# 3.17 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds up to two universal synchronous/asynchronous receivers/transmitters (USART1, USART2) which communicate at speeds of up to 6 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 supports also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and has a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interfaces can be served by the DMA controller.

Table 10. STM32F051xx USART implementation

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 |

|---------------------------------------------|--------|--------|

| Hardware flow control for modem             | Х      | X      |

| Continuous communication using DMA          | Х      | Х      |

| Multiprocessor communication                | Х      | Х      |

| Synchronous mode                            | Х      | Х      |

| Smartcard mode                              | Х      | -      |

| Single-wire half-duplex communication       | Х      | Х      |

| IrDA SIR ENDEC block                        | Х      | -      |

| LIN mode                                    | Х      | -      |

| Dual clock domain and wakeup from Stop mode | Х      | -      |

| Receiver timeout interrupt                  | Х      | -      |

| Modbus communication                        | Х      | -      |

| Auto baud rate detection                    | Х      | -      |

| Driver Enable                               | Х      | Х      |

<sup>1.</sup> X = supported.

## 6 Electrical characteristics

#### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

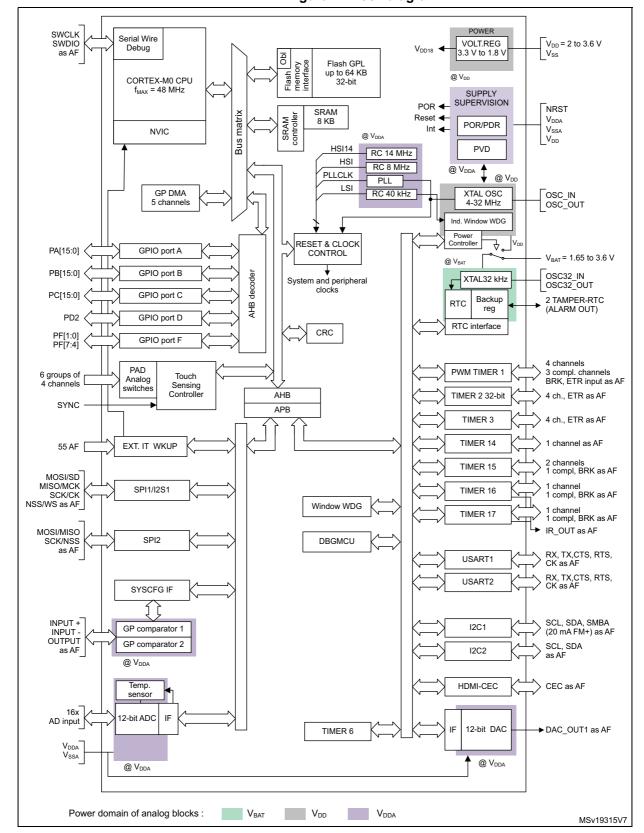

#### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 11.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 12.

577

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 17: Voltage characteristics*, *Table 18: Current characteristics* and *Table 19: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 17. Voltage characteristics<sup>(1)</sup>

| Symbol                             | Ratings                                                 | Min                               | Max                         | Unit |

|------------------------------------|---------------------------------------------------------|-----------------------------------|-----------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>   | External main supply voltage                            | - 0.3                             | 4.0                         | V    |

| V <sub>DDA</sub> -V <sub>SS</sub>  | External analog supply voltage                          | - 0.3                             | 4.0                         | V    |

| V <sub>DD</sub> –V <sub>DDA</sub>  | Allowed voltage difference for $V_{DD} > V_{DDA}$       | -                                 | 0.4                         | V    |

| V <sub>BAT</sub> -V <sub>SS</sub>  | External backup supply voltage                          | - 0.3                             | 4.0                         | ٧    |

|                                    | Input voltage on FT and FTf pins                        | V <sub>SS</sub> - 0.3             | $V_{\rm DDIOx} + 4.0^{(3)}$ | V    |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on TTa pins                               | V <sub>SS</sub> - 0.3             | 4.0                         | ٧    |

| VIN.                               | воото                                                   | 0                                 | 9.0                         | V    |

|                                    | Input voltage on any other pin                          | V <sub>SS</sub> - 0.3             | 4.0                         | V    |

| ΔV <sub>DDx</sub>                  | Variations between different V <sub>DD</sub> power pins | -                                 | 50                          | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins        | -                                 | 50                          | mV   |

| V <sub>ESD(HBM)</sub>              | Electrostatic discharge voltage (human body model)      | see Section 6.3 sensitivity chara | -                           |      |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum must always be respected. Refer to *Table 18: Current characteristics* for the maximum allowed injected current values.

Valid only if the internal pull-up/pull-down resistors are disabled. If internal pull-up or pull-down resistor is enabled, the maximum limit is 4 V.

Max<sup>(1)</sup> Typ @ V<sub>BAT</sub> **Symbol Conditions** Unit **Parameter** 3.3 V 1.8 V T<sub>A</sub> = 85 °C T<sub>A</sub> = 105 °C 1.65  $T_A =$ 3.6 25°C LSE & RTC ON; "Xtal mode": lower driving 0.5 0.5 0.6 0.7 8.0 0.9 1.0 1.3 1.7 capability; RTC LSEDRV[1:0] = '00' domain μΑ I<sub>DD\_VBAT</sub> supply LSE & RTC ON; "Xtal current mode" higher driving 8.0 8.0 0.9 1.0 1.1 1.2 1.3 1.6 2.1 capability; LSEDRV[1:0] = '11'

Table 28. Typical and maximum current consumption from the V<sub>BAT</sub> supply

#### **Typical current consumption**

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

<sup>1.</sup> Data based on characterization results, not tested in production.

Guaranteed by design, not tested in production.

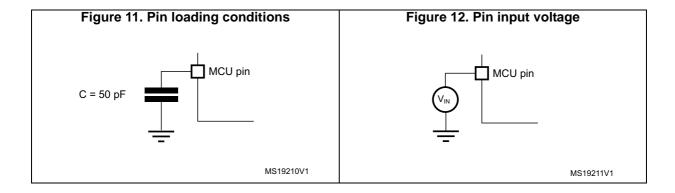

Figure 15. High-speed external clock source AC timing diagram

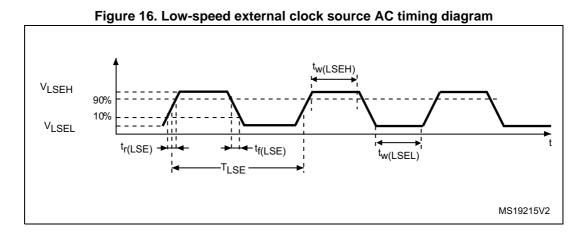

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in Figure 16.

| Symbol                                                                 | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|------------------------------------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                                                   | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| $V_{LSEH}$                                                             | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | $V_{DDIOx}$            | V    |

| $V_{LSEL}$                                                             | OSC32_IN input pin low level voltage  | $V_{SS}$               | -      | 0.3 V <sub>DDIOx</sub> | V    |

| $\begin{matrix} t_{w(\text{LSEH})} \\ t_{w(\text{LSEL})} \end{matrix}$ | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| $t_{r(LSE)}$ $t_{f(LSE)}$                                              | OSC32_IN rise or fall time            | -                      | -      | 50                     | 113  |

Table 34. Low-speed external user clock characteristics

<sup>1.</sup> Guaranteed by design, not tested in production.

## High-speed internal (HSI) RC oscillator

Table 37. HSI oscillator characteristics<sup>(1)</sup>

| Symbol                | Parameter                        | Conditions                    | Min                 | Тур | Max                | Unit |

|-----------------------|----------------------------------|-------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                        | -                             | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step           | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                       | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

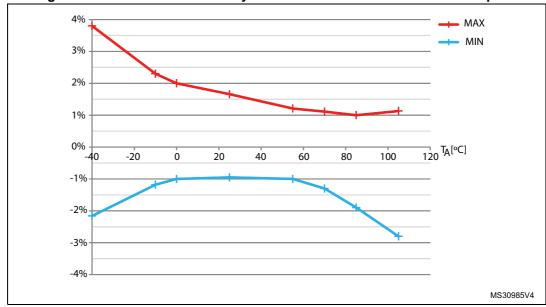

|                       |                                  | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |

|                       | Accuracy of the HSI oscillator   | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |

| ACC                   |                                  | T <sub>A</sub> = 0 to 85°C    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

| ACC <sub>HSI</sub>    |                                  | T <sub>A</sub> = 0 to 70°C    | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | T <sub>A</sub> = 0 to 55°C    | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time      | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption | -                             | -                   | 80  | 100 <sup>(2)</sup> | μΑ   |

- 1.  $V_{DDA} = 3.3 \text{ V}$ ,  $T_A = -40 \text{ to } 105^{\circ}\text{C}$  unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

- 4. Factory calibrated, parts not soldered.

Figure 19. HSI oscillator accuracy characterization results for soldered parts

64/122 DocID022265 Rev 7

# 6.3.17 DAC electrical specifications

**Table 55. DAC characteristics**

| Symbol                           | Parameter                                                                                                    | Min | Тур | Max                     | Unit | Comments                                                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|------|------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                 | Analog supply voltage for DAC ON                                                                             | 2.4 | -   | 3.6                     | ٧    | -                                                                                                                      |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer                                                                                   | 5   | -   | -                       | kΩ   | Load connected to V <sub>SSA</sub>                                                                                     |

| NLOAD.                           | ON                                                                                                           | 25  | -   | -                       | kΩ   | Load connected to V <sub>DDA</sub>                                                                                     |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with buffer OFF                                                                             | -   | -   | 15                      | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 $M\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | ı   | -   | 50                      | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                        |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                       | ٧    | It gives the maximum output excursion of the DAC. It corresponds to 12-bit input code (0x0E0) to (0xF1C) at            |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2  | V    | $V_{\rm DDA}$ = 3.6 V and (0x155) and (0xEAB) at $V_{\rm DDA}$ = 2.4 V                                                 |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                       | mV   | It gives the maximum output                                                                                            |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer OFF                                                                       | -   | -   | V <sub>DDA</sub> – 1LSB | V    | excursion of the DAC.                                                                                                  |

| I <sub>DDA</sub> <sup>(1)</sup>  | DAC DC current consumption in quiescent                                                                      | -   | -   | 600                     | μA   | With no load, middle code (0x800) on the input                                                                         |

| ·DDA                             | mode <sup>(2)</sup>                                                                                          | -   | -   | 700                     | μA   | With no load, worst code (0xF1C) on the input                                                                          |

| DNL <sup>(3)</sup>               | Differential non linearity Difference between two                                                            | -   | -   | ±0.5                    | LSB  | Given for the DAC in 10-bit configuration                                                                              |

|                                  | consecutive code-1LSB)                                                                                       | -   | -   | ±2                      | LSB  | Given for the DAC in 12-bit configuration                                                                              |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                      | LSB  | Given for the DAC in 10-bit configuration                                                                              |

| INL <sup>(3)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                      | LSB  | Given for the DAC in 12-bit configuration                                                                              |

|                                  | Offset error                                                                                                 | -   | -   | ±10                     | mV   | -                                                                                                                      |

| Offset <sup>(3)</sup>            | (difference between measured value at Code                                                                   | -   | -   | ±3                      | LSB  | Given for the DAC in 10-bit at V <sub>DDA</sub> = 3.6 V                                                                |

|                                  | (0x800) and the ideal value<br>= V <sub>DDA</sub> /2)                                                        | -   | -   | ±12                     | LSB  | Given for the DAC in 12-bit at V <sub>DDA</sub> = 3.6 V                                                                |

|                                  |                                                                                                              |     |     |                         |      |                                                                                                                        |

80/122 DocID022265 Rev 7

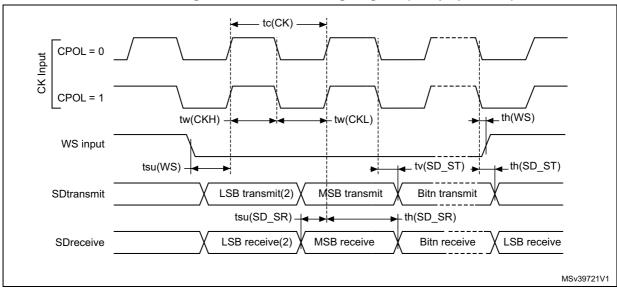

| Symbol                               | Parameter               | Conditions         | Min | Max | Unit |

|--------------------------------------|-------------------------|--------------------|-----|-----|------|

| t <sub>su(SD_MR)</sub>               | Data input setup time   | Master receiver    | 6   | -   |      |

| t <sub>su(SD_SR)</sub>               | Data input setup time   | Slave receiver     | 2   | -   |      |

| t <sub>h(SD_MR)</sub> <sup>(2)</sup> | Data input hold time    | Master receiver    | 4   | -   |      |

| t <sub>h(SD_SR)</sub> (2)            | Data input hold time    | Slave receiver     | 0.5 | -   | 200  |

| t <sub>v(SD_MT)</sub> <sup>(2)</sup> | Data output valid time  | Master transmitter | -   | 4   | ns   |

| t <sub>v(SD_ST)</sub> <sup>(2)</sup> | Data output valid time  | Slave transmitter  | -   | 20  |      |

| t <sub>h(SD_MT)</sub>                | Data output hold time   | Master transmitter | 0   | -   |      |

| t <sub>h(SD_ST)</sub>                | Data output Hold tillle | Slave transmitter  | 13  | -   |      |

Table 64. I<sup>2</sup>S characteristics<sup>(1)</sup> (continued)

- 1. Data based on design simulation and/or characterization results, not tested in production.

- 2. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$  = 8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  = 125 ns.

Figure 32. I<sup>2</sup>S slave timing diagram (Philips protocol)

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DDIOx}$  and  $0.7 \times V_{DDIOx}$

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

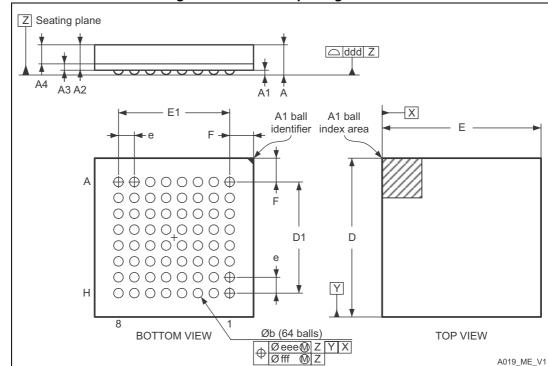

## 7.1 UFBGA64 package information

UFBGA64 is a 64-ball, 5 x 5 mm, 0.5 mm pitch ultra-fine-profile ball grid array package.

Figure 34. UFBGA64 package outline

1. Drawing is not to scale.

Table 65. UFBGA64 package mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| А      | 0.460 | 0.530       | 0.600 | 0.0181 | 0.0209                | 0.0236 |

| A1     | 0.050 | 0.080       | 0.110 | 0.0020 | 0.0031                | 0.0043 |

| A2     | 0.400 | 0.450       | 0.500 | 0.0157 | 0.0177                | 0.0197 |

| A3     | 0.080 | 0.130       | 0.180 | 0.0031 | 0.0051                | 0.0071 |

| A4     | 0.270 | 0.320       | 0.370 | 0.0106 | 0.0126                | 0.0146 |

#### **Device marking**

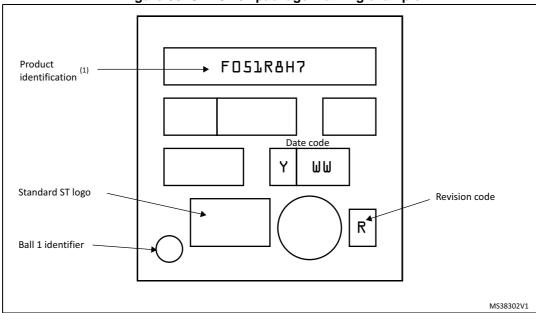

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 36. UFBGA64 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

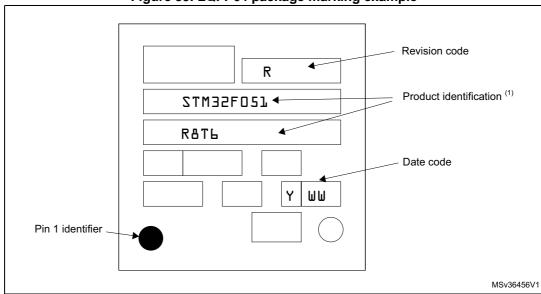

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 39. LQFP64 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

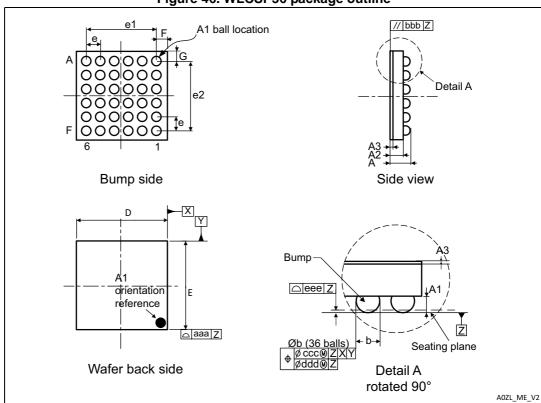

# 7.5 WLCSP36 package information

WLCSP36 is a 36-ball, 2.605 x 2.703 mm, 0.4 mm pitch wafer-level chip-scale package.

Figure 46. WLCSP36 package outline

1. Drawing is not to scale.

Table 70. WLCSP36 package mechanical data

| Symbol            | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol            | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А                 | 0.525       | 0.555 | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1                | -           | 0.175 | -     | -                     | 0.0069 | -      |

| A2                | -           | 0.380 | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup> | -           | 0.025 | -     | -                     | 0.0010 | -      |

| b <sup>(3)</sup>  | 0.220       | 0.250 | 0.280 | 0.0087                | 0.0098 | 0.0110 |

| D                 | 2.570       | 2.605 | 2.640 | 0.1012                | 0.1026 | 0.1039 |

| Е                 | 2.668       | 2.703 | 2.738 | 0.1050                | 0.1064 | 0.1078 |

| е                 | -           | 0.400 | -     | -                     | 0.0157 | -      |

| e1                | -           | 2.000 | -     | -                     | 0.0787 | -      |

| e2                | -           | 2.000 | -     | -                     | 0.0787 | -      |

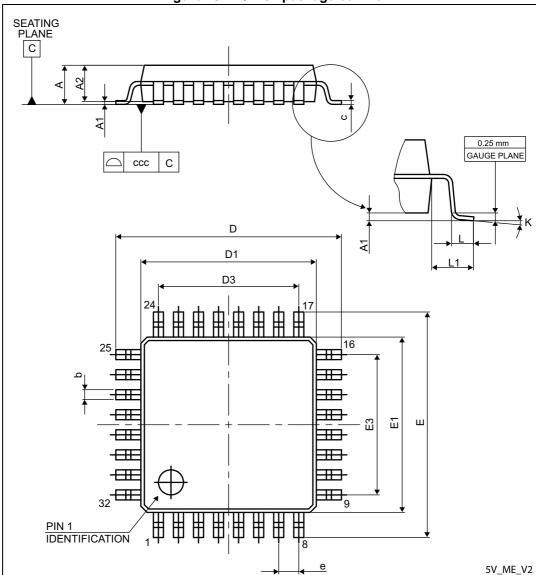

# 7.6 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

Figure 49. LQFP32 package outline

1. Drawing is not to scale.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F051xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 8 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

$P_{INTmax} = 50 \text{ mA} \times 3.5 \text{ V} = 175 \text{ mW}$

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} + 8 \times 20 \text{ mA} \times 1.3 \text{ V} = 272 \text{ mW}$

This gives: P<sub>INTmax</sub> = 175 mW and P<sub>IOmax</sub> = 272 mW:

$P_{Dmax} = 175 + 272 = 447 \text{ mW}$

Using the values obtained in *Table 74*  $T_{Jmax}$  is calculated as follows:

For LQFP64, 45 °C/W

$T_{\text{lmax}}$  = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.115 °C = 102.115 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C) see *Table 20: General operating conditions*.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Section 8: Ordering information).

Note:

With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

```

Suffix 6: T_{Amax} = T_{Jmax} - (45^{\circ}\text{C/W} \times 447 \text{ mW}) = 105\text{-}20.115 = 84.885 ^{\circ}\text{C}

Suffix 7: T_{Amax} = T_{Jmax} - (45^{\circ}\text{C/W} \times 447 \text{ mW}) = 125\text{-}20.115 = 104.885 ^{\circ}\text{C}

```

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 100 °C (measured according to JESD51-2),  $I_{DDmax}$  = 20 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V

$P_{INTmax}$  = 20 mA × 3.5 V= 70 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :

$P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus:  $P_{Dmax} = 134 \text{ mW}$

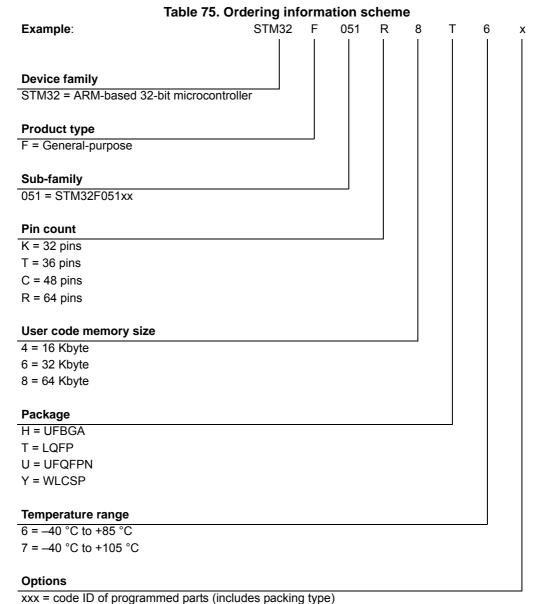

#### **Ordering information** 8

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

TR = tape and reel packing

blank = tray packing

Table 76. Document revision history (continued)

| Table 76. Document revision history (continued) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                                            | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 28-Aug-2015                                     | 5<br>(continued) | <ul> <li>Table 31: Peripheral current consumption</li> <li>Addition of WLCSP36 package. Updates in:</li> <li>Section 2: Description</li> <li>Table 2: STM32F051xx family device features and peripheral count</li> <li>Section 4: Pinouts and pin descriptions with the addition of Figure 7: WLCSP36 package pinout</li> <li>Table 13: Pin definitions</li> <li>Table 20: General operating conditions</li> <li>Section 7: Package information with the addition of Section 7.5: WLCSP36 package information</li> <li>Table 74: Package thermal characteristics</li> <li>Section 8: Part numbering</li> <li>Update of the device marking examples in Section 7: Package information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16-Dec-2015                                     | 6                | Section 2: Description:  - Table 2: STM32F051xx family device features and peripheral count - number of SPIs corrected for 64-pin packages  - Figure 1: Block diagram modified  Section 3: Functional overview:  - Figure 2: Clock tree modified; divider for CEC corrected  - Table 8: Comparison of I <sup>2</sup> C analog and digital filters - adding 20 mA information for FastPlus mode  Section 4: Pinouts and pin descriptions:  - Package pinout figures updated (look and feel)  - Figure 7: WLCSP36 package pinout - now presented in top view  - Table 13: Pin definitions - notes added (VSSA corrected to pin 16 on LQFP32); note 5 added  Section 5: Memory mapping:  - added information on STM32F051x4/x6 difference versus STM32F051x8 map in Figure 10  Section 6: Electrical characteristics:  - Table 24: Embedded internal reference voltage - removed - 40°C-85°C temperature range line and the associated note  - Table 48: I/O static characteristics - removed note  - Section 6.3.16: 12-bit ADC characteristics - changed introductory sentence  - Table 52: ADC characteristics updated and table footnotes 3 and 4 added  - Table 59: TIMx characteristics modified  - Table 59: TIMx characteristics modified  - Table 64: I <sup>2</sup> S characteristics reorganized  - Figure 52: UFQFPN32 package outline - figure footnotes added |