Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 39                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 13x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051c6t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 49. | LQFP32 package outline                          | 106 |

|------------|-------------------------------------------------|-----|

| Figure 50. | Recommended footprint for LQFP32 package        | 107 |

| Figure 51. | LQFP32 package marking example                  | 108 |

| Figure 52. | UFQFPN32 package outline                        | 109 |

| Figure 53. | Recommended footprint for UFQFPN32 package      | 110 |

| Figure 54. | UFQFPN32 package marking example                | 111 |

| Figure 55. | LQFP64 P <sub>D</sub> max versus T <sub>A</sub> | 114 |

8/122

In Standby mode, it is put in power down mode. In this mode, the regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost).

### 3.5.4 Low-power modes

The STM32F051xx microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, the PVD output, RTC, I2C1, USART1,, COMPx or the CEC.

The CEC, USART1 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data. If this is used when the voltage regulator is put in low power mode, the regulator is first switched to normal mode before the clock is provided to the given peripheral.

### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

## 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

## 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Table 4. Internal voltage reference calib | oration values |

|-------------------------------------------|----------------|

|-------------------------------------------|----------------|

| Calibration value name | Description                                                                              | Memory address            |

|------------------------|------------------------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s) and Fast mode (up to 400 kbit/s) and, I2C1 also supports Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |

| Table 8. Com | parison of I <sup>2</sup> C an | alog and digital filters |

|--------------|--------------------------------|--------------------------|

|              |                                | alog and algital mitolo  |

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripherals can be served by the DMA controller.

Refer to Table 9 for the differences between I2C1 and I2C2.

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 | I2C2 |

|--------------------------------------------------------------|------|------|

| 7-bit addressing mode                                        | Х    | Х    |

| 10-bit addressing mode                                       | X    | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                 | X    | Х    |

| Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive I/Os | X    | -    |

| Independent clock                                            | Х    | -    |

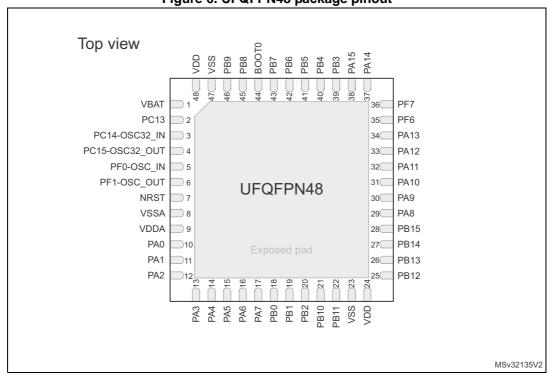

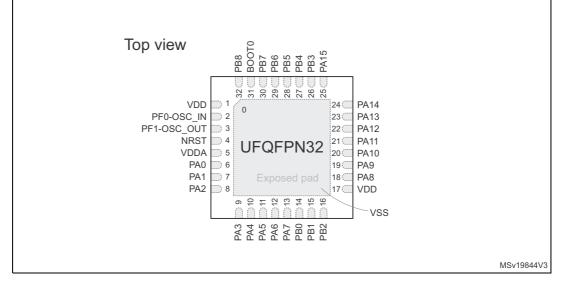

Figure 6. UFQFPN48 package pinout

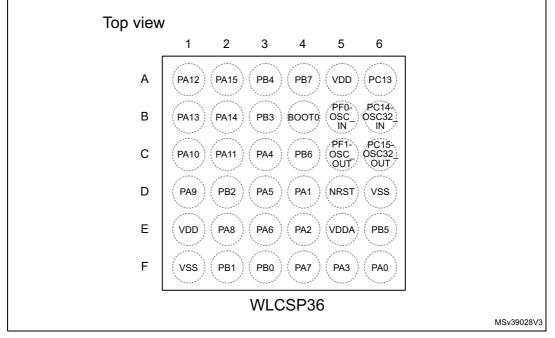

Figure 7. WLCSP36 package pinout

1. The above figure shows the package in top view, changing from bottom view in the previous document versions.

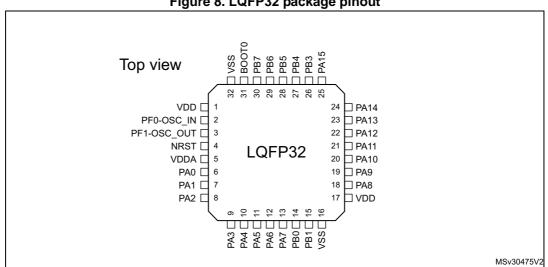

Figure 8. LQFP32 package pinout

|        | P       | in ni           | umbe    | er     |          |                                      |          |               |       | Pin functions                                                     |                         |  |  |

|--------|---------|-----------------|---------|--------|----------|--------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|-------------------------|--|--|

| LQFP64 | UFBGA64 | LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                               | Additional<br>functions |  |  |

| 45     | B8      | 33              | A1      | 22     | 22       | PA12                                 | I/O      | FT            | -     | USART1_RTS,<br>TIM1_ETR,<br>COMP2_OUT,<br>TSC_G4_IO4,<br>EVENTOUT | -                       |  |  |

| 46     | A8      | 34              | B1      | 23     | 23       | PA13<br>(SWDIO)                      | I/O      | FT            | (6)   | IR_OUT,<br>SWDIO                                                  | -                       |  |  |

| 47     | D6      | 35              | -       | -      | -        | PF6                                  | I/O      | FT            | -     | I2C2_SCL                                                          | -                       |  |  |

| 48     | E6      | 36              | -       | -      | -        | PF7                                  | I/O      | FT            | -     | I2C2_SDA                                                          | -                       |  |  |

| 49     | A7      | 37              | B2      | 24     | 24       | PA14<br>(SWCLK)                      | I/O      | FT            | (6)   | USART2_TX,<br>SWCLK                                               | -                       |  |  |

| 50     | A6      | 38              | A2      | 25     | 25       | PA15                                 | I/O      | FT            | -     | SPI1_NSS,<br>I2S1_WS,<br>USART2_RX,<br>TIM2_CH1_ETR,<br>EVENTOUT  | -                       |  |  |

| 51     | B7      | -               | -       | -      | -        | PC10                                 | I/O      | FT            | -     |                                                                   | -                       |  |  |

| 52     | B6      | -               | -       | -      | -        | PC11                                 | I/O      | FT            | -     |                                                                   | -                       |  |  |

| 53     | C5      | -               | -       | -      | -        | PC12                                 | I/O      | FT            | -     |                                                                   | -                       |  |  |

| 54     | B5      | -               | -       | -      | -        | PD2                                  | I/O      | FT            | -     | TIM3_ETR                                                          | -                       |  |  |

| 55     | A5      | 39              | В3      | 26     | 26       | PB3                                  | I/O      | FT            | -     | SPI1_SCK,<br>I2S1_CK,<br>TIM2_CH2,<br>TSC_G5_IO1,<br>EVENTOUT     | -                       |  |  |

| 56     | A4      | 40              | A3      | 27     | 27       | PB4                                  | I/O      | FT            | -     | SPI1_MISO,<br>I2S1_MCK,<br>TIM3_CH1,<br>TSC_G5_IO2,<br>EVENTOUT   | -                       |  |  |

| 57     | C4      | 41              | E6      | 28     | 28       | PB5                                  | I/O      | FT            | -     | SPI1_MOSI,<br>I2S1_SD,<br>I2C1_SMBA,<br>TIM16_BKIN,<br>TIM3_CH2   | -                       |  |  |

Table 13. Pin definitions (continued)

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

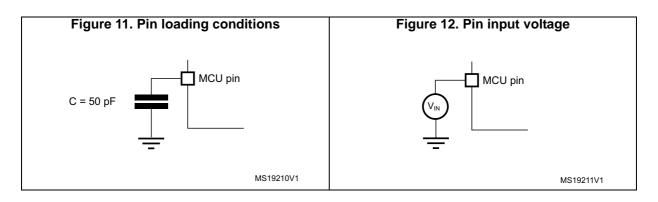

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 12*.

DocID022265 Rev 7

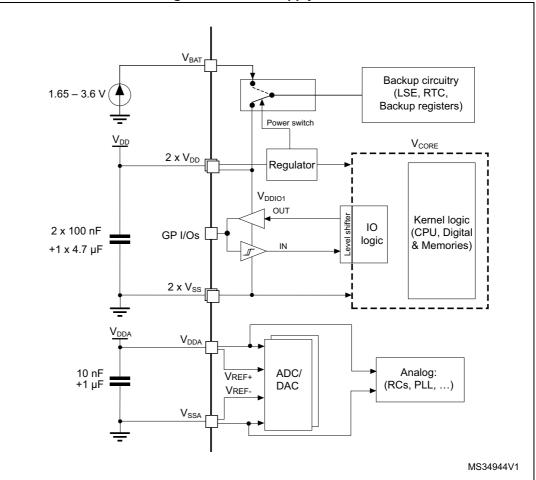

## 6.1.6 Power supply scheme

Figure 13. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 17: Voltage characteristics*, *Table 18: Current characteristics* and *Table 19: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                               | Min                               | Мах                                     | Unit |

|------------------------------------|-------------------------------------------------------|-----------------------------------|-----------------------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>   | External main supply voltage                          | - 0.3                             | 4.0                                     | V    |

| V <sub>DDA</sub> -V <sub>SS</sub>  | External analog supply voltage                        | - 0.3                             | 4.0                                     | V    |

| V <sub>DD</sub> -V <sub>DDA</sub>  | Allowed voltage difference for $V_{DD} > V_{DDA}$     | -                                 | 0.4                                     | V    |

| V <sub>BAT</sub> –V <sub>SS</sub>  | External backup supply voltage                        | - 0.3                             | 4.0                                     | V    |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on FT and FTf pins                      | V <sub>SS</sub> - 0.3             | V <sub>DDIOx</sub> + 4.0 <sup>(3)</sup> | V    |

|                                    | Input voltage on TTa pins                             | V <sub>SS</sub> - 0.3             | 4.0                                     | V    |

|                                    | BOOT0                                                 | 0                                 | 9.0                                     | V    |

|                                    | Input voltage on any other pin                        | V <sub>SS</sub> - 0.3             | 4.0                                     | V    |

| ΔV <sub>DDx</sub>                  | Variations between different $V_{DD}$ power pins      | -                                 | 50                                      | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins      | -                                 | 50                                      | mV   |

| V <sub>ESD(HBM)</sub>              | Electrostatic discharge voltage<br>(human body model) | see Section 6.3 sensitivity chara |                                         | -    |

| Table 17. Voltage characteristics <sup>(1)</sup> | ) |

|--------------------------------------------------|---|

|--------------------------------------------------|---|

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 18: Current characteristics* for the maximum allowed injected current values.

3. Valid only if the internal pull-up/pull-down resistors are disabled. If internal pull-up or pull-down resistor is enabled, the maximum limit is 4 V.

| Symbol                               | Ratings                                                                         | Max.                 | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|----------------------|------|

| ΣI <sub>VDD</sub>                    | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                                      | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                                | -25                  |      |

| ΣI                                   | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                                      | Injected current on B, FT and FTf pins                                          | -5/+0 <sup>(4)</sup> |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                              | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  | 1    |

| ΣI <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 |      |

### Table 18. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. A positive injection is induced by  $V_{IN} > V_{DDIOx}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 17: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

On these I/Os, a positive injection is induced by V<sub>IN</sub> > V<sub>DDA</sub>. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 54: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

### Table 19. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

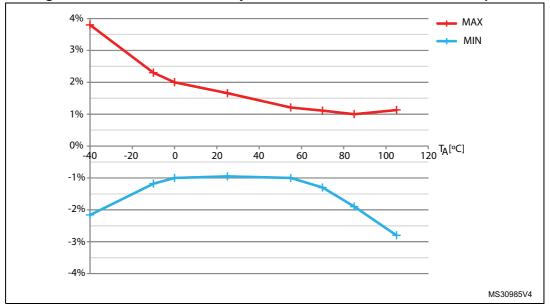

## High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                         | Conditions                    | Min                 | Тур | Мах                | Unit |  |

|-----------------------|-----------------------------------|-------------------------------|---------------------|-----|--------------------|------|--|

| f <sub>HSI</sub>      | Frequency                         | -                             | -                   | 8   | -                  | MHz  |  |

| TRIM                  | HSI user trimming step            | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |  |

| DuCy <sub>(HSI)</sub> | Duty cycle                        | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |  |

|                       |                                   | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> | %    |  |

| ACC <sub>HSI</sub>    | Accuracy of the HSI<br>oscillator | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> |      |  |

|                       |                                   | T <sub>A</sub> = 0 to 85°C    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |  |

|                       |                                   | $T_A = 0$ to 70°C             | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |  |

|                       |                                   | $T_A = 0$ to 55°C             | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |  |

|                       |                                   | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |  |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time       | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |  |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption  | -                             | -                   | 80  | 100 <sup>(2)</sup> | μΑ   |  |

### Table 37. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105°C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

4. Factory calibrated, parts not soldered.

### Figure 19. HSI oscillator accuracy characterization results for soldered parts

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |

Table 42. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 43*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                       | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> |                                                                                                                                   | $V_{DD}$ = 3.3 V, LQFP64, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP64, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-4  | 4B              |

### Table 43. EMS characteristics

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

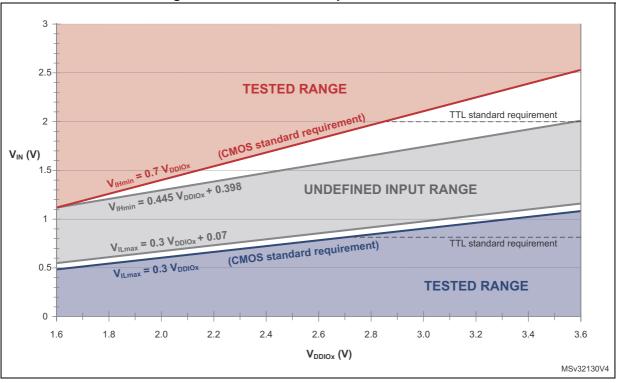

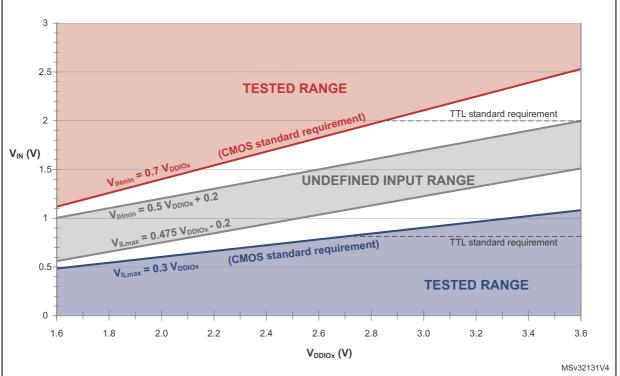

Figure 21. TC and TTa I/O input characteristics

Figure 22. Five volt tolerant (FT and FTf) I/O input characteristics

DocID022265 Rev 7

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур | Max  | Unit | Comments                                                                                                                |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------------|

| Gain error <sup>(3)</sup>            | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                               |

| t <sub>SETTLING</sub> <sup>(3)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | -   | 3   | 4    | μs   | C <sub>LOAD</sub> ≤ 50 pF, R <sub>LOAD</sub> ≥ 5 kΩ                                                                     |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | C <sub>LOAD</sub> ≤ 50 pF, R <sub>LOAD</sub> ≥ 5 kΩ                                                                     |

| t <sub>WAKEUP</sub> <sup>(3)</sup>   | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                   | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |

Table 55. DAC characteristics (continued)

1. Guaranteed by design, not tested in production.

2. The DAC is in "quiescent mode" when it keeps the value steady on the output so no dynamic consumption is involved.

3. Data based on characterization results, not tested in production.

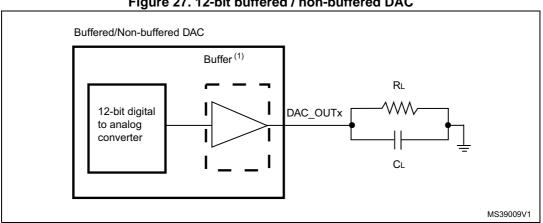

### Figure 27. 12-bit buffered / non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register. 1.

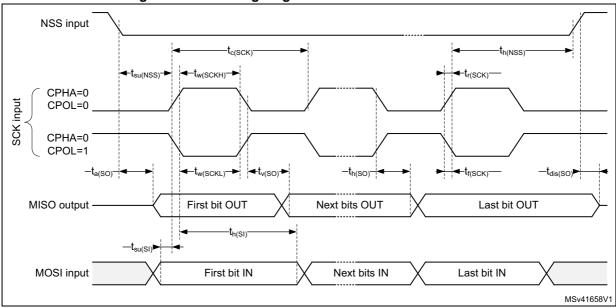

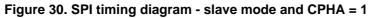

Figure 29. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

# 7.2 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 37. LQFP64 package outline

1. Drawing is not to scale.

| Cumhal |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |  |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |

| с      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D      | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| D1     | -     | 10.000      | -     | -      | 0.3937                | -      |  |

| D3     | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| E      | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| E1     | -     | 10.000      | -     | -      | 0.3937                | -      |  |

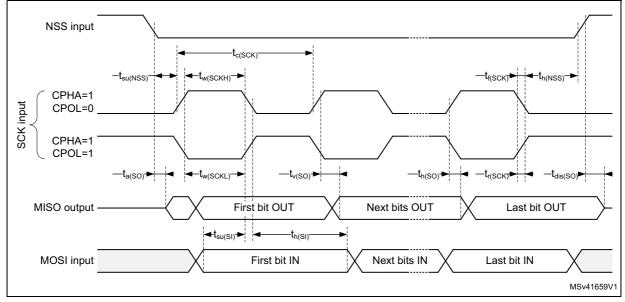

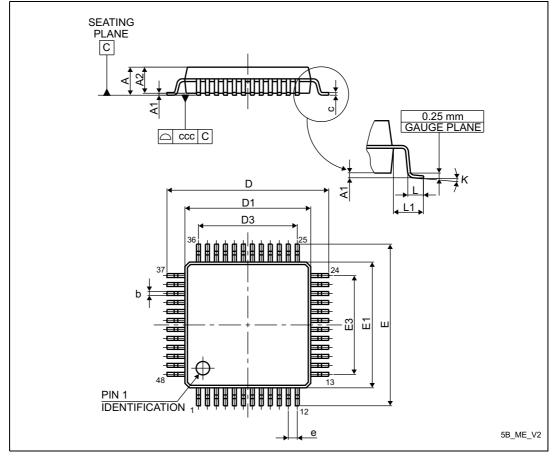

# 7.3 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

1. Drawing is not to scale.

## 7.8 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 20: General operating conditions*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{I\!/\!O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma \; ((\mathsf{V}_{\mathsf{DDIOx}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                 | Value | Unit |

|-----------------|---------------------------------------------------------------------------|-------|------|

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |

|                 | Thermal resistance junction-ambient<br>LQFP48 - 7 × 7 mm                  | 55    |      |

|                 | Thermal resistance junction-ambient<br>LQFP32 - 7 × 7 mm                  | 56    |      |

| Θ <sub>JA</sub> | <b>Thermal resistance junction-ambient</b><br>UFBGA64 - 5 × 5 mm          | 65    | °C/W |

|                 | Thermal resistance junction-ambient<br>UFQFPN48 - 7 × 7 mm                | 32    |      |

|                 | Thermal resistance junction-ambient<br>UFQFPN32 - 5 × 5 mm                | 38    |      |

|                 | Thermal resistance junction-ambient<br>WLCSP36 - 2.6 × 2.7 mm             | 60    |      |

Table 74. Package thermal characteristics

## 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

## 7.8.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 28-Aug-2015 | 5        | <ul> <li>Updated the following:</li> <li>DAC and power management feature descriptions in <i>Features</i></li> <li>Table 2: STM32F051xx family device features and peripheral count</li> <li>Section 3.5.1: Power supply schemes</li> <li>Figure 13: Power supply scheme</li> <li>Table 17: Voltage characteristics</li> <li>Table 20: General operating conditions: updated the footnote for V<sub>IN</sub> parameter</li> <li>Table 28: Typical and maximum current consumption from the V<sub>BAT</sub> supply</li> <li>Table 52: ADC characteristics</li> <li>Table 33: High-speed external user clock characteristics: replaced V<sub>DD</sub> with V<sub>DDIOX</sub></li> <li>Table 34: Low-speed external user clock characteristics: replaced V<sub>DD</sub> with V<sub>DDIOX</sub></li> <li>Table 37: HSI oscillator characteristics and Figure 19: HSI oscillator characteristics: changed the min value for ACC<sub>HSI14</sub></li> <li>Table 41: Flash memory characteristics: changed the values for t<sub>ME</sub> and I<sub>DD</sub> in write mode</li> <li>Table 43: EMS characteristics changed the value of V<sub>EFTB</sub></li> <li>Table 43: EMS characteristics changed the value of V<sub>EFTB</sub></li> <li>Figure 10: STM32F051x8 memory map</li> <li>Figure 21: TC and TTa I/O input characteristics</li> <li>Figure 22: Five volt tolerant (FT and FTf) I/O input characteristics</li> <li>Figure 23: I/O AC characteristics: changed the description and values for V<sub>SC</sub>, V<sub>DDA</sub> and V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Section 6.3:2: Communication interfaces: updated the min value for T<sub>S</sub>-v<sub>bat</sub> and the typical value for R parameters</li> <li>Section and features in the subsection I<sup>2</sup>C interface characteristics:</li> <li>Table 57: TS characteristics: updated the min value for Ts - temp</li> <li>Table 58: V<sub>BAT</sub> monitoring characteristics: changed the min value for Ts-v<sub>bat</sub> and the typical value for R parameters</li> <li>Section 6.3:2: Communication interfaces: updated the description and features in the subsection I<sup>2</sup>C interface cha</li></ul> |

Table 76. Document revision history (continued)