Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051c6u6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 49. | LQFP32 package outline                          | 106 |

|------------|-------------------------------------------------|-----|

| Figure 50. | Recommended footprint for LQFP32 package        | 107 |

| Figure 51. | LQFP32 package marking example                  | 108 |

| Figure 52. | UFQFPN32 package outline                        | 109 |

| Figure 53. | Recommended footprint for UFQFPN32 package      | 110 |

| Figure 54. | UFQFPN32 package marking example                | 111 |

| Figure 55. | LQFP64 P <sub>D</sub> max versus T <sub>A</sub> | 114 |

8/122

## **3** Functional overview

Figure 1 shows the general block diagram of the STM32F051xx devices.

## 3.1 ARM<sup>®</sup>-Cortex<sup>®</sup>-M0 core

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 is a generation of ARM 32-bit RISC processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processors feature exceptional code-efficiency, delivering the high performance expected from an ARM core, with memory sizes usually associated with 8- and 16-bit devices.

The STM32F051xx devices embed ARM core and are compatible with all ARM tools and software.

## 3.2 Memories

The device has the following features:

- 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail-critical applications.

- The non-volatile memory is divided into two arrays:

- 16 to 64 Kbytes of embedded Flash memory for programs and data

- Option bytes

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M0 serial wire) and boot in RAM selection disabled

## 3.3 Boot modes

At startup, the boot pin and boot selector option bit are used to select one of the three boot options:

- boot from User Flash memory

- boot from System Memory

- boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART on pins PA14/PA15 or PA9/PA10.

### **Functional overview**

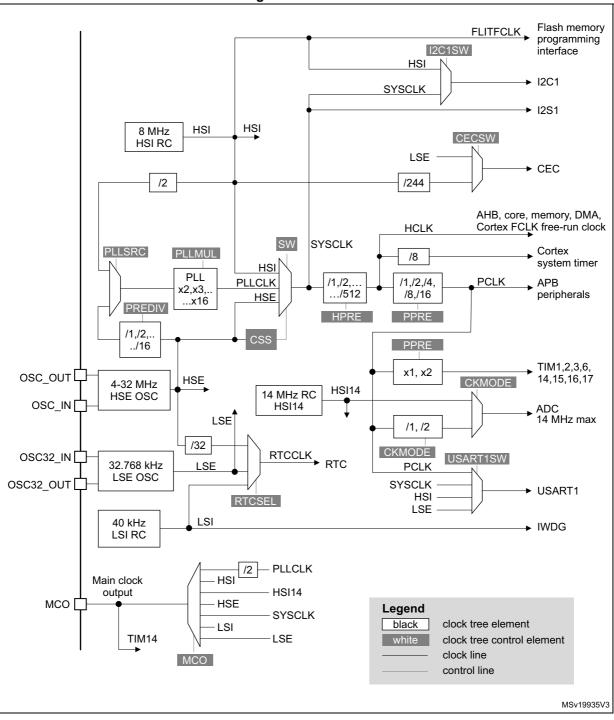

### Figure 2. Clock tree

## 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

## **3.8** Direct memory access controller (DMA)

The 5-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

### 3.9 Interrupts and events

### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 55 GPIOs can be connected to the 16 external interrupt lines.

## 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature

### 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

## 3.11 Digital-to-analog converter (DAC)

The 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This digital Interface supports the following features:

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- DMA capability

- External triggers for conversion

Five DAC trigger inputs are used in the device. The DAC is triggered through the timer trigger outputs and the DAC interface is generating its own DMA requests.

## 3.12 Comparators (COMP)

The device embeds two fast rail-to-rail low-power comparators with programmable reference voltage (internal or external), hysteresis and speed (low speed for low power) and with selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output pins

- Internal reference voltage or submultiple (1/4, 1/2, 3/4).Refer to *Table 24: Embedded internal reference voltage* for the value and precision of the internal reference voltage.

Both comparators can wake up from STOP mode, generate interrupts and breaks for the timers and can be also combined into a window comparator.

## **3.13** Touch sensing controller (TSC)

The STM32F051xx devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 18 capacitive sensing channels distributed over 6 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists in charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the

### 3.14.2 General-purpose timers (TIM2, 3, 14, 15, 16, 17)

There are six synchronizable general-purpose timers embedded in the STM32F051xx devices (see *Table 7* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

### TIM2, TIM3

STM32F051xx devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advancedcontrol timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

### **TIM14**

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

### TIM15, TIM16 and TIM17

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

### 3.14.3 Basic timer TIM6

This timer is mainly used for DAC trigger generation. It can also be used as a generic 16-bit time base.

### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It

# 3.18 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Up to two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in fullduplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

One standard I<sup>2</sup>S interface (multiplexed with SPI1) supporting four different audio standards can operate as master or slave at half-duplex communication mode. It can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, it can output a clock for an external audio component at 256 times the sampling frequency.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    |

| NSS pulse mode              | Х    | Х    |

| I <sup>2</sup> S mode       | Х    | -    |

| TI mode                     | Х    | Х    |

1. X = supported.

# 3.19 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

## 3.20 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

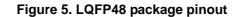

### Pinouts and pin descriptions

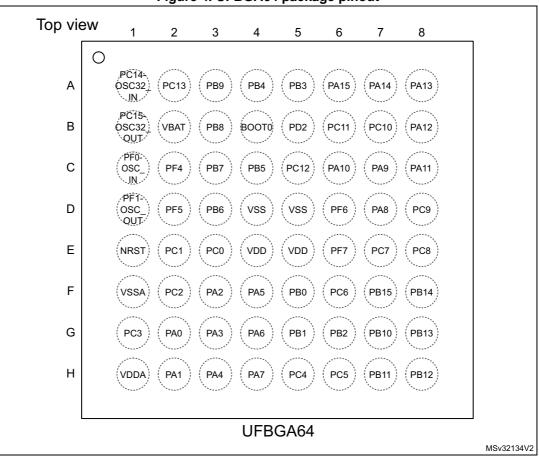

Figure 4. UFBGA64 package pinout

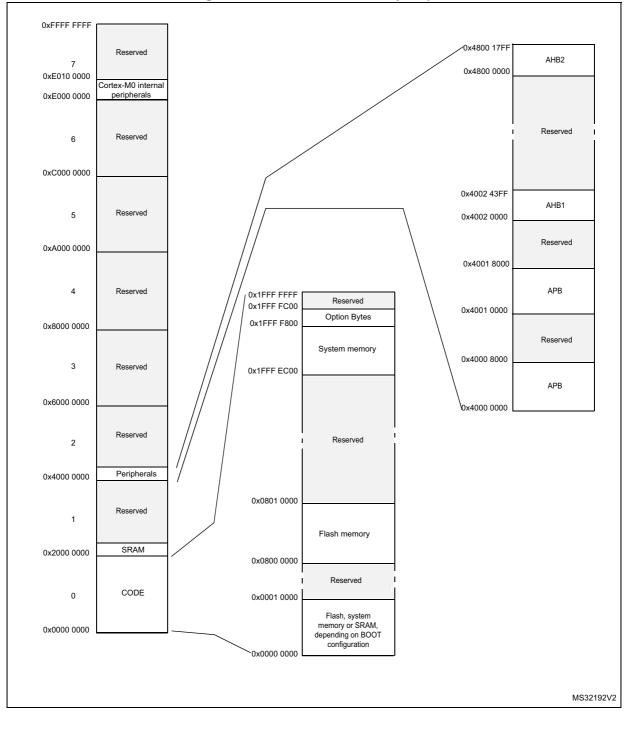

## 5 Memory mapping

To the difference of STM32F051x8 memory map in *Figure 10*, the two bottom code memory spaces of STM32F051x4/STM32F051x6 end at 0x0000 3FFF/0x0000 7FFF and 0x0800 3FFF/0x0000 7FFF, respectively.

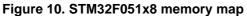

## 6.1.7 Current consumption measurement

### Figure 14. Current consumption measurement scheme

### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (for example control registers)

### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter                                                                                     | Conditions                                                                                        | Monitored        | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------|------------------------------------------------|------|

| Symbol Talameter | Conditions                                                                                    | frequency band                                                                                    | 8/48 MHz         | C.int                                          |      |

|                  | $S_{EMI}$ Peak level $V_{DD} = 3.6 V, T_A = 25 °C, LQFP64 package compliant with IEC 61967-2$ | evel $V_{DD} = 3.6 \text{ V}, \text{ T}_{A} = 25 \text{ °C},$<br>LQFP64 package<br>compliant with | 0.1 to 30 MHz    | -3                                             |      |

| 6                |                                                                                               |                                                                                                   | 30 to 130 MHz    | 28                                             | dBµV |

| SEMI             |                                                                                               |                                                                                                   | 130 MHz to 1 GHz | 23                                             |      |

|                  |                                                                                               | EMI Level                                                                                         | 4                | -                                              |      |

### Table 44. EMI characteristics

### 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### **Electrostatic discharge (ESD)**

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol           | Description                                                                                                                             |    | Functional susceptibility |      |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------|------|--|

|                  |                                                                                                                                         |    | Positive injection        | Unit |  |

|                  | Injected current on BOOT0                                                                                                               |    | NA                        |      |  |

| I <sub>INJ</sub> | Injected current on PA10, PA12, PB4, PB5, PB10, PB15 and PD2 pins with induced leakage current on adjacent pins less than $-10 \ \mu A$ | -5 | NA                        | mA   |  |

| ·IINJ            | Injected current on all other FT and FTf pins                                                                                           | -5 | NA                        |      |  |

|                  | Injected current on PA6 and PC0                                                                                                         | -0 | +5                        |      |  |

|                  | Injected current on all other TTa, TC and RST pins                                                                                      | -5 | +5                        |      |  |

| Table 47. I/ | O current | injection | susceptibility |

|--------------|-----------|-----------|----------------|

|--------------|-----------|-----------|----------------|

### 6.3.14 I/O port characteristics

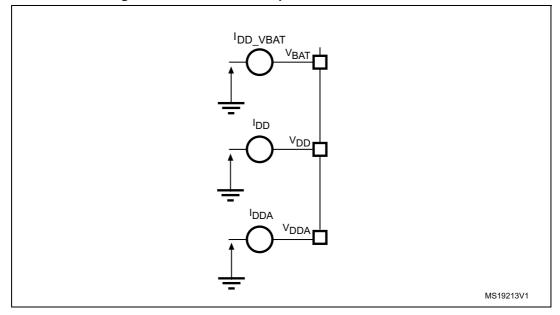

### General input/output characteristics

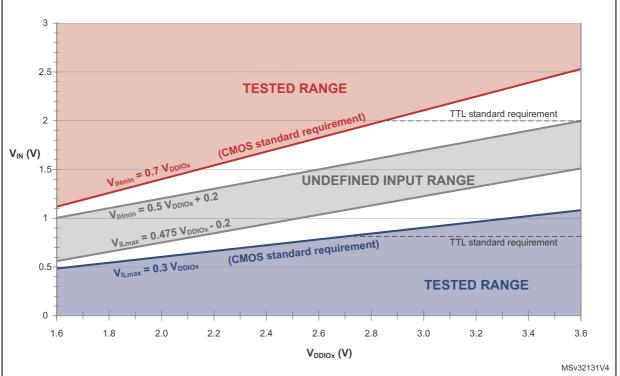

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the conditions summarized in *Table 20: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol           | Parameter                     | Conditions                   | Min                                            | Тур                    | Max                                          | Unit |

|------------------|-------------------------------|------------------------------|------------------------------------------------|------------------------|----------------------------------------------|------|

|                  |                               | TC and TTa I/O               | -                                              | -                      | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup>  |      |

|                  | Low level input               | FT and FTf I/O               | -                                              | -                      | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |      |

| V <sub>IL</sub>  | voltage                       | BOOT0                        | -                                              | -                      | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   | V    |

|                  | All I/Os except<br>BOOT0 pin  | -                            | -                                              | 0.3 V <sub>DDIOx</sub> |                                              |      |

|                  |                               | TC and TTa I/O               | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                      | -                                            |      |

|                  | High level input              | FT and FTf I/O               | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                      | -                                            |      |

| V <sub>IH</sub>  | voltage                       | BOOT0                        | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                      | -                                            | V    |

|                  |                               | All I/Os except<br>BOOT0 pin | 0.7 V <sub>DDIOx</sub>                         | -                      | -                                            |      |

|                  |                               | TC and TTa I/O               | -                                              | 200 <sup>(1)</sup>     | -                                            |      |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis | FT and FTf I/O               | -                                              | 100 <sup>(1)</sup>     | -                                            | mV   |

|                  | ,                             | BOOT0                        | -                                              | 300 <sup>(1)</sup>     | -                                            |      |

### Table 48. I/O static characteristics

Figure 21. TC and TTa I/O input characteristics

Figure 22. Five volt tolerant (FT and FTf) I/O input characteristics

| Symbol |       | millimeters |       |        |        |        |

|--------|-------|-------------|-------|--------|--------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур    | Max    |

| E3     | -     | 7.500       | -     | -      | 0.2953 | -      |

| е      | -     | 0.500       | -     | -      | 0.0197 | -      |

| К      | 0°    | 3.5°        | 7°    | 0°     | 3.5°   | 7°     |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394 | -      |

| CCC    | -     | -           | 0.080 | -      | -      | 0.0031 |

Table 67. LQFP64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 38. Recommended footprint for LQFP64 package

1. Dimensions are expressed in millimeters.

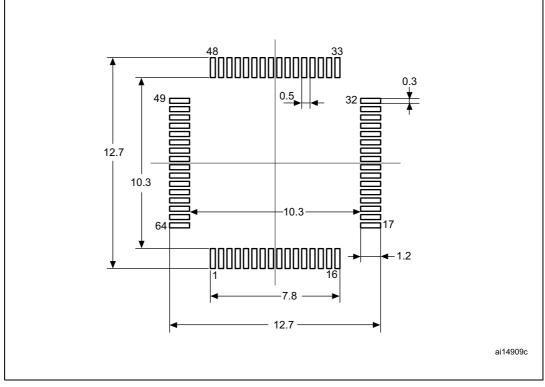

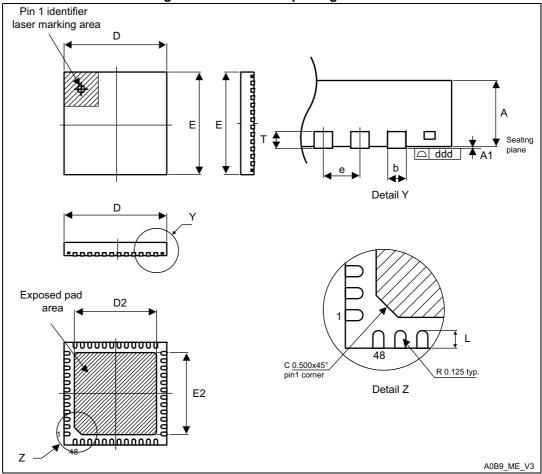

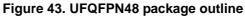

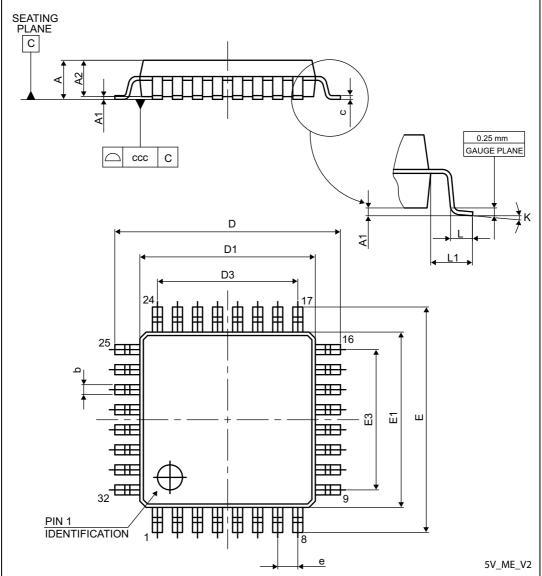

## 7.4 UFQFPN48 package information

UFQFPN48 is a 48-lead, 7x7 mm, 0.5 mm pitch, ultra-thin fine-pitch quad flat package.

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

## 7.6 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

Figure 49. LQFP32 package outline

1. Drawing is not to scale.

## 7.8 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 20: General operating conditions*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{I\!/\!O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma \; ((\mathsf{V}_{\mathsf{DDIOx}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                 | Value | Unit |

|-----------------|---------------------------------------------------------------------------|-------|------|

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |

|                 | Thermal resistance junction-ambient<br>LQFP48 - 7 × 7 mm                  | 55    |      |

|                 | Thermal resistance junction-ambient<br>LQFP32 - 7 × 7 mm                  | 56    |      |

| Θ <sub>JA</sub> | <b>Thermal resistance junction-ambient</b><br>UFBGA64 - 5 × 5 mm          | 65    | °C/W |

|                 | Thermal resistance junction-ambient<br>UFQFPN48 - 7 × 7 mm                | 32    |      |

|                 | Thermal resistance junction-ambient<br>UFQFPN32 - 5 × 5 mm                | 38    |      |

|                 | Thermal resistance junction-ambient<br>WLCSP36 - 2.6 × 2.7 mm             | 60    |      |

Table 74. Package thermal characteristics

### 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

### 7.8.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

## 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Apr-2012 | 1        | Initial release                                                                                                                                                                                                                                                                          |

|             |          | Updated <i>Table: STM32F051xx family device features and peripheral counts</i> for SPI and I <sup>2</sup> C in 32-pin package.                                                                                                                                                           |

| 25-Apr-2012 | 2        | Corrected Group 3 pin order in <i>Table: Capacitive sensing GPIOs available on STM32F051xx devices.</i>                                                                                                                                                                                  |

|             |          | Updated the current consumption values in Section: Electrical characteristics.                                                                                                                                                                                                           |

|             |          | Updated Table: HSI14 oscillator characteristics                                                                                                                                                                                                                                          |

|             |          | Features reorganized and <i>Figure: Block diagram</i> structure changed.                                                                                                                                                                                                                 |

|             |          | Added LQFP32 package.                                                                                                                                                                                                                                                                    |

|             |          | Updated Section: Cyclic redundancy check calculation unit (CRC).                                                                                                                                                                                                                         |

|             | 3        | Modified the number of priority levels in Section: Nested vectored interrupt controller (NVIC).                                                                                                                                                                                          |

|             |          | Added note 3. for PB2 and PB8, changed TIM2_CH_ETR into TIM2_CH1_ETR in <i>Table: Pin definitions</i> and <i>Table: Alternate functions selected through GPIOA_AFR registers for port A.</i><br>Added <i>Table: Alternate functions selected through GPIOB_AFR registers for port B.</i> |

| 23-Jul-2012 |          | Updated I <sub>VDD</sub> , I <sub>VSS</sub> , and I <sub>INJ(PIN)</sub> in <i>Table: Current characteristics.</i>                                                                                                                                                                        |

|             |          | Updated ACC <sub>HSI</sub> in <i>Table: HSI oscillator characteristics</i> and <i>Table: HSI14 oscillator characteristics</i> .                                                                                                                                                          |

|             |          | Updated Table: I/O current injection susceptibility.                                                                                                                                                                                                                                     |

|             |          | Added BOOT0 input low and high level voltage in <i>Table: I/O</i> static characteristics.                                                                                                                                                                                                |

|             |          | Modified number of pins in V <sub>OL</sub> and V <sub>OH</sub> description, and changed condition for V <sub>OLFM+</sub> in <i>Table: Output voltage characteristics.</i>                                                                                                                |

|             |          | Changed $V_{DD}$ to $V_{DDA}$ in Figure: Typical connection diagram using the ADC.                                                                                                                                                                                                       |

|             |          | Updated Ts_temp in Table: TS characteristics.                                                                                                                                                                                                                                            |

|             |          | Updated Figure: I/O AC characteristics definition.                                                                                                                                                                                                                                       |

### Table 76. Document revision history

| Data        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 28-Aug-2015 | 5<br>(continued) | <ul> <li>Table 31: Peripheral current consumption</li> <li>Addition of WLCSP36 package. Updates in:</li> <li>Section 2: Description</li> <li>Table 2: STM32F051xx family device features and peripheral count</li> <li>Section 4: Pinouts and pin descriptions with the addition of Figure 7: WLCSP36 package pinout</li> <li>Table 13: Pin definitions</li> <li>Table 20: General operating conditions</li> <li>Section 7: Package information with the addition of Section 7.5: WLCSP36 package information</li> <li>Table 74: Package thermal characteristics</li> <li>Section 8: Part numbering</li> <li>Update of the device marking examples in Section 7: Package information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16-Dec-2015 | 6                | <ul> <li>Section 2: Description:</li> <li>Table 2: STM32F051xx family device features and peripheral count - number of SPIs corrected for 64-pin packages</li> <li>Figure 1: Block diagram modified</li> <li>Section 3: Functional overview:</li> <li>Figure 2: Clock tree modified; divider for CEC corrected</li> <li>Table 8: Comparison of I<sup>2</sup>C analog and digital filters - adding 20 mA information for FastPlus mode</li> <li>Section 4: Pinouts and pin descriptions:</li> <li>Package pinout figures updated (look and feel)</li> <li>Figure 7: WLCSP36 package pinout - now presented in top view</li> <li>Table 13: Pin definitions - notes added (VSSA corrected to pin 16 on LQFP32); note 5 added</li> <li>Section 5: Memory mapping:</li> <li>added information on STM32F051x4/x6 difference versus STM32F051x8 map in Figure 10</li> <li>Section 6: Electrical characteristics:</li> <li>Table 24: Embedded internal reference voltage - removed - 40°C-85°C temperature range line and the associated note</li> <li>Table 48: I/O static characteristics - removed note</li> <li>Section 6.3.16: 12-bit ADC characteristics - changed introductory sentence</li> <li>Table 52: ADC characteristics updated and table footnotes 3 and 4 added</li> <li>Table 59: TIMx characteristics modified</li> <li>Table 64: I<sup>2</sup>S characteristics reorganized</li> <li>Figure 52: UFQFPN32 package outline - figure footnotes added</li> </ul> |

Table 76. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-Jan-2017 | 7        | <ul> <li>Section 6: Electrical characteristics:</li> <li>Table 36: LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) - information on configuring different drive capabilities removed. See the corresponding reference manual.</li> <li>Table 24: Embedded internal reference voltage - V<sub>REFINT</sub> values</li> <li>Table 55: DAC characteristics - min. R<sub>LOAD</sub> to V<sub>DDA</sub> defined</li> <li>Figure 29: SPI timing diagram - slave mode and CPHA = 0 and Figure 30: SPI timing diagram - slave mode and CPHA = 1 enhanced and corrected</li> <li>Section 8: Ordering information:</li> <li>The name of the section changed from the previous "Part numbering"</li> </ul> |

Table 76. Document revision history (continued)