Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 39                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 13x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051c8t7tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F051xx microcontrollers.

This document should be read in conjunction with the STM32F0xxxx reference manual (RM0091). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

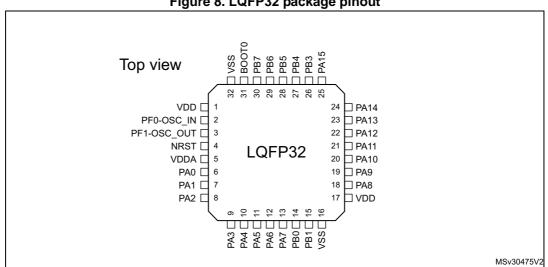

Figure 8. LQFP32 package pinout

| Na                                                                                           | me                     | Abbreviation                                                                                                                      | Definition                                                  |  |  |

|----------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Pin r                                                                                        | name                   | Unless otherwise specified in brackets below the pin name, the pin function during after reset is the same as the actual pin name |                                                             |  |  |

|                                                                                              |                        | S                                                                                                                                 | Supply pin                                                  |  |  |

| Pin                                                                                          | type                   | I                                                                                                                                 | Input-only pin                                              |  |  |

|                                                                                              |                        | I/O                                                                                                                               | Input / output pin                                          |  |  |

|                                                                                              |                        | FT                                                                                                                                | 5 V-tolerant I/O                                            |  |  |

|                                                                                              |                        | FTf 5 V-tolerant I/O, FM+ capable                                                                                                 |                                                             |  |  |

| I/O otr                                                                                      | ucture                 | TTa 3.3 V-tolerant I/O directly connected to ADC                                                                                  |                                                             |  |  |

| 1/O Sti                                                                                      | ucture                 | TC                                                                                                                                | Standard 3.3 V I/O                                          |  |  |

|                                                                                              |                        | В                                                                                                                                 | Dedicated BOOT0 pin                                         |  |  |

|                                                                                              |                        | RST                                                                                                                               | Bidirectional reset pin with embedded weak pull-up resistor |  |  |

| Notes Unless otherwise specified by a note, all I/Os are set as floating inputs durin reset. |                        | specified by a note, all I/Os are set as floating inputs during and after                                                         |                                                             |  |  |

| Pin                                                                                          | Alternate<br>functions | Functions selected through GPIOx_AFR registers                                                                                    |                                                             |  |  |

| functions                                                                                    | Additional functions   | Functions directly                                                                                                                | selected/enabled through peripheral registers               |  |  |

#### Table 13. Pin definitions

|        | Ρ       | in nu           | umbe    | er     |          |                                      |          |               |        | Pin fur             | nctions                                    |

|--------|---------|-----------------|---------|--------|----------|--------------------------------------|----------|---------------|--------|---------------------|--------------------------------------------|

| LQFP64 | UFBGA64 | LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes  | Alternate functions | Additional<br>functions                    |

| 1      | B2      | 1               | -       | -      | -        | VBAT                                 | S        | -             | -      | Backup power supply |                                            |

| 2      | A2      | 2               | A6      | -      | -        | PC13                                 | I/O      | тс            | (1)(2) | -                   | RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT,<br>WKUP2 |

| 3      | A1      | 3               | B6      | -      | -        | PC14-OSC32_IN<br>(PC14)              | I/O      | тс            | (1)(2) | -                   | OSC32_IN                                   |

| 4      | B1      | 4               | C6      | -      | -        | PC15-OSC32_OUT<br>(PC15)             | I/O      | тс            | (1)(2) | -                   | OSC32_OUT                                  |

| 5      | C1      | 5               | B5      | 2      | 2        | PF0-OSC_IN<br>(PF0)                  | I/O      | FT            | -      | -                   | OSC_IN                                     |

| 6      | D1      | 6               | C5      | 3      | 3        | PF1-OSC_OUT<br>(PF1)                 | I/O      | FT            | -      | -                   | OSC_OUT                                    |

| <u> 1157</u> |

|--------------|

|--------------|

#### Table 14. Alternate functions selected through GPIOA\_AFR registers for port A AF0 AF1 AF2 AF3 Pin name AF4 AF5 AF7 AF6 USART2 CTS TIM2 CH1 ETR TSC G1 IO1 COMP1 OUT PA0 --EVENTOUT USART2\_RTS TIM2\_CH2 TSC\_G1\_IO2 PA1 \_ TIM15\_CH1 USART2\_TX TIM2\_CH3 TSC\_G1\_IO3 COMP2\_OUT PA2 ---PA3 TIM15 CH2 USART2 RX TIM2\_CH4 TSC G1 IO4 ----SPI1\_NSS, I2S1\_WS USART2\_CK TSC\_G2\_IO1 TIM14\_CH1 PA4 \_ --\_ SPI1\_SCK, I2S1\_CK CEC TIM2\_CH1\_ETR TSC\_G2\_IO2 PA5 \_ -\_ TSC G2 103 EVENTOUT COMP1 OUT PA6 SPI1 MISO, I2S1 MCK TIM3 CH1 TIM1 BKIN TIM16 CH1 SPI1\_MOSI, I2S1\_SD TIM3\_CH2 TIM1\_CH1N TSC\_G2\_IO4 TIM14\_CH1 TIM17\_CH1 EVENTOUT COMP2\_OUT PA7 PA8 МСО USART1 CK TIM1\_CH1 **EVENTOUT** \_ \_ USART1 TX TIM15 BKIN TIM1 CH2 TSC G4 IO1 PA9 ----TIM17\_BKIN USART1 RX TIM1 CH3 TSC\_G4\_IO2 PA10 ----EVENTOUT COMP1 OUT PA11 USART1\_CTS TIM1 CH4 TSC\_G4\_IO3 ---EVENTOUT USART1\_RTS TIM1 ETR TSC\_G4\_IO4 COMP2 OUT PA12 ---SWDIO IR\_OUT PA13 \_ ---SWCLK USART2\_TX PA14

**EVENTOUT**

TIM2 CH1 ETR

-

-

\_

\_

-

-

-

STM32F051x4 STM32F051x6 STM32F051x8

DocID022265 Rev 7

PA15

SPI1 NSS, I2S1 WS

USART2 RX

37/122

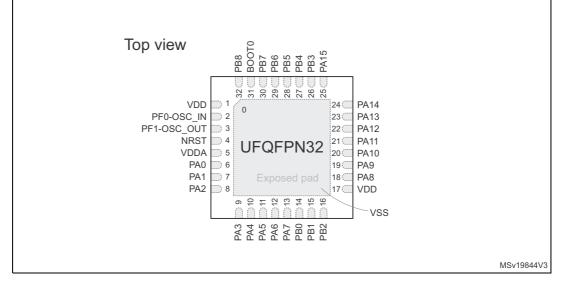

#### 6.1.6 Power supply scheme

Figure 13. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

|                                                            |           |                                                                                  | Тур @ V <sub>BAT</sub> |       |       |       |       | Max <sup>(1)</sup> |                          |                          |                            |      |

|------------------------------------------------------------|-----------|----------------------------------------------------------------------------------|------------------------|-------|-------|-------|-------|--------------------|--------------------------|--------------------------|----------------------------|------|

| Symbol                                                     | Parameter | Conditions                                                                       | 1.65 V                 | 1.8 V | 2.4 V | 2.7 V | 3.3 V | 3.6 V              | T <sub>A</sub> =<br>25 ℃ | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | Unit |

| I <sub>DD_VBAT</sub><br>RTC<br>domain<br>supply<br>current | -         | LSE & RTC ON; "Xtal<br>mode": lower driving<br>capability;<br>LSEDRV[1:0] = '00' | 0.5                    | 0.5   | 0.6   | 0.7   | 0.8   | 0.9                | 1.0                      | 1.3                      | 1.7                        |      |

|                                                            |           | LSE & RTC ON; "Xtal<br>mode" higher driving<br>capability;<br>LSEDRV[1:0] = '11' | 0.8                    | 0.8   | 0.9   | 1.0   | 1.1   | 1.2                | 1.3                      | 1.6                      | 2.1                        | μA   |

Table 28. Typical and maximum current consumption from the  $\rm V_{BAT}$  supply

1. Data based on characterization results, not tested in production.

#### Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 31: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

$\rm f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$  +  $C_{EXT}$  +  $C_S$

$C_S$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

#### **Electrical characteristics**

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                                                            | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit  |

|-----------------|-------------|--------------------------------------------------------------------------------------|----------------------------------------------|-------|-------|

|                 |             |                                                                                      | 4 MHz                                        | 0.07  |       |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                           | 8 MHz                                        | 0.15  |       |

|                 |             | C =C <sub>INT</sub>                                                                  | 16 MHz                                       | 0.31  | l     |

|                 |             |                                                                                      | 24 MHz                                       | 0.53  |       |

|                 |             |                                                                                      | 48 MHz                                       | 0.92  |       |

|                 |             |                                                                                      | 4 MHz                                        | 0.18  |       |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                           | 8 MHz                                        | 0.37  |       |

|                 |             | C <sub>EXT</sub> = 0 pF                                                              | 16 MHz                                       | 0.76  |       |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$                                                        | 24 MHz                                       | 1.39  |       |

|                 |             |                                                                                      | 48 MHz                                       | 2.188 |       |

|                 |             |                                                                                      | 4 MHz                                        | 0.32  |       |

|                 |             | $V_{DDIOx}$ = 3.3 V<br>$C_{EXT}$ = 10 pF<br>$C = C_{INT} + C_{EXT} + C_S$            | 8 MHz                                        | 0.64  |       |

|                 |             |                                                                                      | 16 MHz                                       | 1.25  |       |

|                 |             |                                                                                      | 24 MHz                                       | 2.23  |       |

| I <sub>SW</sub> | I/O current |                                                                                      | 48 MHz                                       | 4.442 | mA    |

| 1210            | consumption |                                                                                      | 4 MHz                                        | 0.49  | 110 ( |

|                 |             | $V_{\text{DDIOx}} = 3.3 \text{ V}$                                                   | 8 MHz                                        | 0.94  | -     |

|                 |             | C <sub>EXT</sub> = 22 pF<br>C = C <sub>INT</sub> + C <sub>EXT</sub> + C <sub>S</sub> | 16 MHz                                       | 2.38  |       |

|                 |             |                                                                                      | 24 MHz                                       | 3.99  |       |

|                 |             |                                                                                      | 4 MHz                                        | 0.64  |       |

|                 |             | V <sub>DDIOx</sub> = 3.3 V<br>C <sub>EXT</sub> = 33 pF                               | 8 MHz                                        | 1.25  |       |

|                 |             | $C_{EXT} = 35 \mu\text{F}$<br>$C = C_{INT} + C_{EXT} + C_{S}$                        | 16 MHz                                       | 3.24  |       |

|                 |             |                                                                                      | 24 MHz                                       | 5.02  |       |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                           | 4 MHz                                        | 0.81  |       |

|                 |             | C <sub>EXT</sub> = 47 pF                                                             | 8 MHz                                        | 1.7   |       |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$ $C = C_{int}$                                          | 16 MHz                                       | 3.67  |       |

|                 |             | V <sub>DDIOx</sub> = 2.4 V                                                           | 4 MHz                                        | 0.66  |       |

|                 |             | $C_{EXT} = 47 \text{ pF}$                                                            | 8 MHz                                        | 1.43  |       |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                                                      | 16 MHz                                       | 2.45  |       |

|                 |             | C = C <sub>int</sub>                                                                 | 24 MHz                                       | 4.97  |       |

| Table 30. | Switching | output I/O | current | consumption |

|-----------|-----------|------------|---------|-------------|

|-----------|-----------|------------|---------|-------------|

1. C<sub>S</sub> = 7 pF (estimated value).

#### 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 32* are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

|                        |                             | -                           |                 |         | -         |       |          |      |      |

|------------------------|-----------------------------|-----------------------------|-----------------|---------|-----------|-------|----------|------|------|

| Symbol                 | Parameter                   | Conditions                  | Typ @Vdd = Vdda |         |           |       |          | Max  | Unit |

|                        | Farameter                   | Conditions                  | = 2.0 V         | = 2.4 V | / = 2.7 V | = 3 V | = 3.3 V  | widx | Unit |

| +                      | Wakeup from Stop            | Regulator in run<br>mode    | 3.2             | 3.1     | 2.9       | 2.9   | 2.8      | 5    |      |

| twustop mode           | mode                        | Regulator in low power mode | 7.0             | 5.8     | 5.2       | 4.9   | 4.6      | 9    |      |

| t <sub>WUSTANDBY</sub> | Wakeup from<br>Standby mode | -                           | 60.4            | 55.6    | 53.5      | 52    | 51       | -    | μs   |

| t <sub>WUSLEEP</sub>   | Wakeup from Sleep<br>mode   | -                           |                 | 4 SY    | /SCLK cy  | cles  | <u>.</u> | -    |      |

Table 32. Low-power mode wakeup timings

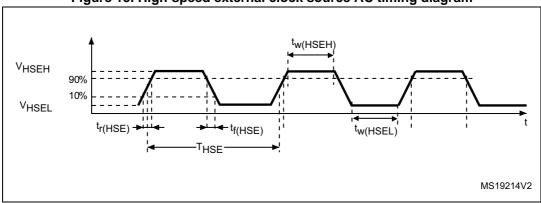

### 6.3.7 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 15: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter <sup>(1)</sup>             | Min                    | Тур | Max                    | Unit |

|----------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage  | 0.7 V <sub>DDIOx</sub> | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage   | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time              | 15                     | -   | -                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   |                                      |                        | -   | 20                     | 115  |

Table 33. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

Figure 15. High-speed external clock source AC timing diagram

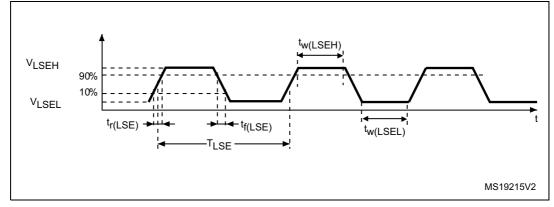

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| $V_{LSEL}$                                   | OSC32_IN input pin low level voltage  | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                      | -      | 50                     | 115  |

Table 34. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### Low-speed internal (LSI) RC oscillator

| Table 39. LSI oscillator | characteristics <sup>(1)</sup> |

|--------------------------|--------------------------------|

|--------------------------|--------------------------------|

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

#### 6.3.9 PLL characteristics

The parameters given in *Table 40* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

| Symbol                | Parameter                      |                   | Value |                    | Unit |

|-----------------------|--------------------------------|-------------------|-------|--------------------|------|

| Symbol                | Faranieler                     | Min               | Тур   | Max                | Onic |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0   | 24 <sup>(2)</sup>  | MHz  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -     | 60 <sup>(2)</sup>  | %    |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -     | 48                 | MHz  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -     | 200 <sup>(2)</sup> | μs   |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -     | 300 <sup>(2)</sup> | ps   |

Table 40. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

#### 6.3.10 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

Table 41. Flash memory characteristics

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

|                    | Supply current          | Write mode                       | -   | -    | 10                 | mA   |

| I <sub>DD</sub>    | Supply current          | Erase mode                       | -   | -    | 12                 | mA   |

1. Guaranteed by design, not tested in production.

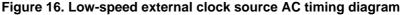

Figure 24. Recommended NRST pin protection

1. The external capacitor protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 51: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

#### 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 52* are derived from tests performed under the conditions summarized in *Table 20: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                                                   | Conditions                                            | Min   | Тур | Max              | Unit               |

|------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|-------|-----|------------------|--------------------|

| V <sub>DDA</sub>                   | Analog supply voltage for ADC ON                            | -                                                     | 2.4   | -   | 3.6              | V                  |

| I <sub>DDA (ADC)</sub>             | Current consumption of the ADC <sup>(1)</sup>               | V <sub>DDA</sub> = 3.3 V                              | -     | 0.9 | -                | mA                 |

| f <sub>ADC</sub>                   | ADC clock frequency                                         | -                                                     | 0.6   | -   | 14               | MHz                |

| f <sub>S</sub> <sup>(2)</sup>      | Sampling rate                                               | 12-bit resolution                                     | 0.043 | -   | 1                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | f <sub>TRIG</sub> <sup>(2)</sup> External trigger frequency | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | -     | -   | 823              | kHz                |

|                                    |                                                             | 12-bit resolution                                     | -     | -   | 17               | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range                                    | -                                                     | 0     | -   | V <sub>DDA</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                                    | See <i>Equation 1</i> and <i>Table 53</i> for details | -     | -   | 50               | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>    | Sampling switch resistance                                  | -                                                     | -     | -   | 1                | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor                          | -                                                     | -     | -   | 8                | pF                 |

| <b>↓</b> (2)(3)                    | Calibration time                                            | f <sub>ADC</sub> = 14 MHz                             |       | 5.9 |                  | μs                 |

| t <sub>CAL</sub> <sup>(2)(3)</sup> | Calibration time                                            | -                                                     | 83    |     |                  | 1/f <sub>ADC</sub> |

Table 52. ADC characteristics

## 6.3.17 DAC electrical specifications

| Table 55. DAC characteristics    |                                                                                                              |     |     |                         |      |                                                                                                                                |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                           | Parameter                                                                                                    | Min | Тур | Max                     | Unit | Comments                                                                                                                       |  |

| V <sub>DDA</sub>                 | Analog supply voltage for<br>DAC ON                                                                          | 2.4 | -   | 3.6                     | V    | -                                                                                                                              |  |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer                                                                                   | 5   | -   | -                       | kΩ   | Load connected to V <sub>SSA</sub>                                                                                             |  |

| LOAD                             | ON                                                                                                           | 25  | -   | -                       | kΩ   | Load connected to V <sub>DDA</sub>                                                                                             |  |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with<br>buffer OFF                                                                          | -   | -   | 15                      | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and V <sub>SS</sub> to have a 1% accuracy is 1.5 M $\Omega$ |  |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -   | -   | 50                      | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                       | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input<br>code (0x0E0) to (0xF1C) at           |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2  | V    | $V_{DDA}$ = 3.6 V and (0x155) and<br>(0xEAB) at $V_{DDA}$ = 2.4 V                                                              |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                       | mV   | It gives the maximum output                                                                                                    |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer OFF                                                                       | -   | -   | V <sub>DDA</sub> – 1LSB | V    | excursion of the DAC.                                                                                                          |  |

| I <sub>DDA</sub> <sup>(1)</sup>  | DAC DC current<br>consumption in quiescent                                                                   | -   | -   | 600                     | μA   | With no load, middle code<br>(0x800) on the input                                                                              |  |

| 'DDA                             | mode <sup>(2)</sup>                                                                                          | -   | -   | 700                     | μA   | With no load, worst code<br>(0xF1C) on the input                                                                               |  |

| DNL <sup>(3)</sup>               | Differential non linearity<br>Difference between two                                                         | -   | -   | ±0.5                    | LSB  | Given for the DAC in 10-bit configuration                                                                                      |  |

|                                  | consecutive code-1LSB)                                                                                       | -   | -   | ±2                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |  |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                      | LSB  | Given for the DAC in 10-bit configuration                                                                                      |  |

| INL <sup>(3)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |  |

|                                  | Offset error                                                                                                 | -   | -   | ±10                     | mV   | -                                                                                                                              |  |

| Offset <sup>(3)</sup>            | (difference between<br>measured value at Code                                                                | -   | -   | ±3                      | LSB  | Given for the DAC in 10-bit at $V_{DDA}$ = 3.6 V                                                                               |  |

|                                  | (0x800) and the ideal value<br>= V <sub>DDA</sub> /2)                                                        | -   | -   | ±12                     | LSB  | Given for the DAC in 12-bit at $V_{DDA}$ = 3.6 V                                                                               |  |

| Table | 55. | DAC | characteristics    |

|-------|-----|-----|--------------------|

| TUDIC |     | DAO | 01101 00101 101100 |

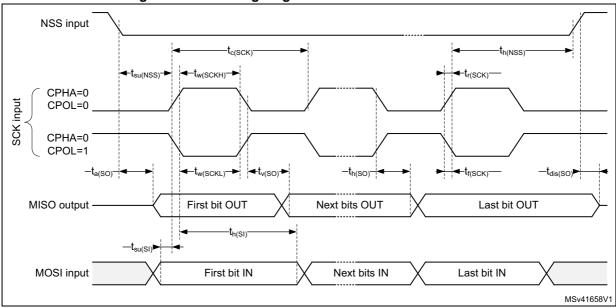

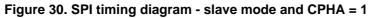

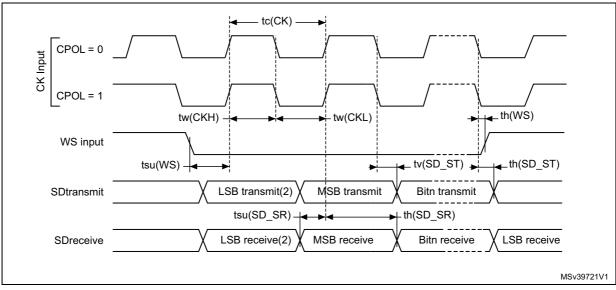

Figure 29. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

| Symbol                               | Parameter              | Conditions         | Min | Мах | Unit |  |  |

|--------------------------------------|------------------------|--------------------|-----|-----|------|--|--|

| t <sub>su(SD_MR)</sub>               | Data input setup time  | Master receiver    | 6   | -   |      |  |  |

| t <sub>su(SD_SR)</sub>               |                        | Slave receiver     | 2   | -   |      |  |  |

| t <sub>h(SD_MR)</sub> <sup>(2)</sup> | Data input hold time   | Master receiver    | 4   | -   |      |  |  |

| t <sub>h(SD_SR)</sub> <sup>(2)</sup> |                        | Slave receiver     | 0.5 | -   |      |  |  |

| t <sub>v(SD_MT)</sub> <sup>(2)</sup> | Data output valid time | Master transmitter | -   | 4   | ns   |  |  |

| t <sub>v(SD_ST)</sub> <sup>(2)</sup> |                        | Slave transmitter  | -   | 20  |      |  |  |

| t <sub>h(SD_MT)</sub>                | Data output hold time  | Master transmitter | 0   | -   | ]    |  |  |

| t <sub>h(SD_ST)</sub>                |                        | Slave transmitter  | 13  | -   |      |  |  |

Table 64. I<sup>2</sup>S characteristics<sup>(1)</sup> (continued)

1. Data based on design simulation and/or characterization results, not tested in production.

2. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$  = 8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  = 125 ns.

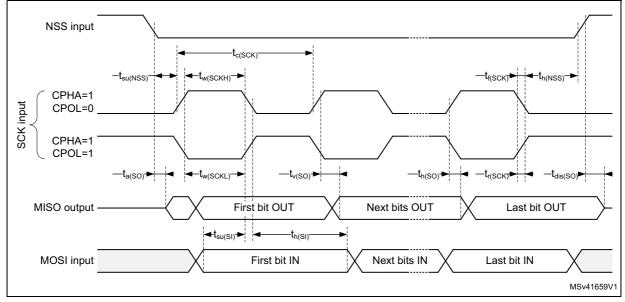

#### Figure 32. I<sup>2</sup>S slave timing diagram (Philips protocol)

1. Measurement points are done at CMOS levels: 0.3 ×  $V_{\text{DDIOx}}$  and 0.7 ×  $V_{\text{DDIOx}}$

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

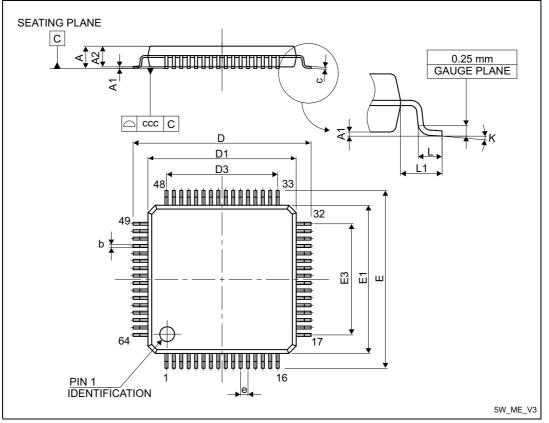

### 7.2 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 37. LQFP64 package outline

1. Drawing is not to scale.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| с      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | -     | 12.000      | -     | -      | 0.4724                | -      |

| D1     | -     | 10.000      | -     | -      | 0.3937                | -      |

| D3     | -     | 7.500       | -     | -      | 0.2953                | -      |

| E      | -     | 12.000      | -     | -      | 0.4724                | -      |

| E1     | -     | 10.000      | -     | -      | 0.3937                | -      |

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |  |

| E3     | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| К      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |  |

| ссс    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

Table 67. LQFP64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

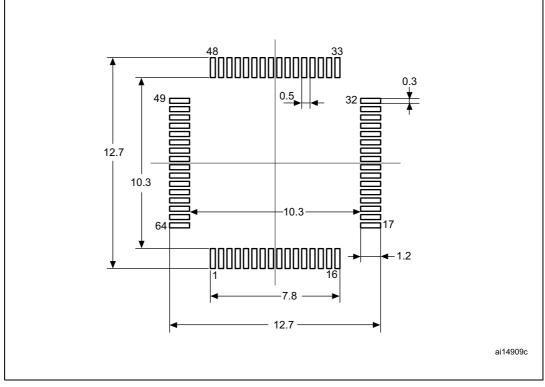

Figure 38. Recommended footprint for LQFP64 package

1. Dimensions are expressed in millimeters.

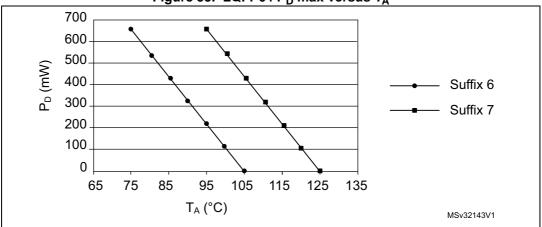

Using the values obtained in *Table* 74  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 45 °C/W

- $T_{Jmax} = 100 \text{ °C} + (45 \text{ °C/W} \times 134 \text{ mW}) = 100 \text{ °C} + 6.03 \text{ °C} = 106.03 \text{ °C}$

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Ordering information*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 55* to select the required temperature range (suffix 6 or 7) according to your ambient temperature or power requirements.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Apr-2012 | 1        | Initial release                                                                                                                                                                                                                                                                          |

|             |          | Updated <i>Table: STM32F051xx family device features and peripheral counts</i> for SPI and I <sup>2</sup> C in 32-pin package.                                                                                                                                                           |

| 25-Apr-2012 | 2        | Corrected Group 3 pin order in <i>Table: Capacitive sensing GPIOs available on STM32F051xx devices.</i>                                                                                                                                                                                  |

|             |          | Updated the current consumption values in Section: Electrical characteristics.                                                                                                                                                                                                           |

|             |          | Updated Table: HSI14 oscillator characteristics                                                                                                                                                                                                                                          |

|             |          | Features reorganized and <i>Figure: Block diagram</i> structure changed.                                                                                                                                                                                                                 |

|             |          | Added LQFP32 package.                                                                                                                                                                                                                                                                    |

|             |          | Updated Section: Cyclic redundancy check calculation unit (CRC).                                                                                                                                                                                                                         |

|             | 3        | Modified the number of priority levels in Section: Nested vectored interrupt controller (NVIC).                                                                                                                                                                                          |

|             |          | Added note 3. for PB2 and PB8, changed TIM2_CH_ETR into TIM2_CH1_ETR in <i>Table: Pin definitions</i> and <i>Table: Alternate functions selected through GPIOA_AFR registers for port A.</i><br>Added <i>Table: Alternate functions selected through GPIOB_AFR registers for port B.</i> |

| 23-Jul-2012 |          | Updated I <sub>VDD</sub> , I <sub>VSS</sub> , and I <sub>INJ(PIN)</sub> in <i>Table: Current characteristics.</i>                                                                                                                                                                        |

|             |          | Updated ACC <sub>HSI</sub> in <i>Table: HSI oscillator characteristics</i> and <i>Table: HSI14 oscillator characteristics</i> .                                                                                                                                                          |

|             |          | Updated Table: I/O current injection susceptibility.                                                                                                                                                                                                                                     |

|             |          | Added BOOT0 input low and high level voltage in <i>Table: I/O</i> static characteristics.                                                                                                                                                                                                |

|             |          | Modified number of pins in V <sub>OL</sub> and V <sub>OH</sub> description, and changed condition for V <sub>OLFM+</sub> in <i>Table: Output voltage characteristics.</i>                                                                                                                |

|             |          | Changed $V_{DD}$ to $V_{DDA}$ in Figure: Typical connection diagram using the ADC.                                                                                                                                                                                                       |

|             |          | Updated Ts_temp in Table: TS characteristics.                                                                                                                                                                                                                                            |

|             |          | Updated Figure: I/O AC characteristics definition.                                                                                                                                                                                                                                       |

#### Table 76. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28-Aug-2015 | 5        | <ul> <li>Updated the following:</li> <li>DAC and power management feature descriptions in <i>Features</i></li> <li>Table 2: STM32F051xx family device features and peripheral count</li> <li>Section 3.5.1: Power supply schemes</li> <li>Figure 13: Power supply scheme</li> <li>Table 17: Voltage characteristics</li> <li>Table 20: General operating conditions: updated the footnote for V<sub>IN</sub> parameter</li> <li>Table 28: Typical and maximum current consumption from the V<sub>BAT</sub> supply</li> <li>Table 52: ADC characteristics</li> <li>Table 33: High-speed external user clock characteristics: replaced V<sub>DD</sub> with V<sub>DDIOX</sub></li> <li>Table 34: Low-speed external user clock characteristics: replaced V<sub>DD</sub> with V<sub>DDIOX</sub></li> <li>Table 37: HSI oscillator characteristics and Figure 19: HSI oscillator characteristics: changed the min value for ACC<sub>HSI14</sub></li> <li>Table 41: Flash memory characteristics: changed the values for t<sub>ME</sub> and I<sub>DD</sub> in write mode</li> <li>Table 43: EMS characteristics changed the value of V<sub>EFTB</sub></li> <li>Table 43: EMS characteristics changed the value of V<sub>EFTB</sub></li> <li>Figure 10: STM32F051x8 memory map</li> <li>Figure 21: TC and TTa I/O input characteristics</li> <li>Figure 22: Five volt tolerant (FT and FTf) I/O input characteristics</li> <li>Figure 23: I/O AC characteristics: changed the description and values for V<sub>SC</sub>, V<sub>DDA</sub> and V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Section 6.3:2: Communication interfaces: updated the min value for T<sub>S</sub>-v<sub>bat</sub> and the typical value for R parameters</li> <li>Section and features in the subsection I<sup>2</sup>C interface characteristics:</li> <li>Table 58: V<sub>BAT</sub> monitoring characteristics: changed the min value for T<sub>S</sub>- temp</li> <li>Table 57: TS characteristics: updated the min value for table 57: Communication interfaces: updated the description and features in the subsection I<sup>2</sup>C interface characteristics</li> <li>Table 58: V<sub>BAT</sub> monitoring characterist</li></ul> |

Table 76. Document revision history (continued)