Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 27                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051k4u7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1 | Introd | duction             |                                                   |

|---|--------|---------------------|---------------------------------------------------|

| 2 | Desci  | ription .           |                                                   |

| 3 | Funct  | tional ov           | verview                                           |

|   | 3.1    | ARM <sup>®</sup> -0 | Cortex <sup>®</sup> -M0 core                      |

|   | 3.2    | Memori              | es 13                                             |

|   | 3.3    | Boot mo             | odes                                              |

|   | 3.4    | Cyclic re           | edundancy check calculation unit (CRC)            |

|   | 3.5    | Power r             | nanagement                                        |

|   |        | 3.5.1               | Power supply schemes                              |

|   |        | 3.5.2               | Power supply supervisors                          |

|   |        | 3.5.3               | Voltage regulator                                 |

|   |        | 3.5.4               | Low-power modes                                   |

|   | 3.6    | Clocks a            | and startup                                       |

|   | 3.7    | General             | I-purpose inputs/outputs (GPIOs) 16               |

|   | 3.8    | Direct m            | nemory access controller (DMA) 17                 |

|   | 3.9    | Interrup            | ts and events                                     |

|   |        | 3.9.1               | Nested vectored interrupt controller (NVIC)       |

|   |        | 3.9.2               | Extended interrupt/event controller (EXTI)        |

|   | 3.10   | Analog-             | to-digital converter (ADC) 17                     |

|   |        | 3.10.1              | Temperature sensor                                |

|   |        | 3.10.2              | Internal voltage reference (V <sub>REFINT</sub> ) |

|   |        | 3.10.3              | V <sub>BAT</sub> battery voltage monitoring       |

|   | 3.11   | Digital-t           | o-analog converter (DAC) 19                       |

|   | 3.12   | Compar              | rators (COMP) 19                                  |

|   | 3.13   | Touch s             | ensing controller (TSC) 19                        |

|   | 3.14   | Timers a            | and watchdogs                                     |

|   |        | 3.14.1              | Advanced-control timer (TIM1)                     |

|   |        | 3.14.2              | General-purpose timers (TIM2, 3, 14, 15, 16, 17)  |

|   |        | 3.14.3              | Basic timer TIM6                                  |

|   |        | 3.14.4              | Independent watchdog (IWDG) 22                    |

|   |        | 3.14.5              | System window watchdog (WWDG)23                   |

DocID022265 Rev 7

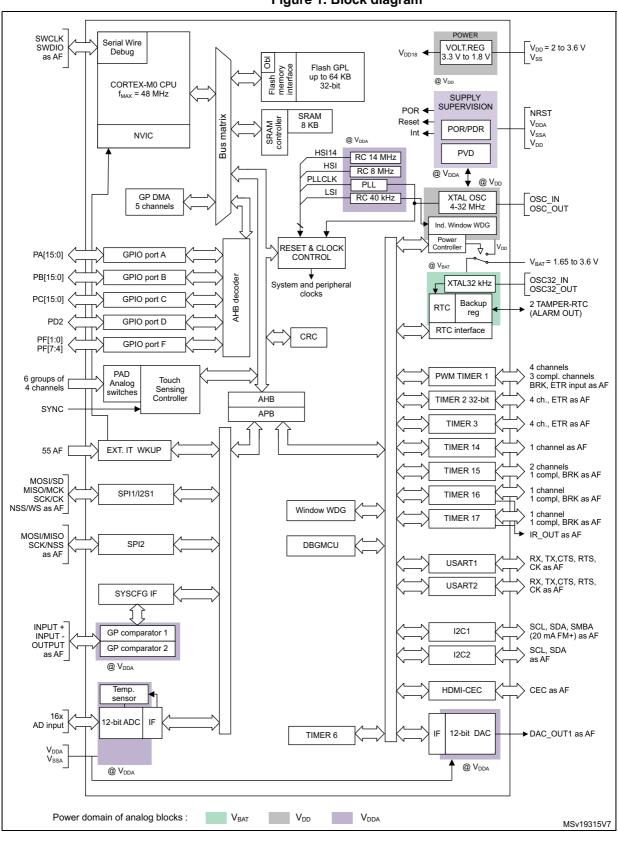

Figure 1. Block diagram

DocID022265 Rev 7

sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

#### 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

#### 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Table 4. Internal voltage reference calib | oration values |

|-------------------------------------------|----------------|

|-------------------------------------------|----------------|

| Calibration value name | Description                                                                              | Memory address            |

|------------------------|------------------------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |

## 3.14 Timers and watchdogs

The STM32F051xx devices include up to six general-purpose timers, one basic timer and an advanced control timer.

Table 7 compares the features of the different timers.

|                    |                |                    |                      |                            | •                            |                             |                          |

|--------------------|----------------|--------------------|----------------------|----------------------------|------------------------------|-----------------------------|--------------------------|

| Timer<br>type      | Timer          | Counter resolution | Counter<br>type      | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

| Advanced control   | TIM1           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | 3                        |

|                    | TIM2           | 32-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

|                    | TIM3           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

| General<br>purpose | TIM14          | 16-bit             | Up                   | integer from<br>1 to 65536 | No                           | 1                           | -                        |

|                    | TIM15          | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 2                           | 1                        |

|                    | TIM16<br>TIM17 | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 1                           | 1                        |

| Basic              | TIM6           | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | -                           | -                        |

Table 7. Timer feature comparison

#### 3.14.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- input capture

- output compare

- PWM generation (edge or center-aligned modes)

- one-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

| I <sup>2</sup> C features <sup>(1)</sup> | I2C1 | I2C2 |

|------------------------------------------|------|------|

| SMBus                                    | Х    | -    |

| Wakeup from STOP                         | Х    | -    |

| Table 9. STM32F051xx I <sup>2</sup> C implementation ( | (continued) |

|--------------------------------------------------------|-------------|

|--------------------------------------------------------|-------------|

1. X = supported.

# 3.17 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds up to two universal synchronous/asynchronous receivers/transmitters (USART1, USART2) which communicate at speeds of up to 6 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 supports also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and has a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 |  |

|---------------------------------------------|--------|--------|--|

| Hardware flow control for modem             | Х      | Х      |  |

| Continuous communication using DMA          | Х      | х      |  |

| Multiprocessor communication                | Х      | х      |  |

| Synchronous mode                            | Х      | х      |  |

| Smartcard mode                              | Х      | -      |  |

| Single-wire half-duplex communication       | Х      | х      |  |

| IrDA SIR ENDEC block                        | Х      | -      |  |

| LIN mode                                    | Х      | -      |  |

| Dual clock domain and wakeup from Stop mode | Х      | -      |  |

| Receiver timeout interrupt                  | Х      | -      |  |

| Modbus communication                        | Х      | -      |  |

| Auto baud rate detection                    | Х      | -      |  |

| Driver Enable                               | Х      | х      |  |

#### Table 10. STM32F051xx USART implementation

1. X = supported.

| Symbol                               | Ratings                                                                         | Max.                 | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|----------------------|------|

| ΣI <sub>VDD</sub>                    | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                                      | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                                | -25                  |      |

| ΣI                                   | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                                      | Injected current on B, FT and FTf pins                                          | -5/+0 <sup>(4)</sup> |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                              | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  | 1    |

| ΣI <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 |      |

#### Table 18. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. A positive injection is induced by  $V_{IN} > V_{DDIOx}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 17: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

On these I/Os, a positive injection is induced by V<sub>IN</sub> > V<sub>DDA</sub>. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 54: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 19. Thermal characteristics

| Symbol           | Ratings Value                |             | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

## 6.3 Operating conditions

#### 6.3.1 General operating conditions

| Symbol            | Parameter                                                                                                                                                                     | Conditions                           | Min      | Max                                  | Unit    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|--------------------------------------|---------|

| f <sub>HCLK</sub> | Internal AHB clock frequency                                                                                                                                                  | -                                    | 0        | 48                                   | MHz     |

| f <sub>PCLK</sub> | Internal APB clock frequency                                                                                                                                                  | -                                    | 0        | 48                                   | INILITZ |

| V <sub>DD</sub>   | Standard operating voltage                                                                                                                                                    | -                                    | 2.0      | 3.6                                  | V       |

| M                 | Analog operating voltage<br>(ADC and DAC not used)                                                                                                                            | Must have a potential equal          | $V_{DD}$ | 3.6                                  | V       |

| V <sub>DDA</sub>  | Analog operating voltage<br>(ADC and DAC used)                                                                                                                                | to or higher than V <sub>DD</sub>    | 2.4      | 3.6                                  | V       |

| V <sub>BAT</sub>  | Backup operating voltage                                                                                                                                                      | -                                    | 1.65     | 3.6                                  | V       |

|                   |                                                                                                                                                                               | TC and RST I/O                       | -0.3     | V <sub>DDIOx</sub> +0.3              |         |

|                   |                                                                                                                                                                               | TTa I/O                              | -0.3     | V <sub>DDA</sub> +0.3 <sup>(1)</sup> | V       |

| V <sub>IN</sub>   | I/O input voltage                                                                                                                                                             | FT and FTf I/O                       | -0.3     | 5.5 <sup>(1)</sup>                   |         |

|                   |                                                                                                                                                                               | BOOT0                                | 0        | 5.5                                  |         |

|                   | Power dissipation at $T_A = 85 \text{ °C}$<br>for suffix 6 or $T_A = 105 \text{ °C}$ for<br>suffix 7 <sup>(2)</sup><br>UFQFPN32<br>UFQFPN48<br>UFQFPN48<br>UFBGA64<br>WLCSP36 | LQFP64                               | -        | 444                                  |         |

|                   |                                                                                                                                                                               | LQFP48                               | -        | 364                                  | mW      |

|                   |                                                                                                                                                                               | LQFP32                               | -        | 357                                  |         |

| $P_{D}$           |                                                                                                                                                                               | UFQFPN32                             | -        | 526                                  |         |

|                   |                                                                                                                                                                               | UFQFPN48                             | -        | 625                                  |         |

|                   |                                                                                                                                                                               | UFBGA64                              | -        | 308                                  |         |

|                   |                                                                                                                                                                               | WLCSP36                              | -        | 333                                  |         |

|                   | Ambient temperature for the                                                                                                                                                   | Maximum power dissipation            | -40      | 85                                   | °C      |

| TA                | suffix 6 version                                                                                                                                                              | Low power dissipation <sup>(3)</sup> | -40      | 105                                  | U       |

| IA                | Ambient temperature for the<br>suffix 7 versionMaximum power dissipationLow power dissipation(3)                                                                              | Maximum power dissipation            | -40      | 105                                  | °C      |

|                   |                                                                                                                                                                               | Low power dissipation <sup>(3)</sup> | -40      | 125                                  | C       |

| TJ                | lunction tomperature range                                                                                                                                                    | Suffix 6 version                     | -40      | 105                                  | °C      |

| IJ                | Junction temperature range                                                                                                                                                    | Suffix 7 version                     | -40      | 125                                  |         |

#### Table 20. General operating conditions

1. For operation with a voltage higher than  $V_{DDIOx}$  + 0.3 V, the internal pull-up resistor must be disabled.

2. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ . See Section 7.8: Thermal characteristics.

3. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.8: *Thermal characteristics*).

#### 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 21* are derived from tests performed under the ambient temperature condition summarized in *Table 20*.

DocID022265 Rev 7

| Symbol            | Parameter                       | Conditions | Min | Мах | Unit |  |

|-------------------|---------------------------------|------------|-----|-----|------|--|

| +                 | V <sub>DD</sub> rise time rate  |            | 0   | 8   |      |  |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate  |            | 20  | 8   |      |  |

| +                 | V <sub>DDA</sub> rise time rate |            | 0   | 8   | µs/V |  |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate |            | 20  | 8   |      |  |

Table 21. Operating conditions at power-up / power-down

#### 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

Table 22. Embedded reset and power control block characteristics

| Symbol                               | Parameter           | Conditions                  | Min                 | Тур  | Мах                 | Unit |

|--------------------------------------|---------------------|-----------------------------|---------------------|------|---------------------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  | Power on/power down | Falling edge <sup>(2)</sup> | 1.80                | 1.88 | 1.96 <sup>(3)</sup> | V    |

| VPOR/PDR`´                           | reset threshold     | Rising edge                 | 1.84 <sup>(3)</sup> | 1.92 | 2.00                | V    |

| V <sub>PDRhyst</sub>                 | PDR hysteresis      | -                           | -                   | 40   | -                   | mV   |

| t <sub>RSTTEMPO</sub> <sup>(4)</sup> | Reset temporization | -                           | 1.50                | 2.50 | 4.50                | ms   |

1. The PDR detector monitors  $V_{DD}$  and also  $V_{DDA}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}.$

2. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

3. Data based on characterization results, not tested in production.

4. Guaranteed by design, not tested in production.

| Symbol            | Parameter        | Conditions   | Min  | Тур  | Max  | Unit |

|-------------------|------------------|--------------|------|------|------|------|

| V                 | PVD threshold 0  | Rising edge  | 2.1  | 2.18 | 2.26 | V    |

| V <sub>PVD0</sub> |                  | Falling edge | 2    | 2.08 | 2.16 | V    |

| M                 | PVD threshold 1  | Rising edge  | 2.19 | 2.28 | 2.37 | V    |

| V <sub>PVD1</sub> |                  | Falling edge | 2.09 | 2.18 | 2.27 | V    |

| M                 | PVD threshold 2  | Rising edge  | 2.28 | 2.38 | 2.48 | V    |

| V <sub>PVD2</sub> |                  | Falling edge | 2.18 | 2.28 | 2.38 | V    |

| M                 | PVD threshold 3  | Rising edge  | 2.38 | 2.48 | 2.58 | V    |

| V <sub>PVD3</sub> |                  | Falling edge | 2.28 | 2.38 | 2.48 | V    |

| M                 | D)(D threshold 4 | Rising edge  | 2.47 | 2.58 | 2.69 | V    |

| V <sub>PVD4</sub> | PVD threshold 4  | Falling edge | 2.37 | 2.48 | 2.59 | V    |

| M                 | D)(D threshold 5 | Rising edge  | 2.57 | 2.68 | 2.79 | V    |

| V <sub>PVD5</sub> | PVD threshold 5  | Falling edge | 2.47 | 2.58 | 2.69 | V    |

Table 23. Programmable voltage detector characteristics

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 31*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 17: Voltage characteristics*

|     | Peripheral               | Typical consumption at 25 °C | Unit     |  |

|-----|--------------------------|------------------------------|----------|--|

|     | BusMatrix <sup>(1)</sup> | 5                            |          |  |

|     | DMA1                     | 7                            |          |  |

|     | SRAM                     | 1                            |          |  |

|     | Flash memory interface   | 14                           |          |  |

|     | CRC                      | 2                            |          |  |

| АНВ | GPIOA                    | 9                            | µA/MHz   |  |

| АПБ | GPIOB                    | 12                           | μΑνινιπΖ |  |

|     | GPIOC                    | 2                            |          |  |

|     | GPIOD                    | 1                            |          |  |

|     | GPIOF                    | 1                            | ]        |  |

|     | TSC                      | 6                            |          |  |

|     | All AHB peripherals      | 55                           |          |  |

#### Table 31. Peripheral current consumption

1. Guaranteed by design, not tested in production.

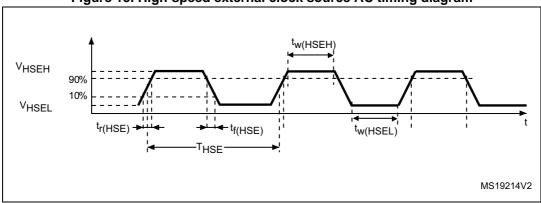

Figure 15. High-speed external clock source AC timing diagram

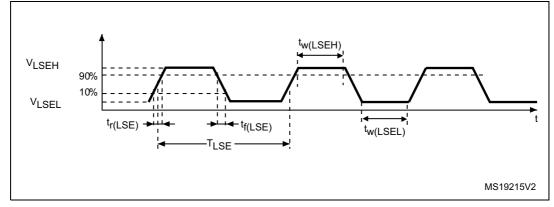

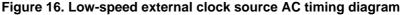

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| $V_{LSEL}$                                   | OSC32_IN input pin low level voltage  | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   |                                       |                        | -      | 50                     | 115  |

Table 34. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

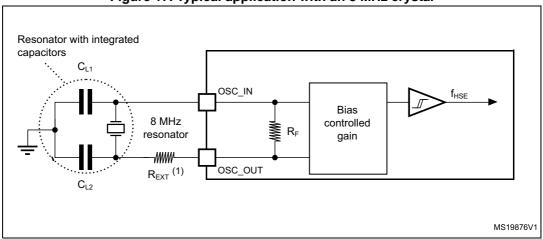

Figure 17. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 36*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions <sup>(1)</sup>                        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------------------|--------------------------------------------------|--------------------|-----|--------------------|------|

|                                     |                                         | low drive capability                             | -                  | 0.5 | 0.9                |      |

|                                     | ISE ourrent consumption                 | medium-low drive capability                      | -                  | -   | 1                  |      |

| 'DD                                 | I <sub>DD</sub> LSE current consumption | medium-high drive capability                     | -                  | -   | 1.3                | μA   |

|                                     |                                         | high drive capability                            | -                  | -   | 1.6                |      |

|                                     |                                         | low drive capability                             | 5                  | -   | -                  |      |

|                                     | Oscillator                              | medium-low drive capability                      | 8                  | -   | -                  | µA/V |

| 9 <sub>m</sub>                      | transconductance                        | transconductance medium-high drive capability 15 |                    | -   | -                  | μΑνν |

|                                     |                                         | high drive capability                            | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                            | V <sub>DDIOx</sub> is stabilized                 | -                  | 2   | -                  | S    |

| Table 36. LSE oscillator | characteristics | (f <sub>LSE</sub> = 32.768 kHz) |

|--------------------------|-----------------|---------------------------------|

|--------------------------|-----------------|---------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

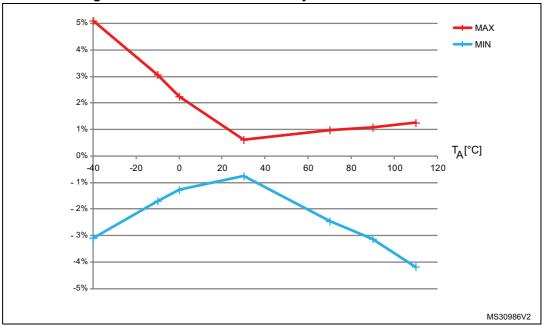

### High-speed internal 14 MHz (HSI14) RC oscillator (dedicated to ADC)

| Symbol                  | Parameter                                                | Conditions                     | Min                 | Тур | Max                | Unit |  |

|-------------------------|----------------------------------------------------------|--------------------------------|---------------------|-----|--------------------|------|--|

| f <sub>HSI14</sub>      | Frequency                                                | -                              | -                   | 14  | -                  | MHz  |  |

| TRIM                    | HSI14 user-trimming step                                 | -                              | -                   | -   | 1 <sup>(2)</sup>   | %    |  |

| DuCy <sub>(HSI14)</sub> | Duty cycle                                               | -                              | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |  |

|                         | Accuracy of the HSI14<br>oscillator (factory calibrated) | T <sub>A</sub> = -40 to 105 °C | -4.2 <sup>(3)</sup> | -   | 5.1 <sup>(3)</sup> | %    |  |

| ACC                     |                                                          | T <sub>A</sub> = −10 to 85 °C  | -3.2 <sup>(3)</sup> | -   | 3.1 <sup>(3)</sup> | %    |  |

| ACC <sub>HSI14</sub>    |                                                          | T <sub>A</sub> = 0 to 70 °C    | -2.5 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |  |

|                         |                                                          | T <sub>A</sub> = 25 °C         | -1                  | -   | 1                  | %    |  |

| t <sub>su(HSI14)</sub>  | HSI14 oscillator startup time                            | -                              | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |  |

| I <sub>DDA(HSI14)</sub> | HSI14 oscillator power<br>consumption                    | -                              | -                   | 100 | 150 <sup>(2)</sup> | μA   |  |

#### Table 38. HSI14 oscillator characteristics<sup>(1)</sup>

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

#### Figure 20. HSI14 oscillator accuracy characterization results

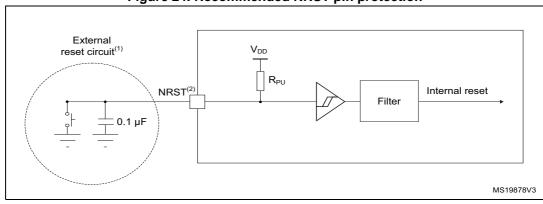

Figure 24. Recommended NRST pin protection

1. The external capacitor protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 51: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

#### 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 52* are derived from tests performed under the conditions summarized in *Table 20: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                                                   | Conditions                                            | Min   | Тур | Max              | Unit               |

|------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|-------|-----|------------------|--------------------|

| V <sub>DDA</sub>                   | Analog supply voltage for ADC ON                            | -                                                     | 2.4   | -   | 3.6              | V                  |

| I <sub>DDA (ADC)</sub>             | Current consumption of the ADC <sup>(1)</sup>               | V <sub>DDA</sub> = 3.3 V                              | -     | 0.9 | -                | mA                 |

| f <sub>ADC</sub>                   | ADC clock frequency                                         | -                                                     | 0.6   | -   | 14               | MHz                |

| f <sub>S</sub> <sup>(2)</sup>      | Sampling rate                                               | 12-bit resolution                                     | 0.043 | -   | 1                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | f <sub>TRIG</sub> <sup>(2)</sup> External trigger frequency | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | -     | -   | 823              | kHz                |

|                                    |                                                             | 12-bit resolution                                     | -     | -   | 17               | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range                                    | -                                                     | 0     | -   | V <sub>DDA</sub> | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                                    | See <i>Equation 1</i> and <i>Table 53</i> for details | -     | -   | 50               | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>    | Sampling switch resistance                                  | -                                                     | -     | -   | 1                | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor                          | -                                                     | -     | -   | 8                | pF                 |

| <b>↓</b> (2)(3)                    | Calibration time                                            | f <sub>ADC</sub> = 14 MHz                             | 5.9   |     |                  | μs                 |

| t <sub>CAL</sub> <sup>(2)(3)</sup> | Calibration time                                            | -                                                     | 83    |     |                  | 1/f <sub>ADC</sub> |

Table 52. ADC characteristics

## 6.3.17 DAC electrical specifications

|                                  | Table 55. DAC characteristics                                                                                |     |     |                         |      |                                                                                                                                |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                           | Parameter                                                                                                    | Min | Тур | Мах                     | Unit | Comments                                                                                                                       |  |  |

| V <sub>DDA</sub>                 | Analog supply voltage for<br>DAC ON                                                                          | 2.4 | -   | 3.6                     | V    | -                                                                                                                              |  |  |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer                                                                                   | 5   | -   | -                       | kΩ   | Load connected to V <sub>SSA</sub>                                                                                             |  |  |

| LOAD                             | ON                                                                                                           | 25  | -   | -                       | kΩ   | Load connected to V <sub>DDA</sub>                                                                                             |  |  |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with<br>buffer OFF                                                                          | -   | -   | 15                      | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and V <sub>SS</sub> to have a 1% accuracy is 1.5 M $\Omega$ |  |  |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -   | -   | 50                      | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                |  |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                       | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input<br>code (0x0E0) to (0xF1C) at           |  |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2  | V    | $V_{DDA}$ = 3.6 V and (0x155) and<br>(0xEAB) at $V_{DDA}$ = 2.4 V                                                              |  |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                       | mV   | It gives the maximum output                                                                                                    |  |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer OFF                                                                       | -   | -   | V <sub>DDA</sub> – 1LSB | V    | excursion of the DAC.                                                                                                          |  |  |

| I <sub>DDA</sub> <sup>(1)</sup>  | DAC DC current<br>consumption in quiescent                                                                   | -   | -   | 600                     | μA   | With no load, middle code<br>(0x800) on the input                                                                              |  |  |

| 'DDA                             | mode <sup>(2)</sup>                                                                                          | -   | -   | 700                     | μA   | With no load, worst code<br>(0xF1C) on the input                                                                               |  |  |

| DNL <sup>(3)</sup>               | Differential non linearity<br>Difference between two                                                         | -   | -   | ±0.5                    | LSB  | Given for the DAC in 10-bit configuration                                                                                      |  |  |

|                                  | consecutive code-1LSB)                                                                                       | -   | -   | ±2                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |  |  |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                      | LSB  | Given for the DAC in 10-bit configuration                                                                                      |  |  |

| INL <sup>(3)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |  |  |

|                                  | Offset error                                                                                                 | -   | -   | ±10                     | mV   | -                                                                                                                              |  |  |

| Offset <sup>(3)</sup>            | (difference between<br>measured value at Code                                                                | -   | -   | ±3                      | LSB  | Given for the DAC in 10-bit at $V_{DDA}$ = 3.6 V                                                                               |  |  |

|                                  | (0x800) and the ideal value<br>= V <sub>DDA</sub> /2)                                                        | -   | -   | ±12                     | LSB  | Given for the DAC in 12-bit at $V_{DDA}$ = 3.6 V                                                                               |  |  |

| Table | 55. | DAC | characteristics    |

|-------|-----|-----|--------------------|

| TUDIC |     | DAO | 01101 00101 101100 |

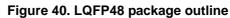

## 7.3 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

1. Drawing is not to scale.

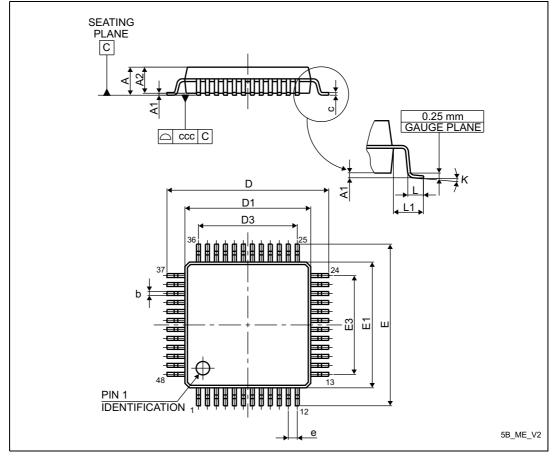

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 45. UFQFPN48 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

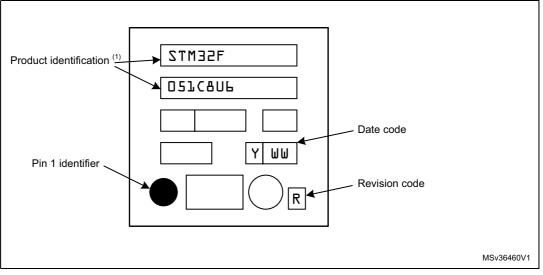

## 7.6 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

Figure 49. LQFP32 package outline

1. Drawing is not to scale.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Apr-2012 | 1        | Initial release                                                                                                                                                                                                                                                                          |

|             |          | Updated <i>Table: STM32F051xx family device features and peripheral counts</i> for SPI and I <sup>2</sup> C in 32-pin package.                                                                                                                                                           |

| 25-Apr-2012 | 2        | Corrected Group 3 pin order in <i>Table: Capacitive sensing GPIOs available on STM32F051xx devices.</i>                                                                                                                                                                                  |

|             |          | Updated the current consumption values in Section: Electrical characteristics.                                                                                                                                                                                                           |

|             |          | Updated Table: HSI14 oscillator characteristics                                                                                                                                                                                                                                          |

|             |          | Features reorganized and <i>Figure: Block diagram</i> structure changed.                                                                                                                                                                                                                 |

|             |          | Added LQFP32 package.                                                                                                                                                                                                                                                                    |

|             |          | Updated Section: Cyclic redundancy check calculation unit (CRC).                                                                                                                                                                                                                         |

|             |          | Modified the number of priority levels in Section: Nested vectored interrupt controller (NVIC).                                                                                                                                                                                          |

|             |          | Added note 3. for PB2 and PB8, changed TIM2_CH_ETR into TIM2_CH1_ETR in <i>Table: Pin definitions</i> and <i>Table: Alternate functions selected through GPIOA_AFR registers for port A.</i><br>Added <i>Table: Alternate functions selected through GPIOB_AFR registers for port B.</i> |

| 23-Jul-2012 | 3        | Updated I <sub>VDD</sub> , I <sub>VSS</sub> , and I <sub>INJ(PIN)</sub> in <i>Table: Current characteristics.</i>                                                                                                                                                                        |

|             |          | Updated ACC <sub>HSI</sub> in <i>Table: HSI oscillator characteristics</i> and <i>Table: HSI14 oscillator characteristics</i> .                                                                                                                                                          |

|             |          | Updated Table: I/O current injection susceptibility.                                                                                                                                                                                                                                     |

|             |          | Added BOOT0 input low and high level voltage in <i>Table: I/O</i> static characteristics.                                                                                                                                                                                                |

|             |          | Modified number of pins in V <sub>OL</sub> and V <sub>OH</sub> description, and changed condition for V <sub>OLFM+</sub> in <i>Table: Output voltage characteristics.</i>                                                                                                                |

|             |          | Changed $V_{DD}$ to $V_{DDA}$ in Figure: Typical connection diagram using the ADC.                                                                                                                                                                                                       |

|             |          | Updated Ts_temp in Table: TS characteristics.                                                                                                                                                                                                                                            |

|             |          | Updated Figure: I/O AC characteristics definition.                                                                                                                                                                                                                                       |

#### Table 76. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 28-Aug-2015 | 5        | <ul> <li>Updated the following:</li> <li>DAC and power management feature descriptions in <i>Features</i></li> <li>Table 2: STM32F051xx family device features and peripheral count</li> <li>Section 3.5.1: Power supply schemes</li> <li>Figure 13: Power supply scheme</li> <li>Table 17: Voltage characteristics</li> <li>Table 20: General operating conditions: updated the footnote for V<sub>IN</sub> parameter</li> <li>Table 28: Typical and maximum current consumption from the V<sub>BAT</sub> supply</li> <li>Table 52: ADC characteristics</li> <li>Table 33: High-speed external user clock characteristics: replaced V<sub>DD</sub> with V<sub>DDIOX</sub></li> <li>Table 34: Low-speed external user clock characteristics: replaced V<sub>DD</sub> with V<sub>DDIOX</sub></li> <li>Table 37: HSI oscillator characteristics and Figure 19: HSI oscillator characteristics: changed the min value for ACC<sub>HSI14</sub></li> <li>Table 41: Flash memory characteristics: changed the values for t<sub>ME</sub> and I<sub>DD</sub> in write mode</li> <li>Table 43: EMS characteristics changed the value of V<sub>EFTB</sub></li> <li>Table 43: EMS characteristics changed the value of V<sub>EFTB</sub></li> <li>Figure 10: STM32F051x8 memory map</li> <li>Figure 21: TC and TTa I/O input characteristics</li> <li>Figure 22: Five volt tolerant (FT and FTf) I/O input characteristics</li> <li>Figure 23: I/O AC characteristics: changed the description and values for V<sub>SC</sub>, V<sub>DDA</sub> and V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Added Figure 28: Maximum V<sub>REFINT</sub> parameters. Section 6.3:2: Communication interfaces: updated the min value for T<sub>S</sub>-v<sub>bat</sub> and the typical value for R parameters</li> <li>Section and features in the subsection I<sup>2</sup>C interface characteristics:</li> <li>Table 57: TS characteristics: updated the min value for Ts - temp</li> <li>Table 58: V<sub>BAT</sub> monitoring characteristics: changed the min value for Ts-v<sub>bat</sub> and the typical value for R parameters</li> <li>Section 6.3:2: Communication interfaces: updated the description and features in the subsection I<sup>2</sup>C interface cha</li></ul> |

Table 76. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-Jan-2017 | 7        | <ul> <li>Section 6: Electrical characteristics:</li> <li>Table 36: LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) - information on configuring different drive capabilities removed. See the corresponding reference manual.</li> <li>Table 24: Embedded internal reference voltage - V<sub>REFINT</sub> values</li> <li>Table 55: DAC characteristics - min. R<sub>LOAD</sub> to V<sub>DDA</sub> defined</li> <li>Figure 29: SPI timing diagram - slave mode and CPHA = 0 and Figure 30: SPI timing diagram - slave mode and CPHA = 1 enhanced and corrected</li> <li>Section 8: Ordering information:</li> <li>The name of the section changed from the previous "Part numbering"</li> </ul> |

Table 76. Document revision history (continued)