Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 55                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051r4t6 |

# **Contents**

| 1 | Intro | duction                                |                                                   | 9  |  |  |

|---|-------|----------------------------------------|---------------------------------------------------|----|--|--|

| 2 | Desc  | cription                               |                                                   | 10 |  |  |

| 3 | Fund  | ctional o                              | verview                                           | 13 |  |  |

|   | 3.1   | ARM®-                                  | Cortex®-M0 core                                   | 13 |  |  |

|   | 3.2   | Memor                                  | ies                                               | 13 |  |  |

|   | 3.3   | Boot m                                 | odes                                              | 13 |  |  |

|   | 3.4   | Cyclic r                               | redundancy check calculation unit (CRC)           | 14 |  |  |

|   | 3.5   | Power                                  | management                                        | 14 |  |  |

|   |       | 3.5.1                                  | Power supply schemes                              | 14 |  |  |

|   |       | 3.5.2                                  | Power supply supervisors                          | 14 |  |  |

|   |       | 3.5.3                                  | Voltage regulator                                 | 14 |  |  |

|   |       | 3.5.4                                  | Low-power modes                                   | 15 |  |  |

|   | 3.6   | Clocks                                 | and startup                                       | 15 |  |  |

|   | 3.7   | General-purpose inputs/outputs (GPIOs) |                                                   |    |  |  |

|   | 3.8   | Direct r                               | memory access controller (DMA)                    | 17 |  |  |

|   | 3.9   | Interrup                               | ots and events                                    | 17 |  |  |

|   |       | 3.9.1                                  | Nested vectored interrupt controller (NVIC)       | 17 |  |  |

|   |       | 3.9.2                                  | Extended interrupt/event controller (EXTI)        | 17 |  |  |

|   | 3.10  | Analog                                 | -to-digital converter (ADC)                       | 17 |  |  |

|   |       | 3.10.1                                 | Temperature sensor                                | 18 |  |  |

|   |       | 3.10.2                                 | Internal voltage reference (V <sub>REFINT</sub> ) |    |  |  |

|   |       | 3.10.3                                 | V <sub>BAT</sub> battery voltage monitoring       | 19 |  |  |

|   | 3.11  | Digital-                               | to-analog converter (DAC)                         | 19 |  |  |

|   | 3.12  | Compa                                  | rators (COMP)                                     | 19 |  |  |

|   | 3.13  | Touch s                                | sensing controller (TSC)                          | 19 |  |  |

|   | 3.14  | Timers                                 | and watchdogs                                     | 21 |  |  |

|   |       | 3.14.1                                 | Advanced-control timer (TIM1)                     | 21 |  |  |

|   |       | 3.14.2                                 | General-purpose timers (TIM2, 3, 14, 15, 16, 17)  | 22 |  |  |

|   |       | 3.14.3                                 | Basic timer TIM6                                  | 22 |  |  |

|   |       | 3.14.4                                 | Independent watchdog (IWDG)                       |    |  |  |

|   |       | 3.14.5                                 | System window watchdog (WWDG)                     | 23 |  |  |

|   |       | 3.14.6   | SysTick timer                                                                    | . 23 |

|---|-------|----------|----------------------------------------------------------------------------------|------|

|   | 3.15  | Real-tir | me clock (RTC) and backup registers                                              | . 23 |

|   | 3.16  | Inter-in | tegrated circuit interface (I <sup>2</sup> C)                                    | . 24 |

|   | 3.17  | Univers  | sal synchronous/asynchronous receiver/transmitter (USART)                        | . 25 |

|   | 3.18  |          | peripheral interface (SPI) / Inter-integrated sound interface (I <sup>2</sup> S) |      |

|   | 3.19  | High-de  | efinition multimedia interface (HDMI) - consumer nics control (CEC)              |      |

|   | 3.20  | Serial v | wire debug port (SW-DP)                                                          | . 26 |

| 4 | Pino  | uts and  | pin descriptions                                                                 | . 27 |

| 5 | Mem   | ory map  | oping                                                                            | . 39 |

| 6 | Elect | rical ch | aracteristics                                                                    | . 42 |

|   | 6.1   | Parame   | eter conditions                                                                  | . 42 |

|   |       | 6.1.1    | Minimum and maximum values                                                       | . 42 |

|   |       | 6.1.2    | Typical values                                                                   | . 42 |

|   |       | 6.1.3    | Typical curves                                                                   | . 42 |

|   |       | 6.1.4    | Loading capacitor                                                                | . 42 |

|   |       | 6.1.5    | Pin input voltage                                                                | . 42 |

|   |       | 6.1.6    | Power supply scheme                                                              | . 43 |

|   |       | 6.1.7    | Current consumption measurement                                                  | . 44 |

|   | 6.2   | Absolu   | te maximum ratings                                                               | . 45 |

|   | 6.3   | Operati  | ing conditions                                                                   | . 47 |

|   |       | 6.3.1    | General operating conditions                                                     | . 47 |

|   |       | 6.3.2    | Operating conditions at power-up / power-down                                    | . 47 |

|   |       | 6.3.3    | Embedded reset and power control block characteristics                           | . 48 |

|   |       | 6.3.4    | Embedded reference voltage                                                       | . 49 |

|   |       | 6.3.5    | Supply current characteristics                                                   | . 49 |

|   |       | 6.3.6    | Wakeup time from low-power mode                                                  | . 59 |

|   |       | 6.3.7    | External clock source characteristics                                            | . 59 |

|   |       | 6.3.8    | Internal clock source characteristics                                            | . 63 |

|   |       | 6.3.9    | PLL characteristics                                                              | . 66 |

|   |       | 6.3.10   | Memory characteristics                                                           | . 66 |

|   |       | 6.3.11   | EMC characteristics                                                              | . 67 |

|   |       | 6.3.12   | Electrical sensitivity characteristics                                           | . 68 |

|   |       | 6.3.13   | I/O current injection characteristics                                            | . 69 |

|   |       |          |                                                                                  |      |

# List of tables

| Table 1.  | Device summary                                                                                | 1  |

|-----------|-----------------------------------------------------------------------------------------------|----|

| Table 2.  | STM32F051xx family device features and peripheral count                                       | 11 |

| Table 3.  | Temperature sensor calibration values                                                         | 18 |

| Table 4.  | Internal voltage reference calibration values                                                 |    |

| Table 5.  | Capacitive sensing GPIOs available on STM32F051xx devices                                     | 20 |

| Table 6.  | Effective number of capacitive sensing channels on STM32F051xx                                | 20 |

| Table 7.  | Timer feature comparison                                                                      |    |

| Table 8.  | Comparison of I <sup>2</sup> C analog and digital filters                                     | 24 |

| Table 9.  | STM32F051xx I <sup>2</sup> C implementation                                                   | 24 |

| Table 10. | STM32F051xx USART implementation                                                              | 25 |

| Table 11. | STM32F051xx SPI/I <sup>2</sup> S implementation                                               | 26 |

| Table 12. | Legend/abbreviations used in the pinout table                                                 | 31 |

| Table 13. | Pin definitions                                                                               | 31 |

| Table 14. | Alternate functions selected through GPIOA_AFR registers for port A                           |    |

| Table 15. | Alternate functions selected through GPIOB_AFR registers for port B                           | 38 |

| Table 16. | STM32F051xx peripheral register boundary addresses                                            | 40 |

| Table 17. | Voltage characteristics                                                                       | 45 |

| Table 18. | Current characteristics                                                                       | 46 |

| Table 19. | Thermal characteristics                                                                       |    |

| Table 20. | General operating conditions                                                                  |    |

| Table 21. | Operating conditions at power-up / power-down                                                 | 48 |

| Table 22. | Embedded reset and power control block characteristics                                        | 48 |

| Table 23. | Programmable voltage detector characteristics                                                 | 48 |

| Table 24. | Embedded internal reference voltage                                                           | 49 |

| Table 25. | Typical and maximum current consumption from V <sub>DD</sub> at 3.6 V                         | 50 |

| Table 26. | Typical and maximum current consumption from the V <sub>DDA</sub> supply                      | 51 |

| Table 27. | Typical and maximum current consumption in Stop and Standby modes                             | 52 |

| Table 28. | Typical and maximum current consumption from the V <sub>BAT</sub> supply                      | 53 |

| Table 29. | Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal | 54 |

| Table 30. | Switching output I/O current consumption                                                      |    |

| Table 31. | Peripheral current consumption                                                                |    |

| Table 32. | Low-power mode wakeup timings                                                                 |    |

| Table 33. | High-speed external user clock characteristics                                                |    |

| Table 34. | Low-speed external user clock characteristics                                                 |    |

| Table 35. | HSE oscillator characteristics                                                                |    |

| Table 36. | LSE oscillator characteristics (f <sub>LSF</sub> = 32.768 kHz)                                | 62 |

| Table 37. | HSI oscillator characteristics                                                                | 64 |

| Table 38. | HSI14 oscillator characteristics                                                              | 65 |

| Table 39. | LSI oscillator characteristics                                                                | 66 |

| Table 40. | PLL characteristics                                                                           | 66 |

| Table 41. | Flash memory characteristics                                                                  | 66 |

| Table 42. | Flash memory endurance and data retention                                                     | 67 |

| Table 43. | EMS characteristics                                                                           |    |

| Table 44. | EMI characteristics                                                                           |    |

| Table 45. | ESD absolute maximum ratings                                                                  | 69 |

| Table 46. | Electrical sensitivities                                                                      | 69 |

| Table 47  | I/O current injection susceptibility                                                          | 70 |

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# 3.8 Direct memory access controller (DMA)

The 5-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

# 3.9 Interrupts and events

#### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex -M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 55 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature

# 3.18 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Up to two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

One standard I<sup>2</sup>S interface (multiplexed with SPI1) supporting four different audio standards can operate as master or slave at half-duplex communication mode. It can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, it can output a clock for an external audio component at 256 times the sampling frequency.

| Table 11. OTHIOZI COTAX OF IT O Implementation |      |      |  |  |  |

|------------------------------------------------|------|------|--|--|--|

| SPI features <sup>(1)</sup>                    | SPI1 | SPI2 |  |  |  |

| Hardware CRC calculation                       | Х    | Х    |  |  |  |

| Rx/Tx FIFO                                     | Х    | Х    |  |  |  |

| NSS pulse mode                                 | Х    | Х    |  |  |  |

| I <sup>2</sup> S mode                          | X    | -    |  |  |  |

| TI mode                                        | Х    | Х    |  |  |  |

Table 11. STM32F051xx SPI/I<sup>2</sup>S implementation

# 3.19 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.20 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

<sup>1.</sup> X = supported.

Table 13. Pin definitions (continued)

|        | P       | in n            | umbe    | er     |          | Table 13. Fill                       |          |               | •     | T .                                                               | nctions                                            |

|--------|---------|-----------------|---------|--------|----------|--------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|----------------------------------------------------|

| LQFP64 | UFBGA64 | LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                               | Additional<br>functions                            |

| 7      | E1      | 7               | D5      | 4      | 4        | NRST                                 | I/O      | RST           | -     | Device reset input / (active                                      |                                                    |

| 8      | E3      | -               | -       | -      | -        | PC0                                  | I/O      | TTa           | -     | EVENTOUT                                                          | ADC_IN10                                           |

| 9      | E2      | -               | -       | -      | -        | PC1                                  | I/O      | TTa           | -     | EVENTOUT                                                          | ADC_IN11                                           |

| 10     | F2      | -               | -       | -      | -        | PC2                                  | I/O      | TTa           | -     | EVENTOUT                                                          | ADC_IN12                                           |

| 11     | G1      | -               | -       | -      | -        | PC3                                  | I/O      | TTa           | -     | EVENTOUT                                                          | ADC_IN13                                           |

| 12     | F1      | 8               | D6      | 16     | 0        | VSSA                                 | S        | -             | (3)   | Analog                                                            | ground                                             |

| 13     | H1      | 9               | E5      | 5      | 5        | VDDA                                 | S        | -             | -     | Analog pov                                                        | wer supply                                         |

| 14     | G2      | 10              | F6      | 6      | 6        | PA0                                  | I/O      | ТТа           | -     | USART2_CTS,<br>TIM2_CH1_ETR,<br>COMP1_OUT,<br>TSC_G1_IO1          | ADC_IN0,<br>COMP1_INM6,<br>RTC_TAMP2,<br>WKUP1     |

| 15     | H2      | 11              | D4      | 7      | 7        | PA1                                  | I/O      | ТТа           | -     | USART2_RTS,<br>TIM2_CH2,<br>TSC_G1_IO2,<br>EVENTOUT               | ADC_IN1,<br>COMP1_INP                              |

| 16     | F3      | 12              | E4      | 8      | 8        | PA2                                  | I/O      | ТТа           | -     | USART2_TX,<br>TIM2_CH3,<br>TIM15_CH1,<br>COMP2_OUT,<br>TSC_G1_IO3 | ADC_IN2,<br>COMP2_INM6                             |

| 17     | G3      | 13              | F5      | 9      | 9        | PA3                                  | I/O      | TTa           | -     | USART2_RX,<br>TIM2_CH4,<br>TIM15_CH2,<br>TSC_G1_IO4               | ADC_IN3,<br>COMP2_INP                              |

| 18     | C2      | -               | -       | -      | -        | PF4                                  | I/O      | FT            | -     | EVENTOUT                                                          | -                                                  |

| 19     | D2      | -               | -       | -      | -        | PF5                                  | I/O      | FT            | -     | EVENTOUT                                                          | -                                                  |

| 20     | Н3      | 14              | С3      | 10     | 10       | PA4                                  | I/O      | ТТа           | -     | SPI1_NSS,<br>I2S1_WS,<br>USART2_CK,<br>TIM14_CH1,<br>TSC_G2_IO1   | ADC_IN4,<br>COMP1_INM4,<br>COMP2_INM4,<br>DAC_OUT1 |

| 21     | F4      | 15              | D3      | 11     | 11       | PA5                                  | I/O      | ТТа           | -     | SPI1_SCK,<br>I2S1_CK, CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2         | ADC_IN5,<br>COMP1_INM5,<br>COMP2_INM5              |

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 20. General operating conditions

| Symbol            | Parameter Conditions                                                                          |                                      | Min             | Max                                  | Unit  |  |

|-------------------|-----------------------------------------------------------------------------------------------|--------------------------------------|-----------------|--------------------------------------|-------|--|

| f <sub>HCLK</sub> | Internal AHB clock frequency                                                                  | -                                    | 0               | 48                                   | MHz   |  |

| f <sub>PCLK</sub> | Internal APB clock frequency                                                                  | -                                    | 0               | 48                                   | IVI⊓∠ |  |

| V <sub>DD</sub>   | Standard operating voltage                                                                    | -                                    | 2.0             | 3.6                                  | V     |  |

| V                 | Analog operating voltage (ADC and DAC not used)                                               | Must have a potential equal          | $V_{DD}$        | 3.6                                  | V     |  |

| $V_{DDA}$         | Analog operating voltage (ADC and DAC used)                                                   | to or higher than V <sub>DD</sub>    | 2.4             | 3.6                                  | V     |  |

| V <sub>BAT</sub>  | Backup operating voltage                                                                      | -                                    | 1.65            | 3.6                                  | V     |  |

|                   |                                                                                               | TC and RST I/O                       | -0.3            | V <sub>DDIOx</sub> +0.3              |       |  |

| <b>V</b>          | I/O input voltage                                                                             | TTa I/O                              | -0.3            | V <sub>DDA</sub> +0.3 <sup>(1)</sup> | V     |  |

| $V_{IN}$          |                                                                                               | FT and FTf I/O                       | -0.3            | 5.5 <sup>(1)</sup>                   |       |  |

|                   |                                                                                               | BOOT0                                | 0               | 5.5                                  |       |  |

|                   |                                                                                               | LQFP64                               | -               | 444                                  | mW    |  |

|                   |                                                                                               | LQFP48                               | -               | 364                                  |       |  |

|                   | Power dissipation at $T_A$ = 85 °C for suffix 6 or $T_A$ = 105 °C for suffix 7 <sup>(2)</sup> | LQFP32                               | -               | 357                                  |       |  |

| $P_{D}$           |                                                                                               | UFQFPN32                             | -               | 526                                  |       |  |

|                   |                                                                                               | UFQFPN48                             | -               | 625                                  |       |  |

|                   |                                                                                               | UFBGA64                              | -               | 308                                  |       |  |

|                   |                                                                                               | WLCSP36                              | -               | 333                                  |       |  |

|                   | Ambient temperature for the                                                                   | Maximum power dissipation            | <del>-4</del> 0 | 85                                   | °C    |  |

| TA                | suffix 6 version                                                                              | Low power dissipation <sup>(3)</sup> | -40             | 105                                  | C     |  |

| IA                | Ambient temperature for the                                                                   | Maximum power dissipation            | <b>–40</b>      | 105                                  | °C    |  |

|                   | suffix 7 version                                                                              | Low power dissipation <sup>(3)</sup> | -40             | 125                                  | 1     |  |

| TJ                | Junction temperature range                                                                    | Suffix 6 version                     | c 6 version –40 |                                      | °C    |  |

| IJ                | Junction temperature range                                                                    | Suffix 7 version                     | -40             | 125                                  | °C    |  |

|                   | •                                                                                             | •                                    |                 | •                                    |       |  |

<sup>1.</sup> For operation with a voltage higher than  $V_{DDIOx}$  + 0.3 V, the internal pull-up resistor must be disabled.

## 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 21* are derived from tests performed under the ambient temperature condition summarized in *Table 20*.

<sup>2.</sup> If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ . See Section 7.8: Thermal characteristics.

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.8: Thermal characteristics).

Table 29. Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal

| Symbol           | Parameter                       | £                 | Typical con<br>Run i | sumption in<br>mode     | Typical con<br>Sleep | Unit                 |       |

|------------------|---------------------------------|-------------------|----------------------|-------------------------|----------------------|----------------------|-------|

|                  | raiametei                       | f <sub>HCLK</sub> | Peripherals enabled  | Peripherals<br>disabled | Peripherals enabled  | Peripherals disabled | Oilit |

|                  |                                 | 48 MHz            | 23.2                 | 13.3                    | 13.2                 | 3.1                  |       |

|                  |                                 | 36 MHz            | 17.6                 | 10.3                    | 10.1                 | 2.6                  |       |

|                  |                                 | 32 MHz            | 15.6                 | 9.3                     | 9.0                  | 2.4                  |       |

|                  | Current                         | 24 MHz            | 12.1                 | 7.4                     | 7.0                  | 2.0                  |       |

|                  | consumption                     | 16 MHz            | 8.4                  | 5.1                     | 5.0                  | 1.6                  | mA    |

| I <sub>DD</sub>  | from V <sub>DD</sub><br>supply  | 8 MHz             | 4.5                  | 3.0                     | 2.8                  | 1.1                  | ША    |

|                  | supply                          | 4 MHz             | 2.8                  | 2.0                     | 2.0                  | 1.1                  |       |

|                  |                                 | 2 MHz             | 1.9                  | 1.5                     | 1.5                  | 1.0                  |       |

|                  |                                 | 1 MHz             | 1.5                  | 1.3                     | 1.3                  | 1.0                  |       |

|                  |                                 | 500 kHz           | 1.2                  | 1.2                     | 1.1                  | 1.0                  |       |

|                  |                                 | 48 MHz            |                      | 1                       | 51                   |                      |       |

|                  |                                 | 36 MHz            |                      | 1′                      | 13                   |                      |       |

|                  |                                 | 32 MHz            |                      | 10                      | 01                   |                      |       |

|                  | Current                         | 24 MHz            |                      | 7                       | 9                    |                      |       |

| l                | consumption                     | 16 MHz            |                      | 5                       | 7                    |                      | μA    |

| I <sub>DDA</sub> | from V <sub>DDA</sub><br>supply | 8 MHz             |                      | 2                       | .2                   |                      | μΛ    |

|                  | Supply                          | 4 MHz             |                      | 2                       | .2                   |                      |       |

|                  |                                 | 2 MHz             |                      | 2                       | .2                   |                      |       |

|                  |                                 | 1 MHz             |                      | 2                       | .2                   |                      |       |

|                  |                                 | 500 kHz           |                      | 2                       | .2                   |                      |       |

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 48: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 35*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                   | Conditions <sup>(1)</sup>                                                      | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------|--------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency        | -                                                                              | 4                  | 8   | 32                 | MHz  |

| R <sub>F</sub>                      | Feedback resistor           | -                                                                              | -                  | 200 | -                  | kΩ   |

|                                     |                             | During startup <sup>(3)</sup>                                                  | -                  | -   | 8.5                |      |

|                                     |                             | $V_{DD}$ = 3.3 V,<br>Rm = 30 $\Omega$ ,<br>CL = 10 pF@8 MHz                    | -                  | 0.4 | -                  |      |

|                                     |                             | $V_{DD} = 3.3 \text{ V},$ $Rm = 45 \Omega,$ $CL = 10 \text{ pF}@8 \text{ MHz}$ | - 0.5 -            |     | -                  |      |

| I <sub>DD</sub>                     | HSE current consumption     | $V_{DD}$ = 3.3 V,<br>Rm = 30 $\Omega$ ,<br>CL = 5 pF@32 MHz                    | -                  | 0.8 | -                  | mA   |

|                                     |                             | $V_{DD}$ = 3.3 V,<br>Rm = 30 $\Omega$ ,<br>CL = 10 pF@32 MHz                   | -                  | 1   | -                  |      |

|                                     |                             | $V_{DD}$ = 3.3 V,<br>Rm = 30 $\Omega$ ,<br>CL = 20 pF@32 MHz                   | -                  | 1.5 | -                  |      |

| 9 <sub>m</sub>                      | Oscillator transconductance | Startup                                                                        | 10                 | -   | -                  | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                | V <sub>DD</sub> is stabilized                                                  | -                  | 2   | -                  | ms   |

Table 35. HSE oscillator characteristics

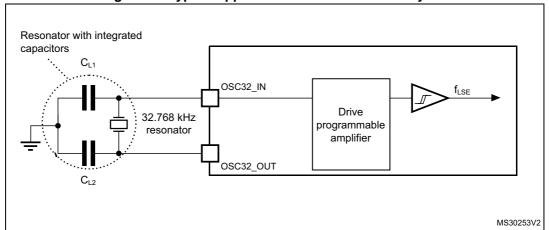

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 17*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

<sup>1.</sup> Resonator characteristics given by the crystal/ceramic resonator manufacturer.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> This consumption level occurs during the first 2/3 of the  $t_{\text{SU(HSE)}}$  startup time

<sup>4.</sup> t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 18. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.8 Internal clock source characteristics

The parameters given in *Table 37* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*. The provided curves are characterization results, not tested in production.

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|

| N <sub>END</sub> | Endurance      | $T_A = -40 \text{ to } +105 ^{\circ}\text{C}$      | 10                 | kcycle |  |

|                  | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |

| t <sub>RET</sub> |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |

Table 42. Flash memory endurance and data retention

#### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 43*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                   | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}$ = 3.3 V, LQFP64, $T_{A}$ = +25 °C, $f_{HCLK}$ = 48 MHz, conforming to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP64, $T_A$ = +25°C, $f_{HCLK}$ = 48 MHz, conforming to IEC 61000-4-4    | 4B              |

Table 43. EMS characteristics

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

<sup>1.</sup> Data based on characterization results, not tested in production.

<sup>2.</sup> Cycling performed over the whole temperature range.

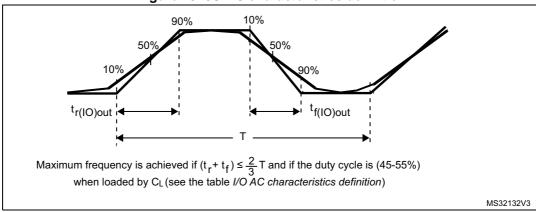

Figure 23. I/O AC characteristics definition

## 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $R_{\text{PU}}$ .

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

| Symbol                 | Parameter                                       | Conditions                        | Min                                         | Тур | Max                                      | Unit |  |  |

|------------------------|-------------------------------------------------|-----------------------------------|---------------------------------------------|-----|------------------------------------------|------|--|--|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                    | -                                 | -                                           | -   | 0.3 V <sub>DD</sub> +0.07 <sup>(1)</sup> | V    |  |  |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                   | -                                 | 0.445 V <sub>DD</sub> +0.398 <sup>(1)</sup> | -   | -                                        | , v  |  |  |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis         | -                                 | -                                           | 200 | -                                        | mV   |  |  |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                          | 40  | 55                                       | kΩ   |  |  |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                                           | -   | 100 <sup>(1)</sup>                       | ns   |  |  |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                   | 2.7 < V <sub>DD</sub> < 3.6       | 300 <sup>(3)</sup>                          | -   | -                                        | ns   |  |  |

|                        | TWIST Input not intered pulse                   | 2.0 < V <sub>DD</sub> < 3.6       | 500 <sup>(3)</sup>                          | -   | -                                        | 115  |  |  |

Table 51. NRST pin characteristics

<sup>1.</sup> Data based on design simulation only. Not tested in production.

<sup>2.</sup> The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

<sup>3.</sup> Data based on design simulation only. Not tested in production.

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |

|-------------------|--------------|--------------------------------|--------------------------------|------|

| /4                | 0            | 0.1                            | 409.6                          |      |

| /8                | 1            | 0.2                            | 819.2                          |      |

| /16               | 2            | 0.4                            | 1638.4                         |      |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |

| /64               | 4            | 1.6                            | 6553.6                         |      |

| /128              | 5            | 3.2                            | 13107.2                        |      |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |

Table 60. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Table 01: WWD0 IIIII/IIIax tillicoat Valde at 40 IIII 2 (1 0217) |       |                   |                   |      |  |

|------------------------------------------------------------------|-------|-------------------|-------------------|------|--|

| Prescaler                                                        | WDGTB | Min timeout value | Max timeout value | Unit |  |

| 1                                                                | 0     | 0.0853            | 5.4613            |      |  |

| 2                                                                | 1     | 0.1706            | 10.9226           | me   |  |

| 4                                                                | 2     | 0.3413            | 21.8453           | ms   |  |

| 8                                                                | 3     | 0.6826            | 43.6906           |      |  |

Table 61. WWDG min/max timeout value at 48 MHz (PCLK)

#### 6.3.22 Communication interfaces

## I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{\rm DDIOX}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

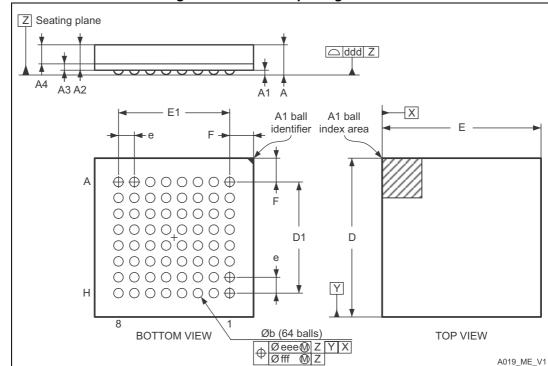

# 7.1 UFBGA64 package information

UFBGA64 is a 64-ball, 5 x 5 mm, 0.5 mm pitch ultra-fine-profile ball grid array package.

Figure 34. UFBGA64 package outline

1. Drawing is not to scale.

Table 65. UFBGA64 package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |

| A1     | 0.050       | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |

| A2     | 0.400       | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |

| A3     | 0.080       | 0.130 | 0.180 | 0.0031                | 0.0051 | 0.0071 |

| A4     | 0.270       | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |

Table 68. LQFP48 package mechanical data

| 0      | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| Α      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 41. Recommended footprint for LQFP48 package 9.70 ai14911d

1. Dimensions are expressed in millimeters.

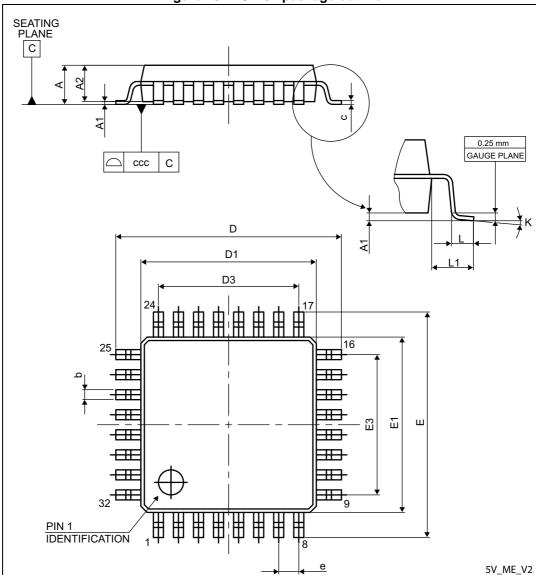

# 7.6 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

Figure 49. LQFP32 package outline

1. Drawing is not to scale.

### 7.8 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 20: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O}$$

max =  $\Sigma (V_{OL} \times I_{OL}) + \Sigma ((V_{DDIOx} - V_{OH}) \times I_{OH})$ ,

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                 | Value | Unit |

|---------------|---------------------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |

|               | Thermal resistance junction-ambient LQFP48 - 7 × 7 mm                     | 55    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient LQFP32 - 7 × 7 mm                     | 56    |      |

|               | Thermal resistance junction-ambient UFBGA64 - 5 × 5 mm                    | 65    | °C/W |

|               | Thermal resistance junction-ambient UFQFPN48 - 7 × 7 mm                   | 32    |      |

|               | Thermal resistance junction-ambient UFQFPN32 - 5 × 5 mm                   | 38    |      |

|               | Thermal resistance junction-ambient WLCSP36 - 2.6 × 2.7 mm                | 60    |      |

Table 74. Package thermal characteristics

#### 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

## 7.8.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F051xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 8 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

$P_{INTmax} = 50 \text{ mA} \times 3.5 \text{ V} = 175 \text{ mW}$

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} + 8 \times 20 \text{ mA} \times 1.3 \text{ V} = 272 \text{ mW}$

This gives: P<sub>INTmax</sub> = 175 mW and P<sub>IOmax</sub> = 272 mW:

$P_{Dmax} = 175 + 272 = 447 \text{ mW}$

Using the values obtained in *Table 74*  $T_{Jmax}$  is calculated as follows:

For LQFP64, 45 °C/W

$T_{\text{lmax}}$  = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.115 °C = 102.115 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C) see *Table 20: General operating conditions*.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Section 8: Ordering information).

Note:

With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

```

Suffix 6: T_{Amax} = T_{Jmax} - (45^{\circ}\text{C/W} \times 447 \text{ mW}) = 105\text{-}20.115 = 84.885 ^{\circ}\text{C}

Suffix 7: T_{Amax} = T_{Jmax} - (45^{\circ}\text{C/W} \times 447 \text{ mW}) = 125\text{-}20.115 = 104.885 ^{\circ}\text{C}

```

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 100 °C (measured according to JESD51-2),  $I_{DDmax}$  = 20 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V

$P_{INTmax}$  = 20 mA × 3.5 V= 70 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :

$P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus:  $P_{Dmax} = 134 \text{ mW}$

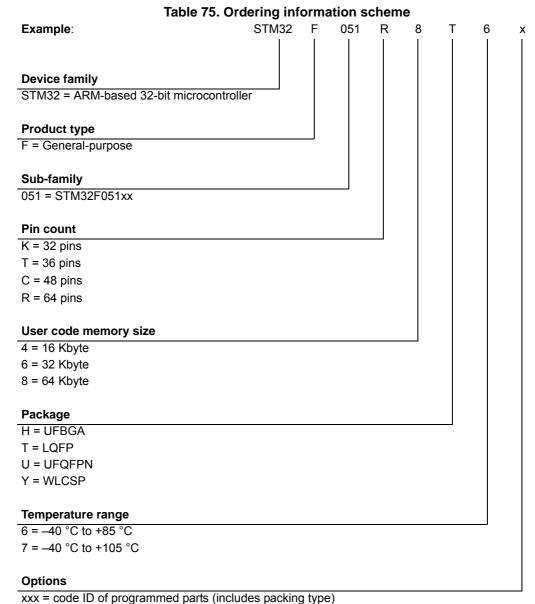

#### **Ordering information** 8

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

TR = tape and reel packing

blank = tray packing

Table 76. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date        | Kevision |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 28-Aug-2015 | 5        | Updated the following:  DAC and power management feature descriptions in Features  Table 2: STM32F051xx family device features and peripheral count  Section 3.5.1: Power supply schemes  Figure 13: Power supply scheme  Table 17: Voltage characteristics  Table 20: General operating conditions: updated the footnote for V <sub>IN</sub> parameter  Table 28: Typical and maximum current consumption from the V <sub>BAT</sub> supply  Table 52: ADC characteristics  Table 33: High-speed external user clock characteristics: replaced V <sub>DD</sub> with V <sub>DDIOX</sub> Table 34: Low-speed external user clock characteristics: replaced V <sub>DD</sub> with V <sub>DDIOX</sub> Table 37: HSI oscillator characteristics and Figure 19: HSI oscillator accuracy characterization results for soldered parts  Table 38: HSI14 oscillator characteristics: changed the min value for ACC <sub>HSI14</sub> Table 41: Flash memory characteristics: changed the values for t <sub>ME</sub> and I <sub>DD</sub> in write mode  Table 43: EMS characteristics: changed the value of V <sub>EFTB</sub> Table 45: ESD absolute maximum ratings  Figure 10: STM32F051x8 memory map  Figure 21: TC and TTa I/O input characteristics  Figure 22: Five volt tolerant (FT and FTf) I/O input characteristics  Figure 23: I/O AC characteristics definition  tstart definition in Table 24: Embedded internal reference voltage  tstart definition in Table 24: Embedded internal reference voltage  tstart definition in Table 52: ADC characteristics  Table 56: Comparator characteristics: changed the description and values for V <sub>SC</sub> , V <sub>DDA</sub> and V <sub>REFINT</sub> scaler startup time from power down  Table 57: TS characteristics: changed the min value for T <sub>S-vbat</sub> and the typical value for R parameters  Section 6.3.22: Communication interfaces: updated the description and features in the subsection I <sup>2</sup> C interface characteristics:  Table 64: FS characteristics: updated the min values for data input hold time (master and slave receiver) |  |  |