Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |  |

|----------------------------|-------------------------------------------------------------------------|--|

| Product Status             | Active                                                                  |  |

| Core Processor             | ARM® Cortex®-M0                                                         |  |

| Core Size                  | 32-Bit Single-Core                                                      |  |

| Speed                      | 48MHz                                                                   |  |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |  |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |  |

| Number of I/O              | 55                                                                      |  |

| Program Memory Size        | 32KB (32K x 8)                                                          |  |

| Program Memory Type        | FLASH                                                                   |  |

| EEPROM Size                | -                                                                       |  |

| RAM Size                   | 8K x 8                                                                  |  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |  |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                   |  |

| Oscillator Type            | Internal                                                                |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |  |

| Mounting Type              | Surface Mount                                                           |  |

| Package / Case             | 64-LQFP                                                                 |  |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051r6t7tr |  |

## List of tables

| Table 48. | I/O static characteristics                         | 70  |

|-----------|----------------------------------------------------|-----|

| Table 49. | Output voltage characteristics                     | 73  |

| Table 50. | I/O AC characteristics                             | 74  |

| Table 51. | NRST pin characteristics                           | 75  |

| Table 52. | ADC characteristics                                | 76  |

| Table 53. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz | 77  |

| Table 54. | ADC accuracy                                       | 78  |

| Table 55. | DAC characteristics                                | 80  |

| Table 56. | Comparator characteristics                         | 82  |

| Table 57. | TS characteristics                                 | 84  |

| Table 58. | V <sub>BAT</sub> monitoring characteristics        | 84  |

| Table 59. | TIMx characteristics                               | 84  |

| Table 60. | IWDG min/max timeout period at 40 kHz (LSI)        | 85  |

| Table 61. | WWDG min/max timeout value at 48 MHz (PCLK)        | 85  |

| Table 62. | I <sup>2</sup> C analog filter characteristics     | 86  |

| Table 63. | SPI characteristics                                | 86  |

| Table 64. | I <sup>2</sup> S characteristics                   | 88  |

| Table 65. | UFBGA64 package mechanical data                    | 91  |

| Table 66. | UFBGA64 recommended PCB design rules               | 92  |

| Table 67. | LQFP64 package mechanical data                     | 94  |

| Table 68. | LQFP48 package mechanical data                     | 98  |

| Table 69. | UFQFPN48 package mechanical data                   | 101 |

| Table 70. | WLCSP36 package mechanical data                    | 103 |

| Table 71. | WLCSP36 recommended PCB design rules               | 104 |

| Table 72. | LQFP32 package mechanical data                     | 107 |

| Table 73. | UFQFPN32 package mechanical data                   | 110 |

| Table 74. | Package thermal characteristics                    | 112 |

| Table 75. | Ordering information scheme                        | 115 |

| Table 76. | Document revision history                          | 116 |

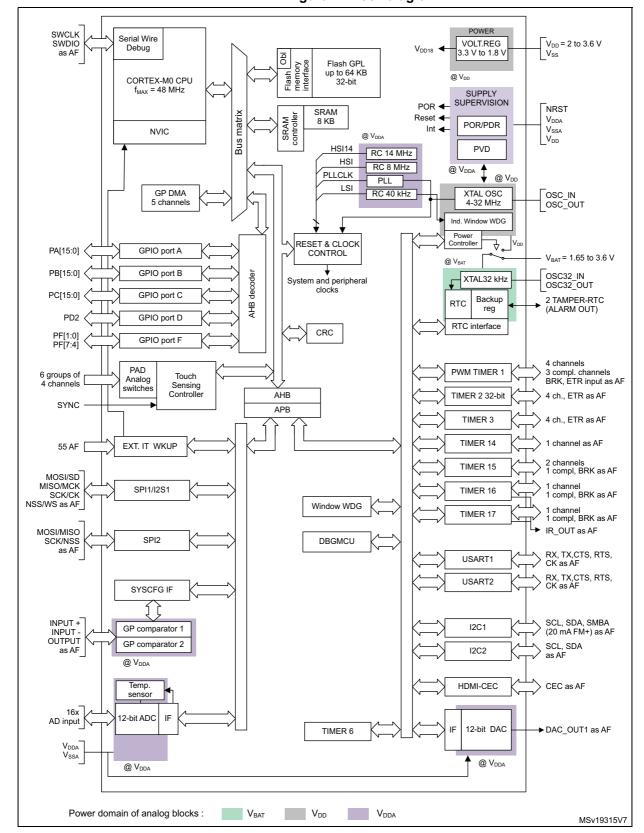

Figure 1. Block diagram

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

## 3.8 Direct memory access controller (DMA)

The 5-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

## 3.9 Interrupts and events

### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex -M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 55 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature

can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

## 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

## 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, or at wake up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop and Standby mode capability

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- two anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s) and Fast mode (up to 400 kbit/s) and, I2C1 also supports Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

Table 8. Comparison of I<sup>2</sup>C analog and digital filters

| Aspect                           | Analog filter                                         | Digital filter                                                                                       |

|----------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15 I2Cx peripheral clocks                                              |

| Benefits                         | Available in Stop mode                                | <ul><li>Extra filtering capability vs.</li><li>standard requirements</li><li>Stable length</li></ul> |

| Drawbacks                        | Variations depending on temperature, voltage, process | Wakeup from Stop on address match is not available when digital filter is enabled.                   |

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripherals can be served by the DMA controller.

Refer to Table 9 for the differences between I2C1 and I2C2.

Table 9. STM32F051xx I<sup>2</sup>C implementation

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 | I2C2 |

|--------------------------------------------------------------|------|------|

| 7-bit addressing mode                                        | Х    | Х    |

| 10-bit addressing mode                                       | Х    | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х    |

| Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive I/Os | Х    | -    |

| Independent clock                                            | Х    | -    |

# 4 Pinouts and pin descriptions

Top view VBAT [ 48 🗆 PF7 47 PF6 PC13 □ PC14-OSC32\_IN [ 46 🗆 PA13 45 PA12 PC15-OSC32\_OUT PF0-OSC\_IN [ 44 🗀 PA11 PF1-OSC\_OUT 6 43 PA10 NRST 🗆 7 42 🗖 PA9 PC0 🗆 8 41 PA8 LQFP64 PC1 □ 40 PC9 PC2 🗆 10 39 D PC8 PC3 🗆 11 38 🗆 PC7 37 D PC6 VSSA 🗆 12 VDDA 🗆 36 🗆 PB15 PA0 🗆 14 35 PB14 PA1 🗆 15 34 🗆 PB13 PA2 □ 16 33 D PB12 17 18 19 20 20 22 23 24 25 25 26 26 27 30 30 30 33 MSv19843V2

Figure 3. LQFP64 package pinout

Table 13. Pin definitions (continued)

|        | P       | in n            | umbe    | er     |          | Table 13. Pin                        |          |               |       | 1                                                                 | nctions                 |

|--------|---------|-----------------|---------|--------|----------|--------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|-------------------------|

| LQFP64 | UFBGA64 | LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                               | Additional<br>functions |

| 33     | Н8      | 25              | -       | -      | -        | PB12                                 | I/O      | FT            | (5)   | SPI2_NSS,<br>TIM1_BKIN,<br>TSC_G6_IO2,<br>EVENTOUT                | -                       |

| 34     | G8      | 26              | -       | -      | -        | PB13                                 | I/O      | FT            | (5)   | SPI2_SCK,<br>TIM1_CH1N,<br>TSC_G6_IO3                             | -                       |

| 35     | F8      | 27              | -       | -      | -        | PB14                                 | I/O      | FT            | (5)   | SPI2_MISO,<br>TIM1_CH2N,<br>TIM15_CH1,<br>TSC_G6_IO4              | -                       |

| 36     | F7      | 28              | -       | -      | -        | PB15                                 | I/O      | FT            | (5)   | SPI2_MOSI,<br>TIM1_CH3N,<br>TIM15_CH1N,<br>TIM15_CH2              | RTC_REFIN               |

| 37     | F6      | -               | -       | -      | -        | PC6                                  | I/O      | FT            | -     | TIM3_CH1                                                          | -                       |

| 38     | E7      | -               | -       | -      | -        | PC7                                  | I/O      | FT            | -     | TIM3_CH2                                                          | -                       |

| 39     | E8      | -               | -       | -      | -        | PC8                                  | I/O      | FT            | -     | TIM3_CH3                                                          | -                       |

| 40     | D8      | -               | -       | -      | -        | PC9                                  | I/O      | FT            | -     | TIM3_CH4                                                          | -                       |

| 41     | D7      | 29              | E2      | 18     | 18       | PA8                                  | I/O      | FT            | -     | USART1_CK,<br>TIM1_CH1,<br>EVENTOUT,<br>MCO                       | -                       |

| 42     | C7      | 30              | D1      | 19     | 19       | PA9                                  | I/O      | FT            | -     | USART1_TX,<br>TIM1_CH2,<br>TIM15_BKIN,<br>TSC_G4_IO1              | -                       |

| 43     | C6      | 31              | C1      | 20     | 20       | PA10                                 | I/O      | FT            | -     | USART1_RX,<br>TIM1_CH3,<br>TIM17_BKIN,<br>TSC_G4_IO2              | -                       |

| 44     | C8      | 32              | C2      | 21     | 21       | PA11                                 | I/O      | FT            | -     | USART1_CTS,<br>TIM1_CH4,<br>COMP1_OUT,<br>TSC_G4_IO3,<br>EVENTOUT | -                       |

44/122

## 6.1.7 Current consumption measurement

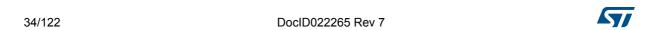

Figure 14. Current consumption measurement scheme

DocID022265 Rev 7

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 25* to *Table 31* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

Table 25. Typical and maximum current consumption from  $V_{DD}$  at 3.6  $V_{DD}$

|                 |                                   |                       |                   | All peripherals enabled |                                     |       |                     | All peripherals disabled |                                     |       |                     |      |

|-----------------|-----------------------------------|-----------------------|-------------------|-------------------------|-------------------------------------|-------|---------------------|--------------------------|-------------------------------------|-------|---------------------|------|

| Symbol          | Parameter                         | Conditions            | f <sub>HCLK</sub> |                         | Max @ T <sub>A</sub> <sup>(1)</sup> |       |                     | <b>T</b>                 | Max @ T <sub>A</sub> <sup>(1)</sup> |       |                     | Unit |

|                 |                                   |                       |                   | Тур                     | 25 °C                               | 85 °C | 105 °C              | Тур                      | 25 °C                               | 85 °C | 105 °C              |      |

|                 |                                   | HSE                   | 48 MHz            | 22.0                    | 22.8                                | 22.8  | 23.8                | 11.8                     | 12.7                                | 12.7  | 13.3                |      |

|                 |                                   | bypass,               | 32 MHz            | 15.0                    | 15.5                                | 15.5  | 16.0                | 7.6                      | 8.7                                 | 8.7   | 9.0                 |      |

|                 | Cupply                            | PLL on                | 24 MHz            | 12.2                    | 13.2                                | 13.2  | 13.6                | 7.2                      | 7.9                                 | 7.9   | 8.1                 |      |

|                 | Supply current in                 | HSE                   | 8 MHz             | 4.4                     | 5.2                                 | 5.2   | 5.4                 | 2.7                      | 2.9                                 | 2.9   | 3.0                 |      |

|                 | Run mode,<br>code                 | bypass,<br>PLL off    | 1 MHz             | 1.0                     | 1.3                                 | 1.3   | 1.4                 | 0.7                      | 0.9                                 | 0.9   | 0.9                 |      |

|                 | executing<br>from Flash<br>memory | Flash HSI clock,      | 48 MHz            | 22.0                    | 22.8                                | 22.8  | 23.8                | 11.8                     | 12.7                                | 12.7  | 13.3                |      |

|                 |                                   |                       | 32 MHz            | 15.0                    | 15.5                                | 15.5  | 16.0                | 7.6                      | 8.7                                 | 8.7   | 9.0                 |      |

|                 |                                   |                       | 24 MHz            | 12.2                    | 13.2                                | 13.2  | 13.6                | 7.2                      | 7.9                                 | 7.9   | 8.1                 |      |

|                 |                                   | HSI clock,<br>PLL off | 8 MHz             | 4.4                     | 5.2                                 | 5.2   | 5.4                 | 2.7                      | 2.9                                 | 2.9   | 3.0                 | A    |

| I <sub>DD</sub> |                                   | HSE                   | 48 MHz            | 22.2                    | 23.2 <sup>(2)</sup>                 | 23.2  | 24.4 <sup>(2)</sup> | 12.0                     | 12.7 <sup>(2)</sup>                 | 12.7  | 13.3 <sup>(2)</sup> | mA   |

|                 |                                   | bypass,               | 32 MHz            | 15.4                    | 16.3                                | 16.3  | 16.8                | 7.8                      | 8.7                                 | 8.7   | 9.0                 |      |

|                 |                                   | PLL on                | 24 MHz            | 11.2                    | 12.2                                | 12.2  | 12.8                | 6.2                      | 7.9                                 | 7.9   | 8.1                 |      |

|                 | Supply current in                 | HSE                   | 8 MHz             | 4.0                     | 4.5                                 | 4.5   | 4.7                 | 1.9                      | 2.9                                 | 2.9   | 3.0                 |      |

|                 | Run mode,                         | bypass,<br>PLL off    | 1 MHz             | 0.6                     | 0.8                                 | 0.8   | 0.9                 | 0.3                      | 0.6                                 | 0.6   | 0.7                 |      |

|                 | code<br>executing                 |                       | 48 MHz            | 22.2                    | 23.2                                | 23.2  | 24.4                | 12.0                     | 12.7                                | 12.7  | 13.3                |      |

|                 | from RAM                          | HSI clock,<br>PLL on  | 32 MHz            | 15.4                    | 16.3                                | 16.3  | 16.8                | 7.8                      | 8.7                                 | 8.7   | 9.0                 |      |

|                 |                                   |                       | 24 MHz            | 11.2                    | 12.2                                | 12.2  | 12.8                | 6.2                      | 7.9                                 | 7.9   | 8.1                 |      |

|                 |                                   | HSI clock,<br>PLL off | 8 MHz             | 4.0                     | 4.5                                 | 4.5   | 4.7                 | 1.9                      | 2.9                                 | 2.9   | 3.0                 |      |

#### 6.3.6 Wakeup time from low-power mode

The wakeup times given in Table 32 are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

| Symbol                 | Parameter                   | Conditions                  | Typ @Vdd = Vdda |         |         |       |         |     | Unit |

|------------------------|-----------------------------|-----------------------------|-----------------|---------|---------|-------|---------|-----|------|

| Symbol                 | Farameter                   |                             | = 2.0 V         | = 2.4 V | = 2.7 V | = 3 V | = 3.3 V | Max | Oill |

| 4                      | Wakeup from Stop<br>mode    | Regulator in run mode       | 3.2             | 3.1     | 2.9     | 2.9   | 2.8     | 5   |      |

| twustop                |                             | Regulator in low power mode | 7.0             | 5.8     | 5.2     | 4.9   | 4.6     | 9   |      |

| t <sub>WUSTANDBY</sub> | Wakeup from<br>Standby mode | -                           | 60.4            | 55.6    | 53.5    | 52    | 51      | -   | μs   |

| t <sub>WUSLEEP</sub>   | Wakeup from Sleep mode      | -                           |                 | 4 S\    | SCLK cy | cles  |         | -   |      |

Table 32. Low-power mode wakeup timings

#### 6.3.7 **External clock source characteristics**

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in Figure 15: High-speed external clock source AC timing diagram.

Table 33. High-speed external user clock characteristics

| Symbol                                     | Parameter(1)                           | Min                    | Тур | Max                    | Unit |

|--------------------------------------------|----------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                       | User external clock source frequency   | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage    | 0.7 V <sub>DDIOx</sub> | -   | $V_{DDIOx}$            | V    |

| V <sub>HSEL</sub>                          | SEL OSC_IN input pin low level voltage |                        | -   | 0.3 V <sub>DDIOx</sub> |      |

| $t_{w(\text{HSEH})} \ t_{w(\text{HSEL})}$  | OSC_IN high or low time                | 15                     | 1   | 1                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time               | -                      | -   | 20                     | 113  |

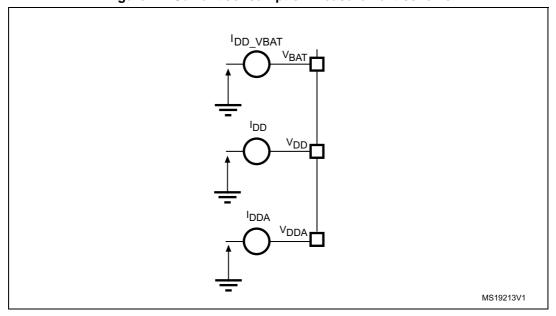

## High-speed internal 14 MHz (HSI14) RC oscillator (dedicated to ADC)

Table 38. HSI14 oscillator characteristics<sup>(1)</sup>

| Symbol                  | Parameter                                             | Conditions                                   | Min                 | Тур | Max                | Unit |

|-------------------------|-------------------------------------------------------|----------------------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI14</sub>      | Frequency                                             | -                                            | -                   | 14  | -                  | MHz  |

| TRIM                    | HSI14 user-trimming step                              | -                                            | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI14)</sub> | Duty cycle                                            | -                                            | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

|                         | Accuracy of the HSI14 oscillator (factory calibrated) | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$ | -4.2 <sup>(3)</sup> | -   | 5.1 <sup>(3)</sup> | %    |

| ۸۵۵                     |                                                       | $T_A = -10 \text{ to } 85 ^{\circ}\text{C}$  | $-3.2^{(3)}$        | -   | 3.1 <sup>(3)</sup> | %    |

| ACC <sub>HSI14</sub>    |                                                       | T <sub>A</sub> = 0 to 70 °C                  | -2.5 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |

|                         |                                                       | T <sub>A</sub> = 25 °C                       | -1                  | -   | 1                  | %    |

| t <sub>su(HSI14)</sub>  | HSI14 oscillator startup time                         | -                                            | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI14)</sub> | HSI14 oscillator power consumption                    | -                                            | -                   | 100 | 150 <sup>(2)</sup> | μΑ   |

- 1.  $V_{DDA}$  = 3.3 V,  $T_{A}$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

Figure 20. HSI14 oscillator accuracy characterization results

## Low-speed internal (LSI) RC oscillator

Table 39. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

<sup>1.</sup>  $V_{DDA}$  = 3.3 V,  $T_{A}$  = -40 to 105 °C unless otherwise specified.

### 6.3.9 PLL characteristics

The parameters given in *Table 40* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

Table 40. PLL characteristics

| Symbol                | Parameter                      |                   | Unit |                    |       |

|-----------------------|--------------------------------|-------------------|------|--------------------|-------|

|                       | Farameter                      | Min               | Тур  | Max                | Offic |

| ť                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0  | 24 <sup>(2)</sup>  | MHz   |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %     |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 48                 | MHz   |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs    |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps    |

Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL OUT</sub>.

## 6.3.10 Memory characteristics

### Flash memory

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

Table 41. Flash memory characteristics

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

|                    | Supply current          | Write mode                       | -   | -    | 10                 | mA   |

| I <sub>DD</sub>    |                         | Erase mode                       | -   | -    | 12                 | mA   |

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

**Functional** susceptibility **Symbol Description** Unit **Positive** Negative injection injection Injected current on BOOT0 -0 NA Injected current on PA10, PA12, PB4, PB5, PB10, PB15 and PD2 pins with induced leakage current on adjacent pins less -5 NA than -10 µA mΑ  $I_{INJ}$ Injected current on all other FT and FTf pins -5 NA Injected current on PA6 and PC0 -0 +5 Injected current on all other TTa, TC and RST pins -5 +5

Table 47. I/O current injection susceptibility

## 6.3.14 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the conditions summarized in *Table 20: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol          | Parameter                     | Conditions                   | Min                                            | Тур                | Max                                          | Unit |  |

|-----------------|-------------------------------|------------------------------|------------------------------------------------|--------------------|----------------------------------------------|------|--|

| V <sub>IL</sub> | Low level input voltage       | TC and TTa I/O               | -                                              | -                  | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup>  |      |  |

|                 |                               | FT and FTf I/O               | -                                              | -                  | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |      |  |

|                 |                               | воото                        | -                                              | -                  | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   | V    |  |

|                 |                               | All I/Os except<br>BOOT0 pin | -                                              | -                  | 0.3 V <sub>DDIOx</sub>                       |      |  |

| V <sub>IH</sub> | High level input voltage      | TC and TTa I/O               | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                  | -                                            |      |  |

|                 |                               | FT and FTf I/O               | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                  | -                                            |      |  |

|                 |                               | воото                        | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                  | -                                            | V    |  |

|                 |                               | All I/Os except<br>BOOT0 pin | 0.7 V <sub>DDIOx</sub>                         | -                  | -                                            |      |  |

| Vhvo            | Schmitt trigger<br>hysteresis | TC and TTa I/O               | -                                              | 200 <sup>(1)</sup> | -                                            |      |  |

|                 |                               | FT and FTf I/O               | -                                              | 100 <sup>(1)</sup> | -                                            | mV   |  |

|                 |                               | воото                        | -                                              | 300 <sup>(1)</sup> | -                                            |      |  |

Table 48. I/O static characteristics

Symbol Unit **Parameter Conditions** Min Тур Max TC, FT and FTf I/O TTa in digital mode ± 0.1  $V_{SS} \le V_{IN} \le V_{DDIOx}$ TTa in digital mode 1 Input leakage  $V_{\text{DDIO}X} \le V_{\text{IN}} \le V_{\text{DDA}}$  $I_{lkg}$ μΑ current(2) TTa in analog mode ± 0.2  $V_{SS} \le V_{IN} \le V_{DDA}$ FT and FTf I/O 10  $V_{DDIOx} \le V_{IN} \le 5 V$ Weak pull-up  $R_{PU}$ equivalent resistor  $V_{IN} = V_{SS}$ 25 40 55 kΩ Weak pull-down  $V_{IN} = -V_{DDIOx}$  $R_{PD}$ equivalent 25 40 55 kΩ resistor(3)

Table 48. I/O static characteristics (continued)

I/O pin capacitance

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 21* for standard I/Os, and in *Figure 22* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

5

$C_{IO}$

рF

<sup>1.</sup> Data based on design simulation only. Not tested in production.

The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 47: I/O current injection susceptibility.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

## 6.3.18 Comparator characteristics

**Table 56. Comparator characteristics**

| Symbol                   | Parameter                                                     | Conditions                                                        |                          | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit  |

|--------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|--------------------|-----|--------------------|-------|

| $V_{DDA}$                | Analog supply voltage                                         | -                                                                 |                          | $V_{DD}$           | -   | 3.6                | V     |

| V <sub>IN</sub>          | Comparator input voltage range                                | -                                                                 |                          | 0                  | -   | $V_{DDA}$          | -     |

| V <sub>SC</sub>          | V <sub>REFINT</sub> scaler offset voltage                     | -                                                                 |                          | -                  | ±5  | ±10                | mV    |

| t <sub>S_SC</sub>        | V <sub>REFINT</sub> scaler startup<br>time from power down    | First V <sub>REFINT</sub> scaler activation after device power on |                          | -                  | -   | 1000<br>(2)        | ms    |

|                          | time from power down                                          | Next activations                                                  |                          | -                  | -   | 0.2                |       |

| t <sub>START</sub>       | Comparator startup time                                       | Startup time to reach prospecification                            | ppagation delay          | -                  | -   | 60                 | μs    |

|                          |                                                               | Ultra-low power mode                                              |                          | -                  | 2   | 4.5                | μs    |

|                          | Propagation delay for<br>200 mV step with<br>100 mV overdrive | Low power mode                                                    |                          | -                  | 0.7 | 1.5                |       |

|                          |                                                               | Medium power mode                                                 |                          | -                  | 0.3 | 0.6                |       |

|                          |                                                               | High speed mode                                                   | V <sub>DDA</sub> ≥ 2.7 V | -                  | 50  | 100                | - ns  |

| +                        |                                                               |                                                                   | V <sub>DDA</sub> < 2.7 V | -                  | 100 | 240                |       |

| $t_D$                    |                                                               | Ultra-low power mode                                              |                          | -                  | 2   | 7                  |       |

|                          | Propagation delay for                                         | Low power mode                                                    |                          | -                  | 0.7 | 2.1                | μs    |

|                          | full range step with<br>100 mV overdrive                      | Medium power mode                                                 |                          | -                  | 0.3 | 1.2                |       |

|                          |                                                               | High aroud made                                                   | V <sub>DDA</sub> ≥ 2.7 V | -                  | 90  | 180                | ns    |

|                          |                                                               | High speed mode                                                   | V <sub>DDA</sub> < 2.7 V | -                  | 110 | 300                | 115   |

| V <sub>offset</sub>      | Comparator offset error                                       | -                                                                 |                          | -                  | ±4  | ±10                | mV    |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                          | -                                                                 |                          | -                  | 18  | -                  | μV/°C |

|                          |                                                               | Ultra-low power mode                                              |                          | -                  | 1.2 | 1.5                | μΑ    |

| l                        | COMP current                                                  | Low power mode                                                    |                          | -                  | 3   | 5                  |       |

| I <sub>DD(COMP)</sub>    | consumption                                                   | Medium power mode                                                 |                          | -                  | 10  | 15                 |       |

|                          |                                                               | High speed mode                                                   |                          | -                  | 75  | 100                |       |

Table 56. Comparator characteristics (continued)

| Symbol           | Parameter             | Condition                                | ons                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|------------------|-----------------------|------------------------------------------|-----------------------|--------------------|-----|--------------------|------|

|                  | Comparator hysteresis | No hysteresis (COMPxHYST[1:0]=00)        | -                     | -                  | 0   | -                  |      |

|                  |                       | Low hysteresis<br>(COMPxHYST[1:0]=01)    | High speed mode       | 3                  | 8   | 13                 |      |

|                  |                       |                                          | All other power modes | 5                  |     | 10                 |      |

| V <sub>hys</sub> |                       | Medium hysteresis<br>(COMPxHYST[1:0]=10) | High speed mode       | 7                  | 15  | 26                 | mV   |

|                  |                       |                                          | All other power modes | 9                  |     | 19                 |      |

|                  |                       | High hysteresis<br>(COMPxHYST[1:0]=11)   | High speed mode       | 18                 | 31  | 49                 |      |

|                  |                       |                                          | All other power modes | 19                 |     | 40                 |      |

- 1. Data based on characterization results, not tested in production.

- 2. For more details and conditions see Figure 28: Maximum V<sub>REFINT</sub> scaler startup time from power down.

Figure 28. Maximum  $V_{\mbox{\scriptsize REFINT}}$  scaler startup time from power down  $2.0V \le V_{DDA} < 2.4V$ 1000  $2.4 \text{V} \leq \text{V}_{\text{DDA}} < 3.0 \text{V}$ 3.0V ≤ V<sub>DDA</sub> < 3.6V 100 ts\_SC(max) (ms) 10 1 -40 -20 0 20 40 60 80 100 Temperature (°C)

fff

inches<sup>(1)</sup> millimeters Symbol Min Тур Max Min Тур Max Α 0.460 0.530 0.600 0.0181 0.0209 0.0236 b 0.170 0.280 0.330 0.0067 0.0110 0.0130 D 4.850 5.000 5.150 0.1909 0.1969 0.2028 D1 3.450 3.500 3.550 0.1358 0.1378 0.1398 Ε 4.850 5.000 5.150 0.1909 0.1969 0.2028 E1 3.500 3.550 3.450 0.1358 0.1378 0.1398 е 0.500 0.0197 F 0.700 0.750 0.800 0.0276 0.0295 0.0315 ddd 0.080 0.0031 0.150 0.0059 eee

Table 65. UFBGA64 package mechanical data (continued)

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

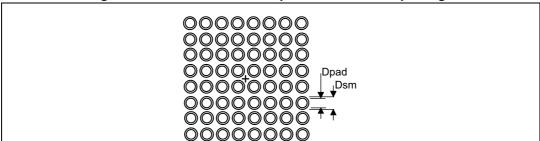

Figure 35. Recommended footprint for UFBGA64 package

0.050

Table 66. UFBGA64 recommended PCB design rules

|                   | <u> </u>                                                         |  |

|-------------------|------------------------------------------------------------------|--|

| Dimension         | Recommended values                                               |  |

| Pitch             | 0.5                                                              |  |

| Dpad              | 0.280 mm                                                         |  |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |  |

| Stencil opening   | 0.280 mm                                                         |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |  |

| Pad trace width   | 0.100 mm                                                         |  |

92/122 DocID022265 Rev 7

0.0020

A019\_FP\_V2

Table 76. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |          | Modified datasheet title.                                                                                                                                                                  |

|             |          | Added packages UFQFPN48 and UFBGA64.                                                                                                                                                       |

|             |          | Replaced "backup domain with "RTC domain" throughout the document.                                                                                                                         |

|             |          | Changed SRAM value from "4 to 8 Kbyte" to "8 Kbyte"                                                                                                                                        |

|             |          | Replaced IWWDG with IWDG in Figure: Block diagram.                                                                                                                                         |

|             |          | Added inputs LSI and LSE to the multiplexer in <i>Figure: Clock tree.</i>                                                                                                                  |

|             |          | Added feature "Reference clock detection" in Section: Real-time clock (RTC) and backup registers.                                                                                          |

|             |          | Modified junction temperature in <i>Table: Thermal characteristics</i> .                                                                                                                   |

|             |          | Renamed Table: Internal voltage reference calibration values.                                                                                                                              |

|             | 4 4      | Replaced $V_{DD}$ with $V_{DDA}$ and $V_{RERINT}$ with $\Delta V_{REFINT}$ in Table:<br>Embedded internal reference voltage.                                                               |

|             |          | Rephrased introduction of Section: Touch sensing controller (TSC).                                                                                                                         |

| 13-Jan-2014 |          | Rephrased Section: Voltage regulator.                                                                                                                                                      |

|             |          | Added sentence "If this is used when the voltage regulator is put in low power mode" under "Stop mode" in Section: Low-power modes.                                                        |

|             |          | Removed sentence "The internal voltage reference is also connected to ADC_IN17 input channel of the ADC." in Section: Comparators (COMP).                                                  |

|             |          | Removed feature "Periodic wakeup from Stop/Standby" in Section: Real-time clock (RTC) and backup registers.                                                                                |

|             |          | Replaced I <sub>DD</sub> with I <sub>DDA</sub> in <i>Table: HSI oscillator characteristics, Table: HSI14 oscillator characteristics</i> and <i>Table: LSI oscillator characteristics</i> . |

|             |          | Moved section "Wakeup time from low-power mode" to Section 6.3.6 and rephrased the section.                                                                                                |

|             |          | Added lines D2 and E2 in <i>Table: UFQFPN48 – 7 x 7 mm, 0.5 mm pitch, package mechanical data.</i>                                                                                         |

|             |          | Added "The peripheral clock used is 48 MHz." in Section <i>On-chip peripheral current consumption.</i>                                                                                     |

Table 76. Document revision history (continued)

| Table 76. Document revision history (continued) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision         | Revision Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 28-Aug-2015                                     | 5<br>(continued) | <ul> <li>Table 31: Peripheral current consumption</li> <li>Addition of WLCSP36 package. Updates in:</li> <li>Section 2: Description</li> <li>Table 2: STM32F051xx family device features and peripheral count</li> <li>Section 4: Pinouts and pin descriptions with the addition of Figure 7: WLCSP36 package pinout</li> <li>Table 13: Pin definitions</li> <li>Table 20: General operating conditions</li> <li>Section 7: Package information with the addition of Section 7.5: WLCSP36 package information</li> <li>Table 74: Package thermal characteristics</li> <li>Section 8: Part numbering</li> <li>Update of the device marking examples in Section 7: Package information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 16-Dec-2015                                     | 6                | Section 2: Description:  - Table 2: STM32F051xx family device features and peripheral count - number of SPIs corrected for 64-pin packages  - Figure 1: Block diagram modified  Section 3: Functional overview:  - Figure 2: Clock tree modified; divider for CEC corrected  - Table 8: Comparison of I <sup>2</sup> C analog and digital filters - adding 20 mA information for FastPlus mode  Section 4: Pinouts and pin descriptions:  - Package pinout figures updated (look and feel)  - Figure 7: WLCSP36 package pinout - now presented in top view  - Table 13: Pin definitions - notes added (VSSA corrected to pin 16 on LQFP32); note 5 added  Section 5: Memory mapping:  - added information on STM32F051x4/x6 difference versus STM32F051x8 map in Figure 10  Section 6: Electrical characteristics:  - Table 24: Embedded internal reference voltage - removed - 40°C-85°C temperature range line and the associated note  - Table 48: I/O static characteristics - removed note  - Section 6.3.16: 12-bit ADC characteristics - changed introductory sentence  - Table 52: ADC characteristics updated and table footnotes 3 and 4 added  - Table 59: TIMx characteristics modified  - Table 59: TIMx characteristics modified  - Table 64: I <sup>2</sup> S characteristics reorganized  - Figure 52: UFQFPN32 package outline - figure footnotes added |  |  |

Table 76. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-Jan-2017 | 7        | <ul> <li>Section 6: Electrical characteristics:         <ul> <li>Table 36: LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) - information on configuring different drive capabilities removed. See the corresponding reference manual.</li> <li>Table 24: Embedded internal reference voltage - V<sub>REFINT</sub> values</li> <li>Table 55: DAC characteristics - min. R<sub>LOAD</sub> to V<sub>DDA</sub> defined</li> <li>Figure 29: SPI timing diagram - slave mode and CPHA = 0 and Figure 30: SPI timing diagram - slave mode and CPHA = 1 enhanced and corrected</li> </ul> </li> <li>Section 8: Ordering information:         <ul> <li>The name of the section changed from the previous "Part numbering"</li> </ul> </li> </ul> |