Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I2S, POR, PWM, WDT                                               |

| Number of I/O              | 55                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f051r8t6 |

# **Contents**

| 1 | Intro | duction   |                                                   | 9  |

|---|-------|-----------|---------------------------------------------------|----|

| 2 | Desc  | cription  |                                                   | 10 |

| 3 | Fund  | ctional o | verview                                           | 13 |

|   | 3.1   | ARM®-     | Cortex®-M0 core                                   | 13 |

|   | 3.2   | Memor     | ies                                               | 13 |

|   | 3.3   | Boot m    | odes                                              | 13 |

|   | 3.4   | Cyclic r  | redundancy check calculation unit (CRC)           | 14 |

|   | 3.5   | Power     | management                                        | 14 |

|   |       | 3.5.1     | Power supply schemes                              | 14 |

|   |       | 3.5.2     | Power supply supervisors                          | 14 |

|   |       | 3.5.3     | Voltage regulator                                 | 14 |

|   |       | 3.5.4     | Low-power modes                                   | 15 |

|   | 3.6   | Clocks    | and startup                                       | 15 |

|   | 3.7   | Genera    | al-purpose inputs/outputs (GPIOs)                 | 16 |

|   | 3.8   | Direct r  | memory access controller (DMA)                    | 17 |

|   | 3.9   | Interrup  | ots and events                                    | 17 |

|   |       | 3.9.1     | Nested vectored interrupt controller (NVIC)       | 17 |

|   |       | 3.9.2     | Extended interrupt/event controller (EXTI)        | 17 |

|   | 3.10  | Analog    | -to-digital converter (ADC)                       | 17 |

|   |       | 3.10.1    | Temperature sensor                                | 18 |

|   |       | 3.10.2    | Internal voltage reference (V <sub>REFINT</sub> ) |    |

|   |       | 3.10.3    | V <sub>BAT</sub> battery voltage monitoring       | 19 |

|   | 3.11  | Digital-  | to-analog converter (DAC)                         | 19 |

|   | 3.12  | Compa     | rators (COMP)                                     | 19 |

|   | 3.13  | Touch s   | sensing controller (TSC)                          | 19 |

|   | 3.14  | Timers    | and watchdogs                                     | 21 |

|   |       | 3.14.1    | Advanced-control timer (TIM1)                     | 21 |

|   |       | 3.14.2    | General-purpose timers (TIM2, 3, 14, 15, 16, 17)  | 22 |

|   |       | 3.14.3    | Basic timer TIM6                                  | 22 |

|   |       | 3.14.4    | Independent watchdog (IWDG)                       |    |

|   |       | 3.14.5    | System window watchdog (WWDG)                     | 23 |

|   |       | 3.14.6   | SysTick timer                                                                    | . 23 |

|---|-------|----------|----------------------------------------------------------------------------------|------|

|   | 3.15  | Real-tir | me clock (RTC) and backup registers                                              | . 23 |

|   | 3.16  | Inter-in | tegrated circuit interface (I <sup>2</sup> C)                                    | . 24 |

|   | 3.17  | Univers  | sal synchronous/asynchronous receiver/transmitter (USART)                        | . 25 |

|   | 3.18  |          | peripheral interface (SPI) / Inter-integrated sound interface (I <sup>2</sup> S) |      |

|   | 3.19  | High-de  | efinition multimedia interface (HDMI) - consumer nics control (CEC)              |      |

|   | 3.20  | Serial v | wire debug port (SW-DP)                                                          | . 26 |

| 4 | Pino  | uts and  | pin descriptions                                                                 | . 27 |

| 5 | Mem   | ory map  | oping                                                                            | . 39 |

| 6 | Elect | rical ch | aracteristics                                                                    | . 42 |

|   | 6.1   | Parame   | eter conditions                                                                  | . 42 |

|   |       | 6.1.1    | Minimum and maximum values                                                       | . 42 |

|   |       | 6.1.2    | Typical values                                                                   | . 42 |

|   |       | 6.1.3    | Typical curves                                                                   | . 42 |

|   |       | 6.1.4    | Loading capacitor                                                                | . 42 |

|   |       | 6.1.5    | Pin input voltage                                                                | . 42 |

|   |       | 6.1.6    | Power supply scheme                                                              | . 43 |

|   |       | 6.1.7    | Current consumption measurement                                                  | . 44 |

|   | 6.2   | Absolu   | te maximum ratings                                                               | . 45 |

|   | 6.3   | Operati  | ing conditions                                                                   | . 47 |

|   |       | 6.3.1    | General operating conditions                                                     | . 47 |

|   |       | 6.3.2    | Operating conditions at power-up / power-down                                    | . 47 |

|   |       | 6.3.3    | Embedded reset and power control block characteristics                           | . 48 |

|   |       | 6.3.4    | Embedded reference voltage                                                       | . 49 |

|   |       | 6.3.5    | Supply current characteristics                                                   | . 49 |

|   |       | 6.3.6    | Wakeup time from low-power mode                                                  | . 59 |

|   |       | 6.3.7    | External clock source characteristics                                            | . 59 |

|   |       | 6.3.8    | Internal clock source characteristics                                            | . 63 |

|   |       | 6.3.9    | PLL characteristics                                                              | . 66 |

|   |       | 6.3.10   | Memory characteristics                                                           | . 66 |

|   |       | 6.3.11   | EMC characteristics                                                              | . 67 |

|   |       | 6.3.12   | Electrical sensitivity characteristics                                           | . 68 |

|   |       | 6.3.13   | I/O current injection characteristics                                            | . 69 |

|   |       |          |                                                                                  |      |

### **Contents**

|   |      | 6.3.14    | I/O port characteristics                    | 70  |

|---|------|-----------|---------------------------------------------|-----|

|   |      | 6.3.15    | NRST pin characteristics                    | 75  |

|   |      | 6.3.16    | 12-bit ADC characteristics                  | 76  |

|   |      | 6.3.17    | DAC electrical specifications               | 80  |

|   |      | 6.3.18    | Comparator characteristics                  | 82  |

|   |      | 6.3.19    | Temperature sensor characteristics          |     |

|   |      | 6.3.20    | V <sub>BAT</sub> monitoring characteristics | 84  |

|   |      | 6.3.21    | Timer characteristics                       | 84  |

|   |      | 6.3.22    | Communication interfaces                    | 85  |

| 7 | Pacl | kage info | ormation                                    | 91  |

|   | 7.1  | UFBGA     | A64 package information                     | 91  |

|   | 7.2  | LQFP6     | 4 package information                       | 94  |

|   | 7.3  | LQFP4     | 8 package information                       | 97  |

|   | 7.4  | UFQFF     | PN48 package information                    | 100 |

|   | 7.5  | WLCSI     | P36 package information                     | 103 |

|   | 7.6  | LQFP3     | 2 package information                       | 106 |

|   | 7.7  | UFQFF     | PN32 package information                    | 108 |

|   | 7.8  | Therma    | al characteristics                          |     |

|   |      | 7.8.1     | Reference document                          | 112 |

|   |      | 7.8.2     | Selecting the product temperature range     | 112 |

| 8 | Orde | ering inf | ormation                                    | 115 |

| 9 | Revi | sion his  | story                                       | 116 |

# List of figures

# STM32F051x4 STM32F051x6 STM32F051x8

| Figure 49. | LQFP32 package outline                          | 106 |

|------------|-------------------------------------------------|-----|

| Figure 50. | Recommended footprint for LQFP32 package        | 107 |

| Figure 51. | LQFP32 package marking example                  | 108 |

| Figure 52. | UFQFPN32 package outline                        | 109 |

| Figure 53. | Recommended footprint for UFQFPN32 package      | 110 |

| Figure 54. | UFQFPN32 package marking example                | 111 |

| Figure 55. | LQFP64 P <sub>D</sub> max versus T <sub>A</sub> | 114 |

Table 2. STM32F051xx family device features and peripheral count

| Perip                 | STM32F051Kx                           |                                       | STM32F051T8                                                                                                         | STM32F051 |                      | 1Cx                  | STM32F051Rx       |       | 1Rx               |       |   |

|-----------------------|---------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------|----------------------|----------------------|-------------------|-------|-------------------|-------|---|

| Flash mem             | 16                                    | 32                                    | 64                                                                                                                  | 64        | 16                   | 32                   | 64                | 16    | 32                | 64    |   |

| SRAM                  | SRAM (Kbyte)                          |                                       |                                                                                                                     |           |                      | 8                    |                   |       |                   |       |   |

|                       | Advanced control                      |                                       | 1 (16-bit)                                                                                                          |           |                      |                      |                   |       |                   |       |   |

| Timers                | General purpose                       |                                       |                                                                                                                     |           |                      | (16-bit)<br>(32-bit) |                   |       |                   |       |   |

|                       | Basic                                 |                                       |                                                                                                                     |           | 1                    | (16-bit)             |                   |       |                   |       |   |

|                       | SPI [I <sup>2</sup> S] <sup>(1)</sup> |                                       | 1 [1] <sup>(2)</sup>                                                                                                |           | 1 [1] <sup>(2)</sup> | 1 [′                 | 1] <sup>(2)</sup> | 2 [1] |                   | 2 [1] |   |

| Comm.                 | I <sup>2</sup> C                      |                                       | 1 <sup>(3)</sup>                                                                                                    |           | 1 <sup>(3)</sup>     | 1                    | (3)               | 2     | 1                 | (3)   | 2 |

| interfaces            | USART                                 | 1 <sup>(4)</sup>                      |                                                                                                                     | 2         | 2                    | 1 <sup>(4)</sup>     | 2                 | 2     | 1 <sup>(4)</sup>  | 2     | 2 |

|                       | CEC                                   |                                       |                                                                                                                     |           |                      | 1                    |                   |       |                   |       |   |

| _                     | t ADC<br>f channels)                  | 1 (10 ext. + 3 int.) 1 (16 ext. + 3 i |                                                                                                                     |           |                      |                      | int.)             |       |                   |       |   |

|                       | t DAC<br>f channels)                  | 1 (1)                                 |                                                                                                                     |           |                      |                      |                   |       |                   |       |   |

| Analog co             | omparator                             | 2                                     |                                                                                                                     |           |                      |                      |                   |       |                   |       |   |

| GP                    | PIOs                                  | 25 (on LQFP32)<br>27 (on UFQFPN32)    |                                                                                                                     | 29        | 39                   |                      |                   | 55    |                   |       |   |

| Capacitive ser        | nsing channels                        | 13 (on LQFP32)<br>14 (on UFQFPN32)    |                                                                                                                     | 14        | 17                   |                      |                   | 18    |                   |       |   |

| Max. CPU              | I frequency                           | 48 MHz                                |                                                                                                                     |           |                      |                      |                   |       |                   |       |   |

| Operating voltage     |                                       | 2.0 to 3.6 V                          |                                                                                                                     |           |                      |                      |                   |       |                   |       |   |

| Operating temperature |                                       |                                       | Ambient operating temperature: -40°C to 85°C / -40°C to 105°C Junction temperature: -40°C to 105°C / -40°C to 125°C |           |                      |                      |                   |       |                   |       |   |

| Pack                  | kages                                 |                                       | _QFP3;<br>=QFPN                                                                                                     |           | WLCSP36              | LQFP48<br>UFQFPN     |                   |       | LQFP64<br>UFBGA64 |       |   |

<sup>1.</sup> The SPI1 interface can be used either in SPI mode or in  $\rm I^2S$  audio mode.

<sup>2.</sup> SPI2 is not present.

<sup>3.</sup> I2C2 is not present.

<sup>4.</sup> USART2 is not present.

In Standby mode, it is put in power down mode. In this mode, the regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost).

### 3.5.4 Low-power modes

The STM32F051xx microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

## • Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, the PVD output, RTC, I2C1, USART1,, COMPx or the CEC.

The CEC, USART1 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data. If this is used when the voltage regulator is put in low power mode, the regulator is first switched to normal mode before the clock is provided to the given peripheral.

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

Note:

The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

# 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

# 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                      | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV)  | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Table 4. Internal voltage reference calibration values

| Calibration value name | Description                                                                              | Memory address            |

|------------------------|------------------------------------------------------------------------------------------|---------------------------|

|                        | Raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |

Table 13. Pin definitions (continued)

|        | P       | in n            | umbe    | er     |          | Table 13. Pin                        |          |               |       | Pin functions                                                     |                         |  |

|--------|---------|-----------------|---------|--------|----------|--------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|-------------------------|--|

| LQFP64 | UFBGA64 | LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                               | Additional<br>functions |  |

| 33     | Н8      | 25              | -       | -      | -        | PB12                                 | I/O      | FT            | (5)   | SPI2_NSS,<br>TIM1_BKIN,<br>TSC_G6_IO2,<br>EVENTOUT                | -                       |  |

| 34     | G8      | 26              | -       | -      | -        | PB13                                 | I/O      | FT            | (5)   | SPI2_SCK,<br>TIM1_CH1N,<br>TSC_G6_IO3                             | -                       |  |

| 35     | F8      | 27              | -       | -      | -        | PB14                                 | I/O      | FT            | (5)   | SPI2_MISO,<br>TIM1_CH2N,<br>TIM15_CH1,<br>TSC_G6_IO4              | -                       |  |

| 36     | F7      | 28              | -       | -      | -        | PB15                                 | I/O      | FT            | (5)   | SPI2_MOSI,<br>TIM1_CH3N,<br>TIM15_CH1N,<br>TIM15_CH2              | RTC_REFIN               |  |

| 37     | F6      | -               | -       | -      | -        | PC6                                  | I/O      | FT            | -     | TIM3_CH1                                                          | -                       |  |

| 38     | E7      | -               | -       | -      | -        | PC7                                  | I/O      | FT            | -     | TIM3_CH2                                                          | -                       |  |

| 39     | E8      | -               | -       | -      | -        | PC8                                  | I/O      | FT            | -     | TIM3_CH3                                                          | -                       |  |

| 40     | D8      | -               | -       | -      | -        | PC9                                  | I/O      | FT            | -     | TIM3_CH4                                                          | -                       |  |

| 41     | D7      | 29              | E2      | 18     | 18       | PA8                                  | I/O      | FT            | -     | USART1_CK,<br>TIM1_CH1,<br>EVENTOUT,<br>MCO                       | -                       |  |

| 42     | C7      | 30              | D1      | 19     | 19       | PA9                                  | I/O      | FT            | -     | USART1_TX,<br>TIM1_CH2,<br>TIM15_BKIN,<br>TSC_G4_IO1              | -                       |  |

| 43     | C6      | 31              | C1      | 20     | 20       | PA10                                 | I/O      | FT            | -     | USART1_RX,<br>TIM1_CH3,<br>TIM17_BKIN,<br>TSC_G4_IO2              | -                       |  |

| 44     | C8      | 32              | C2      | 21     | 21       | PA11                                 | I/O      | FT            | -     | USART1_CTS,<br>TIM1_CH4,<br>COMP1_OUT,<br>TSC_G4_IO3,<br>EVENTOUT | -                       |  |

# On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 31*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in Table 17: Voltage characteristics

Table 31. Peripheral current consumption

|     | Peripheral               | Typical consumption at 25 °C | Unit     |  |

|-----|--------------------------|------------------------------|----------|--|

|     | BusMatrix <sup>(1)</sup> | 5                            |          |  |

|     | DMA1                     | 7                            |          |  |

|     | SRAM                     | 1                            |          |  |

|     | Flash memory interface   | 14                           |          |  |

|     | CRC                      | 2                            |          |  |

| AHB | GPIOA                    | 9                            | μΑ/MHz   |  |

| АПБ | GPIOB                    | 12                           | μΑνίνιπΖ |  |

|     | GPIOC                    | 2                            |          |  |

|     | GPIOD                    | 1                            |          |  |

|     | GPIOF                    | 1                            |          |  |

|     | TSC                      | 6                            |          |  |

|     | All AHB peripherals      | 55                           |          |  |

#### 6.3.6 Wakeup time from low-power mode

The wakeup times given in Table 32 are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*.

| Symbol                 | Parameter                   | Conditions                  | Typ @Vdd = VddA |         |         |       |         |     | Unit |

|------------------------|-----------------------------|-----------------------------|-----------------|---------|---------|-------|---------|-----|------|

|                        | Farameter                   | Conditions                  | = 2.0 V         | = 2.4 V | = 2.7 V | = 3 V | = 3.3 V | Max | Oill |

| twustop                | Wakeup from Stop<br>mode    | Regulator in run mode       | 3.2             | 3.1     | 2.9     | 2.9   | 2.8     | 5   |      |

|                        |                             | Regulator in low power mode | 7.0             | 5.8     | 5.2     | 4.9   | 4.6     | 9   | ue   |

| t <sub>WUSTANDBY</sub> | Wakeup from<br>Standby mode | -                           | 60.4            | 55.6    | 53.5    | 52    | 51      | -   | μs   |

| t <sub>WUSLEEP</sub>   | Wakeup from Sleep mode      | -                           |                 | 4 SY    | SCLK cy | cles  |         | -   |      |

Table 32. Low-power mode wakeup timings

#### 6.3.7 **External clock source characteristics**

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in Figure 15: High-speed external clock source AC timing diagram.

Table 33. High-speed external user clock characteristics

| Symbol                                     | Parameter(1)                         | Min                    | Тур | Max                    | Unit |

|--------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                       | User external clock source frequency | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage  | 0.7 V <sub>DDIOx</sub> | -   | $V_{DDIOx}$            | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage   | $V_{SS}$               | -   | 0.3 V <sub>DDIOx</sub> |      |

| $t_{w(\text{HSEH})} \ t_{w(\text{HSEL})}$  | OSC_IN high or low time              | 15                     | 1   | 1                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time             | -                      | -   | 20                     | 113  |

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

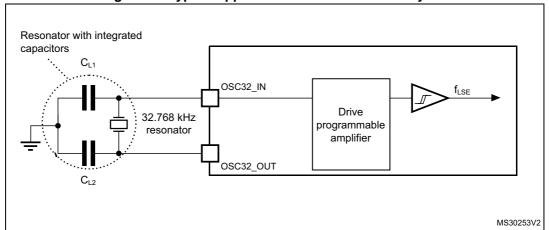

Figure 18. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.8 Internal clock source characteristics

The parameters given in *Table 37* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20: General operating conditions*. The provided curves are characterization results, not tested in production.

# High-speed internal (HSI) RC oscillator

Table 37. HSI oscillator characteristics<sup>(1)</sup>

| Symbol                | Parameter                        | Conditions                    | Min                 | Тур | Max                | Unit |

|-----------------------|----------------------------------|-------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                        | -                             | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step           | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                       | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

| ACC <sub>HSI</sub>    | Accuracy of the HSI oscillator   | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> | %    |

|                       |                                  | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> |      |

|                       |                                  | T <sub>A</sub> = 0 to 85°C    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | T <sub>A</sub> = 0 to 70°C    | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | T <sub>A</sub> = 0 to 55°C    | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time      | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption | -                             | -                   | 80  | 100 <sup>(2)</sup> | μΑ   |

- 1.  $V_{DDA} = 3.3 \text{ V}$ ,  $T_A = -40 \text{ to } 105^{\circ}\text{C}$  unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

- 4. Factory calibrated, parts not soldered.

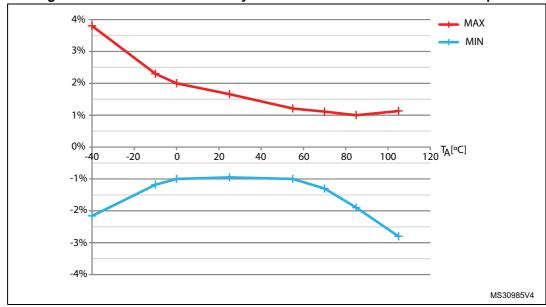

Figure 19. HSI oscillator accuracy characterization results for soldered parts

**Functional** susceptibility **Symbol Description** Unit **Positive** Negative injection injection Injected current on BOOT0 -0 NA Injected current on PA10, PA12, PB4, PB5, PB10, PB15 and PD2 pins with induced leakage current on adjacent pins less -5 NA than -10 µA mΑ  $I_{INJ}$ Injected current on all other FT and FTf pins -5 NA Injected current on PA6 and PC0 -0 +5 Injected current on all other TTa, TC and RST pins -5 +5

Table 47. I/O current injection susceptibility

# 6.3.14 I/O port characteristics

# General input/output characteristics

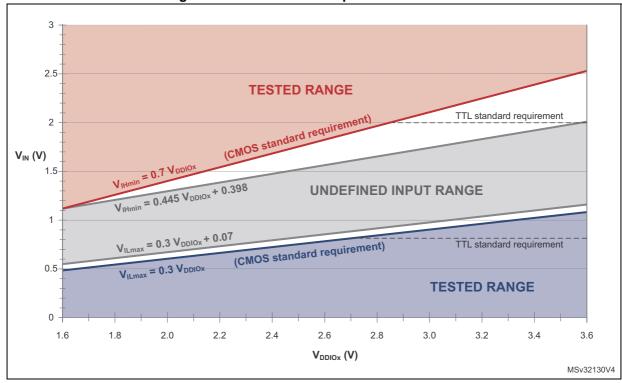

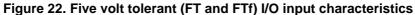

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the conditions summarized in *Table 20: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol           | Parameter                     | Conditions                   | Min                                            | Тур                | Max                                          | Unit |  |

|------------------|-------------------------------|------------------------------|------------------------------------------------|--------------------|----------------------------------------------|------|--|

| V <sub>IL</sub>  | Low level input voltage       | TC and TTa I/O               | -                                              | -                  | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup>  | V    |  |

|                  |                               | FT and FTf I/O               | -                                              | -                  | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |      |  |

|                  |                               | воото                        | -                                              | -                  | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   |      |  |

|                  |                               | All I/Os except<br>BOOT0 pin | -                                              | -                  | 0.3 V <sub>DDIOx</sub>                       |      |  |

| V <sub>IH</sub>  | High level input voltage      | TC and TTa I/O               | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                  | -                                            |      |  |

|                  |                               | FT and FTf I/O               | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                  | -                                            |      |  |

|                  |                               | воото                        | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                  | -                                            | V    |  |

|                  |                               | All I/Os except<br>BOOT0 pin | 0.7 V <sub>DDIOx</sub>                         | -                  | -                                            |      |  |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis | TC and TTa I/O               | -                                              | 200 <sup>(1)</sup> | -                                            |      |  |

|                  |                               | FT and FTf I/O               | -                                              | 100 <sup>(1)</sup> | -                                            | mV   |  |

|                  |                               | воото                        | -                                              | 300 <sup>(1)</sup> | -                                            |      |  |

Table 48. I/O static characteristics

Symbol Unit **Parameter Conditions** Min Тур Max TC, FT and FTf I/O TTa in digital mode ± 0.1  $V_{SS} \le V_{IN} \le V_{DDIOx}$ TTa in digital mode 1 Input leakage  $V_{\text{DDIO}X} \le V_{\text{IN}} \le V_{\text{DDA}}$  $I_{lkg}$ μΑ current(2) TTa in analog mode ± 0.2  $V_{SS} \le V_{IN} \le V_{DDA}$ FT and FTf I/O 10  $V_{DDIOx} \le V_{IN} \le 5 V$ Weak pull-up  $R_{PU}$ equivalent resistor  $V_{IN} = V_{SS}$ 25 40 55 kΩ Weak pull-down  $V_{IN} = -V_{DDIOx}$  $R_{PD}$ equivalent 25 40 55 kΩ resistor(3)

Table 48. I/O static characteristics (continued)

I/O pin capacitance

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 21* for standard I/Os, and in *Figure 22* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

5

$C_{IO}$

рF

<sup>1.</sup> Data based on design simulation only. Not tested in production.

The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 47: I/O current injection susceptibility.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

Figure 21. TC and TTa I/O input characteristics

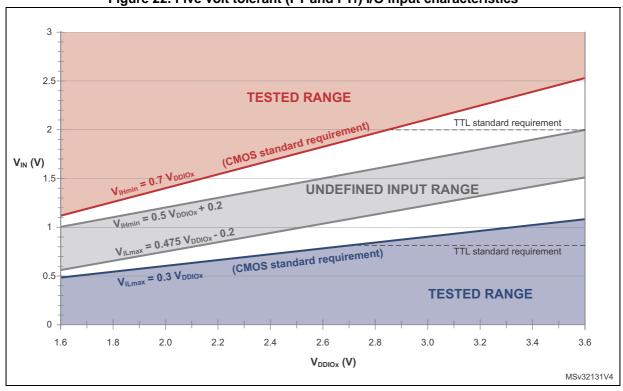

| Symbol                               | Parameter               | Conditions         | Min | Max | Unit |

|--------------------------------------|-------------------------|--------------------|-----|-----|------|

| t <sub>su(SD_MR)</sub>               | Data input setup time   | Master receiver    | 6   | -   |      |

| t <sub>su(SD_SR)</sub>               |                         | Slave receiver     | 2   | -   |      |

| t <sub>h(SD_MR)</sub> <sup>(2)</sup> | - Data input hold time  | Master receiver    | 4   | -   |      |

| t <sub>h(SD_SR)</sub> (2)            |                         | Slave receiver     | 0.5 | -   | 200  |

| t <sub>v(SD_MT)</sub> <sup>(2)</sup> | Data autaut valid time  | Master transmitter | -   | 4   | ns   |

| t <sub>v(SD_ST)</sub> <sup>(2)</sup> | Data output valid time  | Slave transmitter  | -   | 20  |      |

| t <sub>h(SD_MT)</sub>                | Data output hold time   | Master transmitter | 0   | -   |      |

| t <sub>h(SD_ST)</sub>                | Data output Hold tillle | Slave transmitter  | 13  | -   |      |

Table 64. I<sup>2</sup>S characteristics<sup>(1)</sup> (continued)

- 1. Data based on design simulation and/or characterization results, not tested in production.

- 2. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$  = 8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  = 125 ns.

Figure 32. I<sup>2</sup>S slave timing diagram (Philips protocol)

- 1. Measurement points are done at CMOS levels: 0.3 ×  $V_{DDIOx}$  and 0.7 ×  $V_{DDIOx}$

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

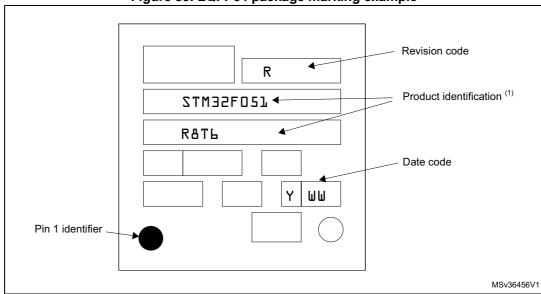

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 39. LQFP64 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

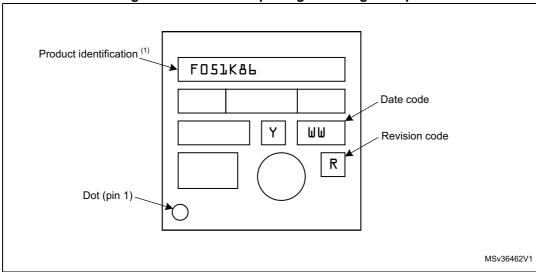

# **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 54. UFQFPN32 package marking example

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 7.8 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 20: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O}$$

max =  $\Sigma (V_{OL} \times I_{OL}) + \Sigma ((V_{DDIOx} - V_{OH}) \times I_{OH})$ ,

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol            | Parameter                                                                 | Value | Unit |  |

|-------------------|---------------------------------------------------------------------------|-------|------|--|

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |  |

|                   | Thermal resistance junction-ambient LQFP48 - 7 × 7 mm                     | 55    |      |  |

|                   | Thermal resistance junction-ambient LQFP32 - 7 × 7 mm                     | 56    |      |  |

|                   | Thermal resistance junction-ambient UFBGA64 - 5 × 5 mm                    | 65    | °C/W |  |

|                   | Thermal resistance junction-ambient UFQFPN48 - 7 × 7 mm                   | 32    |      |  |

|                   | Thermal resistance junction-ambient UFQFPN32 - 5 × 5 mm                   | 38    |      |  |

|                   | Thermal resistance junction-ambient WLCSP36 - 2.6 × 2.7 mm                | 60    |      |  |

Table 74. Package thermal characteristics

### 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

# 7.8.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

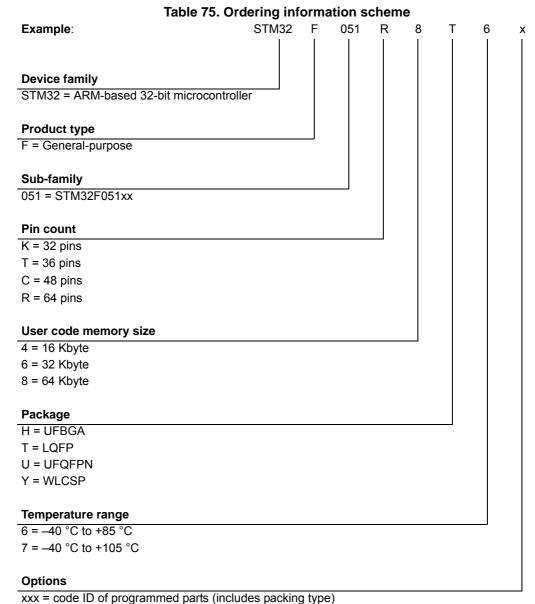

#### **Ordering information** 8

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

TR = tape and reel packing

blank = tray packing