#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | -                                                                          |

| Core Size                  | -                                                                          |

| Speed                      | -                                                                          |

| Connectivity               | -                                                                          |

| Peripherals                | -                                                                          |

| Number of I/O              | -                                                                          |

| Program Memory Size        | -                                                                          |

| Program Memory Type        | -                                                                          |

| EEPROM Size                | -                                                                          |

| RAM Size                   | -                                                                          |

| Voltage - Supply (Vcc/Vdd) | -                                                                          |

| Data Converters            | -                                                                          |

| Oscillator Type            | -                                                                          |

| Operating Temperature      | -                                                                          |

| Mounting Type              | -                                                                          |

| Package / Case             | -                                                                          |

| Supplier Device Package    | -                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c161olmhafxuma1 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2       | Pi         | n Definit      | tions and Functions                                                                                                                                                                                                                                                                                                                              |

|---------------|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol        | Pin<br>Num | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                         |

| XTAL1         | 2          | 1              | XTAL1: Input to the oscillator amplifier and input to the internal clock generator                                                                                                                                                                                                                                                               |

| XTAL2         | 3          | 0              | XTAL2: Output of the oscillator amplifier circuit.<br>To clock the device from an external source, drive XTAL1,<br>while leaving XTAL2 unconnected. Minimum and maximum<br>high/low and rise/fall times specified in the AC<br>Characteristics must be observed.                                                                                 |

| P3            |            | IO             | Port 3 is a 12-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 3 outputs can be configured as push/<br>pull or open drain drivers. The Port 3 pins serve for following<br>alternate functions: |

| P3.2          | 5          | 1              | CAPIN GPT2 Register CAPREL Capture Input<br>This alternate input is <b>only available in the C1610</b> .                                                                                                                                                                                                                                         |

| P3.3          | 6          | 0              | T3OUT GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                          |

| P3.4          | 7          | I              | T3EUD GPT1 Timer T3 External Up/Down Control Input                                                                                                                                                                                                                                                                                               |

| P3.5          | 8          |                | T4IN GPT1 Timer T4 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                                                                                                 |

| P3.6          | 9          |                | T3IN GPT1 Timer T3 Count/Gate Input                                                                                                                                                                                                                                                                                                              |

| P3.7          | 10         |                | T2IN GPT1 Timer T2 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                                                                                                 |

| P3.8<br>P3.9  | 11<br>12   | 1/O<br>1/O     | MRST SSC Master-Receive/Slave-Transmit Inp./Outp.<br>MTSR SSC Master-Transmit/Slave-Receive Outp./Inp.                                                                                                                                                                                                                                           |

| P3.9<br>P3.10 | 12         | 0              | MTSRSSC Master-Transmit/Slave-Receive Outp./Inp.TxD0ASC0 Clock/Data Output (Async./Sync.)                                                                                                                                                                                                                                                        |

| P3.11         | 14         | 1/0            | RxD0 ASC0 Data Input (Async.) or Inp./Outp. (Sync.)                                                                                                                                                                                                                                                                                              |

| P3.12         | 15         | 0              | BHEExternal Memory High Byte Enable Signal,WRHExternal Memory High Byte Write Strobe                                                                                                                                                                                                                                                             |

| P3.13         | 16         | I/O            | SCLK SSC Master Clock Output / Slave Clock Input                                                                                                                                                                                                                                                                                                 |

| Ρ4            |            | IO             | Port 4 is a 6-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 4 can be used to output the segment<br>address lines:                                                                            |

| P4.0          | 17         | 0              | A16 Least Significant Segment Address Line                                                                                                                                                                                                                                                                                                       |

| P4.1          | 18         | 0              | A17 Segment Address Line                                                                                                                                                                                                                                                                                                                         |

| P4.2          | 19         | 0              | A18 Segment Address Line                                                                                                                                                                                                                                                                                                                         |

| P4.3          | 20         | 0              | A19 Segment Address Line                                                                                                                                                                                                                                                                                                                         |

| P4.4          | 23         | 0              | A20 Segment Address Line                                                                                                                                                                                                                                                                                                                         |

| P4.5          | 24         | 0              | A21 Most Significant Segment Address Line                                                                                                                                                                                                                                                                                                        |

| Table 2                     | Pi               | n Definit      | tions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-----------------------------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                      | Pin<br>Num       | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| P2                          |                  | 10             | Port 2 is a 7-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 2 outputs can be configured as push/<br>pull or open drain drivers. The following Port 2 pins serve for<br>alternate functions: |  |  |  |  |

| P2.9                        | 72               | 1              | EX1IN Fast External Interrupt 1 Input                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| P2.10                       | 73               | 1              | EX2IN Fast External Interrupt 2 Input                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| P2.11                       | 74               | 1              | EX3IN Fast External Interrupt 3 Input                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| P2.12                       | 75               | 1              | EX4IN Fast External Interrupt 4 Input                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                             | 76<br>77<br>78   | <br> <br>      | <ul> <li>EX5IN Fast External Interrupt 5 Input</li> <li>EX6IN Fast External Interrupt 6 Input</li> <li>EX7IN Fast External Interrupt 7 Input</li> <li>These external interrupts are only available in the C1610.</li> </ul>                                                                                                                     |  |  |  |  |

| <b>P5</b><br>P5.14<br>P5.15 | 79<br>80         | 1              | Port 5 is a 2-bit input-only port with Schmitt-Trigger char. Thepins of Port 5 also serve as timer inputs:T4EUDGPT1 Timer T4 External Up/Down Control InputT2EUDGPT1 Timer T2 External Up/Down Control Input                                                                                                                                    |  |  |  |  |

| V <sub>DD</sub>             | 4, 22,<br>37, 64 | -              | Digital Supply Voltage:<br>+ 5 V or + 3 V during normal operation and idle mode.<br>$\geq$ 2.5 V during power down mode.                                                                                                                                                                                                                        |  |  |  |  |

| V <sub>SS</sub>             | 1, 21,<br>38, 63 | _              | Digital Ground.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

Note: The following behavioral differences must be observed when the bidirectional reset is active:

- Bit BDRSTEN in register SYSCON cannot be changed after EINIT and is cleared automatically after a reset.

- The reset indication flags always indicate a long hardware reset.

- The PORT0 configuration is treated like on a hardware reset. Especially the bootstrap loader may be activated when POL.4 is low.

- Pin RSTIN may only be connected to external reset devices with an open drain output driver.

- A short hardware reset is extended to the duration of the internal reset sequence.

#### **Memory Organization**

The memory space of the C161K/O is configured in a Von Neumann architecture which means that code memory, data memory, registers and I/O ports are organized within the same linear address space which includes 16 MBytes. The entire memory space can be accessed bytewise or wordwise. Particular portions of the on-chip memory have additionally been made directly bitaddressable.

The C161K/O is prepared to incorporate on-chip program memory (not in the ROM-less derivatives, of course) for code or constant data. The internal ROM area can be mapped either to segment 0 or segment 1.

On-chip Internal RAM (IRAM) is provided (1 KByte in the C161K, 2 KBytes in the C161O) as a storage for user defined variables, for the system stack, general purpose register banks and even for code. A register bank can consist of up to 16 wordwide (R0 to R15) and/or bytewide (RL0, RH0, ..., RL7, RH7) so-called General Purpose Registers (GPRs).

1024 bytes ( $2 \times 512$  bytes) of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are wordwide registers which are used for controlling and monitoring functions of the different on-chip units. Unused SFR addresses are reserved for future members of the C166 Family.

In order to meet the needs of designs where more memory is required than is provided on chip, up to 4 MBytes of external RAM and/or ROM can be connected to the microcontroller.

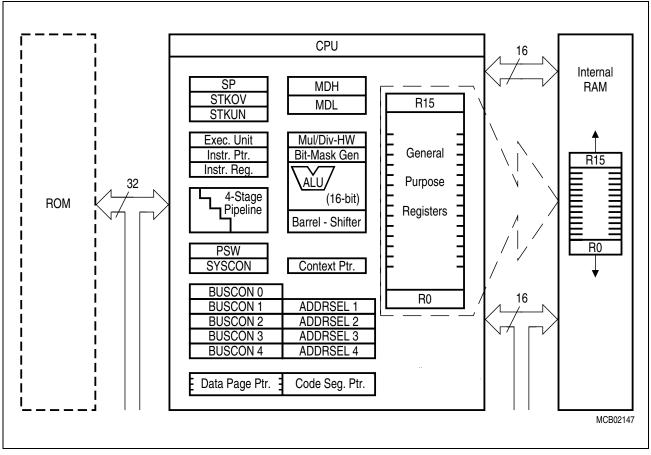

#### **Central Processing Unit (CPU)**

The main core of the CPU consists of a 4-stage instruction pipeline, a 16-bit arithmetic and logic unit (ALU) and dedicated SFRs. Additional hardware has been spent for a separate multiply and divide unit, a bit-mask generator and a barrel shifter.

Based on these hardware provisions, most of the C161K/O's instructions can be executed in just one machine cycle which requires 80 ns at 25 MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle independent of the number of bits to be shifted. All multiple-cycle instructions have been optimized so that they can be executed very fast as well: branches in 2 cycles, a  $16 \times 16$  bit multiplication in 5 cycles and a 32-/16 bit division in 10 cycles. Another pipeline optimization, the so-called 'Jump Cache', allows reducing the execution time of repeatedly performed jumps in a loop from 2 cycles to 1 cycle.

Figure 4

**CPU Block Diagram**

$2C_{H}$

$2D_{H}$

2E<sub>H</sub>

$2F_{H}$

00'00B0<sub>H</sub>

00'00B4<sub>H</sub>

00'00B8<sub>H</sub>

00'00BC<sub>H</sub>

| Table 3 C161K/O                            | Interrupt No    | odes           |                     |                      |                 |

|--------------------------------------------|-----------------|----------------|---------------------|----------------------|-----------------|

| Source of Interrupt or PEC Service Request | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location   | Trap<br>Number  |

| External Interrupt 1                       | CC9IR           | CC9IE          | CC9INT              | 00'0064 <sub>H</sub> | 19 <sub>H</sub> |

| External Interrupt 2                       | CC10IR          | CC10IE         | CC10INT             | 00'0068 <sub>H</sub> | 1A <sub>H</sub> |

| External Interrupt 3                       | CC11IR          | CC11IE         | CC11INT             | 00'006C <sub>H</sub> | 1B <sub>H</sub> |

| External Interrupt 4                       | CC12IR          | CC12IE         | CC12INT             | 00'0070 <sub>H</sub> | 1C <sub>H</sub> |

| External Interrupt 5                       | CC13IR          | CC13IE         | CC13INT             | 00'0074 <sub>H</sub> | 1D <sub>H</sub> |

| External Interrupt 6                       | CC14IR          | CC14IE         | CC14INT             | 00'0078 <sub>H</sub> | 1E <sub>H</sub> |

| External Interrupt 7                       | CC15IR          | CC15IE         | CC15INT             | 00'007C <sub>H</sub> | 1F <sub>H</sub> |

| GPT1 Timer 2                               | T2IR            | T2IE           | T2INT               | 00'0088 <sub>H</sub> | 22 <sub>H</sub> |

| GPT1 Timer 3                               | T3IR            | T3IE           | T3INT               | 00'008C <sub>H</sub> | 23 <sub>H</sub> |

| GPT1 Timer 4                               | T4IR            | T4IE           | T4INT               | 00'0090 <sub>H</sub> | 24 <sub>H</sub> |

| GPT2 Timer 5                               | T5IR            | T5IE           | T5INT               | 00'0094 <sub>H</sub> | 25 <sub>H</sub> |

| GPT2 Timer 6                               | T6IR            | T6IE           | T6INT               | 00'0098 <sub>H</sub> | 26 <sub>H</sub> |

| GPT2 CAPREL Reg.                           | CRIR            | CRIE           | CRINT               | 00'009C <sub>H</sub> | 27 <sub>H</sub> |

| ASC0 Transmit                              | S0TIR           | S0TIE          | SOTINT              | 00'00A8 <sub>H</sub> | 2A <sub>H</sub> |

| ASC0 Transmit Buffer                       | S0TBIR          | SOTBIE         | SOTBINT             | 00'011C <sub>H</sub> | 47 <sub>H</sub> |

| ASC0 Receive                               | S0RIR           | SORIE          | SORINT              | 00'00AC <sub>H</sub> | 2B <sub>H</sub> |

S0EIR

**SCTIR**

**SCRIR**

**SCEIR**

#### C161K/O Interrupt Nodes Table 3

Note: The shaded interrupt nodes are only available in the C1610, not in the C161K.

S0EIE

SCTIE

SCRIE

SCEIE

**SOEINT**

SCTINT

SCRINT

SCEINT

SSC Transmit

**SSC** Receive

SSC Error

ASC0 Error

#### **Special Function Registers Overview**

The following table lists all SFRs which are implemented in the C161K/O in alphabetical order.

**Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-peripherals are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

Note: The shaded registers are only available in the C161O, not in the C161K.

| Name     |   | Physical<br>Address | 8-Bit<br>Addr.  | Description                            | Reset<br>Value    |

|----------|---|---------------------|-----------------|----------------------------------------|-------------------|

| ADDRSEL1 |   | FE18 <sub>H</sub>   | 0C <sub>H</sub> | Address Select Register 1              | 0000 <sub>H</sub> |

| ADDRSEL2 | 2 | FE1A <sub>H</sub>   | 0D <sub>H</sub> | Address Select Register 2              | 0000 <sub>H</sub> |

| ADDRSEL  | 3 | FE1C <sub>H</sub>   | 0E <sub>H</sub> | Address Select Register 3              | 0000 <sub>H</sub> |

| ADDRSEL4 | ŀ | FE1E <sub>H</sub>   | 0F <sub>H</sub> | Address Select Register 4              | 0000 <sub>H</sub> |

| BUSCON0  | b | FF0C <sub>H</sub>   | 86 <sub>H</sub> | Bus Configuration Register 0           | 0XX0 <sub>H</sub> |

| BUSCON1  | b | FF14 <sub>H</sub>   | 8A <sub>H</sub> | Bus Configuration Register 1           | 0000 <sub>H</sub> |

| BUSCON2  | b | FF16 <sub>H</sub>   | 8B <sub>H</sub> | Bus Configuration Register 2           | 0000 <sub>H</sub> |

| BUSCON3  | b | FF18 <sub>H</sub>   | 8C <sub>H</sub> | Bus Configuration Register 3           | 0000 <sub>H</sub> |

| BUSCON4  | b | FF1A <sub>H</sub>   | 8D <sub>H</sub> | Bus Configuration Register 4           | 0000 <sub>H</sub> |

| CAPREL   |   | FE4A <sub>H</sub>   | 25 <sub>H</sub> | GPT2 Capture/Reload Register           | 0000 <sub>H</sub> |

| CC10IC   | b | FF8C <sub>H</sub>   | C6 <sub>H</sub> | EX2IN Interrupt Control Register       | 0000 <sub>H</sub> |

| CC11IC   | b | FF8E <sub>H</sub>   | C7 <sub>H</sub> | EX3IN Interrupt Control Register       | 0000 <sub>H</sub> |

| CC12IC   | b | FF90 <sub>H</sub>   | C8 <sub>H</sub> | EX4IN Interrupt Control Register       | 0000 <sub>H</sub> |

| CC13IC   | b | FF92 <sub>H</sub>   | C9 <sub>H</sub> | EX5IN Interrupt Control Register       | 0000 <sub>H</sub> |

| CC14IC   | b | FF94 <sub>H</sub>   | CA <sub>H</sub> | EX6IN Interrupt Control Register       | 0000 <sub>H</sub> |

| CC15IC   | b | FF96 <sub>H</sub>   | CB <sub>H</sub> | EX7IN Interrupt Control Register       | 0000 <sub>H</sub> |

| CC9IC    | b | FF8A <sub>H</sub>   | C5 <sub>H</sub> | EX1IN Interrupt Control Register       | 0000 <sub>H</sub> |

| СР       |   | FE10 <sub>H</sub>   | 08 <sub>H</sub> | CPU Context Pointer Register           | FC00 <sub>H</sub> |

| CRIC     | b | FF6A <sub>H</sub>   | B5 <sub>H</sub> | GPT2 CAPREL Interrupt Ctrl. Reg.       | 0000 <sub>H</sub> |

| CSP      |   | FE08 <sub>H</sub>   | 04 <sub>H</sub> | CPU Code Seg. Pointer Reg. (read only) | 0000 <sub>H</sub> |

Table 6

C161K/O Registers, Ordered by Name

| Table 6 | C161K/O Registers, Ordered by Name (cont'd) |

|---------|---------------------------------------------|

|---------|---------------------------------------------|

| Name    |   | Physica<br>Address |   | 8-Bit<br>Addr.  | Description                             | Reset<br>Value    |

|---------|---|--------------------|---|-----------------|-----------------------------------------|-------------------|

| DP0H    | b | F102 <sub>H</sub>  | Е | 81 <sub>H</sub> | P0H Direction Control Register          | 00 <sub>H</sub>   |

| DP0L    | b | F100 <sub>H</sub>  | Ε | 80 <sub>H</sub> | P0L Direction Control Register          | 00 <sub>H</sub>   |

| DP1H    | b | F106 <sub>H</sub>  | Ε | 83 <sub>H</sub> | P1H Direction Control Register          | 00 <sub>H</sub>   |

| DP1L    | b | F104 <sub>H</sub>  | Ε | 82 <sub>H</sub> | P1L Direction Control Register          | 00 <sub>H</sub>   |

| DP2     | b | FFC2 <sub>H</sub>  |   | E1 <sub>H</sub> | Port 2 Direction Control Register       | 0000 <sub>H</sub> |

| DP3     | b | FFC6 <sub>H</sub>  |   | E3 <sub>H</sub> | Port 3 Direction Control Register       | 0000 <sub>H</sub> |

| DP4     | b | FFCA <sub>H</sub>  |   | E5 <sub>H</sub> | Port 4 Direction Control Register       | 00 <sub>H</sub>   |

| DP6     | b | FFCE <sub>H</sub>  |   | E7 <sub>H</sub> | Port 6 Direction Control Register       | 00 <sub>H</sub>   |

| DPP0    |   | FE00 <sub>H</sub>  |   | 00 <sub>H</sub> | CPU Data Page Pointer 0 Reg. (10 bits)  | 0000 <sub>H</sub> |

| DPP1    |   | FE02 <sub>H</sub>  |   | 01 <sub>H</sub> | CPU Data Page Pointer 1 Reg. (10 bits)  | 0001 <sub>H</sub> |

| DPP2    |   | FE04 <sub>H</sub>  |   | 02 <sub>H</sub> | CPU Data Page Pointer 2 Reg. (10 bits)  | 0002 <sub>H</sub> |

| DPP3    |   | FE06 <sub>H</sub>  |   | 03 <sub>H</sub> | CPU Data Page Pointer 3 Reg. (10 bits)  | 0003 <sub>H</sub> |

| EXICON  | b | F1C0 <sub>H</sub>  | Ε | E0 <sub>H</sub> | External Interrupt Control Register     | 0000 <sub>H</sub> |

| IDCHIP  |   | F07C <sub>H</sub>  | Ε | 3E <sub>H</sub> | Identifier                              | 05XX <sub>H</sub> |

| IDMANUF |   | F07E <sub>H</sub>  | Ε | 3F <sub>H</sub> | Identifier                              | 1820 <sub>H</sub> |

| IDMEM   |   | F07A <sub>H</sub>  | Ε | 3D <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |

| IDMEM2  |   | F076 <sub>H</sub>  | Ε | 3B <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |

| IDPROG  |   | F078 <sub>H</sub>  | Ε | 3C <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |

| MDC     | b | FF0E <sub>H</sub>  |   | 87 <sub>H</sub> | CPU Multiply Divide Control Register    | 0000 <sub>H</sub> |

| MDH     |   | FE0C <sub>H</sub>  |   | 06 <sub>H</sub> | CPU Multiply Divide Reg. – High Word    | 0000 <sub>H</sub> |

| MDL     |   | FE0E <sub>H</sub>  |   | 07 <sub>H</sub> | CPU Multiply Divide Reg. – Low Word     | 0000 <sub>H</sub> |

| ODP2    | b | F1C2 <sub>H</sub>  | Ε | E1 <sub>H</sub> | Port 2 Open Drain Control Register      | 0000 <sub>H</sub> |

| ODP3    | b | F1C6 <sub>H</sub>  | Ε | E3 <sub>H</sub> | Port 3 Open Drain Control Register      | 0000 <sub>H</sub> |

| ODP6    | b | F1CE <sub>H</sub>  | Ε | E7 <sub>H</sub> | Port 6 Open Drain Control Register      | 00 <sub>H</sub>   |

| ONES    | b | FF1E <sub>H</sub>  |   | 8F <sub>H</sub> | Constant Value 1's Register (read only) | FFFF <sub>H</sub> |

| P0H     | b | FF02 <sub>H</sub>  |   | 81 <sub>H</sub> | Port 0 High Reg. (Upper half of PORT0)  | 00 <sub>H</sub>   |

| P0L     | b | FF00 <sub>H</sub>  |   | 80 <sub>H</sub> | Port 0 Low Reg. (Lower half of PORT0)   | 00 <sub>H</sub>   |

| P1H     | b | FF06 <sub>H</sub>  |   | 83 <sub>H</sub> | Port 1 High Reg. (Upper half of PORT1)  | 00 <sub>H</sub>   |

| P1L     | b | FF04 <sub>H</sub>  |   | 82 <sub>H</sub> | Port 1 Low Reg.(Lower half of PORT1)    | 00 <sub>H</sub>   |

| P2      | b | FFC0 <sub>H</sub>  |   | E0 <sub>H</sub> | Port 2 Register                         | 0000 <sub>H</sub> |

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C161K/ O and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C161K/O will provide signals with the respective timing characteristics.

#### SR (System Requirement):

The external system must provide signals with the respective timing characteristics to the C161K/O.

#### DC Characteristics (Standard Supply Voltage Range)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                          | Symbol                          | Limit Values                 |                              | Unit | Test Condition                                  |  |

|----------------------------------------------------------------------------------------------------|---------------------------------|------------------------------|------------------------------|------|-------------------------------------------------|--|

|                                                                                                    |                                 | min.                         | max.                         |      |                                                 |  |

| Input low voltage (TTL,<br>all except XTAL1)                                                       | V <sub>IL</sub> SR              | -0.5                         | 0.2 V <sub>DD</sub><br>- 0.1 | V    | _                                               |  |

| Input low voltage XTAL1                                                                            | $V_{IL2}$ SR                    | -0.5                         | 0.3 V <sub>DD</sub>          | V    | -                                               |  |

| Input high voltage (TTL,<br>all except RSTIN and XTAL1)                                            | V <sub>IH</sub> SR              | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> +<br>0.5     | V    | _                                               |  |

| Input high voltage RSTIN<br>(when operated as input)                                               | V <sub>IH1</sub> SR             | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input high voltage XTAL1                                                                           | V <sub>IH2</sub> SR             | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                               |  |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT,<br>RSTIN <sup>2)</sup> ) | V <sub>OL</sub> CC              | _                            | 0.45                         | V    | I <sub>OL</sub> = 2.4 mA                        |  |

| Output low voltage<br>(all other outputs)                                                          | V <sub>OL1</sub> CC             | _                            | 0.45                         | V    | <i>I</i> <sub>OL</sub> = 1.6 mA                 |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH</sub> CC              | 2.4                          | _                            | V    | I <sub>OH</sub> = -2.4 mA                       |  |

| (PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT)                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = -0.5 mA                       |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH1</sub> CC             | 2.4                          | _                            | V    | I <sub>OH</sub> = -1.6 mA                       |  |

| (all other outputs)                                                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = -0.5 mA                       |  |

| Input leakage current (Port 5)                                                                     | I <sub>OZ1</sub> CC             | -                            | ±200                         | nA   | $0 V < V_{IN} < V_{DD}$                         |  |

| Input leakage current (all other)                                                                  | I <sub>OZ2</sub> CC             | -                            | ±500                         | nA   | $0.45 \text{ V} < V_{\text{IN}} < V_{\text{C}}$ |  |

| RSTIN inactive current <sup>4)</sup>                                                               | I <sub>RSTH</sub> <sup>5)</sup> | _                            | -10                          | μA   | $V_{\rm IN} = V_{\rm IH1}$                      |  |

# DC Characteristics (Reduced Supply Voltage Range) (Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                          | Symbol                        |         | Limit '             | Values                | Unit | Test Condition                                   |  |

|----------------------------------------------------------------------------------------------------|-------------------------------|---------|---------------------|-----------------------|------|--------------------------------------------------|--|

|                                                                                                    |                               |         | min.                | max.                  |      |                                                  |  |

| Input low voltage (TTL,<br>all except XTAL1)                                                       | $V_{IL}$                      | SR      | -0.5                | 0.8                   | V    | _                                                |  |

| Input low voltage XTAL1                                                                            | $V_{IL2}$                     | SR      | -0.5                | 0.3 V <sub>DD</sub>   | V    | -                                                |  |

| Input high voltage (TTL, all except RSTIN and XTAL1)                                               | $V_{IH}$                      | SR      | 1.8                 | V <sub>DD</sub> + 0.5 | V    | _                                                |  |

| Input high voltage RSTIN<br>(when operated as input)                                               | V <sub>IH1</sub>              | SR      | 0.6 V <sub>DD</sub> | V <sub>DD</sub> + 0.5 | V    | _                                                |  |

| Input high voltage XTAL1                                                                           | V <sub>IH2</sub>              | SR      | 0.7 V <sub>DD</sub> | V <sub>DD</sub> + 0.5 | V    | -                                                |  |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT,<br>RSTIN <sup>2)</sup> ) | V <sub>OL</sub>               | CC      | -                   | 0.45                  | V    | I <sub>OL</sub> = 1.6 mA                         |  |

| Output low voltage<br>(all other outputs)                                                          | V <sub>OL1</sub>              | CC      | _                   | 0.45                  | V    | <i>I</i> <sub>OL</sub> = 1.0 mA                  |  |

| Output high voltage <sup>3)</sup><br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT)           | V <sub>OH</sub>               | CC      | 0.9 V <sub>DD</sub> | _                     | V    | I <sub>OH</sub> = -0.5 mA                        |  |

| Output high voltage <sup>3)</sup><br>(all other outputs)                                           | V <sub>OH1</sub>              | CC      | 0.9 V <sub>DD</sub> | _                     | V    | I <sub>OH</sub> = -0.25 mA                       |  |

| Input leakage current (Port 5)                                                                     | I <sub>OZ1</sub>              | CC      | _                   | ±200                  | nA   | $0 V < V_{IN} < V_{DD}$                          |  |

| Input leakage current (all other)                                                                  | 011                           |         | _                   | ±500                  | nA   | $0.45 \text{ V} < V_{\text{IN}} < V_{\text{DD}}$ |  |

| RSTIN inactive current <sup>4)</sup>                                                               | I <sub>RSTF</sub>             | 5)<br>I | _                   | -10                   | μA   | $V_{\rm IN} = V_{\rm IH1}$                       |  |

| RSTIN active current <sup>4)</sup>                                                                 | I <sub>RSTL</sub>             | 6)      | -100                | _                     | μA   | $V_{\rm IN} = V_{\rm IL}$                        |  |

| RD/WR inact. current <sup>7)</sup>                                                                 | I <sub>RWH</sub>              | 5)      | _                   | -10                   | μA   | $V_{OUT}$ = 2.4 V                                |  |

| RD/WR active current <sup>7)</sup>                                                                 | I <sub>RWL</sub> <sup>6</sup> | 5)      | -500                | -                     | μA   | $V_{OUT} = V_{OLmax}$                            |  |

| ALE inactive current <sup>7)</sup>                                                                 | IALEL                         | 5)      | _                   | 20                    | μA   | $V_{OUT} = V_{OLmax}$                            |  |

| ALE active current <sup>7)</sup>                                                                   | $I_{ALEH}$                    | 6)      | 500                 | _                     | μA   | $V_{OUT}$ = 2.4 V                                |  |

| Port 6 inactive current <sup>7)</sup>                                                              | I <sub>P6H</sub> 5            | )       | _                   | -10                   | μA   | $V_{OUT}$ = 2.4 V                                |  |

| Port 6 active current <sup>7)</sup>                                                                | $I_{P6L}^{6)}$                | )       | -500                | _                     | μA   | $V_{OUT} = V_{OL1max}$                           |  |

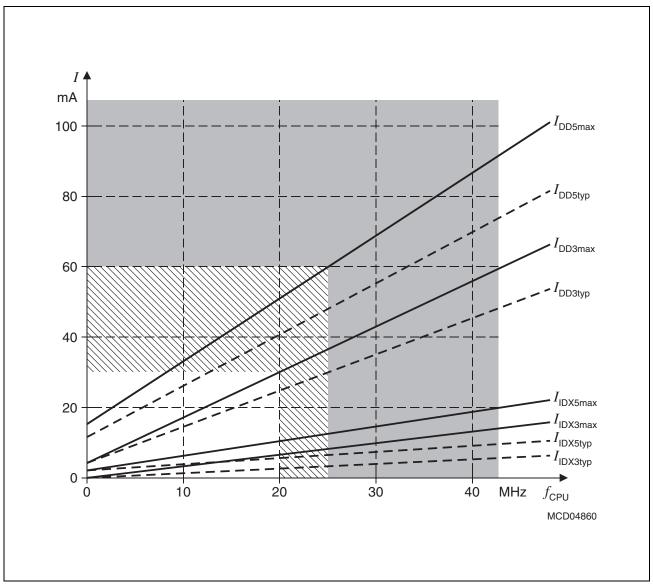

Figure 7 Supply/Idle Current as a Function of Operating Frequency

| Table 9             | CIGINO CIUCK                                                                                               | Generation modes |                            |

|---------------------|------------------------------------------------------------------------------------------------------------|------------------|----------------------------|

| CLKCFG<br>(P0H.7-5) | $\begin{array}{c} \textbf{CPU Frequency} \\ f_{\text{CPU}} = f_{\text{OSC}} \times \textbf{F} \end{array}$ |                  | Notes                      |

| 0 X X               | $f_{OSC} \times 1$                                                                                         | 1 to 25 MHz      | Direct drive <sup>1)</sup> |

| 1 X X               | f <sub>OSC</sub> / 2                                                                                       | 2 to 50 MHz      | CPU clock via prescaler    |

| Table 9 | C161K/O Clock Generation Modes |

|---------|--------------------------------|

|---------|--------------------------------|

<sup>1)</sup> The maximum frequency depends on the duty cycle of the external clock signal.

#### **Prescaler Operation**

When prescaler operation is configured (CLKCFG =  $1XX_B$ ) the CPU clock is derived from the internal oscillator (input clock signal) by a 2:1 prescaler.

The frequency of  $f_{CPU}$  is half the frequency of  $f_{OSC}$  and the high and low time of  $f_{CPU}$  (i.e. the duration of an individual TCL) is defined by the period of the input clock  $f_{OSC}$ .

The timings listed in the AC Characteristics that refer to TCLs therefore can be calculated using the period of  $f_{OSC}$  for any TCL.

#### **Direct Drive**

When direct drive is configured (CLKCFG =  $0XX_B$ ) the CPU clock is directly driven from the internal oscillator with the input clock signal.

The frequency of  $f_{CPU}$  directly follows the frequency of  $f_{OSC}$  so the high and low time of  $f_{CPU}$  (i.e. the duration of an individual TCL) is defined by the duty cycle of the input clock  $f_{OSC}$ .

The timings listed below that refer to TCLs therefore must be calculated using the minimum TCL that is possible under the respective circumstances. This minimum value can be calculated via the following formula:

$TCL_{min} = 1/f_{OSC} \times DC_{min}$  (DC = duty cycle)

For two consecutive TCLs the deviation caused by the duty cycle of  $f_{OSC}$  is compensated so the duration of 2TCL is always  $1/f_{OSC}$ . The minimum value TCL<sub>min</sub> therefore has to be used only once for timings that require an odd number of TCLs (1, 3, ...). Timings that require an even number of TCLs (2, 4, ...) may use the formula 2TCL =  $1/f_{OSC}$ .

#### **AC Characteristics**

## Table 10External Clock Drive XTAL1 (Standard Supply Voltage Range)<br/>(Operating Conditions apply)

| Parameter               | Symbol                |    | Direct Drive<br>1:1 |      | P    | Unit |    |

|-------------------------|-----------------------|----|---------------------|------|------|------|----|

|                         |                       |    | min.                | max. | min. | max. |    |

| Oscillator period       | t <sub>OSC</sub>      | SR | 40                  | -    | 20   | _    | ns |

| High time <sup>1)</sup> | t <sub>1</sub>        | SR | 20 <sup>2)</sup>    | -    | 6    | _    | ns |

| Low time <sup>1)</sup>  | <i>t</i> <sub>2</sub> | SR | 20 <sup>2)</sup>    | -    | 6    | _    | ns |

| Rise time <sup>1)</sup> | t <sub>3</sub>        | SR | _                   | 10   | _    | 6    | ns |

| Fall time <sup>1)</sup> | <i>t</i> <sub>4</sub> | SR | _                   | 10   | -    | 6    | ns |

<sup>1)</sup> The clock input signal must reach the defined levels  $V_{\text{IL2}}$  and  $V_{\text{IH2}}$ .

<sup>2)</sup> The minimum high and low time refers to a duty cycle of 50%. The maximum operating frequency ( $f_{CPU}$ ) in direct drive mode depends on the duty cycle of the clock input signal.

# Table 11External Clock Drive XTAL1 (Reduced Supply Voltage Range)<br/>(Operating Conditions apply)

| Parameter               | Symbol                |    | Dire             | ct Drive<br>1:1 | P    | Prescaler<br>2:1 |    |  |

|-------------------------|-----------------------|----|------------------|-----------------|------|------------------|----|--|

|                         |                       |    | min.             | max.            | min. | max.             |    |  |

| Oscillator period       | t <sub>OSC</sub>      | SR | 50               | -               | 25   | -                | ns |  |

| High time <sup>1)</sup> | <i>t</i> <sub>1</sub> | SR | 25 <sup>2)</sup> | -               | 8    | -                | ns |  |

| Low time <sup>1)</sup>  | <i>t</i> <sub>2</sub> | SR | 25 <sup>2)</sup> | -               | 8    | _                | ns |  |

| Rise time <sup>1)</sup> | t <sub>3</sub>        | SR | -                | 10              | -    | 6                | ns |  |

| Fall time <sup>1)</sup> | <i>t</i> <sub>4</sub> | SR | _                | 10              | _    | 6                | ns |  |

<sup>1)</sup> The clock input signal must reach the defined levels  $V_{\text{IL2}}$  and  $V_{\text{IH2}}$ .

<sup>2)</sup> The minimum high and low time refers to a duty cycle of 50%. The maximum operating frequency ( $f_{CPU}$ ) in direct drive mode depends on the duty cycle of the clock input signal.

## Multiplexed Bus (Reduced Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (150 ns at 20 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                 |    | Max. CPU Clock<br>= 20 MHz |                            | Variable (<br>1 / 2TCL =             | Unit                                                           |    |

|----------------------------------------------------------------------------------------|------------------------|----|----------------------------|----------------------------|--------------------------------------|----------------------------------------------------------------|----|

|                                                                                        |                        |    | min.                       | max.                       | min.                                 | max.                                                           |    |

| Data float after RD                                                                    | t <sub>19</sub>        | SR | _                          | $36 + t_{\rm F}$           | -                                    | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>                           | ns |

| Data valid to $\overline{WR}$                                                          | t <sub>22</sub>        | CC | $24 + t_{\rm C}$           | -                          | 2TCL - 26<br>+ <i>t</i> <sub>C</sub> | -                                                              | ns |

| Data hold after WR                                                                     | t <sub>23</sub>        | CC | $36 + t_{F}$               | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | _                                                              | ns |

| ALE rising edge after $\overline{\text{RD}}$ , $\overline{\text{WR}}$                  | t <sub>25</sub>        | CC | $36 + t_{F}$               | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                              | ns |

| Address hold after RD,<br>WR                                                           | t <sub>27</sub>        | CC | $36 + t_{F}$               | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                              | ns |

| ALE falling edge to $\overline{\text{CS}}^{1)}$                                        | t <sub>38</sub>        | CC | -8 - t <sub>A</sub>        | 10 - <i>t</i> <sub>A</sub> | -8 - <i>t</i> <sub>A</sub>           | 10 - <i>t</i> <sub>A</sub>                                     | ns |

| CS low to Valid Data In <sup>1)</sup>                                                  | t <sub>39</sub>        | SR | _                          | $47+t_{C} + 2t_{A}$        | _                                    | 3TCL - 28<br>+ <i>t</i> <sub>C</sub> + 2 <i>t</i> <sub>A</sub> | ns |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{1)}$ | <i>t</i> <sub>40</sub> | CC | 57 + <i>t</i> <sub>F</sub> | -                          | 3TCL - 18<br>+ <i>t</i> <sub>F</sub> | _                                                              | ns |

| ALE fall. edge to RdCS,<br>WrCS (with RW delay)                                        | t <sub>42</sub>        | CC | 19 + <i>t</i> <sub>A</sub> | -                          | TCL - 6<br>+ <i>t</i> <sub>A</sub>   | _                                                              | ns |

| ALE fall. edge to RdCS,<br>WrCS (no RW delay)                                          | t <sub>43</sub>        | CC | $-6 + t_{A}$               | -                          | -6<br>+ <i>t</i> <sub>A</sub>        | _                                                              | ns |

| Address float after RdCS,<br>WrCS (with RW delay)                                      | t <sub>44</sub>        | CC | _                          | 0                          | _                                    | 0                                                              | ns |

| Address float after RdCS,<br>WrCS (no RW delay)                                        | t <sub>45</sub>        | CC | _                          | 25                         | -                                    | TCL                                                            | ns |

| RdCS to Valid Data In (with RW delay)                                                  | t <sub>46</sub>        | SR | _                          | $20 + t_{\rm C}$           | -                                    | 2TCL - 30<br>+ <i>t</i> <sub>C</sub>                           | ns |

| RdCS to Valid Data In (no RW delay)                                                    | t <sub>47</sub>        | SR | _                          | $45 + t_{\rm C}$           | -                                    | 3TCL - 30<br>+ <i>t</i> <sub>C</sub>                           | ns |

| RdCS, WrCS Low Time<br>(with RW delay)                                                 | t <sub>48</sub>        | CC | $38 + t_{\rm C}$           | -                          | 2TCL - 12<br>+ <i>t</i> <sub>C</sub> | -                                                              | ns |

| RdCS, WrCS Low Time<br>(no RW delay)                                                   | t <sub>49</sub>        | CC | 63 + <i>t</i> <sub>C</sub> | -                          | 3TCL - 12<br>+ <i>t</i> <sub>C</sub> | -                                                              | ns |

## Multiplexed Bus, No Read/Write Delay, Extended ALE

## **AC Characteristics**

### Demultiplexed Bus (Standard Supply Voltage Range)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                   | Symbol                 |    | Max. CPU Clock<br>= 25 MHz |                         | Variable (<br>1 / 2TCL =             | Unit                                                         |    |

|-----------------------------------------------------------------------------|------------------------|----|----------------------------|-------------------------|--------------------------------------|--------------------------------------------------------------|----|

|                                                                             |                        |    | min.                       | max.                    | min.                                 | max.                                                         |    |

| ALE high time                                                               | <i>t</i> 5             | CC | $10 + t_{A}$               | -                       | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |

| Address setup to ALE                                                        | <i>t</i> <sub>6</sub>  | CC | $4 + t_A$                  | _                       | TCL - 16<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |

| ALE falling edge to $\overline{\text{RD}}$ ,<br>WR (with RW-delay)          | t <sub>8</sub>         | CC | $10 + t_{A}$               | -                       | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |

| ALE falling edge to $\overline{RD}$ ,<br>WR (no RW-delay)                   | t <sub>9</sub>         | CC | $-10 + t_{A}$              | _                       | -10<br>+ <i>t</i> <sub>A</sub>       | -                                                            | ns |

| RD, WR low time<br>(with RW-delay)                                          | t <sub>12</sub>        | CC | $30 + t_{\rm C}$           | -                       | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |

| RD, WR low time<br>(no RW-delay)                                            | t <sub>13</sub>        | CC | $50 + t_{\rm C}$           | -                       | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |

| RD to valid data in (with RW-delay)                                         | <i>t</i> <sub>14</sub> | SR | -                          | $20 + t_{\rm C}$        | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| RD to valid data in (no RW-delay)                                           | t <sub>15</sub>        | SR | -                          | $40 + t_{\rm C}$        | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| ALE low to valid data in                                                    | t <sub>16</sub>        | SR | _                          | $40 + t_{A} + t_{C}$    | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub> | ns |

| Address to valid data in                                                    | t <sub>17</sub>        | SR | _                          | $50 + 2t_A + t_C$       | _                                    | $4TCL - 30 + 2t_A + t_C$                                     | ns |

| Data hold after RD rising edge                                              | t <sub>18</sub>        | SR | 0                          | -                       | 0                                    | -                                                            | ns |

| Data float after $\overline{RD}$ rising edge (with RW-delay <sup>1)</sup> ) | t <sub>20</sub>        | SR | -                          | $26 + 2t_A + t_F^{(1)}$ | -                                    | 2TCL - 14<br>+ $22t_A$<br>+ $t_F^{(1)}$                      | ns |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )                | t <sub>21</sub>        | SR | -                          | $10 + 2t_A + t_F^{(1)}$ | _                                    | TCL - 10<br>+ $22t_A$<br>+ $t_F^{(1)}$                       | ns |

### Demultiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                    |                            | PU Clock<br>5 MHz             | Variable (<br>1 / 2TCL =             | Unit                                                           |    |

|----------------------------------------------------------------------------------------|---------------------------|----------------------------|-------------------------------|--------------------------------------|----------------------------------------------------------------|----|

|                                                                                        |                           | min.                       | max.                          | min.                                 | max.                                                           |    |

| Data valid to $\overline{WR}$                                                          | t <sub>22</sub> CC        | $20 + t_{\rm C}$           | -                             | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | _                                                              | ns |

| Data hold after $\overline{WR}$                                                        | t <sub>24</sub> CC        | 10 + <i>t</i> <sub>F</sub> | -                             | TCL - 10<br>+ <i>t</i> <sub>F</sub>  | -                                                              | ns |

| ALE rising edge after<br>RD, WR                                                        | <i>t</i> <sub>26</sub> CC | $-10 + t_{F}$              | -                             | -10 + <i>t</i> <sub>F</sub>          | -                                                              | ns |

| Address hold after $\overline{WR}^{2)}$                                                | t <sub>28</sub> CC        | $0 + t_{F}$                | -                             | $0 + t_{F}$                          | -                                                              | ns |

| ALE falling edge to $\overline{CS}^{3)}$                                               | t <sub>38</sub> CC        | -4 - t <sub>A</sub>        | 10 - <i>t</i> <sub>A</sub>    | -4 - t <sub>A</sub>                  | 10 - <i>t</i> <sub>A</sub>                                     | ns |

| CS low to Valid Data In <sup>3)</sup>                                                  | <i>t</i> <sub>39</sub> SR | _                          | $40 + t_{\rm C} + 2t_{\rm A}$ | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub> + 2 <i>t</i> <sub>A</sub> | ns |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{3)}$ | <i>t</i> <sub>41</sub> CC | $6 + t_{F}$                | -                             | TCL - 14<br>+ <i>t</i> <sub>F</sub>  | _                                                              | ns |

| ALE falling edge to<br>RdCS, WrCS (with RW-<br>delay)                                  | t <sub>42</sub> CC        | 16 + <i>t</i> <sub>A</sub> | -                             | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | -                                                              | ns |

| ALE falling edge to<br>RdCS, WrCS (no RW-<br>delay)                                    | t <sub>43</sub> CC        | $-4 + t_{A}$               | _                             | $-4$ + $t_A$                         | _                                                              | ns |

| RdCS to Valid Data In (with RW-delay)                                                  | <i>t</i> <sub>46</sub> SR | _                          | 16 + <i>t</i> <sub>C</sub>    | _                                    | 2TCL - 24<br>+ <i>t</i> <sub>C</sub>                           | ns |

| RdCS to Valid Data In (no RW-delay)                                                    | <i>t</i> <sub>47</sub> SR | _                          | $36 + t_{\rm C}$              | _                                    | 3TCL - 24<br>+ <i>t</i> <sub>C</sub>                           | ns |

| RdCS, WrCS Low Time<br>(with RW-delay)                                                 | <i>t</i> <sub>48</sub> CC | $30 + t_{\rm C}$           | -                             | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                              | ns |

| RdCS, WrCS Low Time<br>(no RW-delay)                                                   | t <sub>49</sub> CC        | $50 + t_{\rm C}$           | -                             | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                              | ns |

| Data valid to WrCS                                                                     | <i>t</i> <sub>50</sub> CC | $26 + t_{\rm C}$           | -                             | 2TCL - 14<br>+ <i>t</i> <sub>C</sub> | -                                                              | ns |

| Data hold after RdCS                                                                   | <i>t</i> <sub>51</sub> SR | 0                          | -                             | 0                                    | -                                                              | ns |

### Demultiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A + t_C + t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                              | Symbol          |    | Max. CPU Clock<br>= 25 MHz |                            | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                   | Unit |

|--------------------------------------------------------|-----------------|----|----------------------------|----------------------------|----------------------------------------------|-----------------------------------|------|

|                                                        |                 |    | min.                       | max.                       | min.                                         | max.                              |      |

| Data float after RdCS<br>(with RW-delay) <sup>1)</sup> | t <sub>53</sub> | SR | _                          | 20 + <i>t</i> <sub>F</sub> | _                                            | 2TCL - 20<br>+ $2t_A + t_F$<br>1) | ns   |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup>   | t <sub>68</sub> | SR | _                          | 0 + <i>t</i> <sub>F</sub>  | -                                            | TCL - 20<br>+ $2t_A + t_F$<br>1)  | ns   |

| Address hold after<br>RdCS, WrCS                       | t <sub>55</sub> | CC | -6 + <i>t</i> <sub>F</sub> | -                          | -6 + <i>t</i> <sub>F</sub>                   | -                                 | ns   |

| Data hold after WrCS                                   | t <sub>57</sub> | CC | 6 + <i>t</i> <sub>F</sub>  | -                          | TCL - 14<br>+ <i>t</i> <sub>F</sub>          | -                                 | ns   |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

### Demultiplexed Bus (Reduced Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A + t_C + t_F$  (100 ns at 20 MHz CPU clock without waitstates)

| Parameter                                              | Symbol          |    | Max. CPU Clock<br>= 20 MHz  |                           | Variable CPU Clock<br>1 / 2TCL = 1 to 20 MHz |                                   | Unit |

|--------------------------------------------------------|-----------------|----|-----------------------------|---------------------------|----------------------------------------------|-----------------------------------|------|

|                                                        |                 |    | min.                        | max.                      | min.                                         | max.                              |      |

| Data float after RdCS<br>(with RW-delay) <sup>1)</sup> | t <sub>53</sub> | SR | _                           | $30 + t_{\rm F}$          | -                                            | 2TCL - 20<br>+ $2t_A + t_F$<br>1) | ns   |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup>   | t <sub>68</sub> | SR | _                           | 5 + <i>t</i> <sub>F</sub> | -                                            | TCL - 20<br>+ $2t_A + t_F$<br>1)  | ns   |

| Address hold after<br>RdCS, WrCS                       | t <sub>55</sub> | CC | -16 + <i>t</i> <sub>F</sub> | -                         | -16 + <i>t</i> <sub>F</sub>                  | -                                 | ns   |

| Data hold after WrCS                                   | t <sub>57</sub> | CC | 9 + <i>t</i> <sub>F</sub>   | _                         | TCL - 16<br>+ <i>t</i> <sub>F</sub>          | _                                 | ns   |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

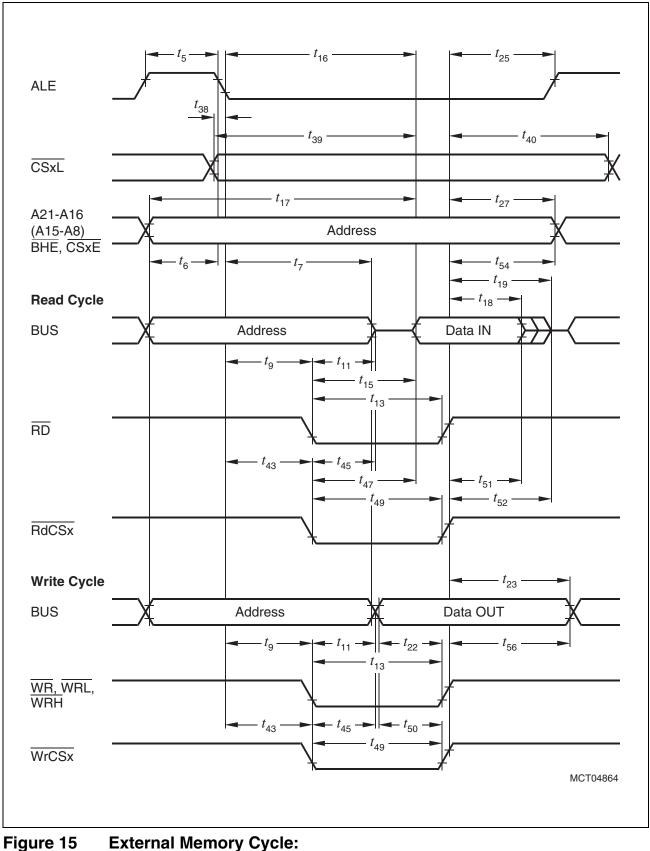

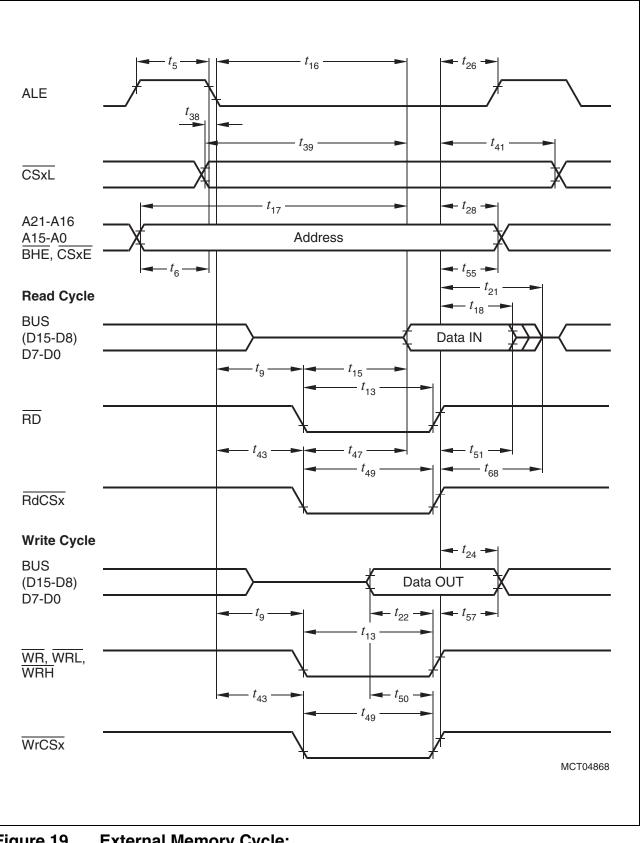

#### Figure 19 External Memory Cycle: Demultiplexed Bus, No Read/Write Delay, Extended ALE

## Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com