Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | POR, Voltage Detect, WDT                                                         |

| Number of I/O              | 41                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

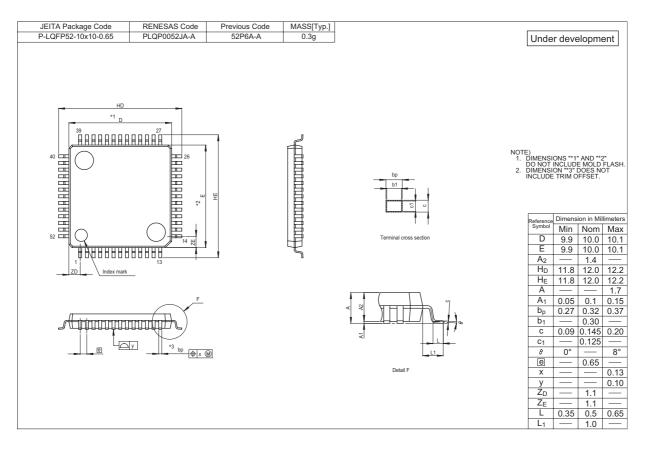

| Package / Case             | 52-LQFP                                                                          |

| Supplier Device Package    | 52-LQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f21256snfp-v2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### 1.4 **Product Information**

Table 1.3 lists the Product Information for R8C/24 Group and Table 1.4 lists the Product Information for R8C/25 Group.

Table 1.3 **Product Information for R8C/24 Group**

Current of Feb. 2008

| Type No.        | ROM Capacity | RAM Capacity | Package Type | Remarks                |

|-----------------|--------------|--------------|--------------|------------------------|

| R5F21244SNFP    | 16 Kbytes    | 1 Kbyte      | PLQP0052JA-A | N version              |

| R5F21245SNFP    | 24 Kbytes    | 2 Kbytes     | PLQP0052JA-A | Blank product          |

| R5F21246SNFP    | 32 Kbytes    | 2 Kbytes     | PLQP0052JA-A |                        |

| R5F21247SNFP    | 48 Kbytes    | 2.5 Kbytes   | PLQP0052JA-A |                        |

| R5F21248SNFP    | 64 Kbytes    | 3 Kbytes     | PLQP0052JA-A |                        |

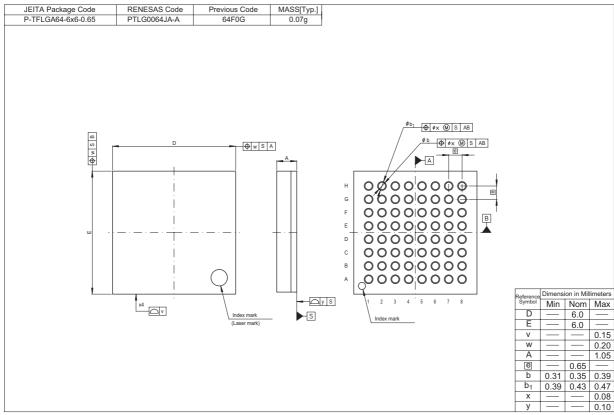

| R5F21244SNLG    | 16 Kbytes    | 1 Kbyte      | PTLG0064JA-A |                        |

| R5F21246SNLG    | 32 Kbytes    | 2 Kbytes     | PTLG0064JA-A |                        |

| R5F21244SDFP    | 16 Kbytes    | 1 Kbyte      | PLQP0052JA-A | D version              |

| R5F21245SDFP    | 24 Kbytes    | 2 Kbytes     | PLQP0052JA-A | Blank product          |

| R5F21246SDFP    | 32 Kbytes    | 2 Kbytes     | PLQP0052JA-A |                        |

| R5F21247SDFP    | 48 Kbytes    | 2.5 Kbytes   | PLQP0052JA-A |                        |

| R5F21248SDFP    | 64 Kbytes    | 3 Kbytes     | PLQP0052JA-A |                        |

| R5F21244SNXXXFP | 16 Kbytes    | 1 Kbyte      | PLQP0052JA-A | N version              |

| R5F21245SNXXXFP | 24 Kbytes    | 2 Kbytes     | PLQP0052JA-A | Factory                |

| R5F21246SNXXXFP | 32 Kbytes    | 2 Kbytes     | PLQP0052JA-A | programming            |

| R5F21247SNXXXFP | 48 Kbytes    | 2.5 Kbytes   | PLQP0052JA-A | product <sup>(1)</sup> |

| R5F21248SNXXXFP | 64 Kbytes    | 3 Kbytes     | PLQP0052JA-A | -                      |

| R5F21244SNXXXLG | 16 Kbytes    | 1 Kbyte      | PTLG0064JA-A |                        |

| R5F21246SNXXXLG | 32 Kbytes    | 2 Kbytes     | PTLG0064JA-A | -                      |

| R5F21244SDXXXFP | 16 Kbytes    | 1 Kbyte      | PLQP0052JA-A | D version              |

| R5F21245SDXXXFP | 24 Kbytes    | 2 Kbytes     | PLQP0052JA-A | Factory                |

| R5F21246SDXXXFP | 32 Kbytes    | 2 Kbytes     | PLQP0052JA-A | programming            |

| R5F21247SDXXXFP | 48 Kbytes    | 2.5 Kbytes   | PLQP0052JA-A | product <sup>(1)</sup> |

| R5F21248SDXXXFP | 64 Kbytes    | 3 Kbytes     | PLQP0052JA-A |                        |

### NOTE:

1. The user ROM is programmed before shipment.

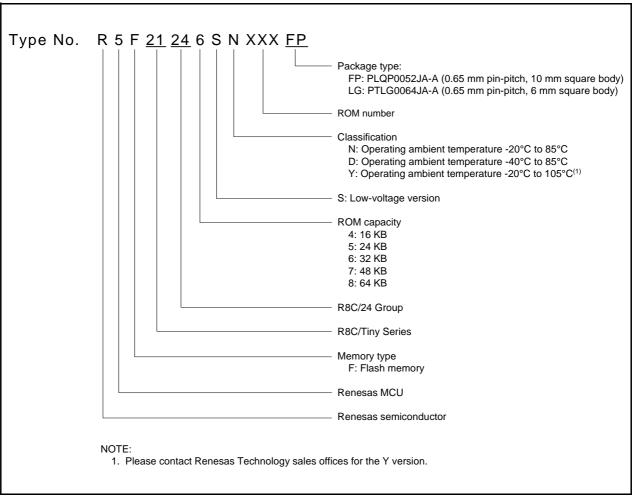

Figure 1.2 Type Number, Memory Size, and Package of R8C/24 Group

## 2. Central Processing Unit (CPU)

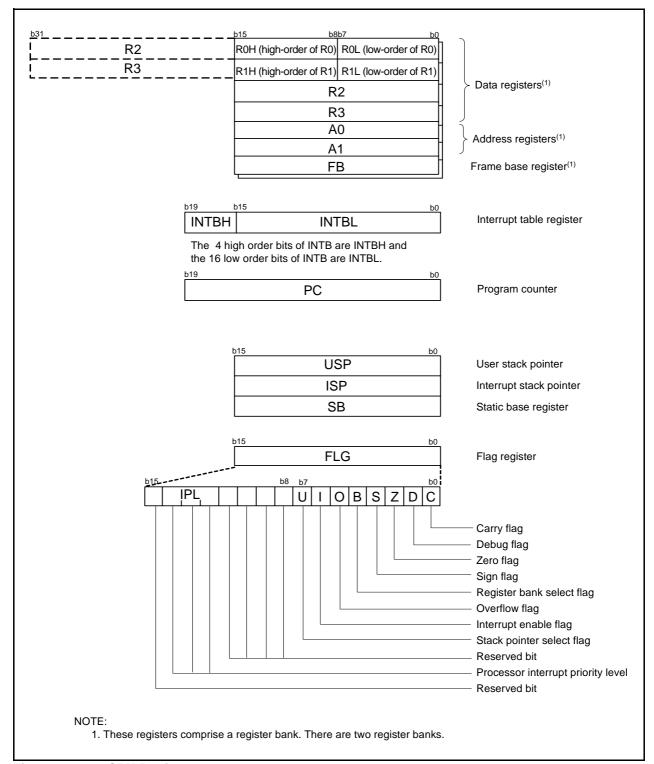

Figure 2.1 shows the CPU Registers. The CPU contains 13 registers. R0, R1, R2, R3, A0, A1, and FB configure a register bank. There are two sets of register bank.

Figure 2.1 CPU Registers

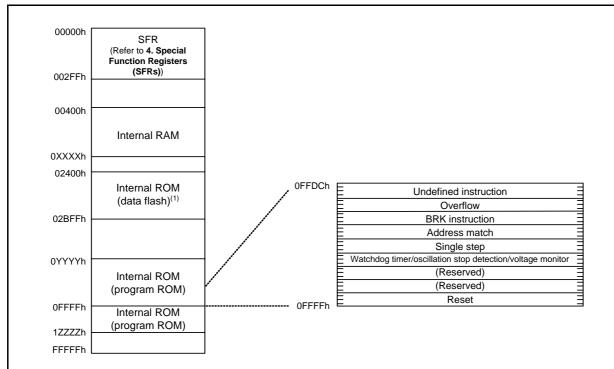

#### 3.2 R8C/25 Group

Figure 3.2 is a Memory Map of R8C/25 Group. The R8C/25 group has 1 Mbyte of address space from addresses 00000h to FFFFFh.

The internal ROM (program ROM) is allocated lower addresses, beginning with address 0FFFFh. For example, a 48-Kbyte internal ROM area is allocated addresses 04000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.

The internal ROM (data flash) is allocated addresses 02400h to 02BFFh.

The internal RAM area is allocated higher addresses, beginning with address 00400h. For example, a 2-Kbyte internal RAM is allocated addresses 00400h to 00BFFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.

Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.

NOTES:

- 1. Data flash block A (1 Kbyte) and B (1 Kbyte) are shown.

- 2. The blank regions are reserved. Do not access locations in these regions.

| 5                                                                                                 |           | Internal ROM   | Internal RAM   |            |                |

|---------------------------------------------------------------------------------------------------|-----------|----------------|----------------|------------|----------------|

| Part Number                                                                                       | Size      | Address 0YYYYh | Address 1ZZZZh | Size       | Address 0XXXXh |

| R5F21254SNFP, R5F21254SNXXXFP,<br>R5F21254SDFP, R5F21254SDXXXFP,<br>R5F21254SNLG, R5F21254SNXXXLG | 16 Kbytes | 0C000h         | -              | 1 Kbyte    | 007FFh         |

| R5F21255SNFP, R5F21255SNXXXFP, R5F21255SDFP, R5F21255SDXXXFP                                      | 24 Kbytes | 0A000h         | -              | 2 Kbytes   | 00BFFh         |

| R5F21256SNFP, R5F21256SNXXXFP,<br>R5F21256SDFP, R5F21256SDXXXFP,<br>R5F21256SNLG, R5F21256SNXXXLG | 32 Kbytes | 08000h         | _              | 2 Kbytes   | 00BFFh         |

| R5F21257SNFP, R5F21257SNXXXFP, R5F21257SDFP, R5F21257SDXXXFP                                      | 48 Kbytes | 04000h         | -              | 2.5 Kbytes | 00DFFh         |

| R5F21258SNFP, R5F21258SNXXXFP, R5F21258SDFP, R5F21258SDXXXFP                                      | 64 Kbytes | 04000h         | 13FFFh         | 3 Kbytes   | 00FFFh         |

Figure 3.2 Memory Map of R8C/25 Group

SFR Information (7)<sup>(1)</sup> Table 4.7

| Address         | Register                           | Symbol   | After reset |

|-----------------|------------------------------------|----------|-------------|

| 0180h           |                                    |          |             |

| 0181h           |                                    |          |             |

| 0182h           |                                    |          |             |

| 0183h           |                                    |          |             |

| 0184h           |                                    |          |             |

| 0185h           |                                    |          |             |

| 0186h           |                                    |          |             |

| 0187h           |                                    |          |             |

| 0188h           |                                    |          |             |

| 0189h           |                                    |          |             |

| 018Ah           |                                    |          |             |

| 018Bh<br>018Ch  |                                    |          |             |

| 018Dh           |                                    |          |             |

| 018Eh           |                                    |          |             |

| 018Fh           |                                    |          |             |

| 0190h           |                                    |          |             |

| 0191h           |                                    |          |             |

| 0192h           |                                    |          |             |

| 0193h           |                                    |          |             |

| 0194h           |                                    |          |             |

| 0195h           |                                    |          |             |

| 0196h           |                                    |          |             |

| 0197h           |                                    |          |             |

| 0198h           |                                    |          |             |

| 0199h           |                                    |          |             |

| 019Ah           |                                    |          |             |

| 019Bh           |                                    |          |             |

| 019Ch           |                                    |          |             |

| 019Dh           |                                    |          |             |

| 019Eh           |                                    |          |             |

| 019Fh           |                                    |          |             |

| 01A0h<br>01A1h  |                                    |          |             |

| 01A111          |                                    |          |             |

| 01A2h           |                                    |          |             |

| 01A4h           |                                    |          |             |

| 01A5h           |                                    |          |             |

| 01A6h           |                                    |          |             |

| 01A7h           |                                    |          |             |

| 01A8h           |                                    |          |             |

| 01A9h           |                                    |          |             |

| 01AAh           |                                    |          |             |

| 01ABh           |                                    |          |             |

| 01ACh           |                                    |          |             |

| 01ADh           |                                    |          |             |

| 01AEh           |                                    |          |             |

| 01AFh           |                                    |          |             |

| 01B0h           |                                    |          |             |

| 01B1h           |                                    |          |             |

| 01B2h           | 5                                  | EMD 4    | 04000000    |

| 01B3h           | Flash Memory Control Register 4    | FMR4     | 01000000b   |

| 01B4h           | Floor Mamony Control Deviator 1    | EMD4     | 4000000Vb   |

| 01B5h           | Flash Memory Control Register 1    | FMR1     | 1000000Xb   |

| 01B6h<br>01B7h  | Flash Memory Control Register 0    | FMR0     | 00000001b   |

| 01B7fi<br>01B8h | Traditivientory Control negister o | I IVIINU | 000000010   |

| 01B6H           |                                    |          |             |

| 01BAh           |                                    |          |             |

| 01BBh           |                                    |          |             |

| 01BCh           |                                    |          |             |

| 01BDh           |                                    |          |             |

| 01BEh           |                                    |          |             |

| 01BFh           |                                    |          |             |

|                 |                                    |          | 1           |

|                 |                                    |          |             |

FFFFh

Option Function Select Register

X: Undefined

NOTES:

1. The blank regions are reserved. Do not access locations in these regions.

2. The OFS register cannot be changed by a program. Use a flash programmer to write to it.

OFS

(Note 2)

| Table 5.9 | Power-on Reset Circuit. | Voltage Monitor 0 Reset Electrical Characteristics <sup>(3)</sup> |

|-----------|-------------------------|-------------------------------------------------------------------|

|           |                         |                                                                   |

| Symbol | Parameter                                               | Condition | Standard |      | Unit  |         |

|--------|---------------------------------------------------------|-----------|----------|------|-------|---------|

|        |                                                         |           | Min.     | Тур. | Max.  |         |

| Vpor1  | Power-on reset valid voltage <sup>(4)</sup>             |           | -        | -    | 0.1   | V       |

| Vpor2  | Power-on reset or voltage monitor 0 reset valid voltage |           | 0        | _    | Vdet0 | V       |

| trth   | External power Vcc rise gradient <sup>(2)</sup>         |           | 20       | _    | _     | mV/msec |

#### NOTES:

- 1. The measurement condition is Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

- 2. This condition (external power Vcc rise gradient) does not apply if Vcc ≥ 1.0 V.

- 3. To use the power-on reset function, enable voltage monitor 0 reset by setting the LVD0ON bit in the OFS register to 0, the VW0C0 and VW0C6 bits in the VW0C register to 1 respectively, and the VCA25 bit in the VCA2 register to 1.

- 4. tw(por1) indicates the duration the external power Vcc must be held below the effective voltage (Vpor1) to enable a power on reset. When turning on the power for the first time, maintain tw(por1) for 30 s or more if -20°C ≤ Topr ≤ 85°C, maintain tw(por1) for 3,000 s or more if -40°C ≤ Topr < -20°C.</p>

#### NOTES:

- 1. When using the voltage monitor 0 digital filter, ensure that the voltage is within the MCU operation voltage range (2.2 V or above) during the sampling time.

- 2. The sampling clock can be selected. Refer to 6. Voltage Detection Circuit of Hardware Manual for details.

- 3. Vdeto indicates the voltage detection level of the voltage detection 0 circuit. Refer to 6. Voltage Detection Circuit of Hardware Manual for details.

Figure 5.3 Power-on Reset Circuit Electrical Characteristics

**Table 5.13** Timing Requirements of Clock Synchronous Serial I/O with Chip Select(1)

| Cumbal | Doromotor                      |                               | Conditions          |            | Standard |               |         |  |

|--------|--------------------------------|-------------------------------|---------------------|------------|----------|---------------|---------|--|

| Symbol | Paramete                       | Parameter                     |                     | Min.       | Тур.     | Max.          |         |  |

| tsucyc | SSCK clock cycle time          |                               |                     | 4          | -        | =             | tcyc(2) |  |

| tHI    | SSCK clock "H" width           |                               |                     | 0.4        | _        | 0.6           | tsucyc  |  |

| tLO    | SSCK clock "L" width           |                               |                     | 0.4        | -        | 0.6           | tsucyc  |  |

| trise  | SSCK clock rising              | Master                        |                     | =          | -        | 1             | tcyc(2) |  |

|        | time                           | Slave                         |                     | -          | -        | 1             | μS      |  |

| tFALL  | SSCK clock falling time        | Master                        |                     | =          | =        | 1             | tcyc(2) |  |

|        |                                | Slave                         |                     | -          | -        | 1             | μS      |  |

| tsu    | SSO, SSI data input setup time |                               |                     | 100        | -        | =             | ns      |  |

| tH     | SSO, SSI data input h          | SSO, SSI data input hold time |                     | 1          | =        | =             | tcyc(2) |  |

| tLEAD  | SCS setup time                 | Slave                         |                     | 1tcyc + 50 | -        | -             | ns      |  |

| tLAG   | SCS hold time                  | Slave                         |                     | 1tcyc + 50 | _        | -             | ns      |  |

| top    | SSO, SSI data output           | delay time                    |                     | -          | -        | 1             | tcyc(2) |  |

| tsa    | SSI slave access time          | )                             | 2.7 V ≤ Vcc ≤ 5.5 V | -          | _        | 1.5tcyc + 100 | ns      |  |

|        |                                |                               | 2.2 V ≤ Vcc < 2.7 V | -          | _        | 1.5tcyc + 200 | ns      |  |

| tor    | SSI slave out open tin         | ne                            | 2.7 V ≤ Vcc ≤ 5.5 V | -          | =        | 1.5tcyc + 100 | ns      |  |

|        |                                |                               | 2.2 V ≤ Vcc < 2.7 V | -          | _        | 1.5tcyc + 200 | ns      |  |

#### NOTES:

Vcc = 2.2 to 5.5 V, Vss = 0 V at Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

1. Vcc = 2.2 to 5.5 V, Vss = 0 V at Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

2. 1tcyc = 1/f1(s)

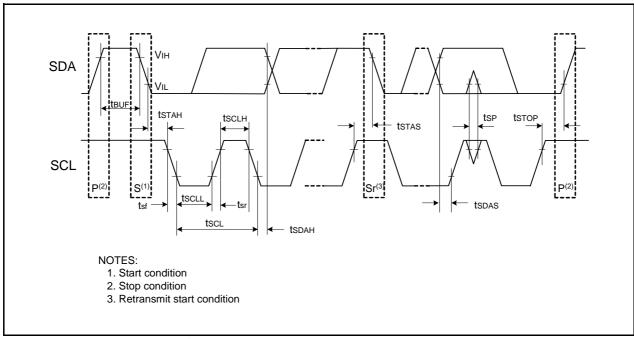

Table 5.14 Timing Requirements of I<sup>2</sup>C bus Interface<sup>(1)</sup>

| Symbol   | Parameter                                   | Condition | St                          | Standard |          |    |  |

|----------|---------------------------------------------|-----------|-----------------------------|----------|----------|----|--|

| Syllibol | Farameter                                   | Condition | Min.                        | Тур.     | Max.     |    |  |

| tscl     | SCL input cycle time                        |           | 12tcyc + 600 <sup>(2)</sup> | -        | _        | ns |  |

| tsclh    | SCL input "H" width                         |           | 3tcyc + 300 <sup>(2)</sup>  | =        | -        | ns |  |

| tscll    | SCL input "L" width                         |           | 5tcyc + 500 <sup>(2)</sup>  | =        | -        | ns |  |

| tsf      | SCL, SDA input fall time                    |           | -                           | -        | 300      | ns |  |

| tsp      | SCL, SDA input spike pulse rejection time   |           | -                           | -        | 1tcyc(2) | ns |  |

| tBUF     | SDA input bus-free time                     |           | 5tcyc(2)                    | -        | -        | ns |  |

| tstah    | Start condition input hold time             |           | 3tcyc(2)                    | =        | -        | ns |  |

| tstas    | Retransmit start condition input setup time |           | 3tcyc(2)                    | =        | -        | ns |  |

| tstop    | Stop condition input setup time             |           | 3tcyc(2)                    | -        | -        | ns |  |

| tsdas    | Data input setup time                       |           | 1tcyc + 20 <sup>(2)</sup>   | -        | -        | ns |  |

| tsdah    | Data input hold time                        |           | 0                           | -        | -        | ns |  |

#### NOTES:

- 1. Vcc = 2.2 to 5.5 V, Vss = 0 V and Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

- 2. 1tcyc = 1/f1(s)

Figure 5.7 I/O Timing of I<sup>2</sup>C bus Interface

Electrical Characteristics (1) [Vcc = 5 V] **Table 5.15**

| Symbol  | Parameter           |                                                                                                                   | Canditio            | Condition     |           | Standard |      |      |  |

|---------|---------------------|-------------------------------------------------------------------------------------------------------------------|---------------------|---------------|-----------|----------|------|------|--|

| Symbol  | Pai                 | ameter                                                                                                            | Conditio            | Condition     |           | Тур.     | Max. | Unit |  |

| Vон     | Output "H" voltage  | Except P2_0 to P2_7,                                                                                              | Iон = -5 mA         |               | Vcc - 2.0 | 1        | Vcc  | V    |  |

|         |                     | XOUT                                                                                                              | IOH = -200 μA       |               | Vcc - 0.5 | 1        | Vcc  | V    |  |

|         |                     | P2_0 to P2_7                                                                                                      | Drive capacity HIGH | Iон = -20 mA  | Vcc - 2.0 | _        | Vcc  | V    |  |

|         |                     |                                                                                                                   | Drive capacity LOW  | Iон = -5 mA   | Vcc - 2.0 | _        | Vcc  | V    |  |

|         |                     | XOUT                                                                                                              | Drive capacity HIGH | Iон = -1 mA   | Vcc - 2.0 | _        | Vcc  | V    |  |

|         |                     |                                                                                                                   | Drive capacity LOW  | IOH = -500 μA | Vcc - 2.0 | 1        | Vcc  | V    |  |

| Vol     | Output "L" voltage  | Except P2_0 to P2_7,                                                                                              | IoL = 5 mA          |               | _         | 1        | 2.0  | V    |  |

|         |                     | XOUT                                                                                                              | IoL = 200 μA        |               | _         | 1        | 0.45 | V    |  |

|         |                     | P2_0 to P2_7                                                                                                      | Drive capacity HIGH | IoL = 20 mA   | _         | 1        | 2.0  | V    |  |

|         |                     |                                                                                                                   | Drive capacity LOW  | IoL = 5 mA    | _         | 1        | 2.0  | V    |  |

|         |                     | XOUT                                                                                                              | Drive capacity HIGH | IoL = 1 mA    | _         | 1        | 2.0  | V    |  |

|         |                     |                                                                                                                   | Drive capacity LOW  | IoL = 500 μA  | _         | 1        | 2.0  | V    |  |

| VT+-VT- | Hysteresis          | INTO, INT1, INT2,<br>  INT3, KI0, KI1, KI2,<br>  KI3, TRAIO, RXD0,<br>  RXD1, CLK0, CLK1,<br>  SSI, SCL, SDA, SSO |                     |               | 0.1       | 0.5      | -    | ٧    |  |

|         |                     | RESET                                                                                                             |                     |               | 0.1       | 1.0      | -    | V    |  |

| Іін     | Input "H" current   |                                                                                                                   | VI = 5 V, Vcc = 5V  |               | =         | =        | 5.0  | μА   |  |

| lıL     | Input "L" current   |                                                                                                                   | VI = 0 V, Vcc = 5V  |               | =         | =        | -5.0 | μА   |  |

| RPULLUP | Pull-up resistance  |                                                                                                                   | VI = 0 V, Vcc = 5V  |               | 30        | 50       | 167  | kΩ   |  |

| RfXIN   | Feedback resistance | XIN                                                                                                               |                     |               | -         | 1.0      | =    | МΩ   |  |

| RfXCIN  | Feedback resistance | XCIN                                                                                                              |                     |               | =         | 18       | _    | МΩ   |  |

| VRAM    | RAM hold voltage    | •                                                                                                                 | During stop mode    |               | 1.8       | _        | -    | V    |  |

### NOTE:

<sup>1.</sup> Vcc = 4.2 to 5.5 V at Topr = -20 to 85°C (N version) / -40 to 85°C (D version), f(XIN) = 20 MHz, unless otherwise specified.

### **Timing Requirements**

(Unless Otherwise Specified: Vcc = 5 V, Vss = 0 V at Topr = 25°C) [Vcc = 5 V]

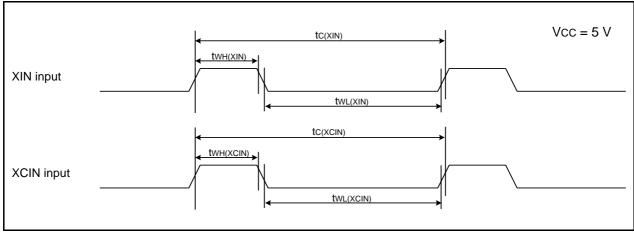

**Table 5.18 XIN Input, XCIN Input**

| Symbol    | Doromotor             | Min. Max. 50 – 25 – 25 – | Unit |       |

|-----------|-----------------------|--------------------------|------|-------|

| Symbol    | Falanetei             | Min.                     | Max. | Offic |

| tc(XIN)   | XIN input cycle time  | 50                       | -    | ns    |

| twh(xin)  | XIN input "H" width   | 25                       | -    | ns    |

| twl(xin)  | XIN input "L" width   | 25                       | -    | ns    |

| tc(XCIN)  | XCIN input cycle time | 14                       | -    | μS    |

| twh(xcin) | XCIN input "H" width  | 7                        | =    | μS    |

| tWL(XCIN) | XCIN input "L" width  | 7                        | =    | μS    |

XIN Input and XCIN Input Timing Diagram when Vcc = 5 V Figure 5.8

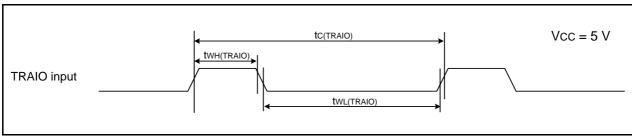

**Table 5.19 TRAIO Input**

| Symbol     | Parameter              | put cycle time 100 - | dard | Unit  |

|------------|------------------------|----------------------|------|-------|

| Syllibol   | raidilletei            | Min.                 | Max. | Offic |

| tc(TRAIO)  | TRAIO input cycle time | 100                  | =    | ns    |

| twh(traio) | TRAIO input "H" width  | 40                   | =    | ns    |

| tWL(TRAIO) | TRAIO input "L" width  | 40                   | -    | ns    |

Figure 5.9 TRAIO Input Timing Diagram when Vcc = 5 V

Table 5.23 Electrical Characteristics (4) [Vcc = 3 V] (Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Symbol | Parameter                                                                                  |                                                                                                                    | Condition                                                                                                                                                                                                |      | Standar |      | Unit |

|--------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|------|

| ,      |                                                                                            |                                                                                                                    |                                                                                                                                                                                                          | Min. | Тур.    | Max. |      |

| Icc    | Power supply current<br>(Vcc = 2.7 to 3.3 V)<br>Single-chip mode,<br>output pins are open, | High-speed clock mode                                                                                              | XIN = 10 MHz (square wave) High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz No division                                                                                       | _    | 6       | _    | mA   |

|        | other pins are Vss                                                                         |                                                                                                                    | XIN = 10 MHz (square wave) High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz Divide-by-8                                                                                       | _    | 2       | _    | mA   |

|        |                                                                                            | High-speed on-<br>chip oscillator<br>mode                                                                          | XIN clock off High-speed on-chip oscillator on fOCO = 10 MHz Low-speed on-chip oscillator on = 125 kHz No division                                                                                       | _    | 5       | 9    | mA   |

|        |                                                                                            | XIN clock off High-speed on-chip oscillator on fOCO = 10 MHz Low-speed on-chip oscillator on = 125 kHz Divide-by-8 | _                                                                                                                                                                                                        | 2    | =       | mA   |      |

|        |                                                                                            | Low-speed on-<br>chip oscillator<br>mode                                                                           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz Divide-by-8, FMR47 = 1                                                                                         | _    | 130     | 300  | μА   |

|        |                                                                                            | Low-speed clock mode                                                                                               | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz FMR47 = 1                                                                             | _    | 130     | 300  | μА   |

|        |                                                                                            |                                                                                                                    | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz Program operation on RAM Flash memory off, FMSTP = 1                                  | -    | 30      | _    | μА   |

|        |                                                                                            | Wait mode                                                                                                          | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz While a WAIT instruction is executed Peripheral clock operation VCA27 = VCA26 = VCA25 = 0 VCA20 = 1            | _    | 25      | 70   | μА   |

|        |                                                                                            |                                                                                                                    | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz While a WAIT instruction is executed Peripheral clock off VCA27 = VCA26 = VCA25 = 0 VCA20 = 1                  | _    | 23      | 55   | μА   |

|        |                                                                                            |                                                                                                                    | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz (high drive) While a WAIT instruction is executed VCA27 = VCA26 = VCA25 = 0 VCA20 = 1 | _    | 3.8     | -    | μА   |

|        |                                                                                            |                                                                                                                    | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz (low drive) While a WAIT instruction is executed VCA27 = VCA26 = VCA25 = 0 VCA20 = 1  | _    | 2.0     | -    | μА   |

|        |                                                                                            | Increase during                                                                                                    | Without sample & hold                                                                                                                                                                                    | -    | 0.9     | -    | mA   |

|        |                                                                                            | A/D converter operation                                                                                            | With sample & hold                                                                                                                                                                                       | =    | 0.5     | =    | mA   |

|        |                                                                                            | Stop mode                                                                                                          | XIN clock off, Topr = 25°C High-speed on-chip oscillator off Low-speed on-chip oscillator off CM10 = 1 Peripheral clock off VCA27 = VCA26 = VCA25 = 0                                                    | _    | 0.7     | 3.0  | μА   |

|        |                                                                                            |                                                                                                                    | XIN clock off, Topr = 85°C High-speed on-chip oscillator off Low-speed on-chip oscillator off CM10 = 1 Peripheral clock off VCA27 = VCA26 = VCA25 = 0                                                    | _    | 1.1     | -    | μА   |

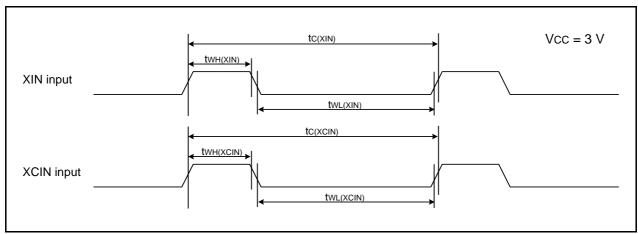

### **Timing requirements**

(Unless Otherwise Specified: Vcc = 3 V, Vss = 0 V at Topr = 25°C) [Vcc = 3 V]

**Table 5.24 XIN Input, XCIN Input**

| Symbol    | Parameter                | Stan | Unit |       |  |

|-----------|--------------------------|------|------|-------|--|

| Symbol    | raidilletei              | Min. | Max. | OTIIL |  |

| tc(XIN)   | XIN input cycle time     | 100  | -    | ns    |  |

| twh(xin)  | XIN input "H" width      | 40   | -    | ns    |  |

| tWL(XIN)  | XIN input "L" width      | 40   | -    | ns    |  |

| tc(XCIN)  | XCIN input cycle time    | 14   | -    | μS    |  |

| twh(xcin) | XCIN input "H" width 7   |      |      | μS    |  |

| twl(xcin) | XCIN input "L" width 7 – |      |      |       |  |

Figure 5.12 XIN Input and XCIN Input Timing Diagram when Vcc = 3 V

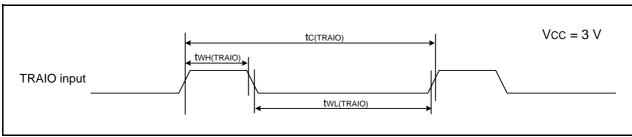

**Table 5.25 TRAIO Input**

| Symbol     | Parameter                   |      | Standard |      |  |

|------------|-----------------------------|------|----------|------|--|

| Symbol     | Faidilletei                 | Min. | Max.     | Unit |  |

| tc(TRAIO)  | TRAIO input cycle time      | 300  | =        | ns   |  |

| twh(traio) | TRAIO input "H" width 120 - |      |          |      |  |

| tWL(TRAIO) | TRAIO input "L" width       | -    | ns       |      |  |

Figure 5.13 TRAIO Input Timing Diagram when Vcc = 3 V

Table 5.29 Electrical Characteristics (6) [Vcc = 2.2 V] (Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Symbol   | Parameter                                                                                  | Condition                                 |                                                                                                                                                                                                          | Standard |      |      | Unit |

|----------|--------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| Cyllibul |                                                                                            |                                           |                                                                                                                                                                                                          | Min.     | Тур. | Max. | Oill |

| Icc      | Power supply current<br>(Vcc = 2.2 to 2.7 V)<br>Single-chip mode,<br>output pins are open, | High-speed clock mode                     | XIN = 5 MHz (square wave) High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz No division                                                                                        | -        | 3.5  | -    | mA   |

|          | other pins are Vss                                                                         |                                           | XIN = 5 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8                                                                               | _        | 1.5  | _    | mA   |

|          |                                                                                            | High-speed on-<br>chip oscillator<br>mode | XIN clock off High-speed on-chip oscillator on fOCO = 5 MHz Low-speed on-chip oscillator on = 125 kHz No division                                                                                        | _        | 3.5  | _    | mA   |

|          |                                                                                            |                                           | XIN clock off<br>High-speed on-chip oscillator on fOCO = 5 MHz<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8                                                                               | _        | 1.5  | _    | mA   |

|          |                                                                                            | Low-speed on-<br>chip oscillator<br>mode  | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz Divide-by-8, FMR47 = 1                                                                                         | -        | 100  | 230  | μА   |

|          |                                                                                            | Low-speed clock mode                      | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz FMR47 = 1                                                                             | _        | 100  | 230  | μА   |

|          |                                                                                            |                                           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz Program operation on RAM Flash memory off, FMSTP = 1                                  | -        | 25   | _    | μА   |

|          |                                                                                            | Wait mode                                 | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz While a WAIT instruction is executed Peripheral clock operation VCA27 = VCA26 = VCA25 = 0 VCA20 = 1            | _        | 22   | 60   | μА   |

|          |                                                                                            |                                           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz While a WAIT instruction is executed Peripheral clock off VCA27 = VCA26 = VCA25 = 0 VCA20 = 1                  | =        | 20   | 55   | μА   |

|          |                                                                                            |                                           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz (high drive) While a WAIT instruction is executed VCA27 = VCA26 = VCA25 = 0 VCA20 = 1 | _        | 3.0  | -    | μА   |

|          |                                                                                            |                                           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz (low drive) While a WAIT instruction is executed VCA27 = VCA26 = VCA25 = 0 VCA20 = 1  | _        | 1.8  | -    | μА   |

|          |                                                                                            | Increase during                           | Without sample & hold                                                                                                                                                                                    | -        | 0.4  | -    | mA   |

|          |                                                                                            | A/D converter operation                   | With sample & hold                                                                                                                                                                                       | _        | 0.3  | _    | mA   |

|          |                                                                                            | Stop mode                                 | XIN clock off, Topr = 25°C High-speed on-chip oscillator off Low-speed on-chip oscillator off CM10 = 1 Peripheral clock off VCA27 = VCA26 = VCA25 = 0                                                    | =        | 0.7  | 3.0  | μА   |

|          |                                                                                            |                                           | XIN clock off, Topr = 85°C High-speed on-chip oscillator off Low-speed on-chip oscillator off CM10 = 1 Peripheral clock off VCA27 = VCA26 = VCA25 = 0                                                    | -        | 1.1  | -    | μА   |

## **Package Dimensions**

Diagrams showing the latest package dimensions and mounting information are available in the "Packages" section of the Renesas Technology website.

## REVISION HISTORY

# R8C/24 Group, R8C/25 Group Datasheet

| D :  | Pov Doto     |           | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. | Date         | Page      | Summary                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0.01 | Sep 17, 2004 | -         | First Edition issued                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.02 | Dec 10, 2004 | All pages | Part Number revised. R8C/26 → R8C/24, R8C/27 → R8C/25                                                                                                                                                                                                                                                                                                                                                        |

|      |              | 2, 3      | Table 1.1 R8C/24 Group Performance, Table 1.2 R8C/25 Group Performance - Serial Interface: I <sup>2</sup> C Bus Interface and Chip-select clock synchronous (SSU) added LIN Module added Interrupt: Internal factors revised; 10 → 11 - Note on Operating Ambient Temperature added.                                                                                                                         |

|      |              | 4         | Figure 1.1 Block Diagram - LIN Module added Chip-select clock synchronous (SSU) is added to I <sup>2</sup> C Bus Interface.                                                                                                                                                                                                                                                                                  |

|      |              | 5, 6      | Table 1.3 Product Information of R8C/24 Group, Table 1.4 Product Information of R8C/25 Group Date and Development state revised.                                                                                                                                                                                                                                                                             |

|      |              | 7         | Figure 1.4 Pin Assignment P3_5/SCL $\rightarrow$ P3_5/SCL/SSCK, P3_3 $\rightarrow$ P3_3/SSI, P3_4/SDA $\rightarrow$ P3_4/SDA/SCS, P3_7 $\rightarrow$ P3_7/SSO, VSS/AVSS $\rightarrow$ VSS, XIN/P4_6 $\rightarrow$ P4_6/XIN, VCC/AVSS $\rightarrow$ VCC 12pin P1_7/TRAIO/INT1 to 22pin P1_0/KI0/AN8 $\rightarrow$ 20pin P1_7/TRAIO/INT1 to 30pin P1_0/KI0/AN8                                                 |

|      |              | 8         | Table 1.5 Pin Description - Analog Power Supply Input eliminated SSU added.                                                                                                                                                                                                                                                                                                                                  |

|      |              | 9         | Table 1.6 Pin Name Information by Pin Number added.                                                                                                                                                                                                                                                                                                                                                          |

|      |              | 15        | Table 4.1 SFR Information (1) - 0031h: Voltage Detection Register 1 $\rightarrow$ Voltage Detection $\underline{A}$ Register 1 - 0032h: Voltage Detection Register 1 $\rightarrow$ Voltage Detection $\underline{A}$ Register 2 01000001b $\rightarrow$ 00100001b (Note 4) - 0036h: "(3), 01000001b (4)" eliminated 0038h: Voltage Monitor 0 Control Register (2), VW0C, 00001000b (3), 01000001b (4) added. |

|      |              | 16        | Table 4.2 SFR Information (2) - 0048h: Timer RD0 Interrupt Control Register, RD0IC, XXXXX000b added 0049h: Timer RD Interrupt Control Register, RDIC  → Timer RD1 Interrupt Control Register, RD1IC - 004Fh: IIC Interrupt Control Register, IIC  → IIC/SSU Interrupt Control Register, IIC2IC                                                                                                               |

|      |              | 19        | Table 4.5 SFR Information (3) - 0106h: LIN Control Register, LINCR, 00h added0107h: LIN Status Register, LINST, 00h added.                                                                                                                                                                                                                                                                                   |

| Pov  | Rev. Date    |      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. | Date         | Page | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0.30 | Sep 01, 2005 | 7    | Figure 1.4 Pin Assignment  • Pin name revised;  VSS → VSS/AVSS,  VCC → VCC/AVCC,  P1_5/RXD0/(TRAIO)/(INT1) → P1_5/RXD0/(TRAIO)/(INT1)(2),  P6_6/INT2/(TXD1) → P6_6/INT2/TXD1,  P6_7/INT3/(RXD1) → P6_7/INT3/RXD1,  P6_5 → P6_5/CLK1  • NOTE2 added                                                                                                                                                                                                           |

|      |              | 8    | <ul> <li>Table 1.5 Pin Description</li> <li>Analog Power Supply Input: line added</li> <li>INT Interrupt Input: "INTO Timer RD input pins. INT1 Timer RA input pins." added</li> <li>Serial Interface: "CLK1" added</li> <li>"I²C Bus Interface (IIC)" → "I²C Bus Interface"</li> <li>"SSU" → "Clock Synchronous Serial I/O with Chip Select"</li> </ul>                                                                                                     |

|      |              | 9    | Table 1.6 Pin Name Information by Pin Number revised  • Pin Number 10: "VSS" → "VSS/AVSS"  • Pin Number 12: "VCC" → "VCC/AVCC"  • Pin Number 27: "INTO" added  • Pin Number 28: "(TXD1)" → "TXD1"  • Pin Number 29: "(RXD1)" → "RXD1"  • Pin Number 35: "CLK1" added                                                                                                                                                                                         |

|      |              | 15   | Tabel 4.1 SFR Information(1) revised:  • 0012h: X0h → 00h  • 0013h: XXXXXX00b → 00h  • 0016h: X0h → 00h  • 0036h: Voltage Monitor 1 Control Register <sup>(2)</sup> → Voltage Monitor 1  Control Register <sup>(5)</sup> • 0038h: 00001000b <sup>(3)</sup> , 01000001b <sup>(4)</sup> → 0000X000b <sup>(3)</sup> , 0100X001b <sup>(4)</sup> • NOTES2, 5: "the voltage monitor 1 reset" added  • NOTE3: "voltage monitor 1 reset" → "voltage monitor 0 reset" |

|      |              | 16   | Tabel 4.2 SFR Information(2) revised:  • 0048h: RD0IC → TRD0IC  • 0049h: RD1IC → TRD1IC  • 004Ah: REIC → TREIC  • 004Fh: SSU/IIC Interrupt Control Register, IIC2AIC → SSU/IIC Interrupt Control Register <sup>(2)</sup> , SSUAIC/IIC2AIC  • 0056h: RAIC → TRAIC  • 0058h: RBIC → TRBIC  • NOTE2 added                                                                                                                                                       |

|      |              | 17   | Tabel 4.3 SFR Information(3) revised:  • 00BCh: 00h → 00h/0000X000b  Tabel 4.4 CFR Information(4) as itself.                                                                                                                                                                                                                                                                                                                                                 |

|      |              | 18   | Tabel 4.4 SFR Information(4) revised:  • 00D6h: 00000XXXb → 00h  • 00F5h: UART1 Function Select Register, U1SR, XXh added                                                                                                                                                                                                                                                                                                                                    |

| Davi      | Doto         | Description |                                                                                                                                                                                    |  |  |

|-----------|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev. Date |              | Page        | Summary                                                                                                                                                                            |  |  |

| 0.30      | Sep 01, 2005 | 19          | Tabel 4.5 SFR Information(5) revised:  • 0118h : Timer RE Second Data Register/Counter Register → Timer RE Second Data Register/Counter Data Register                              |  |  |

|           |              | 21          | Tabel 4.6 SFR Information(6) revised:  • 0145h                                                                                                                                     |  |  |

|           |              | 22 to 44    | 5. Electrical Characteristics added                                                                                                                                                |  |  |

| 0.40      | Jan 24, 2006 | all pages   | <ul> <li>"Preliminary" deleted</li> <li>Symbol name "TRDMDR" → "TRDMR", "SSUAIC" → "SSUIC", and "IIC2AIC" → "IICIC" revised</li> <li>Pin name "TCLK" → "TRDCLK" revised</li> </ul> |  |  |

|           |              | 2           | Table 1.1 Functions and Specifications for R8C/24 Group revised                                                                                                                    |  |  |

|           |              | 3           | Table 1.2 Functions and Specifications for R8C/25 Group revised                                                                                                                    |  |  |

|           |              | 4           | Figure 1.1 Block Diagram;  "Peripheral Functions" added,  "System Clock Generation" → "System Clock Generator" revised                                                             |  |  |

|           |              | 5           | Table 1.3 Product Information for R8C/24 Group revised                                                                                                                             |  |  |

|           |              | 6           | Table 1.4 Product Information for R8C/25 Group revised                                                                                                                             |  |  |

|           |              | 7           | Figure 1.4 Pin Assignments (Top View) "TCLK" $\rightarrow$ "TRDCLK" revised                                                                                                        |  |  |

|           |              | 8           | Table 1.5 Pin Functions "TCLK" $\rightarrow$ "TRDCLK" revised                                                                                                                      |  |  |

|           |              | 9           | Table 1.6 Pin Name Information by Pin Number; "TCLK" → "TRDCLK" revised                                                                                                            |  |  |

|           |              | 10          | Figure 2.1 CPU Registers;<br>"Reserved Area" → "Reserved Bit" revised                                                                                                              |  |  |

|           |              | 12          | 2.8.10 Reserved Area;<br>"Reserved Area" → "Reserved bit" revised                                                                                                                  |  |  |

|           |              | 13          | Figure 3.1 Memory Map of R8C/24 Group;<br>"Program area" → "program ROM" revised                                                                                                   |  |  |

|           |              | 14          | 3.2 R8C/25 Group, Figure 3.2 Memory Map of R8C/25 Group; "Data area" → "data flash", "Program area" → "program ROM" revised                                                        |  |  |

| Day  | Rev. Date    |      | Description                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev. | Date         | Page | Summary                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 0.40 | Jan 24, 2006 | 15   | Table 4.1 SFR Information(1);<br>0024h: "TBD" → "When shipping"<br>NOTES 3 and 4 revised                                                                                                                                                                                                                                                                    |  |  |

|      |              | 19   | Table 4.5 SFR Information (5);  0118h: "Timer RE Second Data Register" → "Timer RE Second Data Register / Counter Data Register"  0119h: "Timer RE Minute Data Register" → "Timer RE Minute Data Register / Compare Data Register"  0138h: "TRDMDR" → "TRDMR"  013Bh: "Timer RD Output Master Enable Register" → "Timer RD Output Master Enable Register 1" |  |  |

|      |              | 22   | Table 5.1 Absolute Maximum Ratings; "Vcc" → "Vcc/AVcc" revised                                                                                                                                                                                                                                                                                              |  |  |

|      |              |      | Table 5.2 Recommended Operating Conditions revised                                                                                                                                                                                                                                                                                                          |  |  |

|      |              | 23   | Table 5.3 A/D Converter Characteristics revised                                                                                                                                                                                                                                                                                                             |  |  |

|      |              | 24   | Table 5.4 Flash Memory (Program ROM) Electrical Characteristics revised                                                                                                                                                                                                                                                                                     |  |  |

|      |              | 25   | Table 5.5 Flash Memory (Data flash Block A, Block B) Electrical revised                                                                                                                                                                                                                                                                                     |  |  |

|      |              | 26   | Table 5.6 Voltage Detection 0 Circuit Electrical Characteristics revised Table 5.7 Voltage Detection 1 Circuit Electrical Characteristics revised Table 5.8 Voltage Detection 2 Circuit Electrical Characteristics revised                                                                                                                                  |  |  |

|      |              | 28   | Table 5.11 High-speed On-Chip Oscillator Circuit Electrical Characteristics revised Table 5.12 Low-speed On-Chip Oscillator Circuit Electrical Characteristics revised Table 5.13 Power Supply Circuit Timing Characteristics revised                                                                                                                       |  |  |

|      |              | 29   | Table 5.14 Timing Requirements of Clock Synchronous Serial I/O with Chip Select revised                                                                                                                                                                                                                                                                     |  |  |

|      |              | 33   | Table 5.15 Timing Requirements of I <sup>2</sup> C bus Interface NOTE1 revised                                                                                                                                                                                                                                                                              |  |  |

|      |              | 34   | Table 5.16 Electrical Characteristics (1) [VCC = 5 V] revised                                                                                                                                                                                                                                                                                               |  |  |

|      |              | 35   | Table 5.17 Electrical Characteristics (2) [VCC = 5 V] revised                                                                                                                                                                                                                                                                                               |  |  |

|      |              | 36   | Table 5.18 XIN Input, XCIN Input revised                                                                                                                                                                                                                                                                                                                    |  |  |

|      |              | 37   | Table 5.20 Serial Interface revised                                                                                                                                                                                                                                                                                                                         |  |  |

|      |              | 38   | Table 5.22 Electrical Characteristics (3) [VCC = 3 V] revised                                                                                                                                                                                                                                                                                               |  |  |

|      |              | 39   | Table 5.23 Electrical Characteristics (4) [Vcc = 3 V] revised                                                                                                                                                                                                                                                                                               |  |  |

|      |              | 40   | Table 5.24 XIN Input, XCIN Input revised                                                                                                                                                                                                                                                                                                                    |  |  |

|      |              | 41   | Table 5.26 Serial Interface revised                                                                                                                                                                                                                                                                                                                         |  |  |

|      |              | 42   | Table 5.28 Electrical Characteristics (5) [VCC = 2.2 V] revised                                                                                                                                                                                                                                                                                             |  |  |

|      |              | 43   | Table 5.29 Electrical Characteristics (6) [Vcc = 2.2 V] revised                                                                                                                                                                                                                                                                                             |  |  |