Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 120MHz                                                                     |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 100                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 58x16b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 144-LQFP                                                                   |

| Supplier Device Package    | 144-LQFP (20x20)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk20fn1m0vlq12     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communication interfaces

- USB high-/full-/low-speed On-the-Go controller with ULPI interface

- USB full-/low-speed On-the-Go controller with on-chip transceiver

- USB Device Charger detect (USBDCD)

- Two Controller Area Network (CAN) modules

- Three SPI modules

- Two I2C modules

- Six UART modules

- Secure Digital Host Controller (SDHC)

- Two I2S modules

#### Terminology and guidelines

| Field | Description                 | Values                                                                                     |

|-------|-----------------------------|--------------------------------------------------------------------------------------------|

| Т     | Temperature range (°C)      | <ul> <li>V = -40 to 105</li> <li>C = -40 to 85</li> </ul>                                  |

| PP    | Package identifier          | <ul> <li>LQ = 144 LQFP (20 mm x 20 mm)</li> <li>MD = 144 MAPBGA (13 mm x 13 mm)</li> </ul> |

| СС    | Maximum CPU frequency (MHz) | • 12 = 120 MHz                                                                             |

| Ν     | Packaging type              | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                             |

# 2.4 Example

This is an example part number:

MK20FN1M0VLQ12

# **3** Terminology and guidelines

### 3.1 Definitions

Key terms are defined in the following table:

| Term                  | Definition                                                                                                                                                                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rating                | A minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:                                                                                                                       |

|                       | Operating ratings apply during operation of the chip.                                                                                                                                                                               |

|                       | Handling ratings apply when the chip is not powered.                                                                                                                                                                                |

|                       | <b>NOTE:</b> The likelihood of permanent chip failure increases rapidly as soon as a characteristic begins to exceed one of its operating ratings.                                                                                  |

| Operating requirement | A specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip                                       |

| Operating behavior    | A specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions                                                  |

| Typical value         | A specified value for a technical characteristic that:                                                                                                                                                                              |

|                       | <ul> <li>Lies within the range of values specified by the operating behavior</li> <li>Is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions</li> </ul> |

|                       | <b>NOTE:</b> Typical values are provided as design guidelines and are neither tested nor guaranteed.                                                                                                                                |

| Symbol                | Description                                                               | Min. | Тур.  | Max.   | Unit | Notes |

|-----------------------|---------------------------------------------------------------------------|------|-------|--------|------|-------|

|                       | • @ 70°C                                                                  | _    | 7.08  | 10.74  | mA   |       |

|                       | • @ 105°C                                                                 |      |       |        |      |       |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks disabled | _    | 1.03  | 4.48   | mA   | 5     |

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks enabled  | —    | 1.58  | 4.96   | mA   | 5     |

| I <sub>DD_VLPW</sub>  | Very-low-power wait mode current at 3.0 V                                 | _    | 0.64  | 4.29   | mA   | 5     |

| I <sub>DD_VLPS</sub>  | Very-low-power stop mode current at 3.0 V                                 |      |       |        |      |       |

|                       | • @ -40 to 25°C                                                           | _    | 0.22  | 0.38   | mA   |       |

|                       | • @ 70°C                                                                  | _    | 0.78  | 1.33   | mA   |       |

|                       | • @ 105°C                                                                 | —    | 2.18  | 3.56   | mA   |       |

| I <sub>DD_LLS</sub>   | Low leakage stop mode current at 3.0 V                                    |      |       |        |      |       |

|                       | • @ -40 to 25°C                                                           | —    | 0.22  | 0.37   | mA   |       |

|                       | • @ 70°C                                                                  | _    | 0.78  | 1.33   | mA   |       |

|                       | • @ 105°C                                                                 | —    | 2.16  | 3.52   | mA   |       |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current at 3.0 V                             |      |       |        |      |       |

|                       | • @ -40 to 25°C                                                           | —    | 4.09  | 5.58   | μA   |       |

|                       | • @ 70°C                                                                  | _    | 20.98 | 28.93  | μA   |       |

|                       | • @ 105°C                                                                 | —    | 84.95 | 111.15 | μA   |       |

| I <sub>DD_VLLS2</sub> | Very low-leakage stop mode 2 current at 3.0 V                             |      |       |        |      |       |

|                       | • @ -40 to 25°C                                                           | —    | 2.68  | 4.22   | μA   |       |

|                       | • @ 70°C                                                                  | —    | 8.8   | 10.74  | μA   |       |

|                       | • @ 105°C                                                                 | _    | 37.28 | 43.61  | μA   |       |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current at 3.0 V                             |      |       |        |      |       |

|                       | • @ -40 to 25°C                                                           | _    | 2.46  | 4.02   | μA   |       |

|                       | • @ 70°C                                                                  | _    | 7.04  | 8.99   | μA   |       |

|                       | • @ 105°C                                                                 | —    | 30.68 | 37.04  | μA   |       |

| I <sub>DD_VBAT</sub>  | Average current when CPU is not accessing<br>RTC registers at 3.0 V       |      |       |        |      | 6     |

|                       | <ul> <li>● -40 to 25°C</li> </ul>                                         | _    | 0.89  | 1.10   | μA   |       |

|                       | • @ 70°C                                                                  | —    | 1.28  | 1.85   | μA   |       |

|                       | • @ 105°C                                                                 | _    | 3.10  | 4.30   | μA   |       |

Table 6. Power consumption operating behaviors (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 120 MHz core and system clock, 60 MHz bus, 30 MHz FlexBus clock, and 20 MHz flash clock. MCG configured for PEE mode. All peripheral clocks disabled.

- 3. 120 MHz core and system clock, 60 MHz bus, 30 MHz FlexBus clock, and 20 MHz flash clock. MCG configured for PEE mode. All peripheral clocks enabled, but peripherals are not in active operation.

- 4. 25 MHz core and system clock, 25 MHz bus clock, and 12.5 MHz FlexBus and flash clock. MCG configured for FEI mode.

#### K20 Sub-Family, Rev.6, 09/2015.

General

- 5. 4 MHz core, system, 2 MHz FlexBus, and 2 MHz bus clock and 0.5 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 6. Includes 32kHz oscillator current and RTC operation.

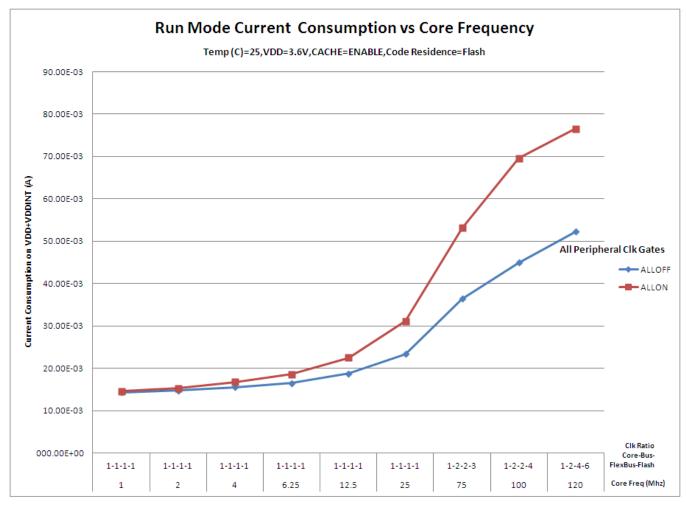

### 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at greater than 50 MHz frequencies. MCG in PEE mode at greater than 100 MHz frequencies.

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFE

Figure 3. Run mode supply current vs. core frequency

| Symbol            | Description                                      | Min. | Max. | Unit | Notes |

|-------------------|--------------------------------------------------|------|------|------|-------|

| t <sub>io50</sub> | Port rise and fall time (low drive strength)     |      |      |      | 7     |

|                   | Slew disabled                                    |      |      |      |       |

|                   | • $1.71 \le V_{DD} \le 2.7V$                     | _    | 18   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 9    | ns   | _     |

|                   | Slew enabled                                     |      |      |      |       |

|                   | <ul> <li>1.71 ≤ V<sub>DD</sub> ≤ 2.7V</li> </ul> | _    | 48   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 24   | ns   | _     |

| t <sub>io60</sub> | Port rise and fall time (high drive strength)    |      |      |      | 6     |

|                   | Slew disabled                                    |      |      |      |       |

|                   | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                  | _    | 6    | ns   |       |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 3    | ns   | _     |

|                   | Slew enabled                                     |      |      |      |       |

|                   | • $1.71 \le V_{DD} \le 2.7V$                     | _    | 28   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 14   | ns   | _     |

| t <sub>io60</sub> | Port rise and fall time (low drive strength)     |      |      |      | 7     |

|                   | Slew disabled                                    |      |      |      |       |

|                   | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                  | _    | 18   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 6    | ns   | _     |

|                   | Slew enabled                                     |      |      |      |       |

|                   | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                  | —    | 48   | ns   | —     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | —    | 24   | ns   | —     |

Table 10. General switching specifications (continued)

- 1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop, VLPS, LLS, and VLLSx modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater synchronous and asynchronous timing must be met.

- 3. This is the minimum pulse width that is guaranteed to be recognized as a pin interrupt request in Stop, VLPS, LLS, and VLLSx modes.

- 4. 75 pF load

- 5. 15 pF load

- 6. 25 pF load

- 7. 15 pF load

# 5.4 Thermal specifications

### 5.4.1 Thermal operating requirements

Table 11. Thermal operating requirements

| Symbol         | Description                      | Min. | Max. | Unit |

|----------------|----------------------------------|------|------|------|

| TJ             | Die junction temperature         | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature <sup>1</sup> | -40  | 105  | °C   |

<sup>1.</sup> Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:

$T_J = T_A + R_{\theta JA} x$  chip power dissipation

# 5.4.2 Thermal attributes

| Board type           | Symbol            | Description                                                                                                          | 144 LQFP | 144 MAPBGA | Unit | Notes |

|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|----------|------------|------|-------|

| Single-layer<br>(1s) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 45       | 50         | °C/W | 1,2   |

| Four-layer<br>(2s2p) | R <sub>0JA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 36       | 30         | °C/W | 1,2,3 |

| Single-layer<br>(1s) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 36       | 41         | °C/W | 1,3   |

| Four-layer<br>(2s2p) | R <sub>eJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 30       | 27         | °C/W | 1,3   |

| _                    | R <sub>θJB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                                                       | 24       | 17         | °C/W | 4     |

| _                    | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to case                                                                           | 9        | 10         | °C/W | 5     |

|                      | Ψ <sub>JT</sub>   | Thermal<br>characterization<br>parameter,<br>junction to<br>package top<br>outside center<br>(natural<br>convection) | 2        | 2          | °C/W | 6     |

rempheral operating requirements and behaviors

#### **NOTES:**

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Determined according to JEDEC Standard JESD51-2, *Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air)* with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Determined according to JEDEC Standard JESD51-6, *Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air)* with the board horizontal.

- 4. Determined according to JEDEC Standard JESD51-8, *Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board*. Board temperature is measured on the top surface of the board near the package.

- 5. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard*, *Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 6. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

# 6 Peripheral operating requirements and behaviors

# 6.1 Core modules

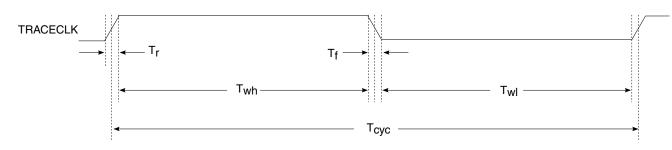

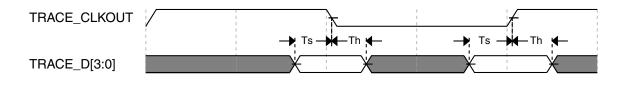

# 6.1.1 Debug trace timing specifications

Table 12. Debug trace operating behaviors

| Symbol           | Description              | Min.      | Max.                | Unit |  |

|------------------|--------------------------|-----------|---------------------|------|--|

| T <sub>cyc</sub> | Clock period             | Frequency | Frequency dependent |      |  |

| T <sub>wl</sub>  | Low pulse width          | 2         | _                   | ns   |  |

| T <sub>wh</sub>  | High pulse width         | 2         |                     | ns   |  |

| T <sub>r</sub>   | Clock and data rise time |           | 3                   | ns   |  |

| T <sub>f</sub>   | Clock and data fall time | —         | 3                   | ns   |  |

| Ts               | Data setup               | 3         |                     | ns   |  |

| T <sub>h</sub>   | Data hold                | 2         |                     | ns   |  |

#### Peripheral operating requirements and behaviors

### 6.1.2 JTAG electricals

| Symbol     | Description                                        | Min. | Max. | Unit |

|------------|----------------------------------------------------|------|------|------|

|            | Operating voltage                                  | 2.7  | 3.6  | V    |

| J1         | TCLK frequency of operation                        |      |      | MHz  |

|            | Boundary Scan                                      | 0    | 10   |      |

|            | JTAG and CJTAG                                     | 0    | 25   |      |

|            | Serial Wire Debug                                  | 0    | 50   |      |

| J2         | TCLK cycle period                                  | 1/J1 |      | ns   |

| J3         | TCLK clock pulse width                             |      |      |      |

|            | Boundary Scan                                      | 50   | _    | ns   |

|            | JTAG and CJTAG                                     | 20   | _    | ns   |

|            | Serial Wire Debug                                  | 10   | _    | ns   |

| J4         | TCLK rise and fall times                           | _    | 3    | ns   |

| J5         | Boundary scan input data setup time to TCLK rise   | 20   | _    | ns   |

| J6         | Boundary scan input data hold time after TCLK rise | 2.4  | _    | ns   |

| J7         | TCLK low to boundary scan output data valid        | _    | 25   | ns   |

| J8         | TCLK low to boundary scan output high-Z            | _    | 25   | ns   |

| <b>J</b> 9 | TMS, TDI input data setup time to TCLK rise        | 8    | _    | ns   |

| J10        | TMS, TDI input data hold time after TCLK rise      | 1    | _    | ns   |

| J11        | TCLK low to TDO data valid                         |      | 17   | ns   |

Table continues on the next page...

| Symbol                   | Description                                                                                                              | Min.                                                                                       | Тур. | Max.  | Unit                                                        | Notes |      |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-------|-------------------------------------------------------------|-------|------|

| f <sub>dco</sub>         | DCO output                                                                                                               | Low range (DRS=00)                                                                         | 20   | 20.97 | 25                                                          | MHz   | 2, 3 |

|                          | frequency range                                                                                                          | $640 \times f_{fll\_ref}$                                                                  |      |       |                                                             |       |      |

|                          |                                                                                                                          | Mid range (DRS=01)                                                                         | 40   | 41.94 | 50                                                          | MHz   | 1    |

|                          |                                                                                                                          | 1280 × f <sub>fll_ref</sub>                                                                |      |       |                                                             |       |      |

|                          |                                                                                                                          | Mid-high range (DRS=10)                                                                    | 60   | 62.91 | 75                                                          | MHz   | 1    |

|                          |                                                                                                                          | 1920 × f <sub>fll_ref</sub>                                                                |      |       |                                                             |       |      |

|                          |                                                                                                                          | High range (DRS=11)                                                                        | 80   | 83.89 | 100                                                         | MHz   |      |

|                          |                                                                                                                          | $2560 \times f_{fll\_ref}$                                                                 |      |       |                                                             |       |      |

| dco_t_DMX32              |                                                                                                                          | Low range (DRS=00)                                                                         |      | 23.99 | —                                                           | MHz   | 4, 5 |

|                          | frequency                                                                                                                | $732 \times f_{fll\_ref}$                                                                  |      |       |                                                             |       |      |

|                          |                                                                                                                          | Mid range (DRS=01)                                                                         | _    | 47.97 | —                                                           | MHz   |      |

|                          |                                                                                                                          | $1464 \times f_{fll\_ref}$                                                                 |      |       |                                                             |       |      |

|                          |                                                                                                                          | Mid-high range (DRS=10)                                                                    |      | 71.99 | _                                                           | MHz   |      |

|                          |                                                                                                                          | $2197 \times f_{fll\_ref}$                                                                 |      |       |                                                             |       |      |

|                          |                                                                                                                          | High range (DRS=11)                                                                        |      | 95.98 | _                                                           | MHz   |      |

|                          |                                                                                                                          | $2929 \times f_{fll\_ref}$                                                                 |      |       |                                                             |       |      |

| J <sub>cyc_fll</sub>     | FLL period jitter                                                                                                        |                                                                                            | _    | 180   | _                                                           | ps    |      |

|                          | • f <sub>VCO</sub> = 48 M                                                                                                |                                                                                            | _    | 150   | _                                                           |       |      |

|                          | • f <sub>VCO</sub> = 98 M                                                                                                |                                                                                            | 100  |       |                                                             |       |      |

| t <sub>fll_acquire</sub> | FLL target frequer                                                                                                       |                                                                                            | —    | 1     | ms                                                          | 6     |      |

|                          |                                                                                                                          | PLL                                                                                        |      |       |                                                             |       |      |

| f <sub>pll_ref</sub>     | PLL reference free                                                                                                       |                                                                                            | 8    |       | 16                                                          | MHz   |      |

| f <sub>vcoclk_2x</sub>   | VCO output freque                                                                                                        | ency                                                                                       | 180  | -     | 360                                                         | MHz   |      |

| f <sub>vcoclk</sub>      | PLL output freque                                                                                                        | ncy                                                                                        | 90   | —     | 180                                                         | MHz   |      |

| f <sub>vcoclk_90</sub>   | PLL quadrature ou                                                                                                        | Itput frequency                                                                            | 90   | _     |                                                             | MHz   |      |

|                          | DILLO energing ou                                                                                                        | rrant                                                                                      | 90   |       | 180                                                         |       |      |

| I <sub>pll</sub>         |                                                                                                                          | MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>DIV multiplier = 23)          | —    | 2.8   | _                                                           | mA    |      |

| I <sub>pll</sub>         | PLL0 operating cu                                                                                                        | rrent                                                                                      | _    | 4.7   |                                                             | mA    | 7    |

|                          |                                                                                                                          | MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>DIV multiplier = 45)          |      |       |                                                             |       |      |

| I <sub>pll</sub>         | PLL1 operating cu                                                                                                        |                                                                                            |      | 2.2   |                                                             | m۸    | 7    |

| ·                        | <ul> <li>VCO @ 184 MHz (f<sub>osc_hi_1</sub> = 32 MHz, f<sub>pll_ref</sub><br/>= 8 MHz, VDIV multiplier = 23)</li> </ul> |                                                                                            | —    | 2.3   |                                                             | mA    |      |

| I <sub>pll</sub>         |                                                                                                                          | rrent<br>MHz (f <sub>osc_hi_1</sub> = 32 MHz, f <sub>pll_ref</sub><br>DIV multiplier = 45) | _    | 3.6   | -                                                           | mA    | 7    |

| t <sub>pll_lock</sub>    | Lock detector dete                                                                                                       | ection time                                                                                | _    | _     | $100 \times 10^{-6}$<br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S     | 8    |

### Table 15. MCG specifications (continued)

Table continues on the next page ...

| Symbol          | Description                     | Conditions <sup>1</sup>              | Min.          | Typ. <sup>2</sup>      | Max.            | Unit             | Notes                                |

|-----------------|---------------------------------|--------------------------------------|---------------|------------------------|-----------------|------------------|--------------------------------------|

|                 |                                 | • ADLPC = 0, ADHSC = 0               | 3.0           | 5.2                    | 7.3             | MHz              |                                      |

|                 |                                 | • ADLPC = 0, ADHSC = 1               | 4.4           | 6.2                    | 9.5             | MHz              |                                      |

|                 | Sample Time                     | See Reference Manual chapter         | for sample ti | mes                    |                 |                  |                                      |

| TUE             | Total unadjusted                | 12-bit modes                         | _             | ±4                     | ±6.8            | LSB <sup>4</sup> | 5                                    |

|                 | error                           | 12-bit modes                         | —             | ±1.4                   | ±2.1            |                  |                                      |

| DNL             | Differential non-<br>linearity  | 12-bit modes                         | _             | ±0.7                   | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                                    |

|                 | intearity                       | <ul> <li>&lt;12-bit modes</li> </ul> | —             | ±0.2                   | -0.3 to<br>0.5  |                  |                                      |

| INL             | Integral non-linearity          | 12-bit modes                         |               | ±1.0                   | –2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                                    |

|                 |                                 | • <12-bit modes                      | —             | ±0.5                   | –0.7 to<br>+0.5 |                  |                                      |

| E <sub>FS</sub> | Full-scale error                | 12-bit modes                         | _             | -4                     | -5.4            | LSB <sup>4</sup> | $V_{ADIN} = V_{DDA}$                 |

|                 |                                 | <li>&lt;12-bit modes</li>            | —             | -1.4                   | -1.8            |                  |                                      |

| EQ              | Quantization error              | 16-bit modes                         |               | -1 to 0                |                 | LSB <sup>4</sup> |                                      |

|                 |                                 | <ul> <li>≤13-bit modes</li> </ul>    | —             | -                      | ±0.5            |                  |                                      |

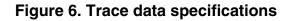

| ENOB            | Effective number of bits        | 16-bit differential mode             |               |                        |                 |                  | 6                                    |

|                 |                                 | • Avg = 32                           | 12.8          | 14.5                   | —               | bits             |                                      |

|                 |                                 | • Avg = 4                            | 11.9          | 13.8                   | —               | bits             |                                      |

|                 |                                 | 16-bit single-ended mode             |               |                        |                 |                  |                                      |

|                 |                                 | • Avg = 32                           | 12.2          | 13.9                   | _               |                  |                                      |

|                 |                                 | • Avg = 4                            | 11.4          | 13.1                   |                 | bits             |                                      |

|                 |                                 |                                      |               |                        |                 | bits             |                                      |

| SINAD           | Signal-to-noise plus distortion | See ENOB                             | 6.02 >        | ENOB +                 | 1.76            | dB               |                                      |

| THD             | Total harmonic                  | 16-bit differential mode             |               |                        |                 | dB               | 7                                    |

|                 | distortion                      | • Avg = 32                           | —             | -94                    | —               | dB               |                                      |

|                 |                                 | 16-bit single-ended mode             | _             | -85                    | _               |                  |                                      |

|                 |                                 | • Avg = 32                           |               |                        |                 |                  |                                      |

| SFDR            | Spurious free                   | 16-bit differential mode             | 00            | 05                     | _               | dB               | 7                                    |

|                 | dynamic range                   | • Avg = 32                           | 82            | 95                     | _               | dB               |                                      |

|                 |                                 | 16-bit single-ended mode             | 78            | 90                     |                 |                  |                                      |

|                 |                                 | • Avg = 32                           |               |                        |                 |                  |                                      |

| E <sub>IL</sub> | Input leakage error             |                                      |               | $I_{ln} \times R_{AS}$ |                 | mV               | I <sub>In</sub> = leakage<br>current |

Table 29. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

Table continues on the next page...

K20 Sub-Family, Rev.6, 09/2015.

Peripheral operating requirements and behaviors

#### 6.6.1.3 16-bit ADC with PGA operating conditions Table 30. 16-bit ADC with PGA operating conditions

| Symbol              | Description                | Conditions                                                                                                                                                   | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes                   |

|---------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|------|-------------------------|

| V <sub>DDA</sub>    | Supply voltage             | Absolute                                                                                                                                                     | 1.71             | —                 | 3.6              | V    |                         |

| V <sub>REFPGA</sub> | PGA ref voltage            |                                                                                                                                                              | VREF_OU<br>T     | VREF_OU<br>T      | VREF_OU<br>T     | V    | 2, 3                    |

| V <sub>ADIN</sub>   | Input voltage              |                                                                                                                                                              | V <sub>SSA</sub> | —                 | V <sub>DDA</sub> | V    |                         |

| V <sub>CM</sub>     | Input Common<br>Mode range |                                                                                                                                                              | V <sub>SSA</sub> | _                 | V <sub>DDA</sub> | V    |                         |

| R <sub>PGAD</sub>   | Differential input         | Gain = 1, 2, 4, 8                                                                                                                                            | —                | 128               | —                | kΩ   | IN+ to IN- <sup>4</sup> |

|                     | impedance                  | Gain = 16, 32                                                                                                                                                | _                | 64                | —                |      |                         |

|                     |                            | Gain = 64                                                                                                                                                    | _                | 32                | _                |      |                         |

| R <sub>AS</sub>     | Analog source resistance   |                                                                                                                                                              |                  | 100               | _                | Ω    | 5                       |

| Τ <sub>S</sub>      | ADC sampling time          |                                                                                                                                                              | 1.25             | _                 | _                | μs   | 6                       |

| C <sub>rate</sub>   | ADC conversion<br>rate     | <ul> <li>≤ 13 bit modes</li> <li>No ADC hardware<br/>averaging</li> <li>Continuous conversions<br/>enabled</li> <li>Peripheral clock = 50<br/>MHz</li> </ul> | 18.484           |                   | 450              | Ksps | 7                       |

|                     |                            | 16 bit modes                                                                                                                                                 | 37.037           |                   | 250              | Ksps | 8                       |

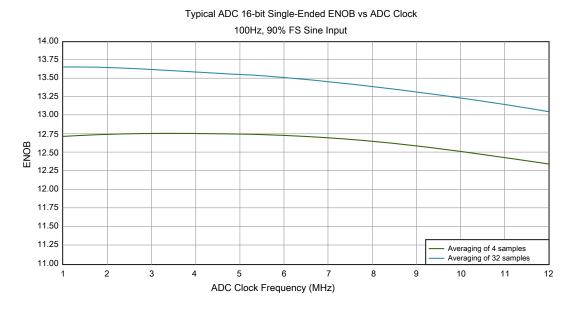

Figure 26. Offset at half scale vs. temperature

# 6.6.4 Voltage reference electrical specifications

| Table 35. | VREF full-range operating requirements |

|-----------|----------------------------------------|

|-----------|----------------------------------------|

| Symbol           | Description             | Min.                                      | Max. | Unit | Notes |

|------------------|-------------------------|-------------------------------------------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71                                      | 3.6  | V    |       |

| T <sub>A</sub>   | Temperature             | Operating temperature range of the device |      | °C   |       |

| CL               | Output load capacitance | 1(                                        | 00   | nF   | 1, 2  |

1. C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

The load capacitance should not exceed +/-25% of the nominal specified C<sub>L</sub> value over the operating temperature range of the device.

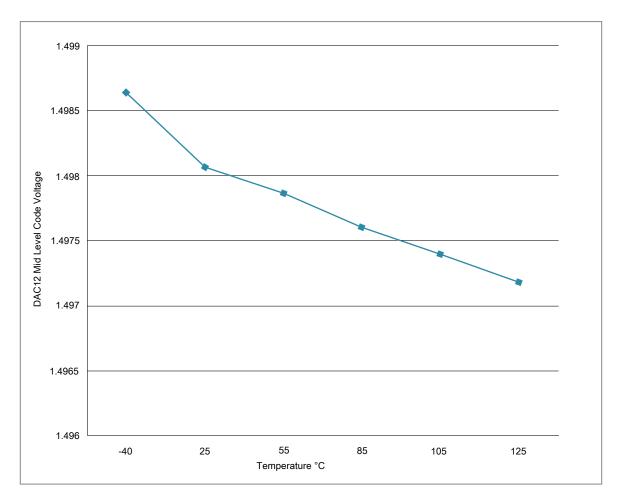

Figure 27. ULPI timing diagram

### 6.8.5 CAN switching specifications

See General switching specifications.

### 6.8.6 DSPI switching specifications (limited voltage range)

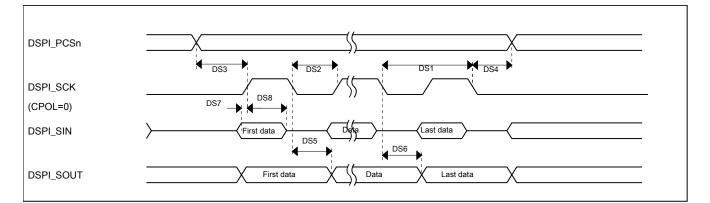

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provide DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                      | Unit | Notes |

|-----|-------------------------------------|-------------------------------|---------------------------|------|-------|

|     | Operating voltage                   | 2.7                           | 3.6                       | V    |       |

|     | Frequency of operation              | —                             | 30                        | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 2 x t <sub>BUS</sub>          | _                         | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) – 2     | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 1     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 2     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | —                             | 8.5                       | ns   |       |

Table 42.

Master mode DSPI timing (limited voltage range)

Table continues on the next page ...

#### rempheral operating requirements and behaviors

| Num | Description                      | Min. | Max. | Unit | Notes |

|-----|----------------------------------|------|------|------|-------|

| DS6 | DSPI_SCK to DSPI_SOUT invalid    | -2   | —    | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup | 15   | —    | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold  | 0    |      | ns   |       |

#### Table 42. Master mode DSPI timing (limited voltage range) (continued)

1. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

2. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

#### Figure 28. DSPI classic SPI timing — master mode

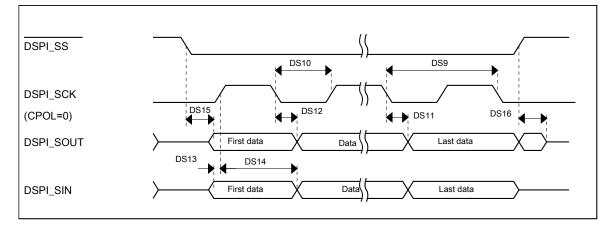

#### Table 43. Slave mode DSPI timing (limited voltage range)

| Num  | Description                              | Min.                      | Max.                      | Unit |

|------|------------------------------------------|---------------------------|---------------------------|------|

|      | Operating voltage                        | 2.7                       | 3.6                       | V    |

|      | Frequency of operation                   |                           | 15                        | MHz  |

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | —                         | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | _                         | 10                        | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                         | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         | —                         | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                         | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | _                         | 14                        | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 14                        | ns   |

Figure 29. DSPI classic SPI timing — slave mode

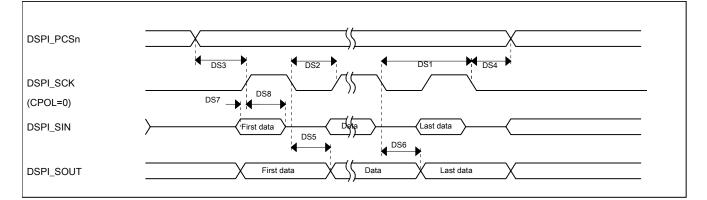

### 6.8.7 DSPI switching specifications (full voltage range)

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

|     | Operating voltage                   | 1.71                          | 3.6                      | V    | 1     |

|     | Frequency of operation              | —                             | 15                       | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 4 x t <sub>BUS</sub>          | —                        | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | —                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | —                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | —                             | 10                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -4.5                          | —                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 20.5                          | —                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             |                          | ns   |       |

Table 44. Master mode DSPI timing (full voltage range)

1. The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

#### rempheral operating requirements and behaviors

#### Figure 30. DSPI classic SPI timing — master mode

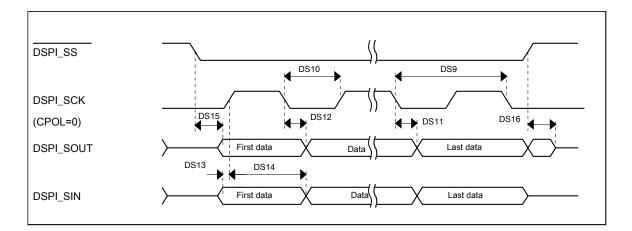

| Num  | Description                              | Min.                      | Max.                     | Unit |

|------|------------------------------------------|---------------------------|--------------------------|------|

|      | Operating voltage                        | 1.71                      | 3.6                      | V    |

|      | Frequency of operation                   |                           | 7.5                      | MHz  |

| DS9  | DSPI_SCK input cycle time                | 8 x t <sub>BUS</sub>      | —                        | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) - 4 | (t <sub>SCK/2)</sub> + 4 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              |                           | 20                       | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                        | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         | —                        | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         |                          | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 19                       | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | —                         | 19                       | ns   |

#### Table 45. Slave mode DSPI timing (full voltage range)

#### Figure 31. DSPI classic SPI timing — slave mode

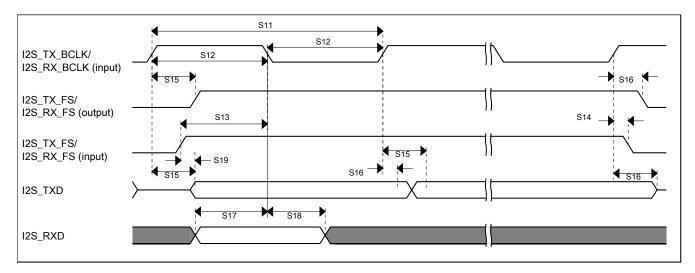

# Table 54. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range) (continued)

| Num. | Characteristic                                                    | Min. | Max. | Unit |

|------|-------------------------------------------------------------------|------|------|------|

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 30   | _    | ns   |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 3    | _    | ns   |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | —    | 63   | ns   |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | _    | ns   |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 30   | _    | ns   |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                    | 2    | _    | ns   |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>    | —    | 72   | ns   |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

Figure 39. I2S/SAI timing — slave modes

# 6.9 Human-machine interfaces (HMI)

### 6.9.1 TSI electrical specifications

Table 55. TSI electrical specifications

| Symbol              | Description                        | Min. | Тур. | Max. | Unit | Notes            |

|---------------------|------------------------------------|------|------|------|------|------------------|

| V <sub>DDTSI</sub>  | Operating voltage                  | 1.71 | —    | 3.6  | V    |                  |

| C <sub>ELE</sub>    | Target electrode capacitance range | 1    | 20   | 500  | pF   | 1                |

| f <sub>REFmax</sub> | Reference oscillator frequency     | _    | 8    | 15   | MHz  | <sup>2</sup> , 3 |

| f <sub>ELEmax</sub> | Electrode oscillator frequency     |      | 1    | 1.8  | MHz  | <sup>2</sup> , 4 |

Table continues on the next page...

K20 Sub-Family, Rev.6, 09/2015.

| 144<br>LQFP | 144<br>Map<br>Bga | Pin Name         | Default                                                      | ALT0                                                         | ALT1             | ALT2       | ALT3                                | ALT4             | ALT5    | ALT6            | ALT7 | EzPort |

|-------------|-------------------|------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------|------------|-------------------------------------|------------------|---------|-----------------|------|--------|

| 71          | G8                | VSS              | VSS                                                          | VSS                                                          |                  |            |                                     |                  |         |                 |      |        |

| 72          | M12               | PTA18            | EXTAL0                                                       | EXTAL0                                                       | PTA18            |            | FTM0_FLT2                           | FTM_CLKIN0       |         |                 |      |        |

| 73          | M11               | PTA19            | XTALO                                                        | XTAL0                                                        | PTA19            |            | FTM1_FLT0                           | FTM_CLKIN1       |         | LPTMR0_<br>ALT1 |      |        |

| 74          | L12               | RESET_b          | RESET_b                                                      | RESET_b                                                      |                  |            |                                     |                  |         |                 |      |        |

| 75          | K12               | PTA24            | CMP3_IN4                                                     | CMP3_IN4                                                     | PTA24            | ULPI_DATA2 |                                     |                  |         | FB_A29          |      |        |

| 76          | J12               | PTA25            | CMP3_IN5                                                     | CMP3_IN5                                                     | PTA25            | ULPI_DATA3 |                                     |                  |         | FB_A28          |      |        |

| 77          | J11               | PTA26            | ADC2_SE15                                                    | ADC2_SE15                                                    | PTA26            | ULPI_DATA4 |                                     |                  |         | FB_A27          |      |        |

| 78          | J10               | PTA27            | ADC2_SE14                                                    | ADC2_SE14                                                    | PTA27            | ULPI_DATA5 |                                     |                  |         | FB_A26          |      |        |

| 79          | H12               | PTA28            | ADC2_SE13                                                    | ADC2_SE13                                                    | PTA28            | ULPI_DATA6 |                                     |                  |         | FB_A25          |      |        |

| 80          | H11               | PTA29            | ADC2_SE12                                                    | ADC2_SE12                                                    | PTA29            | ULPI_DATA7 |                                     |                  |         | FB_A24          |      |        |

| 81          | H10               | PTB0/<br>LLWU_P5 | ADC0_SE8/<br>ADC1_SE8/<br>ADC2_SE8/<br>ADC3_SE8/<br>TSI0_CH0 | ADC0_SE8/<br>ADC1_SE8/<br>ADC2_SE8/<br>ADC3_SE8/<br>TSI0_CH0 | PTB0/<br>LLWU_P5 | 12C0_SCL   | FTM1_CH0                            |                  |         | FTM1_QD_<br>PHA |      |        |

| 82          | H9                | PTB1             | ADC0_SE9/<br>ADC1_SE9/<br>ADC2_SE9/<br>ADC3_SE9/<br>TSI0_CH6 | ADC0_SE9/<br>ADC1_SE9/<br>ADC2_SE9/<br>ADC3_SE9/<br>TSI0_CH6 | PTB1             | I2C0_SDA   | FTM1_CH1                            |                  |         | FTM1_QD_<br>PHB |      |        |

| 83          | G12               | PTB2             | ADC0_SE12/<br>TSI0_CH7                                       | ADC0_SE12/<br>TSI0_CH7                                       | PTB2             | I2C0_SCL   | UART0_<br>RTS_b                     |                  |         | FTM0_FLT3       |      |        |

| 84          | G11               | PTB3             | ADC0_SE13/<br>TSI0_CH8                                       | ADC0_SE13/<br>TSI0_CH8                                       | PTB3             | I2C0_SDA   | UART0_<br>CTS_b/<br>UART0_<br>COL_b |                  |         | FTM0_FLT0       |      |        |

| 85          | G10               | PTB4             | ADC1_SE10                                                    | ADC1_SE10                                                    | PTB4             |            |                                     |                  |         | FTM1_FLT0       |      |        |

| 86          | G9                | PTB5             | ADC1_SE11                                                    | ADC1_SE11                                                    | PTB5             |            |                                     |                  |         | FTM2_FLT0       |      |        |

| 87          | F12               | PTB6             | ADC1_SE12                                                    | ADC1_SE12                                                    | PTB6             |            |                                     |                  | FB_AD23 |                 |      |        |

| 88          | F11               | PTB7             | ADC1_SE13                                                    | ADC1_SE13                                                    | PTB7             |            |                                     |                  | FB_AD22 |                 |      |        |

| 89          | F10               | PTB8             | DISABLED                                                     |                                                              | PTB8             |            | UART3_<br>RTS_b                     |                  | FB_AD21 |                 |      |        |

| 90          | F9                | PTB9             | DISABLED                                                     |                                                              | PTB9             | SPI1_PCS1  | UART3_<br>CTS_b                     |                  | FB_AD20 |                 |      |        |

| 91          | E12               | PTB10            | ADC1_SE14                                                    | ADC1_SE14                                                    | PTB10            | SPI1_PCS0  | UART3_RX                            | I2S1_TX_<br>BCLK | FB_AD19 | FTM0_FLT1       |      |        |

| 92          | E11               | PTB11            | ADC1_SE15                                                    | ADC1_SE15                                                    | PTB11            | SPI1_SCK   | UART3_TX                            | I2S1_TX_FS       | FB_AD18 | FTM0_FLT2       |      |        |

| 93          | H7                | VSS              | VSS                                                          | VSS                                                          |                  |            |                                     |                  |         |                 |      |        |

| 94          | F5                | VDD              | VDD                                                          | VDD                                                          |                  |            |                                     |                  |         |                 |      |        |

| 95          | E10               | PTB16            | TSI0_CH9                                                     | TSI0_CH9                                                     | PTB16            | SPI1_SOUT  | UART0_RX                            | I2S1_TXD0        | FB_AD17 | EWM_IN          |      |        |

| 96          | E9                | PTB17            | TSI0_CH10                                                    | TSI0_CH10                                                    | PTB17            | SPI1_SIN   | UART0_TX                            | I2S1_TXD1        | FB_AD16 | EWM_OUT_b       |      |        |

| 97          | D12               | PTB18            | TSI0_CH11                                                    | TSI0_CH11                                                    | PTB18            | CAN0_TX    | FTM2_CH0                            | I2S0_TX_<br>BCLK | FB_AD15 | FTM2_QD_<br>PHA |      |        |

| 98          | D11               | PTB19            | TSI0_CH12                                                    | TSI0_CH12                                                    | PTB19            | CAN0_RX    | FTM2_CH1                            | I2S0_TX_FS       | FB_OE_b | FTM2_QD_<br>PHB |      |        |

#### K20 Sub-Family, Rev.6, 09/2015.

NP

Pinout

nevision History

| Rev. No. | Date    | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | 10/2012 | Replaced TBDs throughout.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5        | 10/2013 | <ul><li>Changes for 4N96B mask set:</li><li>Min VDD operating requirement specification updated to support operation down to 1.71V.</li></ul>                                                                                                                                                                                                                                                                                                                            |

|          |         | New specifications:                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |         | <ul> <li>Updated Vdd_ddr min specification.</li> <li>Added Vodpu specification.</li> <li>Removed loz, loz_ddr, and loz_tamper Hi-Z leakage specifications. They have been replaced by new lina, lind, and Zind specifications.</li> <li>Fpll_ref_acc specification has been added.</li> </ul>                                                                                                                                                                            |

|          |         | <ul> <li>I<sup>2</sup>C module was previously covered by the general switching specifications. To provide<br/>more detail on I<sup>2</sup>C operation a dedicated Inter-Integrated Circuit Interface (I<sup>2</sup>C) timing<br/>section has been added.</li> </ul>                                                                                                                                                                                                      |

|          |         | Modified specifications:                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |         | <ul> <li>Vref_ddr max spec has been updated.</li> <li>Tpor spec has been split into two specifications based on VDD slew rate.</li> <li>Trd1allx and Trd1alln max have been updated.</li> <li>16-bit ADC Temp sensor slope and Temp sensor voltage (Vtemp25) have been modified. The typical values that were listed previously have been updated, and min and max specifications have been added.</li> </ul>                                                            |

|          |         | Corrections:                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |         | <ul> <li>Some versions of the datasheets listed incorrect clock mode information in the<br/>"Diagram: Typical IDD_RUN operating behavior section." These errors have been<br/>corrected.</li> <li>Fintf_ft specification was previously shown as a max value. It has been corrected to be</li> </ul>                                                                                                                                                                     |

|          |         | <ul> <li>shown as a typical value as originally intended.</li> <li>Corrected DDR write and read timing diagrams to show the correct location of the Tcmv specification.</li> <li>SDHC peripheral 50MHz high speed mode options were left out of the last datasheet.</li> </ul>                                                                                                                                                                                           |

| 6        | 09/2015 | These have been added to the SDHC specifications section.     Updated the footnotes of Thermal Attributes table     Removed Power Sequencing section                                                                                                                                                                                                                                                                                                                     |

|          |         | <ul> <li>Added footnote to ambient temperature specification of Thermal Operating requirements</li> <li>Removed "USB HS/LS/FS on-the-go controller with on-chip high speed transceiver" from features section</li> <li>Updated Terminology and guidelines section</li> <li>Updated the footnotes and the values of Power consumption operating behaviors table</li> <li>Added Notes in USB electrical specification section</li> <li>Updated I2C timing table</li> </ul> |

### Table 57. Revision History (continued)

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, the Energy Efficient Solutions logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

© 2012–2015 Freescale Semiconductor, Inc.

Document Number K20P144M120SF3 Revision 6, 09/2015