Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorARM® Cortex®-M4Core Size32-Bit Single-CoreSpeed120MHzConnectivityCANbus, EBI/EMI, IPC, IrDA, SD, SPI, UART/USART, USB, USB OTGPeripheralsDMA, IPS, LVD, POR, PWM, WDTNumber of I/O100Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size16K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-MAPBGA (13x13)Purchase URLhttps://www.e-xfl.com/product-detail/nxp-semiconductors/pk20fx512vmd12 |                            |                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed120MHzConnectivityCANbus, EBI/EMI, I²C, IrDA, SD, SPI, UART/USART, USB, USB OTGPeripheralsDMA, I²S, LVD, POR, PWM, WDTNumber of I/O100Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size16K x 8RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                | Product Status             | Obsolete                                                                   |

| Speed120MHzConnectivityCANbus, EBI/EMI, I²C, IrDA, SD, SPI, UART/USART, USB, USB OTGPeripheralsDMA, I²S, LVD, POR, PWM, WDTNumber of I/O100Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size16K x 8RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                           | Core Processor             | ARM® Cortex®-M4                                                            |

| ConnectivityCANbus, EBI/EMI, I²C, IrDA, SD, SPI, UART/USART, USB, USB OTGPeripheralsDMA, I²S, LVD, POR, PWM, WDTNumber of I/O100Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size16K x 8RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                      | Core Size                  | 32-Bit Single-Core                                                         |

| PeripheralsDMA, I2S, LVD, POR, PWM, WDTNumber of I/O100Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size16K x 8RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                               | Speed                      | 120MHz                                                                     |

| Number of I/O100Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size16K x 8RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                      | Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Program Memory Size512KB (512K x 8)Program Memory TypeFLASHEEPROM Size16K x 8RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                      | Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                  |

| Program Memory TypeFLASHEEPROM Size16K x 8RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                         | Number of I/O              | 100                                                                        |

| EEPROM Size16K × 8RAM Size128K × 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                 | Program Memory Size        | 512KB (512K x 8)                                                           |

| RAM Size128K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                   | Program Memory Type        | FLASH                                                                      |

| Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                                   | EEPROM Size                | 16K x 8                                                                    |

| Data ConvertersA/D 45x16b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                                                                         | RAM Size                   | 128K x 8                                                                   |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                                                                                                             | Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Operating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                                                                                                                                    | Data Converters            | A/D 45x16b; D/A 2x12b                                                      |

| Mounting TypeSurface MountPackage / Case144-LBGASupplier Device Package144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Oscillator Type            | Internal                                                                   |

| Package / Case     144-LBGA       Supplier Device Package     144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Supplier Device Package 144-MAPBGA (13x13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mounting Type              | Surface Mount                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Package / Case             | 144-LBGA                                                                   |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/pk20fx512vmd12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Supplier Device Package    | 144-MAPBGA (13x13)                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/pk20fx512vmd12     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 2. It covers digital pins.

- 3. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

# 5 General

# 5.1 AC electrical characteristics

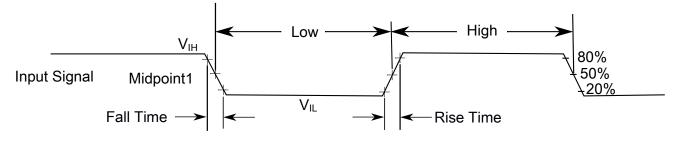

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  + ( $V_{IH}$  -  $V_{IL}$ ) / 2

Figure 1. Input signal measurement reference

All digital I/O switching characteristics assume:

- 1. output pins

- have  $C_L=30$  pF loads,

- are configured for fast slew rate (PORTx\_PCRn[SRE]=0), and

- are configured for high drive strength (PORTx\_PCRn[DSE]=1)

- 2. input pins

- have their passive filter disabled (PORTx\_PCRn[PFE]=0)

# 5.2 Nonswitching electrical specifications

## 5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol           | Description           | Min. | Max. | Unit | Notes |

|------------------|-----------------------|------|------|------|-------|

| V <sub>DD</sub>  | Supply voltage        | 1.71 | 3.6  | V    |       |

| V <sub>DDA</sub> | Analog supply voltage | 1.71 | 3.6  | V    |       |

Table continues on the next page...

General

- 5. 4 MHz core, system, 2 MHz FlexBus, and 2 MHz bus clock and 0.5 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 6. Includes 32kHz oscillator current and RTC operation.

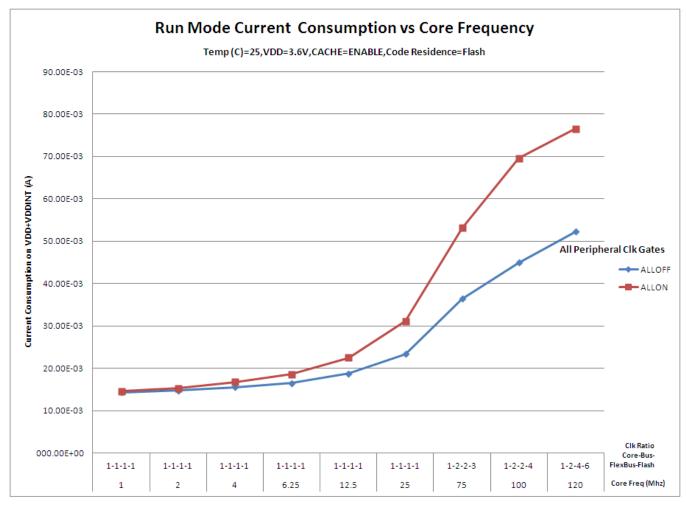

## 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at greater than 50 MHz frequencies. MCG in PEE mode at greater than 100 MHz frequencies.

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFE

Figure 3. Run mode supply current vs. core frequency

#### General

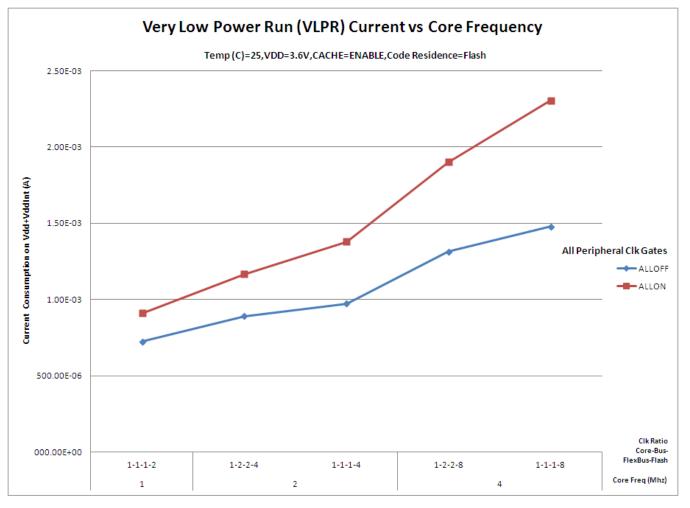

Figure 4. VLPR mode supply current vs. core frequency

## 5.2.6 EMC radiated emissions operating behaviors Table 7. EMC radiated emissions operating behaviors for 256MAPBGA

| Symbol           | Description                        | Frequency<br>band (MHz) | Тур. | Unit | Notes   |

|------------------|------------------------------------|-------------------------|------|------|---------|

| V <sub>RE1</sub> | Radiated emissions voltage, band 1 | 0.15–50                 | 21   | dBµV | 1, 2, 3 |

| V <sub>RE2</sub> | Radiated emissions voltage, band 2 | 50–150                  | 24   | dBµV |         |

| V <sub>RE3</sub> | Radiated emissions voltage, band 3 | 150–500                 | 29   | dBµV |         |

| V <sub>RE4</sub> | Radiated emissions voltage, band 4 | 500–1000                | 28   | dBµV |         |

- Determined according to IEC Standard 61967-1, Integrated Circuits Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions – TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

- 2.  $V_{DD}$  = 3.3 V,  $T_A$  = 25 °C,  $f_{OSC}$  = 12 MHz (crystal),  $f_{SYS}$  = 72 MHz,  $f_{BUS}$  = 72 MHz

- 3. Determined according to IEC Standard JESD78, IC Latch-Up Test

| Symbol            | Description                                      | Min. | Max. | Unit | Notes |

|-------------------|--------------------------------------------------|------|------|------|-------|

| t <sub>io50</sub> | Port rise and fall time (low drive strength)     |      |      |      | 7     |

|                   | Slew disabled                                    |      |      |      |       |

|                   | • $1.71 \le V_{DD} \le 2.7V$                     | _    | 18   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 9    | ns   | _     |

|                   | Slew enabled                                     |      |      |      |       |

|                   | <ul> <li>1.71 ≤ V<sub>DD</sub> ≤ 2.7V</li> </ul> | _    | 48   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 24   | ns   | _     |

| t <sub>io60</sub> | Port rise and fall time (high drive strength)    |      |      |      | 6     |

|                   | Slew disabled                                    |      |      |      |       |

|                   | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                  | _    | 6    | ns   |       |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 3    | ns   | _     |

|                   | Slew enabled                                     |      |      |      |       |

|                   | • $1.71 \le V_{DD} \le 2.7V$                     | _    | 28   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 14   | ns   | _     |

| t <sub>io60</sub> | Port rise and fall time (low drive strength)     |      |      |      | 7     |

|                   | Slew disabled                                    |      |      |      |       |

|                   | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                  | _    | 18   | ns   | _     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | _    | 6    | ns   | _     |

|                   | Slew enabled                                     |      |      |      |       |

|                   | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                  | —    | 48   | ns   | —     |

|                   | • $2.7 \le V_{DD} \le 3.6V$                      | —    | 24   | ns   | —     |

Table 10. General switching specifications (continued)

- 1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop, VLPS, LLS, and VLLSx modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater synchronous and asynchronous timing must be met.

- 3. This is the minimum pulse width that is guaranteed to be recognized as a pin interrupt request in Stop, VLPS, LLS, and VLLSx modes.

- 4. 75 pF load

- 5. 15 pF load

- 6. 25 pF load

- 7. 15 pF load

# 5.4 Thermal specifications

#### rempheral operating requirements and behaviors

| Symbol               | Description                           | Min. | Тур. | Max. | Unit | Notes |

|----------------------|---------------------------------------|------|------|------|------|-------|

|                      | • f <sub>vco</sub> = 180 MHz          | —    | 100  | _    | ps   |       |

|                      | • f <sub>vco</sub> = 360 MHz          | —    | 75   | —    | ps   |       |

| J <sub>acc_pll</sub> | PLL accumulated jitter over 1µs (RMS) |      |      |      |      | 10    |

|                      | • f <sub>vco</sub> = 180 MHz          | —    | 600  | —    | ps   |       |

|                      | • f <sub>vco</sub> = 360 MHz          | —    | 300  | —    | ps   |       |

#### Table 15. MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco t</sub>) over voltage and temperature should be considered.

- 4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 6. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 7. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 9. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- 10. Accumulated jitter depends on VCO frequency and VDIV.

# 6.3.2 Oscillator electrical specifications

### 6.3.2.1 Oscillator DC electrical specifications Table 16. Oscillator DC electrical specifications

| Symbol          | Description                             | Min. | Тур. | Max. | Unit | Notes |

|-----------------|-----------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub> | Supply voltage                          | 1.71 | —    | 3.6  | V    |       |

| IDDOSC          | Supply current — low-power mode (HGO=0) |      |      |      |      | 1     |

|                 | • 32 kHz                                | _    | 500  | _    | nA   |       |

|                 | • 4 MHz                                 | _    | 200  | _    | μA   |       |

|                 | • 8 MHz (RANGE=01)                      | _    | 300  | _    | μA   |       |

|                 | • 16 MHz                                | _    | 950  | _    | μA   |       |

|                 | • 24 MHz                                | _    | 1.2  | _    | mA   |       |

|                 | • 32 MHz                                | _    | 1.5  | _    | mA   |       |

| IDDOSC          | Supply current — high-gain mode (HGO=1) |      |      |      |      | 1     |

|                 | • 32 kHz                                | _    | 25   | _    | μA   |       |

|                 |                                         | _    | 400  | —    | μA   |       |

Table continues on the next page...

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

|                              | • 4 MHz                                                                                                | —    | 500             |      | μA   |       |

|                              | • 8 MHz (RANGE=01)                                                                                     | —    | 2.5             | _    | mA   |       |

|                              | • 16 MHz                                                                                               | —    | 3               | _    | mA   |       |

|                              | • 24 MHz                                                                                               | —    | 4               | _    | mA   |       |

|                              | • 32 MHz                                                                                               |      |                 |      |      |       |

| C <sub>x</sub>               | EXTAL load capacitance                                                                                 | —    | —               | —    |      | 2, 3  |

| Cy                           | XTAL load capacitance                                                                                  |      |                 | —    |      | 2, 3  |

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                              | —    | —               | _    | MΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                              | —    | 10              |      | MΩ   |       |

|                              | Feedback resistor — high-frequency, low-power mode (HGO=0)                                             | —    | _               | _    | MΩ   |       |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                             | —    | 1               | _    | MΩ   |       |

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                                | —    | _               | _    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | —    | 200             | _    | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                               | _    |                 | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | —    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | —    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | —    | V <sub>DD</sub> | _    | V    |       |

Table 16. Oscillator DC electrical specifications (continued)

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3.  $C_x$  and  $C_y$  can be provided by using either integrated capacitors or external components.

- 4. When low-power mode is selected, R<sub>F</sub> is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other device.

| Symbol          | Description                     | Conditions <sup>1</sup>              | Min.          | Typ. <sup>2</sup>      | Max.            | Unit             | Notes                                |

|-----------------|---------------------------------|--------------------------------------|---------------|------------------------|-----------------|------------------|--------------------------------------|

|                 |                                 | • ADLPC = 0, ADHSC = 0               | 3.0           | 5.2                    | 7.3             | MHz              |                                      |

|                 |                                 | • ADLPC = 0, ADHSC = 1               | 4.4           | 6.2                    | 9.5             | MHz              |                                      |

|                 | Sample Time                     | See Reference Manual chapter         | for sample ti | mes                    |                 |                  |                                      |

| TUE             | Total unadjusted                | 12-bit modes                         | _             | ±4                     | ±6.8            | LSB <sup>4</sup> | 5                                    |

|                 | error                           | 12-bit modes                         | —             | ±1.4                   | ±2.1            |                  |                                      |

| DNL             | Differential non-<br>linearity  | 12-bit modes                         | _             | ±0.7                   | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                                    |

|                 | intearity                       | <ul> <li>&lt;12-bit modes</li> </ul> | —             | ±0.2                   | -0.3 to<br>0.5  |                  |                                      |

| INL             | Integral non-linearity          | 12-bit modes                         |               | ±1.0                   | –2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                                    |

|                 |                                 | • <12-bit modes                      | —             | ±0.5                   | –0.7 to<br>+0.5 |                  |                                      |

| E <sub>FS</sub> | Full-scale error                | 12-bit modes                         | _             | -4                     | -5.4            | LSB <sup>4</sup> | $V_{ADIN} = V_{DDA}$                 |

|                 |                                 | <li>&lt;12-bit modes</li>            | —             | -1.4                   | -1.8            |                  |                                      |

| EQ              | Quantization error              | 16-bit modes                         |               | -1 to 0                |                 | LSB <sup>4</sup> |                                      |

|                 |                                 | <ul> <li>≤13-bit modes</li> </ul>    | —             | -                      | ±0.5            |                  |                                      |

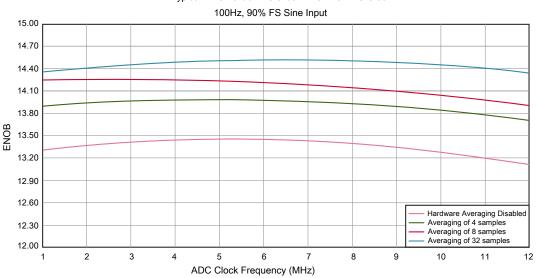

| ENOB            | Effective number of             | 16-bit differential mode             |               |                        |                 |                  | 6                                    |

|                 | bits                            | • Avg = 32                           | 12.8          | 14.5                   | —               | bits             |                                      |

|                 |                                 | • Avg = 4                            | 11.9          | 13.8                   | —               | bits             |                                      |

|                 |                                 | 16-bit single-ended mode             |               |                        |                 |                  |                                      |

|                 |                                 | • Avg = 32                           | 12.2          | 13.9                   | _               |                  |                                      |

|                 |                                 | • Avg = 4                            | 11.4          | 13.1                   |                 | bits             |                                      |

|                 |                                 |                                      |               |                        |                 | bits             |                                      |

| SINAD           | Signal-to-noise plus distortion | See ENOB                             | 6.02 >        | ENOB +                 | 1.76            | dB               |                                      |

| THD             | Total harmonic                  | 16-bit differential mode             |               |                        |                 | dB               | 7                                    |

|                 | distortion                      | • Avg = 32                           | —             | -94                    | —               | dB               |                                      |

|                 |                                 | 16-bit single-ended mode             | _             | -85                    | _               |                  |                                      |

|                 |                                 | • Avg = 32                           |               |                        |                 |                  |                                      |

| SFDR            | Spurious free                   | 16-bit differential mode             | 00            | 05                     | _               | dB               | 7                                    |

|                 | dynamic range                   | • Avg = 32                           | 82            | 95                     | _               | dB               |                                      |

|                 |                                 | 16-bit single-ended mode             | 78            | 90                     |                 |                  |                                      |

|                 |                                 | • Avg = 32                           |               |                        |                 |                  |                                      |

| E <sub>IL</sub> | Input leakage error             |                                      |               | $I_{ln} \times R_{AS}$ |                 | mV               | I <sub>In</sub> = leakage<br>current |

Table 29. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

Table continues on the next page...

| Symbol              | Description         | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup> | Max. | Unit  | Notes                                                                  |

|---------------------|---------------------|-------------------------------------------------|------|-------------------|------|-------|------------------------------------------------------------------------|

|                     |                     |                                                 |      |                   |      |       | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor slope   | Across the full temperature range of the device | 1.55 | 1.62              | 1.69 | mV/°C | 8                                                                      |

| V <sub>TEMP25</sub> | Temp sensor voltage | 25 °C                                           | 706  | 716               | 726  | mV    | 8                                                                      |

## Table 29. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^{N}$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Typical ADC 16-bit Differential ENOB vs ADC Clock

Figure 21. Typical ENOB vs. ADC\_CLK for 16-bit differential mode

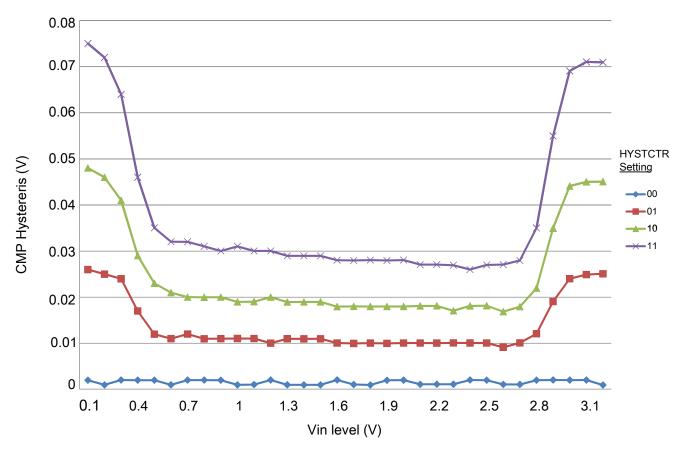

Table 32. Comparator and 6-bit DAC electrical specifications (continued)

| Symbol | Description                          | Min. | Тур. | Max. | Unit             |

|--------|--------------------------------------|------|------|------|------------------|

| INL    | 6-bit DAC integral non-linearity     | -0.5 | _    | 0.5  | LSB <sup>3</sup> |

| DNL    | 6-bit DAC differential non-linearity | -0.3 |      | 0.3  | LSB              |

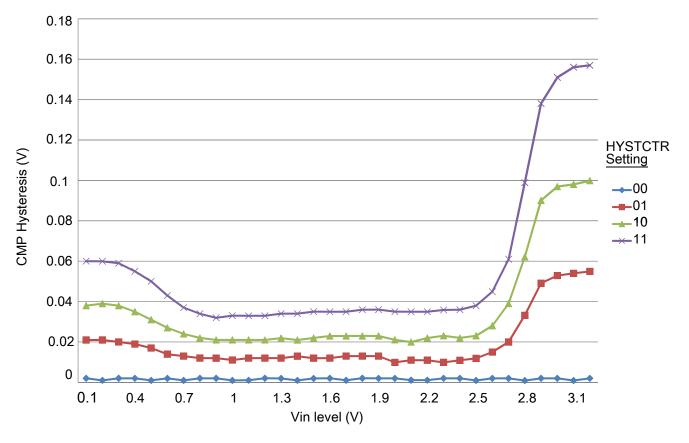

1. Typical hysteresis is measured with input voltage range limited to 0.6 to V<sub>DD</sub>-0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

Figure 23. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

Figure 24. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

# 6.6.3 12-bit DAC electrical characteristics

## 6.6.3.1 12-bit DAC operating requirements Table 33. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max. | Unit | Notes |

|-------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub>  | Supply voltage          | 1.71 | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| CL                | Output load capacitance | —    | 100  | pF   | 2     |

| ١L                | Output load current     |      | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}$

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

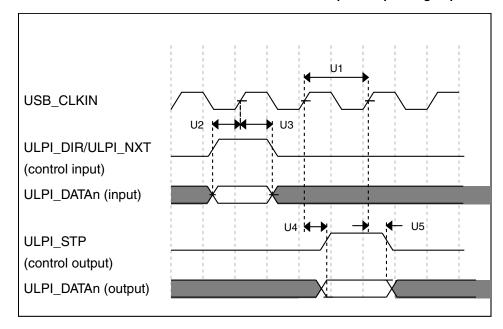

Figure 27. ULPI timing diagram

# 6.8.5 CAN switching specifications

See General switching specifications.

# 6.8.6 DSPI switching specifications (limited voltage range)

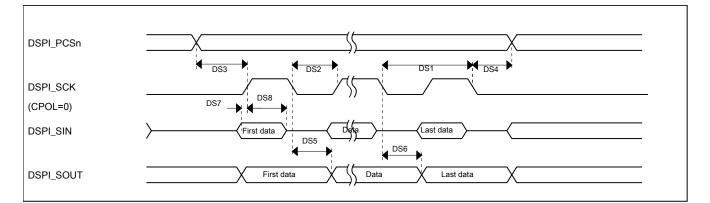

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provide DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                      | Unit | Notes |

|-----|-------------------------------------|-------------------------------|---------------------------|------|-------|

|     | Operating voltage                   | 2.7                           | 3.6                       | V    |       |

|     | Frequency of operation              | —                             | 30                        | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 2 x t <sub>BUS</sub>          | _                         | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) – 2     | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 1     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 2     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | —                             | 8.5                       | ns   |       |

Table 42.

Master mode DSPI timing (limited voltage range)

Table continues on the next page ...

#### rempheral operating requirements and behaviors

| Num | Description                      | Min. | Max. | Unit | Notes |

|-----|----------------------------------|------|------|------|-------|

| DS6 | DSPI_SCK to DSPI_SOUT invalid    | -2   | —    | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup | 15   | —    | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold  | 0    |      | ns   |       |

## Table 42. Master mode DSPI timing (limited voltage range) (continued)

1. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

2. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

### Figure 28. DSPI classic SPI timing — master mode

### Table 43. Slave mode DSPI timing (limited voltage range)

| Num  | Description                              | Min.                      | Max.                      | Unit |

|------|------------------------------------------|---------------------------|---------------------------|------|

|      | Operating voltage                        | 2.7                       | 3.6                       | V    |

|      | Frequency of operation                   |                           | 15                        | MHz  |

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | —                         | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | _                         | 10                        | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                         | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         | —                         | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                         | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 14                        | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 14                        | ns   |

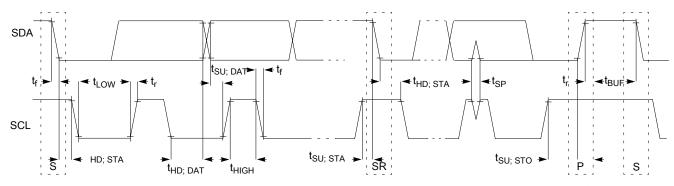

# 6.8.8 Inter-Integrated Circuit Interface (I<sup>2</sup>C) timing

Table 46. I<sup>2</sup>C timing

| Characteristic                                                                                     | Symbol                | Standa           | rd Mode           | Fast                               | Mode             | Unit |

|----------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|------|

|                                                                                                    |                       | Minimum          | Maximum           | Minimum                            | Maximum          |      |

| SCL Clock Frequency                                                                                | f <sub>SCL</sub>      | 0                | 100               | 0                                  | 400 <sup>1</sup> | kHz  |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA | 4                | _                 | 0.6                                | —                | μs   |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>      | 4.7              | _                 | 1.25                               | —                | μs   |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>     | 4                | _                 | 0.6                                | —                | μs   |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA | 4.7              | _                 | 0.6                                | —                | μs   |

| Data hold time for I <sup>2</sup> C bus devices                                                    | t <sub>HD</sub> ; DAT | 0 <sup>2</sup>   | 3.45 <sup>3</sup> | 04                                 | 0.9 <sup>2</sup> | μs   |

| Data set-up time                                                                                   | t <sub>SU</sub> ; DAT | 250 <sup>5</sup> |                   | 100 <sup>3,6</sup>                 | _                | ns   |

| Rise time of SDA and SCL signals                                                                   | t <sub>r</sub>        | _                | 1000              | 20 +0.1C <sub>b</sub> <sup>7</sup> | 300              | ns   |

| Fall time of SDA and SCL signals                                                                   | t <sub>f</sub>        | —                | 300               | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns   |

| Set-up time for STOP condition                                                                     | t <sub>SU</sub> ; STO | 4                |                   | 0.6                                | _                | μs   |

| Bus free time between STOP and<br>START condition                                                  | t <sub>BUF</sub>      | 4.7              | —                 | 1.3                                | —                | μs   |

| Pulse width of spikes that must be<br>suppressed by the input filter                               | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns   |

- 1. The maximum SCL Clock Frequency in Fast mode with maximum bus loading can only be achieved when using a pin configured for high drive across the full voltage range and when using the a pin configured for low drive with VDD ≥ 2.7 V.

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves

acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL

lines.

- 3. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 4. Input signal Slew = 10 ns and Output Load = 50 pF

- 5. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 6. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 7.  $C_b$  = total capacitance of the one bus line in pF.

Figure 32. Timing definition for fast and standard mode devices on the I<sup>2</sup>C bus

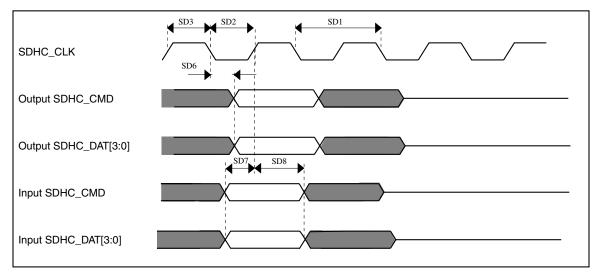

| Num | Symbol                                                               | Description                                   | Min.         | Max.      | Unit |  |  |  |

|-----|----------------------------------------------------------------------|-----------------------------------------------|--------------|-----------|------|--|--|--|

| SD5 | t <sub>THL</sub>                                                     | Clock fall time                               | —            | 3         | ns   |  |  |  |

|     | SDHC output / card inputs SDHC_CMD, SDHC_DAT (reference to SDHC_CLK) |                                               |              |           |      |  |  |  |

| SD6 | t <sub>OD</sub>                                                      | SDHC output delay (output valid)              | -5           | 6.5       | ns   |  |  |  |

|     |                                                                      | SDHC input / card inputs SDHC_CMD, SDHC_DAT ( | reference to | SDHC_CLK) |      |  |  |  |

| SD7 | t <sub>ISU</sub>                                                     | SDHC input setup time                         | 5            | —         | ns   |  |  |  |

| SD8 | t <sub>IH</sub>                                                      | SDHC input hold time                          | 1.3          |           | ns   |  |  |  |

Table 48. SDHC switching specifications over the full operating voltage range (continued)

Figure 33. SDHC timing

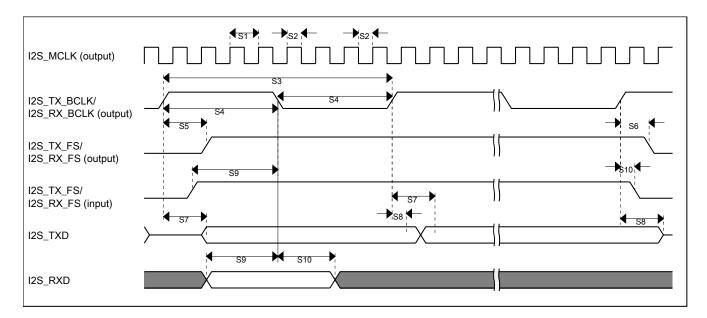

# 6.8.11 I2S/SAI switching specifications

This section provides the AC timing for the I2S/SAI module in master mode (clocks are driven) and slave mode (clocks are input). All timing is given for noninverted serial clock polarity (TCR2[BCP] is 0, RCR2[BCP] is 0) and a noninverted frame sync (TCR4[FSP] is 0, RCR4[FSP] is 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the bit clock signal (BCLK) and/or the frame sync (FS) signal shown in the following figures.

# 6.8.11.1 Normal Run, Wait and Stop mode performance over a limited operating voltage range

This section provides the operating performance over a limited operating voltage for the device in Normal Run, Wait and Stop modes.

# Table 51. I2S/SAI master mode timing in Normal Run, Wait and Stop modes (full voltage range) (continued)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

| S1   | I2S_MCLK cycle time                                               | 40   | —    | ns          |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 80   | _    | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   |      | 15   | ns          |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | -1.0 | -    | ns          |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | -    | 15   | ns          |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | _    | ns          |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 20.5 | -    | ns          |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | _    | ns          |

## Figure 36. I2S/SAI timing — master modes

# Table 52.I2S/SAI slave mode timing in Normal Run, Wait and Stop modes<br/>(full voltage range)

| Num. | Characteristic                                       | Min. | Max. | Unit        |

|------|------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                    | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)           | 80   | —    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input) | 45%  | 55%  | MCLK period |

Table continues on the next page ...

| Symbol               | Description                                                                      | Min.  | Тур.   | Max.  | Unit     | Notes            |

|----------------------|----------------------------------------------------------------------------------|-------|--------|-------|----------|------------------|

| C <sub>REF</sub>     | Internal reference capacitor                                                     | —     | 1      | —     | pF       |                  |

| V <sub>DELTA</sub>   | Oscillator delta voltage                                                         | _     | 600    | _     | mV       | <sup>2</sup> , 5 |

| I <sub>REF</sub>     | Reference oscillator current source base current<br>• 2 μA setting (REFCHRG = 0) | _     | 2      | 3     | μA       | 2, 6             |

|                      | <ul> <li>32 µA setting (REFCHRG = 15)</li> </ul>                                 | —     | 36     | 50    |          |                  |

| I <sub>ELE</sub>     | Electrode oscillator current source base current<br>• 2 µA setting (EXTCHRG = 0) | _     | 2      | 3     | μA       | 2, 7             |

|                      | <ul> <li>32 μA setting (EXTCHRG = 15)</li> </ul>                                 | —     | 36     | 50    |          |                  |

| Pres5                | Electrode capacitance measurement precision                                      | _     | 8.3333 | 38400 | fF/count | 8                |

| Pres20               | Electrode capacitance measurement precision                                      | _     | 8.3333 | 38400 | fF/count | 9                |

| Pres100              | Electrode capacitance measurement precision                                      | _     | 8.3333 | 38400 | fF/count | 10               |

| MaxSens              | Maximum sensitivity                                                              | 0.008 | 1.46   | _     | fF/count | 11               |

| Res                  | Resolution                                                                       | _     | _      | 16    | bits     |                  |

| T <sub>Con20</sub>   | Response time @ 20 pF                                                            | 8     | 15     | 25    | μs       | 12               |

| I <sub>TSI_RUN</sub> | Current added in run mode                                                        | _     | 55     | —     | μA       |                  |

| I <sub>TSI_LP</sub>  | Low power mode current adder                                                     |       | 1.3    | 2.5   | μA       | 13               |

Table 55. TSI electrical specifications (continued)

1. The TSI module is functional with capacitance values outside this range. However, optimal performance is not guaranteed.

- 2. Fixed external capacitance of 20 pF.

- 3. REFCHRG = 2, EXTCHRG=0.

- 4. REFCHRG = 0, EXTCHRG = 10.

- 5.  $V_{DD} = 3.0 V.$

- 6. The programmable current source value is generated by multiplying the SCANC[REFCHRG] value and the base current.

- 7. The programmable current source value is generated by multiplying the SCANC[EXTCHRG] value and the base current.

- 8. Measured with a 5 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 8; lext = 16.

- 9. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 2; lext = 16.

- 10. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 16, NSCN = 3; lext = 16.

- 11. Sensitivity defines the minimum capacitance change when a single count from the TSI module changes. Sensitivity depends on the configuration used. The documented values are provided as examples calculated for a specific configuration of operating conditions using the following equation: (C<sub>ref</sub> \* I<sub>ext</sub>)/( I<sub>ref</sub> \* PS \* NSCN)

The typical value is calculated with the following configuration:

$I_{ext}$  = 6  $\mu$ A (EXTCHRG = 2), PS = 128, NSCN = 2,  $I_{ref}$  = 16  $\mu$ A (REFCHRG = 7),  $C_{ref}$  = 1.0 pF

The minimum value is calculated with the following configuration:

$I_{ext}$  = 2 µA (EXTCHRG = 0), PS = 128, NSCN = 32,  $I_{ref}$  = 32 µA (REFCHRG = 15),  $C_{ref}$  = 0.5 pF

The highest possible sensitivity is the minimum value because it represents the smallest possible capacitance that can be measured by a single count.

- 12. Time to do one complete measurement of the electrode. Sensitivity resolution of 0.0133 pF, PS = 0, NSCN = 0, 1 electrode, EXTCHRG = 7.

- 13. REFCHRG=0, EXTCHRG=4, PS=7, NSCN=0F, LPSCNITV=F, LPO is selected (1 kHz), and fixed external capacitance of 20 pF. Data is captured with an average of 7 periods window.

# 7 Dimensions

| ۲ | 11 | I | υ | u | t |  |

|---|----|---|---|---|---|--|

| Г | II | I | υ | u | L |  |

| 144<br>LQFP | 144<br>MAP<br>BGA | Pin Name                                       | Default                                        | ALTO                                           | ALT1             | ALT2      | ALT3            | ALT4             | ALT5 | ALT6     | ALT7            | EzPort |

|-------------|-------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------|-----------|-----------------|------------------|------|----------|-----------------|--------|

| _           | C10               | NC                                             | NC                                             | NC                                             |                  |           |                 |                  |      |          |                 |        |

| 1           | D3                | PTE0                                           | ADC1_SE4a                                      | ADC1_SE4a                                      | PTE0             | SPI1_PCS1 | UART1_TX        | SDHC0_D1         |      | I2C1_SDA | RTC_<br>CLKOUT  |        |

| 2           | D2                | PTE1/<br>LLWU_P0                               | ADC1_SE5a                                      | ADC1_SE5a                                      | PTE1/<br>LLWU_P0 | SPI1_SOUT | UART1_RX        | SDHC0_D0         |      | I2C1_SCL | SPI1_SIN        |        |

| 3           | D1                | PTE2/<br>LLWU_P1                               | ADC1_SE6a                                      | ADC1_SE6a                                      | PTE2/<br>LLWU_P1 | SPI1_SCK  | UART1_<br>CTS_b | SDHC0_<br>DCLK   |      |          |                 |        |

| 4           | E4                | PTE3                                           | ADC1_SE7a                                      | ADC1_SE7a                                      | PTE3             | SPI1_SIN  | UART1_<br>RTS_b | SDHC0_CMD        |      |          | SPI1_SOUT       |        |

| 5           | E5                | VDD                                            | VDD                                            | VDD                                            |                  |           |                 |                  |      |          |                 |        |

| 6           | F6                | VSS                                            | VSS                                            | VSS                                            |                  |           |                 |                  |      |          |                 |        |

| 7           | E3                | PTE4/<br>LLWU_P2                               | DISABLED                                       |                                                | PTE4/<br>LLWU_P2 | SPI1_PCS0 | UART3_TX        | SDHC0_D3         |      |          |                 |        |

| 8           | E2                | PTE5                                           | DISABLED                                       |                                                | PTE5             | SPI1_PCS2 | UART3_RX        | SDHC0_D2         |      | FTM3_CH0 |                 |        |

| 9           | E1                | PTE6                                           | DISABLED                                       |                                                | PTE6             | SPI1_PCS3 | UART3_<br>CTS_b | I2S0_MCLK        |      | FTM3_CH1 | USB_SOF_<br>OUT |        |

| 10          | F4                | PTE7                                           | DISABLED                                       |                                                | PTE7             |           | UART3_<br>RTS_b | I2S0_RXD0        |      | FTM3_CH2 |                 |        |

| 11          | F3                | PTE8                                           | ADC2_SE16                                      | ADC2_SE16                                      | PTE8             | I2S0_RXD1 | UART5_TX        | I2S0_RX_FS       |      | FTM3_CH3 |                 |        |

| 12          | F2                | PTE9                                           | ADC2_SE17                                      | ADC2_SE17                                      | PTE9             | I2S0_TXD1 | UART5_RX        | I2S0_RX_<br>BCLK |      | FTM3_CH4 |                 |        |

| 13          | F1                | PTE10                                          | DISABLED                                       |                                                | PTE10            |           | UART5_<br>CTS_b | I2S0_TXD0        |      | FTM3_CH5 |                 |        |

| 14          | G4                | PTE11                                          | ADC3_SE16                                      | ADC3_SE16                                      | PTE11            |           | UART5_<br>RTS_b | I2S0_TX_FS       |      | FTM3_CH6 |                 |        |

| 15          | G3                | PTE12                                          | ADC3_SE17                                      | ADC3_SE17                                      | PTE12            |           |                 | I2S0_TX_<br>BCLK |      | FTM3_CH7 |                 |        |

| 16          | E6                | VDD                                            | VDD                                            | VDD                                            |                  |           |                 |                  |      |          |                 |        |

| 17          | F7                | VSS                                            | VSS                                            | VSS                                            |                  |           |                 |                  |      |          |                 |        |

| 18          | H3                | VSS                                            | VSS                                            | VSS                                            |                  |           |                 |                  |      |          |                 |        |

| 19          | H1                | USB0_DP                                        | USB0_DP                                        | USB0_DP                                        |                  |           |                 |                  |      |          |                 |        |

| 20          | H2                | USB0_DM                                        | USB0_DM                                        | USB0_DM                                        |                  |           |                 |                  |      |          |                 |        |

| 21          | G1                | VOUT33                                         | VOUT33                                         | VOUT33                                         |                  |           |                 |                  |      |          |                 |        |

| 22          | G2                | VREGIN                                         | VREGIN                                         | VREGIN                                         |                  |           |                 |                  |      |          |                 |        |

| 23          | J1                | PGA2_DP/<br>ADC2_DP0/<br>ADC3_DP3/<br>ADC0_DP1 | PGA2_DP/<br>ADC2_DP0/<br>ADC3_DP3/<br>ADC0_DP1 | PGA2_DP/<br>ADC2_DP0/<br>ADC3_DP3/<br>ADC0_DP1 |                  |           |                 |                  |      |          |                 |        |

| 24          | J2                | PGA2_DM/<br>ADC2_DM0/<br>ADC3_DM3/<br>ADC0_DM1 | PGA2_DM/<br>ADC2_DM0/<br>ADC3_DM3/<br>ADC0_DM1 | PGA2_DM/<br>ADC2_DM0/<br>ADC3_DM3/<br>ADC0_DM1 |                  |           |                 |                  |      |          |                 |        |

| 25          | K1                | PGA3_DP/<br>ADC3_DP0/<br>ADC2_DP3/<br>ADC1_DP1 | PGA3_DP/<br>ADC3_DP0/<br>ADC2_DP3/<br>ADC1_DP1 | PGA3_DP/<br>ADC3_DP0/<br>ADC2_DP3/<br>ADC1_DP1 |                  |           |                 |                  |      |          |                 |        |

rmout

| 144<br>LQFP | 144<br>Map<br>Bga | Pin Name          | Default                               | ALTO      | ALT1              | ALT2                                | ALT3                                | ALT4             | ALT5     | ALT6             | ALT7                       | EzPort   |

|-------------|-------------------|-------------------|---------------------------------------|-----------|-------------------|-------------------------------------|-------------------------------------|------------------|----------|------------------|----------------------------|----------|

| 48          | J4                | PTE27             | ADC3_SE4b                             | ADC3_SE4b | PTE27             |                                     | UART4_<br>RTS_b                     | I2S1_MCLK        |          |                  |                            |          |

| 49          | H4                | PTE28             | ADC3_SE7a                             | ADC3_SE7a | PTE28             |                                     |                                     |                  |          |                  |                            |          |

| 50          | J5                | PTA0              | JTAG_TCLK/<br>SWD_CLK/<br>EZP_CLK     | TSI0_CH1  | PTA0              | UART0_<br>CTS_b/<br>UART0_<br>COL_b | FTM0_CH5                            |                  |          |                  | JTAG_TCLK/<br>SWD_CLK      | EZP_CLK  |

| 51          | J6                | PTA1              | JTAG_TDI/<br>EZP_DI                   | TSI0_CH2  | PTA1              | UART0_RX                            | FTM0_CH6                            |                  |          |                  | JTAG_TDI                   | EZP_DI   |

| 52          | K6                | PTA2              | JTAG_TDO/<br>TRACE_<br>SWO/<br>EZP_DO | TSI0_CH3  | PTA2              | UART0_TX                            | FTM0_CH7                            |                  |          |                  | JTAG_TDO/<br>TRACE_<br>SWO | EZP_DO   |

| 53          | K7                | PTA3              | JTAG_TMS/<br>SWD_DIO                  | TSI0_CH4  | PTA3              | UART0_<br>RTS_b                     | FTM0_CH0                            |                  |          |                  | JTAG_TMS/<br>SWD_DIO       |          |

| 54          | L7                | PTA4/<br>LLWU_P3  | NMI_b/<br>EZP_CS_b                    | TSI0_CH5  | PTA4/<br>LLWU_P3  |                                     | FTM0_CH1                            |                  |          |                  | NMI_b                      | EZP_CS_b |

| 55          | M8                | PTA5              | DISABLED                              |           | PTA5              | USB_CLKIN                           | FTM0_CH2                            |                  | CMP2_OUT | I2S0_TX_<br>BCLK | JTAG_TRST_<br>b            |          |

| 56          | E7                | VDD               | VDD                                   | VDD       |                   |                                     |                                     |                  |          |                  |                            |          |

| 57          | G7                | VSS               | VSS                                   | VSS       |                   |                                     |                                     |                  |          |                  |                            |          |

| 58          | J7                | PTA6              | ADC3_SE6a                             | ADC3_SE6a | PTA6              | ULPI_CLK                            | FTM0_CH3                            | I2S1_RXD0        | CLKOUT   |                  | TRACE_<br>CLKOUT           |          |

| 59          | J8                | PTA7              | ADC0_SE10                             | ADC0_SE10 | PTA7              | ULPI_DIR                            | FTM0_CH4                            | I2S1_RX_<br>BCLK |          |                  | TRACE_D3                   |          |

| 60          | K8                | PTA8              | ADC0_SE11                             | ADC0_SE11 | PTA8              | ULPI_NXT                            | FTM1_CH0                            | I2S1_RX_FS       |          | FTM1_QD_<br>PHA  | TRACE_D2                   |          |

| 61          | L8                | PTA9              | ADC3_SE5a                             | ADC3_SE5a | PTA9              | ULPI_STP                            | FTM1_CH1                            |                  |          | FTM1_QD_<br>PHB  | TRACE_D1                   |          |

| 62          | M9                | PTA10             | ADC3_SE4a                             | ADC3_SE4a | PTA10             | ULPI_DATA0                          | FTM2_CH0                            |                  |          | FTM2_QD_<br>PHA  | TRACE_D0                   |          |

| 63          | L9                | PTA11             | ADC3_SE15                             | ADC3_SE15 | PTA11             | ULPI_DATA1                          | FTM2_CH1                            |                  |          | FTM2_QD_<br>PHB  |                            |          |

| 64          | K9                | PTA12             | CMP2_IN0                              | CMP2_IN0  | PTA12             | CAN0_TX                             | FTM1_CH0                            |                  |          | I2S0_TXD0        | FTM1_QD_<br>PHA            |          |

| 65          | J9                | PTA13/<br>LLWU_P4 | CMP2_IN1                              | CMP2_IN1  | PTA13/<br>LLWU_P4 | CAN0_RX                             | FTM1_CH1                            |                  |          | I2S0_TX_FS       | FTM1_QD_<br>PHB            |          |

| 66          | L10               | PTA14             | CMP3_IN0                              | CMP3_IN0  | PTA14             | SPI0_PCS0                           | UART0_TX                            |                  |          | I2S0_RX_<br>BCLK | I2S0_TXD1                  |          |

| 67          | L11               | PTA15             | CMP3_IN1                              | CMP3_IN1  | PTA15             | SPI0_SCK                            | UART0_RX                            |                  |          | I2S0_RXD0        |                            |          |

| 68          | K10               | PTA16             | CMP3_IN2                              | CMP3_IN2  | PTA16             | SPI0_SOUT                           | UART0_<br>CTS_b/<br>UART0_<br>COL_b |                  |          | I2S0_RX_FS       | 12S0_RXD1                  |          |

| 69          | K11               | PTA17             | ADC1_SE17                             | ADC1_SE17 | PTA17             | SPI0_SIN                            | UART0_<br>RTS_b                     |                  |          | I2S0_MCLK        |                            |          |

| 70          | E8                | VDD               | VDD                                   | VDD       |                   |                                     |                                     |                  |          |                  |                            |          |

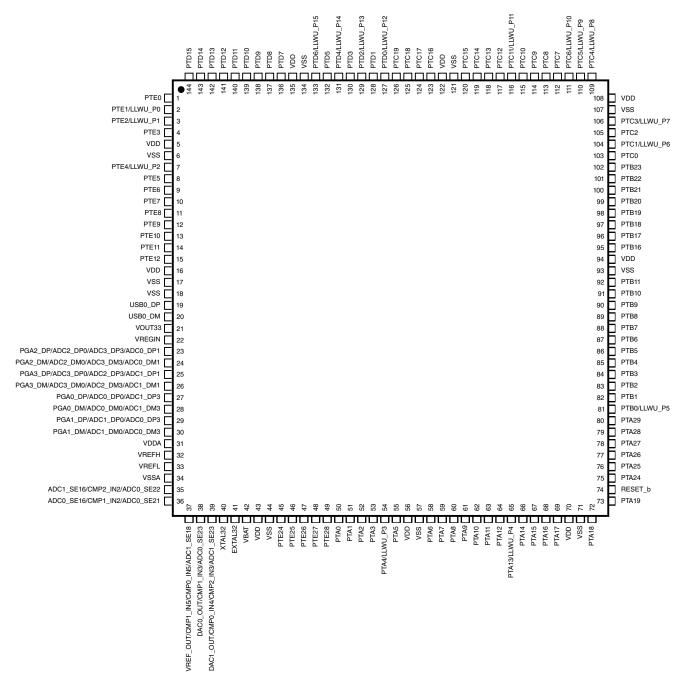

# 8.3 K20 pinouts

The figure below shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

nevision History

| Rev. No. | Date    | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | 10/2012 | Replaced TBDs throughout.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5        | 10/2013 | <ul><li>Changes for 4N96B mask set:</li><li>Min VDD operating requirement specification updated to support operation down to 1.71V.</li></ul>                                                                                                                                                                                                                                                                                                                            |

|          |         | New specifications:                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |         | <ul> <li>Updated Vdd_ddr min specification.</li> <li>Added Vodpu specification.</li> <li>Removed loz, loz_ddr, and loz_tamper Hi-Z leakage specifications. They have been replaced by new lina, lind, and Zind specifications.</li> <li>Fpll_ref_acc specification has been added.</li> </ul>                                                                                                                                                                            |

|          |         | <ul> <li>I<sup>2</sup>C module was previously covered by the general switching specifications. To provide<br/>more detail on I<sup>2</sup>C operation a dedicated Inter-Integrated Circuit Interface (I<sup>2</sup>C) timing<br/>section has been added.</li> </ul>                                                                                                                                                                                                      |