#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC 603e                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 166MHz                                                                  |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | SDRAM                                                                   |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | -                                                                       |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 3.3V                                                                    |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                       |

| Package / Case                  | 357-BBGA                                                                |

| Supplier Device Package         | 357-PBGA (25x25)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8241tvr166d |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

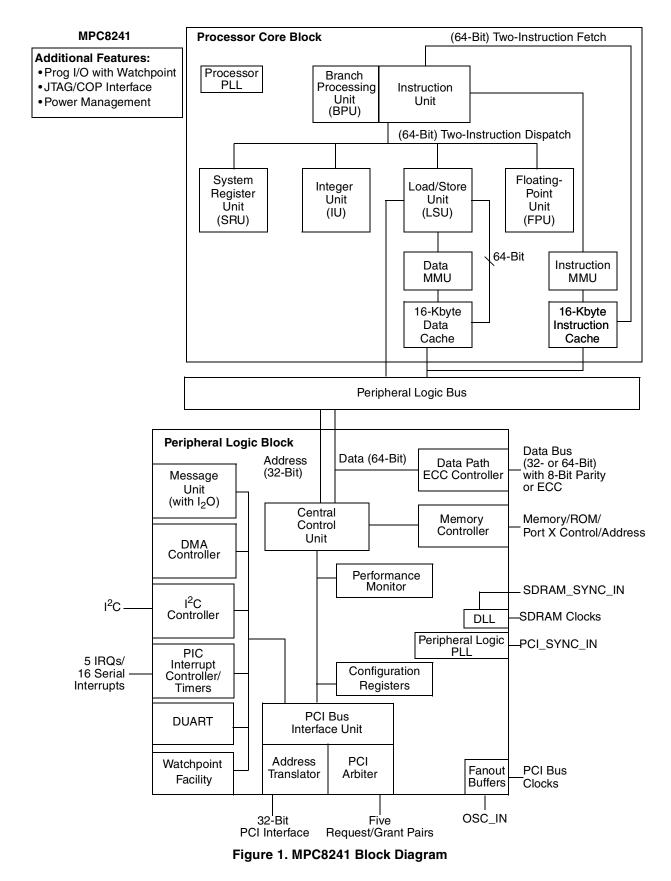

Overview

- I<sup>2</sup>C controller with full master/slave support that accepts broadcast messages

- Programmable interrupt controller (PIC)

- Five hardware interrupts (IRQs) or 16 serial interrupts

- Four programmable timers with cascade

- Two (dual) universal asynchronous receiver/transmitters (UARTs)

- Integrated PCI bus and SDRAM clock generation

- Programmable PCI bus and memory interface output drivers

- System level performance monitor facility

- Debug features

- Memory attribute and PCI attribute signals

- Debug address signals

- $\overline{\text{MIV}}$  signal—marks valid address and data bus cycles on the memory bus

- Programmable input and output signals with watchpoint capability

- Error injection/capture on data path

- IEEE Std. 1149.1 (JTAG)/test interface

### **3 General Parameters**

The following list summarizes the general parameters of the MPC8241:

| Technology        | 0.25 µm CMOS, five-layer metal                                                                |

|-------------------|-----------------------------------------------------------------------------------------------|

| Die size          | 49.2 mm <sup>2</sup>                                                                          |

| Transistor count  | 4.5 million                                                                                   |

| Logic design      | Fully static                                                                                  |

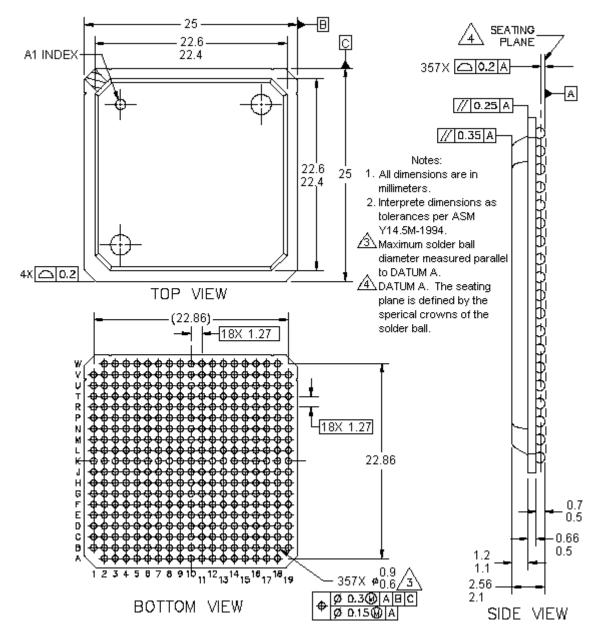

| Packages          | Surface-mount 357 (thick substrate and thick mold cap) plastic ball grid array (PBGA)         |

| Core power supply | 1.8 V $\pm$ 100 mV DC (nominal; see Table 2 for details and recommended operating conditions) |

| I/O power supply  | 3.0 to 3.6 V DC                                                                               |

NP\_\_\_\_

#### **Electrical and Thermal Characteristics**

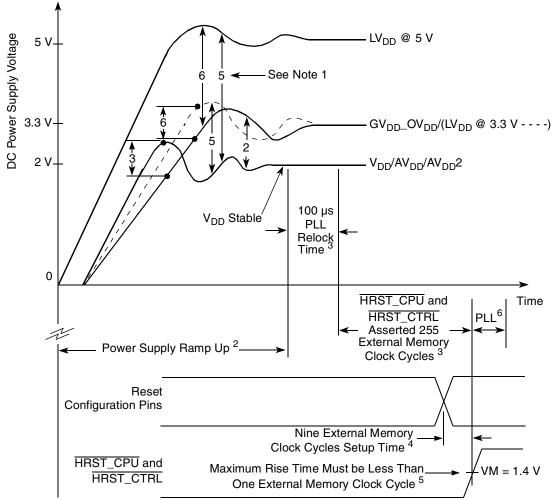

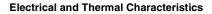

Figure 2 shows supply voltage sequencing and separation cautions.

#### Notes:

- 1. Numbers associated with waveform separations correspond to caution numbers listed in Table 2.

- 2. See the Cautions section of Table 2 for details on this topic.

- 3. Refer to Table 8 for details on PLL relock and reset signal assertion timing requirements.

- 4. Refer to Table 10 for details on reset configuration pin setup timing requirements.

- 5. HRST\_CPU/HRST\_CTRL must transition from a logic 0 to a logic 1 in less than one SDRAM\_SYNC\_IN clock cycle for the device to be in the nonreset state.

- 6. PLL\_CFG signals must be driven on reset and must be held for at least 25 clock cycles after the negation of HRST\_CTRL and HRST\_CPU negate in order to be latched.

#### Figure 2. Supply Voltage Sequencing and Separation Cautions

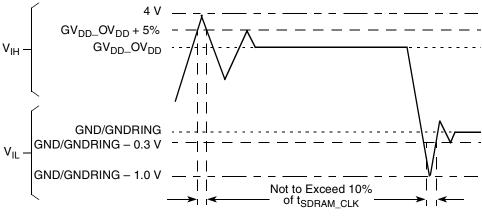

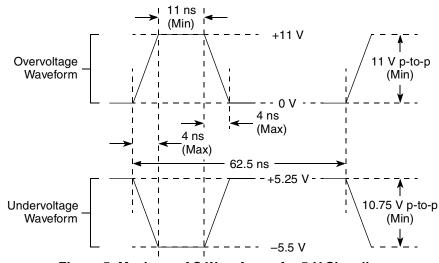

Figure 3 shows the undershoot and overshoot voltage of the memory interface.

Figure 3. Overshoot/Undershoot Voltage

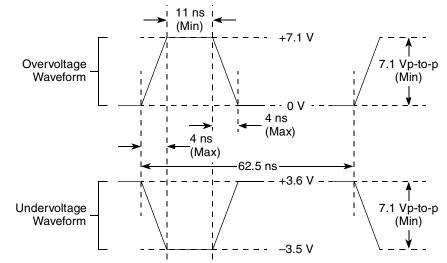

Figure 4 and Figure 5 show the undershoot and overshoot voltage of the PCI interface for the 3.3- and 5-V signals, respectively.

Figure 4. Maximum AC Waveforms for 3.3-V Signaling

#### **Electrical and Thermal Characteristics**

Figure 5. Maximum AC Waveforms for 5-V Signaling

### 4.2 DC Electrical Characteristics

Table 3 provides the DC electrical characteristics for the MPC8241 at recommended operating conditions.

| Characteristics                                                                                       | Conditions                                                                           | Symbol          | Min                                                         | Мах                                                 | Unit | Notes |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------|-----------------------------------------------------|------|-------|

| Input high voltage                                                                                    | PCI only, except<br>PCI_SYNC_IN                                                      | V <sub>IH</sub> | $0.65 \times \text{GV}_{\text{DD}} - \text{OV}_{\text{DD}}$ | LV <sub>DD</sub>                                    | V    | 1     |

| Input low voltage                                                                                     | PCI only, except<br>PCI_SYNC_IN                                                      | V <sub>IL</sub> | —                                                           | $0.3 \times \text{GV}_{\text{DD}}$ $OV_{\text{DD}}$ | V    |       |

| Input high voltage All other pins, including PCI_SYNC_IN (GV <sub>DD</sub> _OV <sub>DD</sub> = 3.3 V) |                                                                                      | V <sub>IH</sub> | 2.0                                                         | 3.3                                                 | V    |       |

| Input low voltage                                                                                     | ut low voltage All inputs, including PCI_SYNC_IN                                     |                 | GND/GNDRING                                                 | 0.8                                                 | V    | 2     |

| Input leakage current for<br>pins using DRV_PCI driver                                                | $0.5 V \le V_{in} \le 2.7 V$<br>@ LV <sub>DD</sub> = 4.75 V                          | ۱ <sub>L</sub>  | —                                                           | ±70                                                 | μA   | 3     |

| Input leakage current all others                                                                      |                                                                                      |                 | —                                                           | ±10                                                 | μA   | 3     |

| Output high voltage                                                                                   | $I_{OH}$ = driver dependent<br>(GV <sub>DD</sub> _OV <sub>DD</sub> = 3.3 V)          | V <sub>OH</sub> | 2.4                                                         | _                                                   | V    | 4     |

| Output low voltage                                                                                    | Output low voltage $I_{OL}$ = driver dependent $(GV_{DD} - OV_{DD} = 3.3 \text{ V})$ |                 | _                                                           | 0.4                                                 | V    | 4     |

**Table 3. DC Electrical Specifications**

# NP

#### Table 8. Clock AC Timing Specifications (continued)

At recommended operating conditions (see Table 2) with LV<sub>DD</sub> = 3.3 V  $\pm$  0.3 V

| Num | Characteristics and Conditions | Min | Мах | Unit | Notes |

|-----|--------------------------------|-----|-----|------|-------|

| 21  | OSC_IN frequency stability     | _   | 100 | ppm  |       |

Notes:

- 1. Rise and fall times for the PCI\_SYNC\_IN input are measured from 0.4 through 2.4 V.

- 2. Specification value at maximum frequency of operation.

- 3. Pin-to-pin skew includes quantifying the additional amount of clock skew (or jitter) from the DLL besides any intentional skew added to the clocking signals from the variable length DLL synchronization feedback loop, that is, the amount of variance between the internal *sys\_logic\_clk* and the SDRAM\_SYNC\_IN signal after the DLL is locked. While pin-to-pin skew between SDRAM\_CLKs can be measured, the relationship between the internal *sys\_logic\_clk* and the external SDRAM\_SYNC\_IN cannot be measured and is guaranteed by design.

- 4. Relock time is guaranteed by design and characterization. Relock time is not tested.

- 5. Relock timing is guaranteed by design. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and PCI\_SYNC\_IN are reached during the reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRST\_CPU/HRST\_CTRL must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the reset sequence.

- 6. DLL\_EXTEND is bit 7 of the PMC2 register <72>. N is a non-zero integer (see Figure 7 through Figure 10). T<sub>clk</sub> is the period of one SDRAM\_SYNC\_OUT clock cycle in ns. T<sub>loop</sub> is the propagation delay of the DLL synchronization feedback loop (PC board runner) from SDRAM\_SYNC\_OUT to SDRAM\_SYNC\_IN in ns; 6.25 inches of loop length (unloaded PC board runner) corresponds to approximately 1 ns of delay. For details about how Figure 7 through Figure 10 may be used, refer to the Freescale application note AN2164, MPC8245/MPC8241 Memory Clock Design Guidelines, for details on MPC8241 memory clock design.

- 7. Rise and fall times for the OSC\_IN input are guaranteed by design and characterization. OSC\_IN input rise and fall times are not tested.

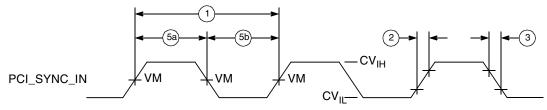

Figure 6 shows the PCI\_SYNC\_IN input clock timing diagram, and Figure 7 through Figure 10 show the DLL locking range loop delay versus frequency of operation.

VM = Midpoint Voltage (1.4 V)

Figure 6. PCI\_SYNC\_IN Input Clock Timing Diagram

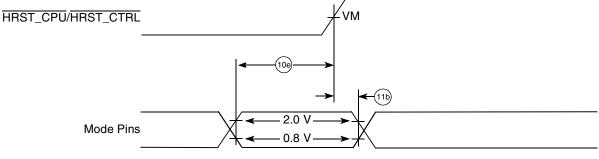

Figure 13 shows the input timing diagram for mode select signals.

VM = Midpoint Voltage (1.4 V)

Figure 13. Input Timing Diagram for Mode Select Signals

### 4.5.3 Output AC Timing Specification

Table 11 provides the processor bus AC timing specifications for the MPC8241 at recommended operating conditions (see Table 2) with  $LV_{DD} = 3.3 V \pm 0.3 V$  (see Figure 11). All output timings assume a purely resistive 50- $\Omega$  load (see Figure 14). Output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias, and connectors in the system. These specifications are for the default driver strengths that Table 4 indicates.

| Num  | Characteristic                                                                   | Min | Мах  | Unit | Notes   |

|------|----------------------------------------------------------------------------------|-----|------|------|---------|

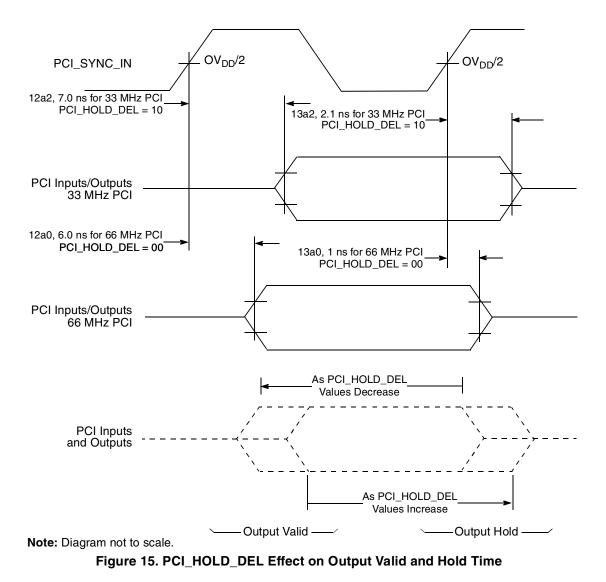

| 12a  | PCI_SYNC_IN to output valid, see Figure 15                                       |     |      | 4    |         |

| 12a0 | Tap 0, PCI_HOLD_DEL = 00, [MCP,CKE] = 11, 66 MHz PCI (default)                   | _   | 6.0  | ns   | 1, 3    |

| 12a1 | Tap 1, PCI_HOLD_DEL = 01, [MCP,CKE] = 10                                         | —   | 6.5  |      |         |

| 12a2 | Tap 2, PCI_HOLD_DEL = 10, [MCP,CKE] = 01, 33 MHz PCI                             | —   | 7.0  |      |         |

| 12a3 | Tap 3, PCI_HOLD_DEL = 11, [MCP,CKE] = 00                                         | —   | 7.5  |      |         |

| 12b  | <i>sys_logic_clk</i> to output valid (memory address, control, and data signals) | —   | 4.5  | ns   | 2       |

| 12c  | <i>sys_logic_clk</i> to output valid (for all others)                            | —   | 7.0  | ns   | 2       |

| 12d  | <i>sys_logic_clk</i> to output valid (for I <sup>2</sup> C)                      | —   | 5.0  | ns   | 2       |

| 12e  | <i>sys_logic_clk</i> to output valid (ROM/Flash/Port X)                          | —   | 6.0  | ns   | 2       |

| 13a  | Output hold (PCI), see Figure 15                                                 |     |      |      |         |

| 13a0 | Tap 0, PCI_HOLD_DEL = 00, [MCP,CKE] = 11, 66 MHz PCI (default)                   | 2.0 |      | ns   | 1, 3, 4 |

| 13a1 | Tap 1, PCI_HOLD_DEL = 01, [MCP,CKE] = 10                                         | 2.5 | _    |      |         |

| 13a2 | Tap 2, PCI_HOLD_DEL = 10, [MCP,CKE] = 01, 33 MHz PCI                             | 3.0 | _    |      |         |

| 13a3 | Tap 3, PCI_HOLD_DEL = 11, [MCP,CKE] = 00                                         | 3.5 |      |      |         |

| 13b  | Output hold (all others)                                                         | 1.0 |      | ns   | 2       |

| 14a  | PCI_SYNC_IN to output high impedance (for PCI)                                   | —   | 14.0 | ns   | 1, 3    |

Table 11. Output AC Timing Specifications

**Electrical and Thermal Characteristics**

### 4.6 $I^2C$

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8241.

### 4.6.1 I<sup>2</sup>C DC Electrical Characteristics

Table 12 provides the DC electrical characteristics for the I<sup>2</sup>C interfaces.

#### Table 12. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  5%.

| Parameter                | Symbol          | Min                 | Мах                                | Unit | Notes |

|--------------------------|-----------------|---------------------|------------------------------------|------|-------|

| Input high voltage level | V <sub>IH</sub> | $0.7 	imes OV_{DD}$ | OV <sub>DD</sub> + 0.3             | V    |       |

| Input low voltage level  | V <sub>IL</sub> | -0.3                | $0.3 	imes OV_{DD}$                | V    |       |

| Low level output voltage | V <sub>OL</sub> | 0                   | $0.2 \times \text{OV}_{\text{DD}}$ | V    | 1     |

#### **Electrical and Thermal Characteristics**

#### Table 12. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  5%.

| Pulse width of spikes which must be suppressed by the input filter                                                           | t <sub>i2KHKL</sub> | 0   | 50 | ns | 2 |

|------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|----|----|---|

| Input current each I/O pin (input voltage is between $0.1 \times \text{OV}_{DD}$ and $0.9 \times \text{OV}_{DD}(\text{max})$ | I <sub>I</sub>      | -10 | 10 | μA | 3 |

| Capacitance for each I/O pin                                                                                                 | Cl                  | _   | 10 | pF |   |

#### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2. Refer to the MPC8245 Integrated Processor Reference Manual for information on the digital filter used.

3. I/O pins obstruct the SDA and SCL lines if the  $OV_{DD}$  is switched off.

### 4.6.2 I<sup>2</sup>C AC Electrical Specifications

Table 13 provides the AC timing parameters for the  $I^2C$  interfaces.

### Table 13. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}\left(min\right)$  and  $V_{IL}\left(max\right)$  levels (see Table 12).

| Parameter                                                                                    | Symbol <sup>1</sup>            | Min                  | Мах              | Unit |

|----------------------------------------------------------------------------------------------|--------------------------------|----------------------|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>               | 0                    | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub> <sup>4</sup> | 1.3                  | _                | μs   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub> 4            | 0.6                  | _                | μs   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> 4          | 0.6                  | _                | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> 4          | 0.6                  | _                | μs   |

| Data setup time                                                                              | t <sub>I2DVKH</sub> 4          | 100                  | —                | ns   |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>i2DXKL</sub>            | 0 <sup>_2</sup>      |                  | μs   |

| Data output delay time:                                                                      | t <sub>I2OVKL</sub>            | —                    | 0.9 <sup>3</sup> |      |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub>            | 0.6                  | _                | μs   |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub>            | 1.3                  | _                | μs   |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>                | $0.1 \times OV_{DD}$ | _                | V    |

Figure 25 shows the top surface, side profile, and pinout of the MPC8241, 357 PBGA ZQ and VR packages.

Figure 25. MPC8241 Package Dimensions and Pinout Assignments (ZQ and VR Packages)

| Signal Name         | Package Pin Number                         | Pin Type     | Power<br>Supply                                                | Output<br>Driver Type | Notes     |

|---------------------|--------------------------------------------|--------------|----------------------------------------------------------------|-----------------------|-----------|

| RCS1                | В9                                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                              | DRV_MEM_CTRL          |           |

| RCS2/TRIG_IN        | P18                                        | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>                              | —                     | 5, 12     |

| RCS3/TRIG_OUT       | N18                                        | Output       | GV <sub>DD</sub> _OV <sub>DD</sub>                             | DRV_STD_MEM           | 5         |

| SDMA[1:0]           | A15 B15                                    | I/O          | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | 1, 10, 11 |

| SDMA[11:2]          | A11 B12 A12 C12 B13 C13 D12<br>A14 C14 B14 | Output       | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | 1         |

| DRDY                | P1                                         | Input        | $GV_{DD}OV_{DD}$                                               | —                     | 12, 13    |

| SDMA12/SRESET       | L3                                         | I/O          | $\text{GV}_{\text{DD}} - \text{OV}_{\text{DD}}$                | DRV_MEM_CTRL          | 5, 12     |

| SDMA13/TBEN         | КЗ                                         | I/O          | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | 5, 12     |

| SDMA14/CHKSTOP_IN   | К2                                         | I/O          | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | 5, 12     |

| SDBA1               | C11                                        | Output       | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_MEM_CTRL          | _         |

| SDBA0               | B11                                        | Output       | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | _         |

| PAR[0:7]            | E19 C19 D5 D6 E16 F17 B2 C1                | I/O          | $\text{GV}_{\text{DD}}$ $\text{OV}_{\text{DD}}$                | DRV_STD_MEM           | 1         |

| SDRAS               | B19                                        | Output       | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | DRV_MEM_CTRL          | 10        |

| SDCAS               | D16                                        | Output       | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | 10        |

| CKE                 | C6                                         | Output       | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | 10, 11    |

| WE                  | B16                                        | Output       | $GV_{DD}OV_{DD}$                                               | DRV_MEM_CTRL          | _         |

| AS                  | A16                                        | Output       | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_MEM_CTRL          | 10, 11    |

|                     | PIC Con                                    | trol Signals |                                                                |                       | -         |

| IRQ0/S_INT          | P4                                         | Input        | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | —                     |           |

| IRQ1/S_CLK          | R2                                         | I/O          | $GV_{DD}OV_{DD}$                                               | DRV_PCI               | _         |

| IRQ2/S_RST          | U19                                        | I/O          | $GV_{DD}OV_{DD}$                                               | DRV_PCI               | _         |

| IRQ3/S_FRAME        | P15                                        | I/O          | $GV_{DD}OV_{DD}$                                               | DRV_PCI               | _         |

| IRQ4/L_INT          | P2                                         | I/O          | $GV_{DD}OV_{DD}$                                               | DRV_PCI               |           |

|                     | l <sup>2</sup> C Con                       | trol Signals |                                                                |                       |           |

| SDA                 | P17                                        | I/O          | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | DRV_STD_MEM           | 8, 12     |

| SCL                 | R19                                        | I/O          | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_STD_MEM           | 8, 12     |

|                     | DUART Co                                   | ontrol Signa | Is                                                             |                       |           |

| SOUT1/PCI_CLK0      | T16                                        | Output       | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_MEM_CTRL          | 5, 14     |

| SIN1/PCI_CLK1       | U16                                        | I/O          | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_MEM_CTRL          | 5, 14, 24 |

| SOUT2/RTS1/PCI_CLK2 | W18                                        | Output       | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_MEM_CTRL          | 5, 14     |

| SIN2/CTS1/PCI_CLK3  | V19                                        | I            | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | DRV_MEM_CTRL          | 5, 14, 24 |

|                     | Clock-C                                    | Out Signals  |                                                                |                       |           |

| PCI_CLK0/SOUT1      | T16                                        | Output       | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | DRV_PCI_CLK           | 5, 14     |

#### Table 16. MPC8241 Pinout Listing (continued)

| Signal Name                                 | Package Pin Number                                                                                                                                                                                                                                                                  | Pin Type                                                | Power<br>Supply                                                | Output<br>Driver Type | Notes     |  |  |  |  |  |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|-----------------------|-----------|--|--|--|--|--|--|--|

| TMS                                         | T18                                                                                                                                                                                                                                                                                 | Input                                                   | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | _                     | 6, 13     |  |  |  |  |  |  |  |

| TRST                                        | R16                                                                                                                                                                                                                                                                                 | Input                                                   | $GV_{DD}OV_{DD}$                                               | —                     | 6, 13     |  |  |  |  |  |  |  |

|                                             | Power and                                                                                                                                                                                                                                                                           | Ground Sign                                             | als                                                            |                       |           |  |  |  |  |  |  |  |

| GNDRING/GND                                 | F07 F08 F09 F10 F11 F12 F13<br>G07 G08 G09 G10 G11 G12 G13<br>H07 H08 H09 H10 H11 H12 H13<br>J07 J08 J09 J10 J11 J12 J13 K07<br>K08 K09 K10 K11 K12 K13 L07<br>L08 L09 L10 L11 L12 L13 M07<br>M08 M09 M10 M11 M12 M13<br>N07 N08 N09 N10 N11 N12 N13<br>P08 P09 P10 P11 P12 P13 R15 | Ground                                                  | _                                                              | _                     | 17        |  |  |  |  |  |  |  |

| LV <sub>DD</sub>                            | R18 U18 T1 U4 T6 W11 T14                                                                                                                                                                                                                                                            | Reference<br>voltage<br>3.3 V,<br>5.0 V                 | LV <sub>DD</sub>                                               | _                     | _         |  |  |  |  |  |  |  |

| GV <sub>DD</sub> _OV <sub>DD</sub> /PWRRING | D09 D10 D11 E06 E07 E08 E09<br>E10 E11 E12 E13 E14 F06 F14<br>G06 G14 H06 H14 J06 J14 K06<br>K14 L06 L14 M06 M14 N06 N14<br>P06 P07 P14 R08 R09 R10 R11<br>R12                                                                                                                      | Power for<br>memory<br>drivers and<br>PCI/Stnd<br>3.3 V | GV <sub>DD</sub> OV <sub>DD</sub>                              | _                     | 18        |  |  |  |  |  |  |  |

| V <sub>DD</sub>                             | F03 H3 L5 N4 P5 V5 U8 W12<br>W16 R13 P19 L19 H19 F19 F15<br>C15 A13 A8 B5 A2                                                                                                                                                                                                        | Power for core 1.8 V                                    | V <sub>DD</sub>                                                | _                     | _         |  |  |  |  |  |  |  |

| No Connect                                  | N5 W2 B1                                                                                                                                                                                                                                                                            | —                                                       | —                                                              | —                     | —         |  |  |  |  |  |  |  |

| AV <sub>DD</sub>                            | M5                                                                                                                                                                                                                                                                                  | Power for<br>PLL (CPU<br>core logic)<br>1.8 V           | AV <sub>DD</sub>                                               | _                     | _         |  |  |  |  |  |  |  |

| AV <sub>DD</sub> 2                          | R14                                                                                                                                                                                                                                                                                 | Power for<br>PLL<br>(peripheral<br>logic)<br>1.8 V      | AV <sub>DD</sub> 2                                             | _                     | _         |  |  |  |  |  |  |  |

|                                             | Debug/Man                                                                                                                                                                                                                                                                           | ufacturing P                                            | ins                                                            |                       | 1         |  |  |  |  |  |  |  |

| DA0/QACK                                    | A3                                                                                                                                                                                                                                                                                  | Output                                                  | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_STD_MEM           | 5, 11, 12 |  |  |  |  |  |  |  |

| DA1/CKO                                     | L1                                                                                                                                                                                                                                                                                  | Output                                                  | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | DRV_STD_MEM           | 5         |  |  |  |  |  |  |  |

| DA2                                         | R5                                                                                                                                                                                                                                                                                  | Output                                                  | $GV_{DD}OV_{DD}$                                               | DRV_PCI               | 19        |  |  |  |  |  |  |  |

| DA3/PCI_CLK4                                | V17                                                                                                                                                                                                                                                                                 | Output                                                  | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_PCI_CLK           | 5         |  |  |  |  |  |  |  |

| DA4/REQ4                                    | W13                                                                                                                                                                                                                                                                                 | I/O                                                     | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | _                     | 5, 6      |  |  |  |  |  |  |  |

| DA5/GNT4                                    | T11                                                                                                                                                                                                                                                                                 | Output                                                  | GV <sub>DD</sub> OV <sub>DD</sub>                              | DRV_PCI               | 2, 4, 5   |  |  |  |  |  |  |  |

#### Table 16. MPC8241 Pinout Listing (continued)

# 6 PLL Configuration

The PLL\_CFG[0:4] are configured by the internal PLLs. For a specific PCI\_SYNC\_IN (PCI bus) frequency, the PLL configuration signals set both the peripheral logic/memory bus PLL (VCO) frequency of operation for the PCI-to-memory frequency multiplying and the MPC603e CPU PLL (VCO) frequency of operation for memory-to-CPU frequency multiplying. The PLL configurations are shown in Table 17 and Table 18.

|                  |                               | 16                                                                     | 66 MHz-Part                                                | 2                              | 2                                                                      | 200-MHz Part <sup>2</sup>                                  |                                |                             | Multipliers                 |  |  |

|------------------|-------------------------------|------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|-----------------------------|-----------------------------|--|--|

| Ref <sup>2</sup> | PLL_CFG<br>[0:4] <sup>1</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>3</sup><br>(MHz) | Peripheral<br>Logic/<br>Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>3</sup><br>(MHz) | Peripheral<br>Logic/<br>Mem Bus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem VCO) | Mem-to-<br>CPU<br>(CPU VCO) |  |  |

| 0                | 00000                         | I                                                                      | Not available                                              |                                | 25-26 <sup>5</sup>                                                     | 75-78                                                      | 188-195                        | 3 (2)                       | 2.5 (2)                     |  |  |

| 2                | 00010                         | 34 <sup>4</sup> –37 <sup>5</sup>                                       | 34–37                                                      | 153–166                        | 34 <sup>4</sup> -44 <sup>5</sup>                                       | 34–44                                                      | 153–200                        | 1 (4)                       | 4.5 (2)                     |  |  |

| 3                | 00011 <sup>6</sup>            | 50 <sup>7</sup> –66 <sup>3</sup>                                       | 50–66                                                      | 100–132                        | 50 <sup>7</sup> –66 <sup>3</sup>                                       | 50–66                                                      | 100–132                        | 1 (Bypass)                  | 2 (4)                       |  |  |

| 4                | 00100                         | 25–41 <sup>5</sup>                                                     | 50–82                                                      | 100–164                        | 25–44 <sup>8,10</sup>                                                  | 50–88                                                      | 100–176                        | 2 (4)                       | 2 (4)                       |  |  |

| 6                | 00110 <sup>9</sup>            |                                                                        | Bypass                                                     |                                |                                                                        | Bypass                                                     |                                | Bypass                      | Bypass                      |  |  |

| 7<br>Rev. B      | 00111 <sup>6</sup>            | 50 <sup>4</sup> –55 <sup>5</sup>                                       | 50–55                                                      | 150–166                        | 50 <sup>4</sup> –66 <sup>3</sup>                                       | 50–66                                                      | 150–198                        | 1 (Bypass)                  | 3 (2)                       |  |  |

| 7<br>Rev. D      | 00111                         |                                                                        | •                                                          |                                | Nota                                                                   | available                                                  |                                | •                           |                             |  |  |

| 8                | 01000                         | 50 <sup>4</sup> –55 <sup>5</sup>                                       | 50–55                                                      | 150–166                        | 50 <sup>4</sup> –66 <sup>3</sup>                                       | 50–66                                                      | 150–198                        | 1 (4)                       | 3 (2)                       |  |  |

| 9                | 01001                         | 38 <sup>4</sup> –41 <sup>5,11</sup>                                    | 76–82                                                      | 152–164                        | 38 <sup>4</sup> –50 <sup>5,12</sup>                                    | 76–100                                                     | 152–200                        | 2 (2)                       | 2 (2)                       |  |  |

| В                | 01011                         | I                                                                      | Not available                                              |                                | 44 <sup>5</sup>                                                        | 66                                                         | 198                            | 2(2)                        | 2.5(2)                      |  |  |

| С                | 01100                         | 30 <sup>4</sup> –33 <sup>5</sup>                                       | 60–66                                                      | 150–165                        | 30 <sup>4</sup> -40 <sup>5</sup>                                       | 60–80                                                      | 150–200                        | 2 (4)                       | 2.5 (2)                     |  |  |

| E                | 01110                         | 25–27 <sup>5</sup>                                                     | 50–54                                                      | 150–162                        | 25–33 <sup>5</sup>                                                     | 60–66                                                      | 150–198                        | 2 (4)                       | 3 (2)                       |  |  |

| 10               | 10000                         | 25–27 <sup>5,11</sup>                                                  | 75–83                                                      | 150–166                        | 25–33 <sup>5,12</sup>                                                  | 75–100                                                     | 150–200                        | 3 (2)                       | 2 (2)                       |  |  |

| 12               | 10010                         | 50 <sup>4</sup> –55 <sup>5,11</sup>                                    | 75–83                                                      | 150–166                        | 50 <sup>4</sup> –66 <sup>3</sup>                                       | 75–99                                                      | 150–198                        | 1.5 (2)                     | 2 (2)                       |  |  |

| 14               | 10100                         |                                                                        | Not available                                              |                                | 25–28 <sup>5</sup>                                                     | 50–56                                                      | 175–196                        | 2 (4)                       | 3.5 (2)                     |  |  |

| 16               | 10110                         |                                                                        |                                                            |                                | 25 <sup>5</sup>                                                        | 50                                                         | 200                            | 2(4)                        | 4(2)                        |  |  |

| 17               | 10111                         |                                                                        |                                                            |                                | 25 <sup>5</sup>                                                        | 100                                                        | 200                            | 4(2)                        | 2(2)                        |  |  |

| 19               | 11001                         | 33 <sup>5,13</sup>                                                     | 66                                                         | 165                            | 33 <sup>13</sup> –40 <sup>5</sup>                                      | 66–80                                                      | 165–200                        | 2(2)                        | 2.5(2)                      |  |  |

| 1A               | 11010                         | 37 <sup>4</sup> –41 <sup>5</sup>                                       | 37–41                                                      | 150–166                        | 37 <sup>4</sup> –50 <sup>5</sup>                                       | 37–50                                                      | 150–200                        | 1 (4)                       | 4 (2)                       |  |  |

| 1B               | 11011                         |                                                                        | Not available                                              | •                              | 33 <sup>5,13</sup>                                                     | 66                                                         | 198                            | 2(2)                        | 3(2)                        |  |  |

| 1C               | 11100                         | ]                                                                      |                                                            |                                | 44 <sup>5,13</sup>                                                     | 66                                                         | 198                            | 1.5(2)                      | 3(2)                        |  |  |

| 1D               | 11101                         | 44 <sup>5,13</sup>                                                     | 66                                                         | 166                            | 44 <sup>13</sup> –53 <sup>5</sup>                                      | 66–80                                                      | 165–200                        | 1.5 (2)                     | 2.5 (2)                     |  |  |

Table 17. PLL Configurations (166- and 200-MHz)

|                  | 166 MHz-Part <sup>2</sup>     |                                                                        |                                                            | 200-MHz Part <sup>2</sup>      |                                                                        |                                                            | Multipliers                    |                             |                             |

|------------------|-------------------------------|------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|-----------------------------|-----------------------------|

| Ref <sup>2</sup> | PLL_CFG<br>[0:4] <sup>1</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>3</sup><br>(MHz) | Peripheral<br>Logic/<br>Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>3</sup><br>(MHz) | Peripheral<br>Logic/<br>Mem Bus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem VCO) | Mem-to-<br>CPU<br>(CPU VCO) |

| 1E               | 11110 <sup>14</sup>           | Not usable                                                             |                                                            | Not usable                     |                                                                        |                                                            | Off                            | Off                         |                             |

| 1F               | 11111 <sup>14</sup>           | Not usable                                                             |                                                            |                                | Not usable                                                             |                                                            |                                | Off                         |                             |

#### Notes:

- 1. PLL\_CFG[0:4] settings not listed are reserved. Bits 7–4 of register offset <0xE2> contain the PLL\_CFG[0:4] setting value. Note the impact of the relevant revisions for mode 7.

- 2. Range values are shown rounded down to the nearest whole number (decimal place accuracy removed) for clarity.

- 3. Limited by maximum PCI input frequency (66 MHz).

- 4. Limited by minimum CPU VCO frequency (300 MHz).

- 5. Limited by maximum CPU operating frequency.

- 6. In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in PLL bypass mode.

- 7. Limited by minimum CPU operating frequency (100 MHz).

- 8. Limited due to maximum memory VCO frequency (352 MHz).

- 9. In dual PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal peripheral logic directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI\_SYNC\_IN:Mem) mode operation. In this mode, the OSC\_IN input signal clocks the internal processor directly in 1:1 (OSC\_IN:CPU) mode operation, and the processor PLL is disabled. The PCI\_SYNC\_IN and OSC\_IN input clocks must be externally synchronized. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in dual PLL bypass mode.

- 10.Limited by maximum CPU VCO frequency (704 MHz).

11.Limited by maximum system memory interface operating frequency (83 MHz @ 166 MHz CPU bus speed).

- 12.Limited by maximum system memory interface operating frequency (100 MHz @ 200 MHz CPU bus speed).

- 13.Limited by minimum memory VCO frequency (132 MHz).

14.In clock off mode, no clocking occurs inside the MPC8241, regardless of the PCI\_SYNC\_IN input.

|                  | PLL_<br>CFG[0:4] <sup>10,11</sup> | 266-MHz Part <sup>9</sup>                                       |                                                  |                             | Multipliers             |                         |  |

|------------------|-----------------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------|-------------------------|--|

| Ref <sup>2</sup> |                                   | PCI Clock Input<br>(PCI_SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph Logic/<br>Mem Bus<br>Clock Range<br>(MHz) | CPU Clock<br>Range<br>(MHz) | PCI-to-Mem<br>(Mem VCO) | Mem-to-CPU<br>(CPU VCO) |  |

| 0                | 00000                             | 25–35 <sup>5</sup>                                              | 75–105                                           | 188–263                     | 3 (2)                   | 2.5 (2)                 |  |

| 1                | 00001                             | 25–29 <sup>5</sup>                                              | 75–88                                            | 225–264                     | 3 (2)                   | 3 (2)                   |  |

| 2                | 00010                             | 50 <sup>15</sup> –59 <sup>5</sup>                               | 50–59                                            | 225–266                     | 1 (4)                   | 4.5 (2)                 |  |

| 3                | 00011 <sup>12</sup>               | 50 <sup>14</sup> –66 <sup>1</sup>                               | 50–66                                            | 100–133                     | 1 (Bypass)              | 2 (4)                   |  |

| 4                | 00100                             | 25–44 <sup>4</sup>                                              | 50–88                                            | 100–176                     | 2 (4)                   | 2 (4)                   |  |

Table 18. PLL Configurations (266-MHz Parts)

|                  | PLL_<br>CFG[0:4] <sup>10,11</sup> | :                                                               | 266-MHz Part <sup>9</sup>                        | Multipliers                 |                         |                         |

|------------------|-----------------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------|-------------------------|

| Ref <sup>2</sup> |                                   | PCI Clock Input<br>(PCI_SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph Logic/<br>Mem Bus<br>Clock Range<br>(MHz) | CPU Clock<br>Range<br>(MHz) | PCI-to-Mem<br>(Mem VCO) | Mem-to-CPU<br>(CPU VCO) |

| 6                | 00110 <sup>13</sup>               | Bypass                                                          |                                                  |                             | Bypass                  |                         |

| 7 (Rev. B)       | 00111 <sup>12</sup>               | 50 <sup>6</sup> –66 <sup>1</sup>                                | 50–66                                            | 150–198                     | 1 (Bypass)              | 3 (2)                   |

| 7 (Rev. D)       | 00111 <sup>14</sup>               |                                                                 | ,<br>,                                           | Not Available               |                         |                         |

| 8                | 01000                             | 50 <sup>6</sup> –66 <sup>1</sup>                                | 50–66                                            | 150–198                     | 1 (4)                   | 3 (2)                   |

| 9                | 01001                             | 38 <sup>6</sup> –66 <sup>1</sup>                                | 76–132                                           | 152–264                     | 2 (2)                   | 2 (2)                   |

| А                | 01010                             | 25–29 <sup>5</sup>                                              | 50–58                                            | 225–261                     | 2 (4)                   | 4.5 (2)                 |

| В                | 01011                             | 45 <sup>3</sup> –59 <sup>5</sup>                                | 68–88                                            | 204–264                     | 1.5 (2)                 | 3 (2)                   |

| С                | 01100                             | 30 <sup>6</sup> –44 <sup>4</sup>                                | 60–88                                            | 150–220                     | 2 (4)                   | 2.5 (2)                 |

| D                | 01101                             | 45 <sup>3</sup> –50 <sup>5</sup>                                | 68–75                                            | 238–263                     | 1.5 (2)                 | 3.5 (2)                 |

| Е                | 01110                             | 25–44 <sup>5</sup>                                              | 50–88                                            | 150–264                     | 2 (4)                   | 3 (2)                   |

| F                | 01111                             | 25 <sup>5</sup>                                                 | 75                                               | 263                         | 3 (2)                   | 3.5 (2)                 |

| 10               | 10000                             | 25–44 <sup>5</sup>                                              | 75–132                                           | 150–264                     | 3 (2)                   | 2 (2)                   |

| 11               | 10001                             | 25–26 <sup>5</sup>                                              | 100–106                                          | 250–266                     | 4 (2)                   | 2.5 (2)                 |

| 12               | 10010                             | 50 <sup>6</sup> –66 <sup>1</sup>                                | 75–99                                            | 150–198                     | 1.5 (2)                 | 2 (2)                   |

| 13               | 10011                             |                                                                 | Not available                                    |                             | 4 (2)                   | 3 (2)                   |

| 14               | 10100                             | 25–38 <sup>5</sup>                                              | 50–76                                            | 175–266                     | 2 (4)                   | 3.5 (2)                 |

| 15               | 10101                             |                                                                 | Not available                                    |                             | 2.5 (2)                 | 4 (2)                   |

| 16               | 10110                             | 25–33 <sup>5</sup>                                              | 50–66                                            | 200–264                     | 2 (4)                   | 4 (2)                   |

| 17               | 10111                             | 25–33 <sup>5</sup>                                              | 100–132                                          | 200–264                     | 4 (2)                   | 2 (2)                   |

| 18               | 11000                             | 27 <sup>3</sup> –35 <sup>5</sup>                                | 68–88                                            | 204–264                     | 2.5 (2)                 | 3 (2)                   |

| 19               | 11001                             | 33 <sup>3</sup> –53 <sup>5</sup>                                | 66–106                                           | 165–265                     | 2 (2)                   | 2.5 (2)                 |

| 1A               | 11010                             | 50 <sup>18</sup> –66 <sup>1</sup>                               | 50–66                                            | 200–264                     | 1 (4)                   | 4 (2)                   |

| 1B               | 11011                             | 34 <sup>3</sup> –44 <sup>5</sup>                                | 68–88                                            | 204–264                     | 2 (2)                   | 3 (2)                   |

| 1C               | 11100                             | 44 <sup>3</sup> –59 <sup>5</sup>                                | 66–88                                            | 198–264                     | 1.5 (2)                 | 3 (2)                   |

| 1D               | 11101                             | 44 <sup>3</sup> –66 <sup>1</sup>                                | 66–99                                            | 165–248                     | 1.5 (2)                 | 2.5 (2)                 |

| 1E (Rev. B)      | 11110 <sup>8</sup>                |                                                                 | Not usable                                       |                             | Off                     | Off                     |

| 1E (Rev. D)      | 11110                             | 33 <sup>3</sup> -38 <sup>5</sup>                                | 66-76                                            | 231-266                     | 2(2)                    | 3.5(2)                  |

| Table 18. PLL Configurations | (266-MHz Parts) (continued) |

|------------------------------|-----------------------------|

|------------------------------|-----------------------------|

|                  | 266-MHz Part <sup>9</sup>         |                                                                 |                                                  | Multipliers                 |                         |                         |

|------------------|-----------------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------|-------------------------|

| Ref <sup>2</sup> | PLL_<br>CFG[0:4] <sup>10,11</sup> | PCI Clock Input<br>(PCI_SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph Logic/<br>Mem Bus<br>Clock Range<br>(MHz) | CPU Clock<br>Range<br>(MHz) | PCI-to-Mem<br>(Mem VCO) | Mem-to-CPU<br>(CPU VCO) |

| 1F               | 11111 <sup>8</sup>                | Not usable                                                      |                                                  | Off                         | Off                     |                         |

Table 18. PLL Configurations (266-MHz Parts) (continued)

#### Notes:

- 1. Limited by maximum PCI input frequency (66 MHz).

- 2. Note the impact of the relevant revisions for modes 7 and 1E.

- 3. Limited by minimum memory VCO frequency (132 MHz).

- 4. Limited due to maximum memory VCO frequency (352 MHz).

- 5. Limited by maximum CPU operating frequency.

- 6. Limited by minimum CPU VCO frequency (300 MHz).

- 7. Limited by maximum CPU VCO frequency (704 MHz).

- 8. In clock off mode, no clocking occurs inside the MPC8241, regardless of the PCI\_SYNC\_IN input.

- 9. Range values are shown rounded down to the nearest whole number (decimal place accuracy removed) for clarity.

- 10.PLL\_CFG[0:4] settings that are not listed are reserved.

- 11.Bits 7-4 of register offset <0xE2> contain the PLL\_CFG[0:4] setting value.

- 12.In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in PLL bypass mode.

- 13.In dual PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal peripheral logic directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI\_SYNC\_IN:Mem) mode operation. In this mode, the OSC\_IN input signal clocks the internal processor directly in 1:1 (OSC\_IN:CPU) mode operation and the processor PLL is disabled. The PCI\_SYNC\_IN and OSC\_IN input clocks must be externally synchronized. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in dual PLL bypass mode.

- 14.Limited by minimum CPU operating frequency (100 MHz).

- 15.Limited by minimum memory bus frequency (50 MHz).

# 7 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8241.

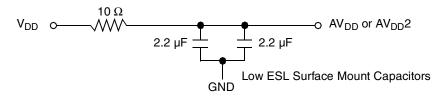

### 7.1 PLL Power Supply Filtering

The AV<sub>DD</sub> and AV<sub>DD</sub>2 power signals on the MPC8241 provide power to the peripheral logic/memory bus PLL and the MPC603e processor PLL. To ensure stability of the internal clocks, the power supplied to the AV<sub>DD</sub> and AV<sub>DD</sub>2 input signals should be filtered of any noise in the 500 kHz to 10 MHz resonant frequency range of the PLLs. Two separate circuits similar to the one shown in Figure 26 using surface mount capacitors with minimum effective series inductance (ESL) is recommended for AV<sub>DD</sub> and AV<sub>DD</sub>2 power signal pins. In *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), Dr. Howard Johnson recommends using multiple small capacitors of equal value instead of multiple values.

Place the circuits as closely as possible to the respective input signal pins to minimize noise coupled from nearby circuits. Routing from the capacitors to the input signal pins should be as direct as possible with minimal inductance of vias.

Figure 26. PLL Power Supply Filter Circuit

### 7.2 Decoupling Recommendations

Dynamic power management, large address and data buses, and high operating frequencies enable the MPC8241 to generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8241 system, and the MPC8241 itself requires a clean, tightly regulated source of power. Therefore, place at least one decoupling capacitor at each  $V_{DD}$ ,  $GV_{DD}$ – $OV_{DD}$ , and  $LV_{DD}$  pin. These decoupling capacitors receive their power from dedicated power planes in the PCB, using short traces to minimize inductance. These capacitors should have a value of 0.1 µF. To minimize lead inductance, use only ceramic SMT (surface mount technology) capacitors, preferably 0508 or 0603, on which connections are made along the length of the part.

In addition, distribute several bulk storage capacitors around the PCB to feed the  $V_{DD}$ ,  $GV_{DD}$ – $OV_{DD}$ , and  $LV_{DD}$  planes and enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the necessary quick response time, and should be connected to the power and ground planes through two vias to minimize inductance. Freescale recommends using bulk capacitors: 100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

### 7.3 Connection Recommendations

To ensure reliable operation, connect unused inputs to an appropriate signal level. Tie unused active-low inputs to  $OV_{DD}$ . Connect unused active-high inputs to GND. All no connect (NC) signals must remain unconnected.

Power and ground connections must be made to all external V<sub>DD</sub>, GV<sub>DD</sub>, GV<sub>DD</sub>, LV<sub>DD</sub>, and GND pins.

The PCI\_SYNC\_OUT signal is to be routed halfway out to the PCI devices and then returned to the PCI\_SYNC\_IN input.

The SDRAM\_SYNC\_OUT signal is to be routed halfway out to the SDRAM devices and then returned to the SDRAM\_SYNC\_IN input of the MPC8241. The trace length can be used to skew or adjust the timing window as needed. See the Tundra *Tsi107<sup>TM</sup> Design Guide* (AN1849) and Freescale application notes AN2164/D, *MPC8245/MPC8241 Memory Clock Design Guidelines: Part 1* and AN2746, *MPC8245/MPC8241 Memory Clock Design Guidelines: Part 2* for more details. Note the SDRAM\_SYNC\_IN to PCI\_SYNC\_IN time requirement (see Table 10).

System Design Information

Shin-Etsu MicroSi, Inc.888-642-767410028 S. 51st St.888-642-7674Phoenix, AZ 850441Internet: www.microsi.com888-246-9050Thermagon Inc.888-246-90504707 Detroit Ave.2Cleveland, OH 441021Internet: www.thermagon.com1

### 7.7.3 Heat Sink Usage

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_A$  = ambient temperature for the package (°C)  $R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Unfortunately, two values are in common usage: the value determined on a single-layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single-layer board is appropriate for the tightly packed printed-circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)  $R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)  $R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device-related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the airflow around the device, the interface material, the mounting arrangement on the printed-circuit board, or the thermal dissipation on the printed-circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the thermal characterization parameter ( $\psi_{JT}$ ) measures the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\psi_{JT} \times P_D)$$

**Ordering Information**

where:

$T_T$  = thermocouple temperature atop the package (°C)  $\psi_{JT}$  = thermal characterization parameter (°C/W)  $P_D$  = power dissipation in package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

When a heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance minimizes the change in thermal performance that is caused by removing part of the thermal interface to the heat sink. Considering the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

In many cases, it is appropriate to simulate the system environment using a computational fluid dynamics thermal simulation tool. In such a tool, the simplest thermal model of a package that has demonstrated reasonable accuracy (about 20%) is a two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case covers the situation where a heat sink is used or a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed-circuit board.

### 7.8 References

Semiconductor Equipment and Materials International 805 East Middlefield Rd. Mountain View, CA 94043 (415) 964-5111

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the web at http://www.jedec.org.

# 8 Ordering Information

Ordering information for the parts that this document fully covers is provided in Section 8.1, "Part Numbers Fully Addressed by This Document." Section 8.2, "Part Numbers Not Fully Addressed by This Document," lists the part numbers which do not fully conform to the specifications of this document. These special part numbers require an additional document called a hardware specifications addendum.

**Document Revision History**

#### Table 20. Part Numbers Addressed by MPC8241TXXPNS Series (Document No. MPC8241ECS01AD))

| MPC | nnnn | т                                                  | XX                                                              | nnn                             | X                       |            |

|-----|------|----------------------------------------------------|-----------------------------------------------------------------|---------------------------------|-------------------------|------------|

| MPC | 8241 | T = Extended<br>temperature spec.<br>-40° to 105°C | ZQ = thick substrate and<br>thick mold cap PBGA (two<br>layers) | 166, 200<br>@ 1.8 V<br>± 100 mV | D:1.4 =<br>Rev. ID:0x14 | 0x80811014 |

Notes:

1. See Section 5, "Package Description," for more information on available package types.

2. Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by hardware specifications addendums may support other maximum core frequencies.

### 8.3 Part Marking

Parts are marked as the example shown in Figure 32.

#### Notes:

MMMMM is the 5-digit mask number. ATWLYYWW is traceability code. CCCCC is the country code.

#### Figure 32. Part Marking for MPC8241 Device

## 9 Document Revision History

Table 21 provides a revision history for this hardware specification.

#### Table 21. Revision History Table

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                             |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10       | 02/2009 | In Table 16, "MPC8241 Pinout Listing," added footnote 10 to PMAA[2].<br>In Table 16, "MPC8241 Pinout Listing," removed footnote 12 for second listing of RCS3/TRIG_OUT.                                                                           |

| 9        | 09/2007 | Completely replaced Section 4.6 with compliant I <sup>2</sup> C specifications as with other related integrated processor devices.<br>Section 7.6, "JTAG Configuration Signals" Reworded paragraph beginning "The arrangement shown in Figure 27" |