Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Core Processor                  | PowerPC 603e                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 166MHz                                                      |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | SDRAM                                                       |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | -                                                           |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | -                                                           |

| Package / Case                  | 357-BBGA                                                    |

| Supplier Device Package         | 357-PBGA (25x25)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8241lvr166d |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

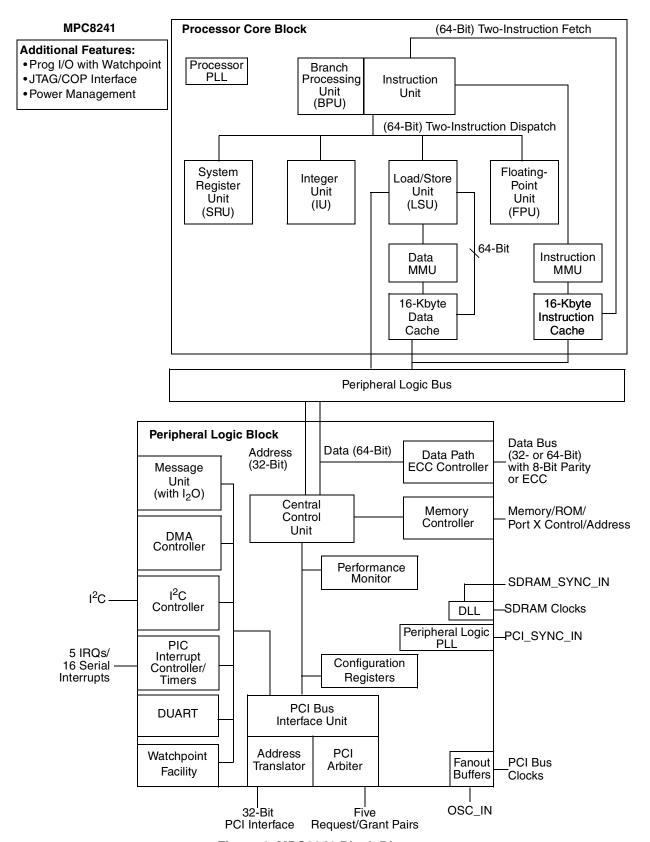

Figure 1. MPC8241 Block Diagram

MPC8241 Integrated Processor Hardware Specifications, Rev. 10

- I<sup>2</sup>C controller with full master/slave support that accepts broadcast messages

- Programmable interrupt controller (PIC)

- Five hardware interrupts (IRQs) or 16 serial interrupts

- Four programmable timers with cascade

- Two (dual) universal asynchronous receiver/transmitters (UARTs)

- Integrated PCI bus and SDRAM clock generation

- Programmable PCI bus and memory interface output drivers

- System level performance monitor facility

- Debug features

- Memory attribute and PCI attribute signals

- Debug address signals

- MIV signal—marks valid address and data bus cycles on the memory bus

- Programmable input and output signals with watchpoint capability

- Error injection/capture on data path

- IEEE Std. 1149.1 (JTAG)/test interface

# 3 General Parameters

The following list summarizes the general parameters of the MPC8241:

Technology 0.25 µm CMOS, five-layer metal

Die size 49.2 mm<sup>2</sup>

Transistor count 4.5 million

Logic design Fully static

Packages Surface-mount 357 (thick substrate and thick mold cap)

plastic ball grid array (PBGA)

Core power supply  $1.8 \text{ V} \pm 100 \text{ mV DC (nominal; see Table 2 for details}$

and recommended operating conditions)

I/O power supply 3.0 to 3.6 V DC

# 4 Electrical and Thermal Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8241.

## 4.1 DC Electrical Characteristics

This section covers ratings, conditions, and other characteristics.

# 4.1.1 Absolute Maximum Ratings

This section describes the MPC8241 DC electrical characteristics. Table 1 provides the absolute maximum ratings.

**Table 1. Absolute Maximum Ratings**

| Characteristic <sup>1</sup>                                     | Symbol                               | Range       | Unit |

|-----------------------------------------------------------------|--------------------------------------|-------------|------|

| Supply voltage—CPU core and peripheral logic                    | V <sub>DD</sub>                      | -0.3 to 2.1 | V    |

| Supply voltage—memory bus drivers, PCI and standard I/O buffers | GV <sub>DD</sub> OV <sub>DD</sub>    | -0.3 to 3.6 | V    |

| Supply voltage—PLLs                                             | AV <sub>DD</sub> /AV <sub>DD</sub> 2 | -0.3 to 2.1 | V    |

| Supply voltage—PCI reference                                    | LV <sub>DD</sub>                     | -0.3 to 5.4 | V    |

| Input voltage <sup>2</sup>                                      | V <sub>in</sub>                      | -0.3 to 3.6 | V    |

| Operational die-junction temperature range                      | Tj                                   | 0 to 105    | •C   |

| Storage temperature range                                       | T <sub>stg</sub>                     | -55 to 150  | •C   |

### Notes:

2. PCI inputs with LV<sub>DD</sub> = 5 V  $\pm$  5% V DC may be correspondingly stressed at voltages exceeding LV<sub>DD</sub> + 0.5 V DC.

<sup>1.</sup> Table 2 provides functional and tested operating conditions. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

# 4.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for the MPC8241.

Table 2. Recommended Operating Conditions <sup>1</sup>

| Charac                                                                         | teristic         | Symbol                            | Recommended<br>Value | Unit | Notes   |

|--------------------------------------------------------------------------------|------------------|-----------------------------------|----------------------|------|---------|

| Supply voltage                                                                 |                  | V <sub>DD</sub>                   | 1.8 ± 100 mV         | V    | 2       |

| I/O buffer supply for PCI and standard; supply voltages for memory bus drivers |                  | GV <sub>DD</sub> OV <sub>DD</sub> | $3.3\pm0.3$          | V    | 2       |

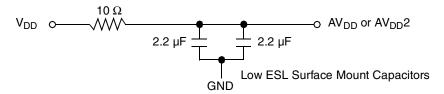

| CPU PLL supply voltage                                                         |                  | AV <sub>DD</sub>                  | 1.8 ± 100 mV         |      | 2       |

| PLL supply voltage—peripheral logic                                            |                  | AV <sub>DD</sub> 2                | 1.8 ± 100 mV         | V    | 2       |

| PCI reference                                                                  | PCI reference    |                                   | 5.0 ± 5%             | V    | 4, 5, 6 |

|                                                                                |                  |                                   | $3.3 \pm 0.3$        | V    | 5, 6, 7 |

| Input voltage                                                                  | PCI inputs       | V <sub>in</sub>                   | 0 to 3.6 or 5.75     | V    | 4, 7    |

|                                                                                | All other inputs |                                   | 0 to 3.6             | V    | 8       |

| Die-junction temperature                                                       |                  | T <sub>j</sub>                    | 0 to 105             | •C   |         |

#### Notes:

- 1. Freescale has tested these operating conditions and recommends them. Proper device operation outside of these conditions is not guaranteed.

- 2. Caution: GV<sub>DD</sub>\_OV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 by more than 1.8 V at any time including during power-on reset. Note that GV<sub>DD</sub>\_OV<sub>DD</sub> pins are all shorted together: This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences. Connections should not be made to individual PWRRING pins.

- 3. **Caution:** V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 must not exceed GV<sub>DD</sub>OV<sub>DD</sub> by more than 0.6 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. PCI pins are designed to withstand LV<sub>DD</sub> + 0.5 V DC when LV<sub>DD</sub> is connected to a 5.0 V DC power supply.

- 5. **Caution:** LV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 by more than 5.4 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 6. **Caution:** LV<sub>DD</sub> must not exceed GV<sub>DD</sub>OV<sub>DD</sub> by more than 3.0 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 7. PCI pins are designed to withstand LV<sub>DD</sub> + 0.5 V DC when LV<sub>DD</sub> is connected to a 3.3 V DC power supply.

- 8. Caution: Input voltage (V<sub>in</sub>) must not be greater than the supply voltage (V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2) by more than 2.5 V at all times including during power-on reset. Input voltage (V<sub>in</sub>) must not be greater than GV<sub>DD</sub>OV<sub>DD</sub> by more than 0.6 V at all times including during power-on reset.

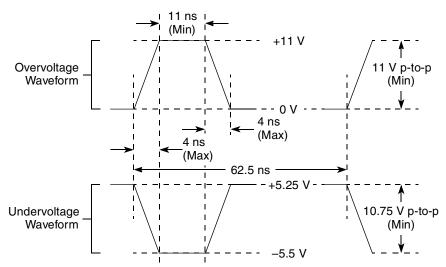

Figure 5. Maximum AC Waveforms for 5-V Signaling

# 4.2 DC Electrical Characteristics

Table 3 provides the DC electrical characteristics for the MPC8241 at recommended operating conditions.

**Table 3. DC Electrical Specifications**

| Characteristics                                     | Conditions                                                                                               | Symbol          | Min                                                         | Max                                                             | Unit | Notes |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------|-----------------------------------------------------------------|------|-------|

| Input high voltage                                  | PCI only, except<br>PCI_SYNC_IN                                                                          | V <sub>IH</sub> | $0.65 \times \text{GV}_{\text{DD}} - \text{OV}_{\text{DD}}$ | LV <sub>DD</sub>                                                | V    | 1     |

| Input low voltage                                   | PCI only, except<br>PCI_SYNC_IN                                                                          | V <sub>IL</sub> | _                                                           | $0.3 \times \text{GV}_{\text{DD}}\text{-}\text{OV}_{\text{DD}}$ | V    |       |

| Input high voltage                                  | All other pins, including PCI_SYNC_IN (GV <sub>DD</sub> _OV <sub>DD</sub> = 3.3 V)                       | V <sub>IH</sub> | 2.0                                                         | 3.3                                                             | V    |       |

| Input low voltage                                   | All inputs, including PCI_SYNC_IN                                                                        | V <sub>IL</sub> | GND/GNDRING                                                 | 0.8                                                             | V    | 2     |

| Input leakage current for pins using DRV_PCI driver | $0.5 \text{ V} \le \text{V}_{\text{in}} \le 2.7 \text{ V}$<br>@ $\text{LV}_{\text{DD}} = 4.75 \text{ V}$ | ΙL              | _                                                           | ±70                                                             | μΑ   | 3     |

| Input leakage current all others                    | $LV_{DD} = 3.6 \text{ V}$<br>$GV_{DD} = 3.6 \text{ V}$<br>$GV_{DD} = 3.465 \text{ V}$                    | Ι <sub>L</sub>  | _                                                           | ±10                                                             | μΑ   | 3     |

| Output high voltage                                 | I <sub>OH</sub> = driver dependent<br>(GV <sub>DD</sub> _OV <sub>DD</sub> = 3.3 V)                       | V <sub>OH</sub> | 2.4                                                         | _                                                               | V    | 4     |

| Output low voltage                                  | I <sub>OL</sub> = driver dependent<br>(GV <sub>DD</sub> _OV <sub>DD</sub> = 3.3 V)                       | V <sub>OL</sub> | _                                                           | 0.4                                                             | V    | 4     |

| Table 3. DC Electrical Specifications (continued | Table 3. | DC Electrical | Specifications | (continued |

|--------------------------------------------------|----------|---------------|----------------|------------|

|--------------------------------------------------|----------|---------------|----------------|------------|

| Characteristics | Conditions                | Symbol          | Min | Мах  | Unit | Notes |

|-----------------|---------------------------|-----------------|-----|------|------|-------|

| Capacitance     | $V_{in} = 0 V, f = 1 MHz$ | C <sub>in</sub> |     | 16.0 | pF   |       |

#### Notes:

- 1. See Table 16 for pins with internal pull-up resistors.

- 2. All grounded pins are connected together.

- 3. Leakage current is measured on input and output pins in the high-impedance state. The leakage current is measured for nominal  $GV_{DD}$ - $OV_{DD}$ / $LV_{DD}$  and  $V_{DD}$  or both  $GV_{DD}$ - $OV_{DD}$ / $LV_{DD}$  and  $V_{DD}$  must vary in the same direction.

- 4. See Table 4 for the typical drive capability of a specific signal pin based on the type of output driver associated with that pin as listed in Table 16.

# 4.2.1 Output Driver Characteristics

Table 4 provides information on the characteristics of the output drivers referenced in Table 16. The values are preliminary estimates from an IBIS model and are not tested.

Table 4. Drive Capability of MPC8241 Output Pins 5,6

| Driver Type                | Programmable Output Impedance (Ω) | Supply Voltage                             | Іон  | l <sub>OL</sub> | Unit | Notes |

|----------------------------|-----------------------------------|--------------------------------------------|------|-----------------|------|-------|

| DRV_STD_MEM                | 20 (default)                      | GV <sub>DD</sub> _OV <sub>DD</sub> = 3.3 V | 36.6 | 18.0            | mA   | 2, 4  |

|                            | 40                                |                                            | 18.6 | 9.2             | mA   | 2, 4  |

| DRV_PCI                    | 20                                |                                            | 12.0 | 12.4            | mA   | 1, 3  |

|                            | 40 (default)                      |                                            | 6.1  | 6.3             | mA   | 1, 3  |

| DRV_MEM_CTRL               |                                   | 89.0                                       | 42.3 | mA              | 2, 4 |       |

| DRV_PCI_CLK<br>DRV_MEM_CLK | 20                                |                                            | 36.6 | 18.0            | mA   | 2, 4  |

|                            | 40                                |                                            | 18.6 | 9.2             | mA   | 2, 4  |

#### Notes:

- 1. For DRV\_PCI,  $I_{OH}$  read from the IBIS listing in the pull-up mode, I(Min) column, at the 0.33-V label by interpolating between the 0.3- and 0.4-V table entries current values which corresponds to the PCI  $V_{OH}$  = 2.97 = 0.9 ×  $GV_{DD}$ \_ $OV_{DD}$  ( $GV_{DD}$ \_ $OV_{DD}$  = 3.3 V) where table entry voltage =  $GV_{DD}$ \_ $OV_{DD}$  PCI  $V_{OH}$ .

- 2. For all others with  $GV_{DD}$  OV $_{DD}$  = 3.3 V,  $I_{OH}$  read from the IBIS listing in the pull-up mode, I(Min) column, at the 0.9-V table entry which corresponds to the  $V_{OH}$  = 2.4 V where table entry voltage =  $GV_{DD}$  OV $_{DD}$   $V_{OH}$ .

- 3. For DRV\_PCI,  $I_{OL}$  read from the IBIS listing in the pull-down mode, I(Min) column, at 0.33 V = PCI  $V_{OL}$  = 0.1 ×  $GV_{DD}$ \_OV<sub>DD</sub> ( $GV_{DD}$ \_OV<sub>DD</sub> = 3.3 V) by interpolating between the 0.3- and 0.4-V table entries.

- 4. For all others with GV<sub>DD</sub>\_OV<sub>DD</sub> = 3.3 V, I<sub>OL</sub> read from the IBIS listing in the pull-down mode, I(Min) column, at the 0.4-V table entry.

- 5. See driver bit details for output driver control register (0x73) in the MPC8245 Integrated Processor Reference Manual.

- 6. See Chip Errata No. 19 in the MPC8245/MPC8241 Integrated Processor Chip Errata.

Table 7 provides the operating frequency information for the MPC8241 at recommended operating conditions (see Table 2) with  $LV_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}$ .

**Table 7. Operating Frequency**

|                           | 166 MHz                                            |     | 200 MHz |     | 266 MHz |     |      |

|---------------------------|----------------------------------------------------|-----|---------|-----|---------|-----|------|

| Characteristic            | $V_{DD}/AV_{DD}/AV_{DD}2 = 1.8 \pm 100 \text{ mV}$ |     |         |     |         |     | Unit |

|                           | Min                                                | Max | Min     | Max | Min     | Max |      |

| Processor frequency (CPU) | 100                                                | 166 | 100     | 200 | 100     | 266 | MHz  |

| Memory bus frequency      | 33                                                 | 83  | 33      | 100 | 33      | 133 | MHz  |

| PCI input frequency       |                                                    |     | 25-     | -66 |         |     | MHz  |

Caution: The PCI\_SYNC\_IN frequency and PLL\_CFG[0:4] settings must be chosen such that the resulting peripheral logic/memory bus frequency and CPU (core) frequencies do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:4] signal description in Section 6, "PLL Configuration," for valid PLL\_CFG[0:4] settings and PCI\_SYNC\_IN frequencies.

# 4.5.1 Clock AC Specifications

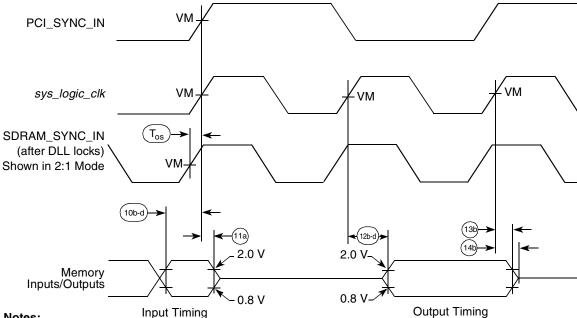

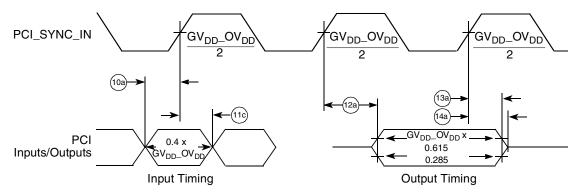

Table 8 provides the clock AC timing specifications at recommended operating conditions, as defined in Section 4.5.2, "Input AC Timing Specifications." These specifications are for the default driver strengths indicated in Table 4. Figure 6 shows the PCI\_SYNC\_IN input clock timing diagram with the labeled number items listed in Table 8.

**Table 8. Clock AC Timing Specifications**

At recommended operating conditions (see Table 2) with  $LV_{DD}$  = 3.3 V  $\pm$  0.3 V

| Num  | Characteristics and Conditions                                                         | Min                            | Max | Unit | Notes   |

|------|----------------------------------------------------------------------------------------|--------------------------------|-----|------|---------|

| 1    | Frequency of operation (PCI_SYNC_IN)                                                   | 25                             | 66  | MHz  |         |

| 2, 3 | PCI_SYNC_IN rise and fall times                                                        | _                              | 2.0 | ns   | 1       |

| 4    | PCI_SYNC_IN duty cycle measured at 1.4 V                                               | 40                             | 60  | %    |         |

| 5a   | PCI_SYNC_IN pulse width high measured at 1.4 V                                         | 6                              | 9   | ns   | 2       |

| 5b   | PCI_SYNC_IN pulse width low measured at 1.4 V                                          | 6                              | 9   | ns   | 2       |

| 7    | PCI_SYNC_IN jitter                                                                     | — 200                          |     | ps   |         |

| 8a   | PCI_CLK[0:4] skew (pin-to-pin)                                                         | _                              | 250 | ps   |         |

| 8b   | SDRAM_CLK[0:3] skew (pin-to-pin)                                                       | _                              | 190 | ps   | 3       |

| 10   | Internal PLL relock time                                                               | _                              | 100 | μs   | 2, 4, 5 |

| 15   | DLL lock range with DLL_EXTEND = 0 (disabled) and normal tap delay; (default DLL mode) | See Figure 7                   |     | ns   | 6       |

| 16   | DLL lock range for other modes                                                         | See Figure 8 through Figure 10 |     | ns   | 6       |

| 17   | Frequency of operation (OSC_IN)                                                        | 25 66                          |     | MHz  |         |

| 19   | OSC_IN rise and fall times                                                             | _                              | 5   | ns   | 7       |

| 20   | OSC_IN duty cycle measured at 1.4 V                                                    | 40                             | 60  | %    |         |

MPC8241 Integrated Processor Hardware Specifications, Rev. 10

Notes:

VM = Midpoint voltage (1.4 V).

10b-d = Input signals valid timing.

11a = Input hold time of SDRAM\_SYNC\_IN to memory.

12b-d = sys\_logic\_clk to output valid timing.

13b = Output hold time for non-PCI signals.

14b = SDRAM-SYNC\_IN to output high-impedance timing for non-PCI signals.

Tos = Offset timing required to align sys\_logic\_clk with SDRAM\_SYNC\_IN. The SDRAM\_SYNC\_IN signal is adjusted by the DLL to accommodate for internal delay. This causes SDRAM\_SYNC\_IN to appear before sys\_logic\_clk once the DLL locks.

Figure 11. Input/Output Timing Diagram Referenced to SDRAM\_SYNC\_IN

Figure 12. Input/Output Timing Diagram Referenced to PCI\_SYNC\_IN

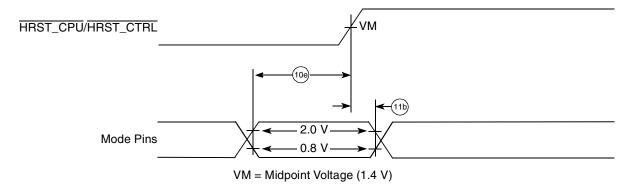

Figure 13 shows the input timing diagram for mode select signals.

Figure 13. Input Timing Diagram for Mode Select Signals

# 4.5.3 Output AC Timing Specification

Table 11 provides the processor bus AC timing specifications for the MPC8241 at recommended operating conditions (see Table 2) with  $LV_{DD}=3.3~V\pm0.3~V$  (see Figure 11). All output timings assume a purely resistive 50- $\Omega$  load (see Figure 14). Output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias, and connectors in the system. These specifications are for the default driver strengths that Table 4 indicates.

| Num  | Characteristic                                                            | Min | Max  | Unit | Notes   |

|------|---------------------------------------------------------------------------|-----|------|------|---------|

| 12a  | PCI_SYNC_IN to output valid, see Figure 15                                | -   |      |      | ·!      |

| 12a0 | Tap 0, PCI_HOLD_DEL = 00, [MCP,CKE] = 11, 66 MHz PCI (default)            | _   | 6.0  | ns   | 1, 3    |

| 12a1 | Tap 1, PCI_HOLD_DEL = 01, [MCP,CKE] = 10                                  | _   | 6.5  |      |         |

| 12a2 | Tap 2, PCI_HOLD_DEL = 10, [MCP,CKE] = 01, 33 MHz PCI                      | _   | 7.0  |      |         |

| 12a3 | Tap 3, PCI_HOLD_DEL = 11, [MCP,CKE] = 00                                  | _   | 7.5  |      |         |

| 12b  | sys_logic_clk to output valid (memory address, control, and data signals) | _   | 4.5  | ns   | 2       |

| 12c  | sys_logic_clk to output valid (for all others)                            | _   | 7.0  | ns   | 2       |

| 12d  | sys_logic_clk to output valid (for I <sup>2</sup> C)                      | _   | 5.0  | ns   | 2       |

| 12e  | sys_logic_clk to output valid (ROM/Flash/Port X)                          | _   | 6.0  | ns   | 2       |

| 13a  | Output hold (PCI), see Figure 15                                          |     |      |      |         |

| 13a0 | Tap 0, PCI_HOLD_DEL = 00, [MCP,CKE] = 11, 66 MHz PCI (default)            | 2.0 | _    | ns   | 1, 3, 4 |

| 13a1 | Tap 1, PCI_HOLD_DEL = 01, [MCP,CKE] = 10                                  | 2.5 | _    |      |         |

| 13a2 | Tap 2, PCI_HOLD_DEL = 10, [MCP,CKE] = 01, 33 MHz PCI                      | 3.0 | _    |      |         |

| 13a3 | Tap 3, PCI_HOLD_DEL = 11, [MCP,CKE] = 00                                  | 3.5 | _    |      |         |

| 13b  | Output hold (all others)                                                  | 1.0 | _    | ns   | 2       |

| 14a  | PCI_SYNC_IN to output high impedance (for PCI)                            | _   | 14.0 | ns   | 1, 3    |

**Table 11. Output AC Timing Specifications**

## MPC8241 Integrated Processor Hardware Specifications, Rev. 10

## Table 12. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $OV_{DD}$  of 3.3 V  $\pm$  5%.

| Pulse width of spikes which must be suppressed by the input filter                                                     | t <sub>I2KHKL</sub> | 0   | 50 | ns | 2 |

|------------------------------------------------------------------------------------------------------------------------|---------------------|-----|----|----|---|

| Input current each I/O pin (input voltage is between $0.1 \times \text{OV}_{DD}$ and $0.9 \times \text{OV}_{DD}$ (max) | I <sub>I</sub>      | -10 | 10 | μΑ | 3 |

| Capacitance for each I/O pin                                                                                           | C <sub>I</sub>      | _   | 10 | pF |   |

### Notes:

- 1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2. Refer to the MPC8245 Integrated Processor Reference Manual for information on the digital filter used.

- 3. I/O pins obstruct the SDA and SCL lines if the  ${

m OV}_{

m DD}$  is switched off.

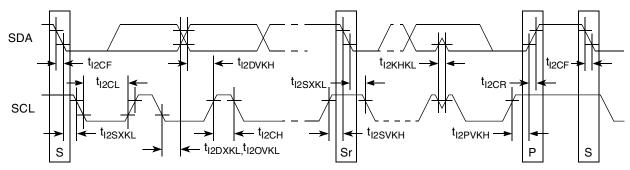

# 4.6.2 I<sup>2</sup>C AC Electrical Specifications

Table 13 provides the AC timing parameters for the I<sup>2</sup>C interfaces.

# Table 13. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}\,(\mbox{min})$  and  $V_{IL}\,(\mbox{max})$  levels (see Table 12).

| Parameter                                                                                    | Symbol <sup>1</sup>   | Min                  | Max              | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|----------------------|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>      | 0                    | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub> 4   | 1.3                  | _                | μs   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub> 4   | 0.6                  | _                | μs   |

| Setup time for a repeated START condition                                                    | t <sub>l2SVKH</sub> 4 | 0.6                  | _                | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> 4 | 0.6                  | _                | μs   |

| Data setup time                                                                              | t <sub>l2DVKH</sub> 4 | 100                  | _                | ns   |

| Data input hold time:  CBUS compatible masters  I <sup>2</sup> C bus devices                 | t <sub>I2DXKL</sub>   |                      |                  | μs   |

| Data output delay time:                                                                      | t <sub>I2OVKL</sub>   | _                    | 0.9 <sup>3</sup> |      |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub>   | 0.6                  | _                | μs   |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub>   | 1.3                  | _                | μs   |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>       | $0.1 \times OV_{DD}$ | _                | V    |

Figure 17 shows the AC timing diagram for the  $I^2C$  bus.

Figure 17. I<sup>2</sup>C Bus AC Timing Diagram

#### 4.7 **PIC Serial Interrupt Mode AC Timing Specifications**

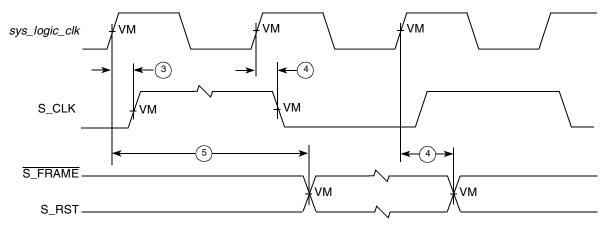

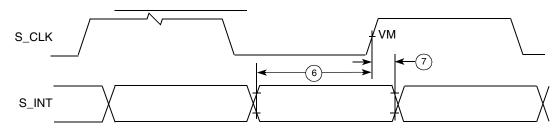

Table 14 provides the PIC serial interrupt mode AC timing specifications for the MPC8241 at recommended operating conditions (see Table 2) with  $GV_{DD}$  = 3.3 V  $\pm$  5% and  $LV_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}.$

| Num | Characteristic                            | Min                        | Max                        | Unit | Notes |

|-----|-------------------------------------------|----------------------------|----------------------------|------|-------|

| 1   | S_CLK frequency                           | 1/14 SDRAM_SYNC_IN         | 1/2 SDRAM_SYNC_IN          | MHz  | 1     |

| 2   | S_CLK duty cycle                          | 40                         | 60                         |      | _     |

| 3   | S_CLK output valid time                   | _                          | 6                          | ns   | _     |

| 4   | Output hold time                          | 0                          | _                          | ns   | _     |

| 5   | S_FRAME, S_RST output valid time          | _                          | 1 sys_logic_clk period + 6 | ns   | 2     |

| 6   | S_INT input setup time to S_CLK           | 1 sys_logic_clk period + 2 | _                          | ns   | 2     |

| 7   | S_INT inputs invalid (hold time) to S_CLK | _                          | 0                          | ns   | 2     |

**Table 14. PIC Serial Interrupt Mode AC Timing Specifications**

## Notes:

- 1. See the MPC8245 Integrated Processor Reference Manual for a description of the PIC interrupt control register (ICR) and S\_CLK frequency programming.

- 2. S\_RST, S\_FRAME, and S\_INT shown in Figure 18 and Figure 19, depict timing relationships to sys\_logic\_clk and S\_CLK and do not describe functional relationships between S\_RST, S\_FRAME, and S\_INT. The MPC8245 Integrated Processor Reference Manual describes the functional relationships between these signals.

- 3. The sys\_logic\_clk waveform is the clocking signal of the internal peripheral logic from the output of the peripheral logic PLL; sys\_logic\_clk is the same as SDRAM\_SYNC\_IN when the SDRAM\_SYNC\_OUT to SDRAM\_SYNC\_IN feedback loop is implemented and the DLL is locked. See the MPC8245 Integrated Processor Reference Manual for a complete clocking description.

Figure 18. PIC Serial Interrupt Mode Output Timing Diagram

Figure 19. PIC Serial Interrupt Mode Input Timing Diagram

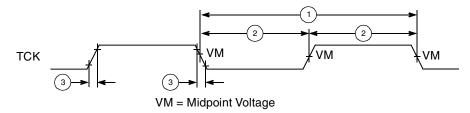

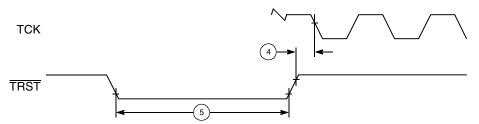

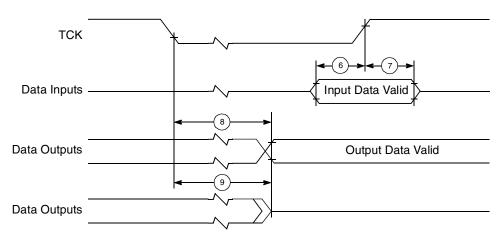

# 4.7.1 IEEE 1149.1 (JTAG) AC Timing Specifications

Table 15 provides the JTAG AC timing specifications for the MPC8241 while in the JTAG operating mode at recommended operating conditions (see Table 2) with  $LV_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}$ . Timings are independent of the system clock (PCI\_SYNC\_IN).

| Num | Characteristic                          | Min | Max | Unit | Notes |

|-----|-----------------------------------------|-----|-----|------|-------|

|     | TCK frequency of operation              | 0   | 25  | MHz  | _     |

| 1   | TCK cycle time                          | 40  | _   | ns   | _     |

| 2   | TCK clock pulse width measured at 1.5 V | 20  | _   | ns   | _     |

| 3   | TCK rise and fall times                 | 0   | 3   | ns   | _     |

| 4   | TRST setup time to TCK falling edge     | 10  | _   | ns   | 1     |

| 5   | TRST assert time                        | 10  | _   | ns   | _     |

| 6   | Input data setup time                   | 5   | _   | ns   | 2     |

| 7   | Input data hold time                    | 15  | _   | ns   | 2     |

| 8   | TCK to output data valid                | 0   | 30  | ns   | 3     |

| 9   | TCK to output high impedance            | 0   | 30  | ns   | 3     |

| 10  | TMS, TDI data setup time                | 5   | _   | ns   | _     |

Table 15. JTAG AC Timing Specification (Independent of PCI\_SYNC\_IN)

MPC8241 Integrated Processor Hardware Specifications, Rev. 10

Table 15. JTAG AC Timing Specification (Independent of PCI\_SYNC\_IN)

| Num | Characteristic            | Min | Max | Unit | Notes |

|-----|---------------------------|-----|-----|------|-------|

| 11  | TMS, TDI data hold time   | 15  | _   | ns   | _     |

| 12  | TCK to TDO data valid     | 0   | 15  | ns   | _     |

| 13  | TCK to TDO high impedance | 0   | 15  | ns   | _     |

### Notes:

- 1. TRST is an asynchronous signal. The setup time is for test purposes only.

- 2. Nontest (other than TDI and TMS) signal input timing with respect to TCK.

- 3. Nontest (other than TDO) signal output timing with respect to TCK.

Figure 20 through Figure 23 show the different timing diagrams for JTAG.

Figure 20. JTAG Clock Input Timing Diagram

Figure 21. JTAG TRST Timing Diagram

Figure 22. JTAG Boundary Scan Timing Diagram

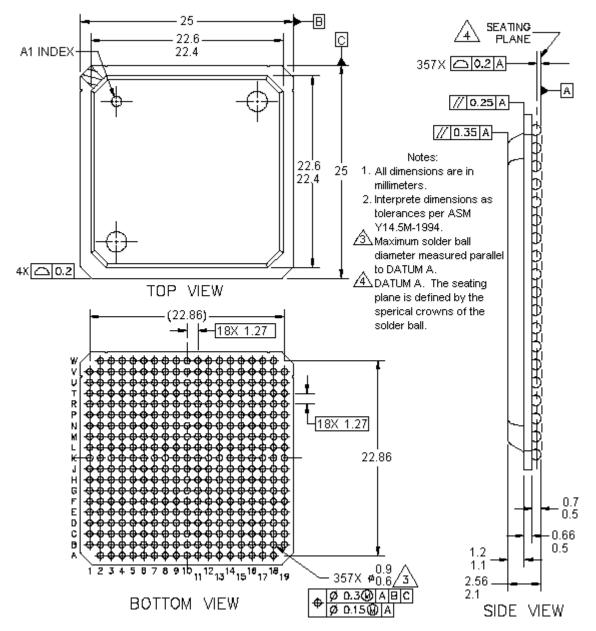

Figure 25 shows the top surface, side profile, and pinout of the MPC8241, 357 PBGA ZQ and VR packages.

Figure 25. MPC8241 Package Dimensions and Pinout Assignments (ZQ and VR Packages)

# 5.3 Pinout Listings

Table 16 provides the pinout listing for the MPC8241, 357 PBGA package.

Table 16. MPC8241 Pinout Listing

|                                                                                                                                    | Table 10. Mil 00                                                                                                         |              |                                    | 1                     | T       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------|-----------------------|---------|--|--|

| Signal Name Package Pin Number                                                                                                     |                                                                                                                          | Pin Type     | Power<br>Supply                    | Output<br>Driver Type | Notes   |  |  |

| PCI Interface Signals                                                                                                              |                                                                                                                          |              |                                    |                       |         |  |  |

| C/BE[3:0]                                                                                                                          | V11 V7 W3 R3                                                                                                             | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 1, 2    |  |  |

| DEVSEL                                                                                                                             | U6                                                                                                                       | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2, 3    |  |  |

| FRAME                                                                                                                              | T8                                                                                                                       | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2, 3    |  |  |

| ĪRDY                                                                                                                               | U7                                                                                                                       | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2, 3    |  |  |

| LOCK                                                                                                                               | V6                                                                                                                       | Input        | GV <sub>DD</sub> _OV <sub>DD</sub> | _                     | 3       |  |  |

| AD[31:0]                                                                                                                           | U13 V13 U11 W14 V14 U12 W10<br>T10 V10 U9 V9 W9 W8 T9 W7<br>V8 V4 W4 V3 V2 T5 R6 V1 T2 U3<br>P3 T4 R1 T3 R4 U2 U1        | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 1, 2    |  |  |

| PAR                                                                                                                                | R7                                                                                                                       | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2       |  |  |

| GNT[3:0]                                                                                                                           | W15 U15 W17 V12                                                                                                          | Output       | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 1, 2    |  |  |

| GNT4/DA5                                                                                                                           | T11                                                                                                                      | Output       | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2, 4, 5 |  |  |

| REQ[3:0]                                                                                                                           | V16 U14 T15 V15                                                                                                          | Input        | GV <sub>DD</sub> OV <sub>DD</sub>  | _                     | 1, 6    |  |  |

| REQ4/DA4                                                                                                                           | REQ4/DA4 W13                                                                                                             |              | GV <sub>DD</sub> _OV <sub>DD</sub> | _                     | 5, 6    |  |  |

| PERR                                                                                                                               | PERR T7                                                                                                                  |              | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2, 3, 7 |  |  |

| SERR                                                                                                                               | SERR U5                                                                                                                  |              | GV <sub>DD</sub> _OV <sub>DD</sub> | DRV_PCI               | 2, 3, 8 |  |  |

| STOP                                                                                                                               | STOP W5                                                                                                                  |              | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2, 3    |  |  |

| TRDY                                                                                                                               | TRDY W6                                                                                                                  |              | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_PCI               | 2, 3    |  |  |

| ĪNTA                                                                                                                               | T12                                                                                                                      | Output       | GV <sub>DD</sub> _OV <sub>DD</sub> | DRV_PCI               | 2, 8    |  |  |

| IDSEL                                                                                                                              | U10                                                                                                                      | Input        | GV <sub>DD</sub> _OV <sub>DD</sub> | _                     | _       |  |  |

|                                                                                                                                    | Memory Int                                                                                                               | terface Sign | als                                |                       |         |  |  |

| MDL[0:31]                                                                                                                          | M19 M17 L16 L17 K18 J18 K17<br>K16 J15 J17 H18 F16 H16 H15<br>G17 D19 B3 C4 C2 D3 G5 E1 H5<br>E2 F1 F2 G2 J5 H1 H4 J4 J1 | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_STD_MEM           | 1, 9    |  |  |

| MDH[0:31] M18 L18 L15 K19 K15 J19 J16<br>H17 G19 G18 G16 D18 F18 E18<br>G15 E15 C3 D4 E5 F5 D1 E4 D2<br>E3 F4 G3 G4 G1 H2 J3 J2 K5 |                                                                                                                          | I/O          | GV <sub>DD</sub> _OV <sub>DD</sub> | DRV_STD_MEM           | 1       |  |  |

| DQM[0:7]                                                                                                                           | A18 B18 A6 C7 D15 D14 A9 B8                                                                                              | Output       | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_MEM_CTRL          | 1       |  |  |

| CS[0:7]                                                                                                                            | A17 B17 C16 C17 C9 C8<br>A10 B10                                                                                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_MEM_CTRL          | 1       |  |  |

| FOE                                                                                                                                | A7                                                                                                                       | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_MEM_CTRL          | 10, 11  |  |  |

| RCS0                                                                                                                               | C10                                                                                                                      | Output       | GV <sub>DD</sub> OV <sub>DD</sub>  | DRV_MEM_CTRL          | 10, 11  |  |  |

|                                                                                                                                    |                                                                                                                          |              |                                    |                       |         |  |  |

Table 16. MPC8241 Pinout Listing (continued)

| SDMA[11:2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Signal Name             | Package Pin Number          | Pin Type     | Power<br>Supply                                                                  | Output<br>Driver Type | Notes     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------|--------------|----------------------------------------------------------------------------------|-----------------------|-----------|

| RCS3/TRIG_OUT   N18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RCS1 B9                 |                             | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | _         |

| SDMA[1:0]   A15 B15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RCS2/TRIG_IN P18        |                             | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>                                                | _                     | 5, 12     |

| SDMA[11:2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RCS3/TRIG_OUT           | N18                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_STD_MEM           | 5         |

| A14 C14 B14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SDMA[1:0]               | A15 B15                     | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 1, 10, 11 |

| SDMA12/SRESET   L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SDMA[11:2]              |                             | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 1         |

| SDMA13/TBEN   K3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DRDY                    | P1                          | Input        | $GV_DD\!\!-\!\!OV_DD$                                                            | _                     | 12, 13    |

| SDMA14/CHKSTOP_IN   K2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SDMA12/SRESET           | L3                          | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 5, 12     |

| SDBA1   C11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SDMA13/TBEN             | К3                          | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 5, 12     |

| SDBA0   B11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SDMA14/CHKSTOP_IN       | K2                          | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 5, 12     |

| PAR[0:7]         E19 C19 D5 D6 E16 F17 B2 C1         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_STD_MEM         1           SDRAS         B19         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10           SDCAS         D16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10           CKE         C6         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10, 11           WE         B16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         —           AS         A16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10, 11           PIC Control Signals           IRQ0/S_INT         P4         Input         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10, 11           IRQ1/S_CLK         R2         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ2/S_RST         U19         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ4/L_INT         P2         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IPQ GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —         —           IPQ GV <sub>DD</sub> OV <sub>DD</sub> DRV_STD_MEM         8, 12           SCC                                                                                                                 | SDBA1                   | C11                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | _         |

| SDRAS         B19         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10           SDCAS         D16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10           CKE         C6         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10,11           WE         B16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         —           AS         A16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10,11           PIC Control Signals           IRQ0/S_INT         P4         Input         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10,11           PIC Control Signals           IRQ2/S_RST         U19         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ3/S_FRAME         P15         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ4/L_INT         P2         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           I²C Control Signals           SDA         P17         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_STD_MEM         8, 12           SOUT1/PCI_CLK0         T16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         5, 14, 2 <td>SDBA0</td> <td>B11</td> <td>Output</td> <td>GV<sub>DD</sub>OV<sub>DD</sub></td> <td>DRV_MEM_CTRL</td> <td>_</td> | SDBA0                   | B11                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | _         |

| SDCAS   D16   Output   GV <sub>DD</sub> OV <sub>DD</sub>   DRV_MEM_CTRL   10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PAR[0:7]                | E19 C19 D5 D6 E16 F17 B2 C1 | I/O          | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_STD_MEM           | 1         |

| CKE         C6         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10, 11           WE         B16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         —           AS         A16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10, 11           PIC Control Signals           IRQ0/S_INT         P4         Input         GV <sub>DD</sub> OV <sub>DD</sub> —         —           IRQ1/S_CLK         R2         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ2/S_RST         U19         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ3/S_FRAME         P15         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           I²C Control Signals           SDA         P17         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_STD_MEM         8, 12           SCL         R19         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_STD_MEM         8, 12           DUART Control Signals           SOUT1/PCI_CLK0         T16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         5, 14, 2           SOUT2/RTS1/PCI_CLK1         U16         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL </td <td>SDRAS</td> <td>B19</td> <td>Output</td> <td>GV<sub>DD</sub>OV<sub>DD</sub></td> <td>DRV_MEM_CTRL</td> <td>10</td>         | SDRAS                   | B19                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 10        |

| WE         B16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         —           AS         A16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         10, 11           PIC Control Signals           IRQ0/S_INT         P4         Input         GV <sub>DD</sub> OV <sub>DD</sub> —         —           IRQ1/S_CLK         R2         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ2/S_RST         U19         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ3/S_FRAME         P15         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           IRQ4/L_INT         P2         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_PCI         —           I²C Control Signals           SDA         P17         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_STD_MEM         8, 12           DUART Control Signals           SOUT1/PCI_CLK0         T16         Output         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         5, 14, 2           SOUT2/RTS1/PCI_CLK1         U16         I/O         GV <sub>DD</sub> OV <sub>DD</sub> DRV_MEM_CTRL         5, 14, 2           Clock-Out Signals                                                                                                                                                                                                       | SDCAS                   | D16                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 10        |

| RQ0/S_INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CKE C6                  |                             | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 10, 11    |

| IRQO/S_INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | WE                      | B16                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | _         |

| IRQ0/S_INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ĀS                      | A16                         | Output       | GV <sub>DD</sub> OV <sub>DD</sub>                                                | DRV_MEM_CTRL          | 10, 11    |

| IRQ1/S_CLK   R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         | PIC Con                     | trol Signals | •                                                                                |                       |           |