#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Betans                          |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Core Processor                  | PowerPC 603e                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 200MHz                                                      |

| Co-Processors/DSP               | -                                                           |

| RAM Controllers                 | SDRAM                                                       |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | -                                                           |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 3.3V                                                        |

| Operating Temperature           | -40°C ~ 105°C (TA)                                          |

| Security Features               | -                                                           |

| Package / Case                  | 357-BBGA                                                    |

| Supplier Device Package         | 357-PBGA (25x25)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8241tvr200d |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

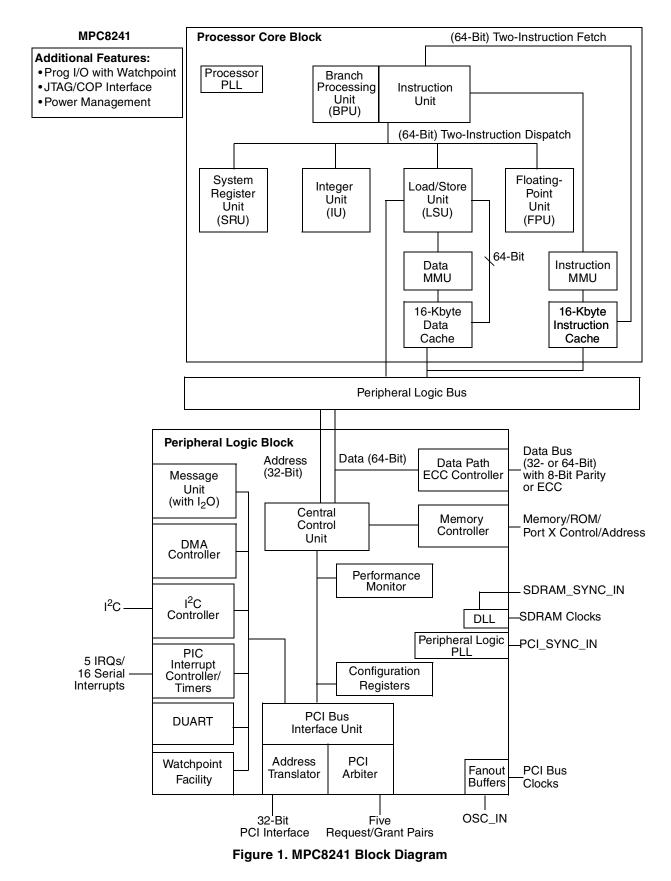

Overview

MPC8241 Integrated Processor Hardware Specifications, Rev. 10

**Electrical and Thermal Characteristics**

# 4 Electrical and Thermal Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8241.

## 4.1 DC Electrical Characteristics

This section covers ratings, conditions, and other characteristics.

### 4.1.1 Absolute Maximum Ratings

This section describes the MPC8241 DC electrical characteristics. Table 1 provides the absolute maximum ratings.

| Characteristic <sup>1</sup>                                     | Symbol                               | Range       | Unit |

|-----------------------------------------------------------------|--------------------------------------|-------------|------|

| Supply voltage—CPU core and peripheral logic                    | V <sub>DD</sub>                      | -0.3 to 2.1 | V    |

| Supply voltage—memory bus drivers, PCI and standard I/O buffers | GV <sub>DD</sub> OV <sub>DD</sub>    | -0.3 to 3.6 | V    |

| Supply voltage—PLLs                                             | AV <sub>DD</sub> /AV <sub>DD</sub> 2 | -0.3 to 2.1 | V    |

| Supply voltage—PCI reference                                    | LV <sub>DD</sub>                     | -0.3 to 5.4 | V    |

| Input voltage <sup>2</sup>                                      | V <sub>in</sub>                      | -0.3 to 3.6 | V    |

| Operational die-junction temperature range                      | Tj                                   | 0 to 105    | •C   |

| Storage temperature range                                       | T <sub>stg</sub>                     | –55 to 150  | •C   |

#### Table 1. Absolute Maximum Ratings

#### Notes:

1. Table 2 provides functional and tested operating conditions. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

2. PCI inputs with  $LV_{DD}$  = 5 V ± 5% V DC may be correspondingly stressed at voltages exceeding  $LV_{DD}$  + 0.5 V DC.

### 4.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for the MPC8241.

| Chara                                                   | Symbol                            | Recommended<br>Value  | Unit             | Notes |         |

|---------------------------------------------------------|-----------------------------------|-----------------------|------------------|-------|---------|

| Supply voltage                                          | V <sub>DD</sub>                   | $1.8\pm100~\text{mV}$ | V                | 2     |         |

| I/O buffer supply for PCI and sta<br>memory bus drivers | GV <sub>DD</sub> OV <sub>DD</sub> | $3.3\pm0.3$           | V                | 2     |         |

| CPU PLL supply voltage                                  | AV <sub>DD</sub>                  | $1.8\pm100~\text{mV}$ |                  | 2     |         |

| PLL supply voltage—periphera                            | AV <sub>DD</sub> 2                | $1.8\pm100~\text{mV}$ | V                | 2     |         |

| PCI reference                                           |                                   | LV <sub>DD</sub>      | $5.0\pm5\%$      | V     | 4, 5, 6 |

|                                                         |                                   |                       | $3.3\pm0.3$      | V     | 5, 6, 7 |

| Input voltage                                           | PCI inputs                        | V <sub>in</sub>       | 0 to 3.6 or 5.75 | V     | 4, 7    |

|                                                         | All other inputs                  |                       | 0 to 3.6         | V     | 8       |

| Die-junction temperature                                |                                   | Тј                    | 0 to 105         | •C    |         |

#### Table 2. Recommended Operating Conditions <sup>1</sup>

#### Notes:

1. Freescale has tested these operating conditions and recommends them. Proper device operation outside of these conditions is not guaranteed.

- Caution: GV<sub>DD</sub>\_OV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 by more than 1.8 V at any time including during power-on reset. Note that GV<sub>DD</sub>\_OV<sub>DD</sub> pins are all shorted together: This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences. Connections should not be made to individual PWRRING pins.

- Caution: V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 must not exceed GV<sub>DD</sub>OV<sub>DD</sub> by more than 0.6 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. PCI pins are designed to withstand LV<sub>DD</sub> + 0.5 V DC when LV<sub>DD</sub> is connected to a 5.0 V DC power supply.

- 5. Caution: LV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2 by more than 5.4 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 6. Caution: LV<sub>DD</sub> must not exceed GV<sub>DD</sub>OV<sub>DD</sub> by more than 3.0 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 7. PCI pins are designed to withstand LV<sub>DD</sub> + 0.5 V DC when LV<sub>DD</sub> is connected to a 3.3 V DC power supply.

- Caution: Input voltage (V<sub>in</sub>) must not be greater than the supply voltage (V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2) by more than 2.5 V at all times including during power-on reset. Input voltage (V<sub>in</sub>) must not be greater than GV<sub>DD</sub>OV<sub>DD</sub> by more than 0.6 V at all times including during power-on reset.

NP\_\_\_\_

#### **Electrical and Thermal Characteristics**

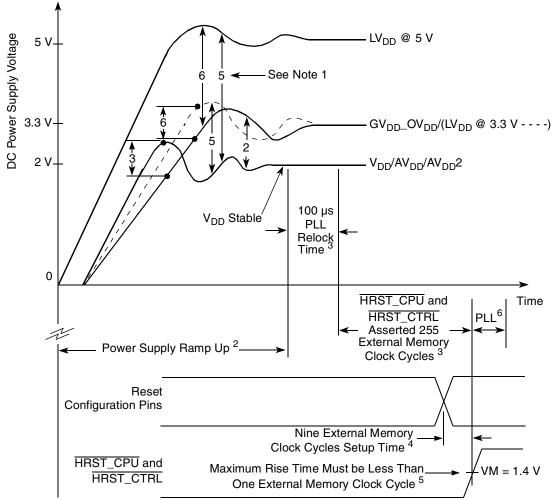

Figure 2 shows supply voltage sequencing and separation cautions.

#### Notes:

- 1. Numbers associated with waveform separations correspond to caution numbers listed in Table 2.

- 2. See the Cautions section of Table 2 for details on this topic.

- 3. Refer to Table 8 for details on PLL relock and reset signal assertion timing requirements.

- 4. Refer to Table 10 for details on reset configuration pin setup timing requirements.

- 5. HRST\_CPU/HRST\_CTRL must transition from a logic 0 to a logic 1 in less than one SDRAM\_SYNC\_IN clock cycle for the device to be in the nonreset state.

- 6. PLL\_CFG signals must be driven on reset and must be held for at least 25 clock cycles after the negation of HRST\_CTRL and HRST\_CPU negate in order to be latched.

#### Figure 2. Supply Voltage Sequencing and Separation Cautions

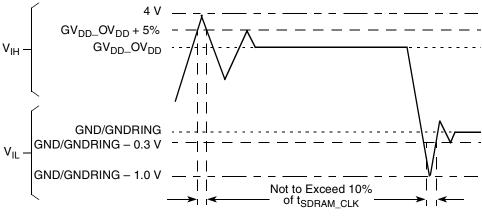

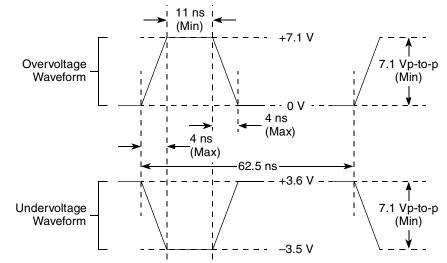

Figure 3 shows the undershoot and overshoot voltage of the memory interface.

Figure 3. Overshoot/Undershoot Voltage

Figure 4 and Figure 5 show the undershoot and overshoot voltage of the PCI interface for the 3.3- and 5-V signals, respectively.

Figure 4. Maximum AC Waveforms for 3.3-V Signaling

| Num  | Characteristic                                                                    | Min | Max | Unit | Notes   |

|------|-----------------------------------------------------------------------------------|-----|-----|------|---------|

| 10b0 | Tap 0, register offset <0x77>, bits 5:4 = 0b00                                    | 2.6 | _   | ns   | 2, 3, 6 |

| 10b1 | Tap 1, register offset <0x77>, bits 5:4 = 0b01                                    | 1.9 | _   |      |         |

| 10b2 | Tap 2, register offset <0x77>, bits 5:4 = 0b10 (default)                          | 1.2 | —   |      |         |

| 10b3 | Tap 3, register offset <0x77>, bits 5:4 = 0b11                                    | 0.5 | —   |      |         |

| 10c  | PIC miscellaneous debug input signals valid to <i>sys_logic_clk</i> (input setup) | 3.0 | —   | ns   | 2, 3    |

| 10d  | I <sup>2</sup> C input signals valid to <i>sys_logic_clk</i> (input setup)        | 3.0 | —   | ns   | 2, 3    |

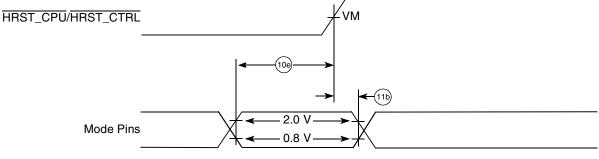

| 10e  | Mode select inputs valid to HRST_CPU/HRST_CTRL (input setup)                      |     | _   | ns   | 2, 3–5  |

| 11   | T <sub>os</sub> —SDRAM_SYNC_IN to <i>sys_logic_clk</i> offset time                |     | 1.0 | ns   | 7       |

| 11a  | sys_logic_clk to memory signal inputs invalid (input hold)                        |     |     |      |         |

| 11a0 | Tap 0, register offset <0x77>, bits 5:4 = 0b00                                    | 0   | —   | ns   | 2, 3, 6 |

| 11a1 | Tap 1, register offset <0x77>, bits 5:4 = 0b01                                    | 0.7 | —   |      |         |

| 11a2 | Tap 2, register offset <0x77>, bits 5:4 = 0b10 (default)                          |     | —   |      |         |

| 11a3 | Tap 3, register offset <0x77>, bits 5:4 = 0b11                                    | 2.1 | —   |      |         |

| 11b  | HRST_CPU/HRST_CTRL to mode select inputs invalid (input hold)                     | 0   | —   | ns   | 2, 3, 5 |

| 11c  | PCI_SYNC_IN to inputs invalid (input hold)                                        | 1.0 | —   | ns   | 1, 2, 3 |

#### Table 10. Input AC Timing Specifications (continued)

#### Notes:

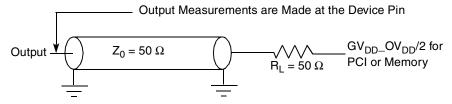

1. All PCI signals are measured from  $GV_{DD}$ \_ $OV_{DD}$ /2 of the rising edge of PCI\_SYNC\_IN to 0.4 ×  $GV_{DD}$ \_ $OV_{DD}$  of the signal in question for 3.3-V PCI signaling levels. See Figure 12.

- 2. All memory and related interface input signal specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the VM = 1.4 V of the rising edge of the memory bus clock. sys\_logic\_clk. sys\_logic\_clk is the same as PCI\_SYNC\_IN in 1:1 mode, but is twice the frequency in 2:1 mode (processor/memory bus clock rising edges occur on every rising and falling edge of PCI\_SYNC\_IN). See Figure 11.

- 3. Input timings are measured at the pin.

- 4. t<sub>CLK</sub> is the time of one SDRAM\_SYNC\_IN clock cycle.

- 5. All mode select input signals specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the VM = 1.4 V of the rising edge of the HRST\_CPU/HRST\_CTRL signal. See Figure 13.

- The memory interface input setup and hold times are programmable to four possible combinations by programming bits 5:4 of register offset <0x77> to select the desired input setup and hold times.

- 7. T<sub>os</sub> represents a timing adjustment for SDRAM\_SYNC\_IN with respect to sys\_logic\_clk. Due to the internal delay present on the SDRAM\_SYNC\_IN signal with respect to the sys\_logic\_clk inputs to the DLL, the resulting SDRAM clocks become offset by the delay amount. The feedback trace length of SDRAM\_SYNC\_OUT to SDRAM\_SYNC\_IN must be shortened to accommodate this range relative to the SDRAM clock output trace lengths to maintain phase-alignment of the memory clocks with respect to sys\_logic\_clk. It is recommended that the length of SDRAM\_SYNC\_OUT to SDRAM\_SYNC\_IN be shortened by 0.7 ns because that is the midpoint of the range of T<sub>os</sub> and allows the impact from the range of T<sub>os</sub> to be reduced. Additional analyses of trace lengths and SDRAM loading must be performed to optimize timing. For details on trace measurements and the T<sub>os</sub> problem, refer to the Freescale application note AN2164, MPC8245/MPC8241 Memory Clock Design Guidelines.

Figure 13 shows the input timing diagram for mode select signals.

VM = Midpoint Voltage (1.4 V)

Figure 13. Input Timing Diagram for Mode Select Signals

### 4.5.3 Output AC Timing Specification

Table 11 provides the processor bus AC timing specifications for the MPC8241 at recommended operating conditions (see Table 2) with  $LV_{DD} = 3.3 V \pm 0.3 V$  (see Figure 11). All output timings assume a purely resistive 50- $\Omega$  load (see Figure 14). Output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias, and connectors in the system. These specifications are for the default driver strengths that Table 4 indicates.

| Num  | Characteristic                                                                   | Min | Мах  | Unit | Notes   |  |  |

|------|----------------------------------------------------------------------------------|-----|------|------|---------|--|--|

| 12a  | PCI_SYNC_IN to output valid, see Figure 15                                       |     |      |      |         |  |  |

| 12a0 | Tap 0, PCI_HOLD_DEL = 00, [MCP,CKE] = 11, 66 MHz PCI (default)                   | _   | 6.0  | ns   | 1, 3    |  |  |

| 12a1 | Tap 1, PCI_HOLD_DEL = 01, [MCP,CKE] = 10                                         | _   | 6.5  |      |         |  |  |

| 12a2 | Tap 2, PCI_HOLD_DEL = 10, [MCP,CKE] = 01, 33 MHz PCI                             | _   | 7.0  |      |         |  |  |

| 12a3 | Tap 3, PCI_HOLD_DEL = 11, [MCP,CKE] = 00                                         | —   | 7.5  |      |         |  |  |

| 12b  | <i>sys_logic_clk</i> to output valid (memory address, control, and data signals) | —   | 4.5  | ns   | 2       |  |  |

| 12c  | <i>sys_logic_clk</i> to output valid (for all others)                            | —   | 7.0  | ns   | 2       |  |  |

| 12d  | sys_logic_clk to output valid (for I <sup>2</sup> C)                             |     | 5.0  | ns   | 2       |  |  |

| 12e  | <i>sys_logic_clk</i> to output valid (ROM/Flash/Port X)                          | —   | 6.0  | ns   | 2       |  |  |

| 13a  | Output hold (PCI), see Figure 15                                                 |     |      |      |         |  |  |

| 13a0 | Tap 0, PCI_HOLD_DEL = 00, [MCP,CKE] = 11, 66 MHz PCI (default)                   | 2.0 |      | ns   | 1, 3, 4 |  |  |

| 13a1 | Tap 1, PCI_HOLD_DEL = 01, [MCP,CKE] = 10                                         | 2.5 | _    |      |         |  |  |

| 13a2 | Tap 2, PCI_HOLD_DEL = 10, [MCP,CKE] = 01, 33 MHz PCI                             | 3.0 | _    |      |         |  |  |

| 13a3 | Tap 3, PCI_HOLD_DEL = 11, [MCP,CKE] = 00                                         | 3.5 |      |      |         |  |  |

| 13b  | Output hold (all others)                                                         | 1.0 |      | ns   | 2       |  |  |

| 14a  | PCI_SYNC_IN to output high impedance (for PCI)                                   | —   | 14.0 | ns   | 1, 3    |  |  |

Table 11. Output AC Timing Specifications

#### MPC8241 Integrated Processor Hardware Specifications, Rev. 10

| Num | Characteristic                                          | Min | Мах | Unit | Notes |

|-----|---------------------------------------------------------|-----|-----|------|-------|

| 14b | sys_logic_clk to output high impedance (for all others) |     | 4.0 | ns   | 2     |

#### Table 11. Output AC Timing Specifications (continued)

Notes:

- 1. All PCI signals are measured from  $GV_{DD}$ – $OV_{DD}$ /2 of the rising edge of PCI\_SYNC\_IN to 0.285 ×  $GV_{DD}$ – $OV_{DD}$  or 0.615 ×  $GV_{DD}$ – $OV_{DD}$  of the signal in question for 3.3 V PCI signaling levels. See Figure 12.

- 2. All memory and related interface output signal specifications are specified from the VM = 1.4 V of the rising edge of the memory bus clock, sys\_logic\_clk to the TTL level (0.8 or 2.0 V) of the signal in question. sys\_logic\_clk is the same as PCI\_SYNC\_IN in 1:1 mode, but is twice the frequency in 2:1 mode (processor/memory bus clock rising edges occur on every rising and falling edge of PCI\_SYNC\_IN). See Figure 11.

- 3. PCI bused signals are composed of the following signals: LOCK, IRDY, C/BE[3:0], PAR, TRDY, FRAME, STOP, DEVSEL, PERR, SERR, AD[31:0], REQ[4:0], GNT[4:0], IDSEL, and INTA.

- 4. To meet minimum output hold specifications relative to PCI\_SYNC\_IN for both 33- and 66-MHz PCI systems, the MPC8241 has a programmable output hold delay for PCI signals (the PCI\_SYNC\_IN to output valid timing is also affected). The initial value of the output hold delay is determined by the values on the MCP and CKE reset configuration signals; the values on these two signals are inverted and subsequently stored as the initial settings of PCI\_HOLD\_DEL = PMCR2[5, 4] (power management configuration register 2 <0x72>), respectively. Because MCP and CKE have internal pull-up resistors, the default value of PCI\_HOLD\_DEL after reset is 0b00. Additional output hold delay values are available by programming the PCI\_HOLD\_DEL value of the PMCR2 configuration register. See Figure 15 for PCI\_HOLD\_DEL effect on output valid and hold time.

Figure 14 provides the AC test load for the MPC8241.

Figure 14. AC Test Load for the MPC8241

#### Table 13. I<sup>2</sup>C AC Electrical Specifications (continued)

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 12).

| Parameter                                                                       | Symbol <sup>1</sup> | Min                  | Мах | Unit |

|---------------------------------------------------------------------------------|---------------------|----------------------|-----|------|

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times OV_{DD}$ | —   | V    |

#### Note:

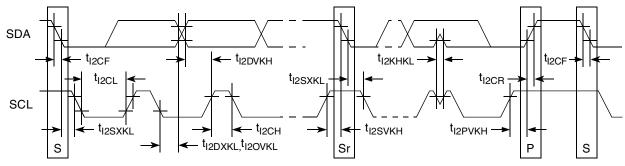

- 1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>I2DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>I2SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>I2C</sub> clock reference (K) going to the low (L) state or hold time. Also, t<sub>I2PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the stop condition (P) reaching the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. As a transmitter, the MPC8245 provides a delay time of at least 300 ns for the SDA signal (referred to the Vihmin of the SCL signal) to bridge the undefined region of the falling edge of SCL to avoid the unintended generation of a Start or Stop condition. When the MPC8245 acts as the I<sup>2</sup>C bus master while transmitting, it drives both SCL and SDA. As long as the load on SCL and SDA is balanced, the MPC8245 does not cause an unintended generation of a Start or Stop condition. Therefore, the 300 ns SDA output delay time is not a concern. If, under some rare condition, the 300 ns SDA output delay time is required for the MPC8245 as transmitter, the following setting is recommended for the FDR bit field of the I2CFDR register to ensure both the desired I<sup>2</sup>C SCL clock frequency and SDA output delay time are achieved. It is assumed that the desired I<sup>2</sup>C SCL clock frequency is 400 KHz and the digital filter sampling rate register (DFFSR bits in I2CFDR) is programmed with its default setting of 0x10 (decimal 16):

| SDRAM Clock Frequency       | 100 MHz     | 133 MHz   |

|-----------------------------|-------------|-----------|

| FDR Bit Setting             | 0x00        | 0x2A      |

| Actual FDR Divider Selected | 384         | 896       |

|                             | 000 4 1/11- | 440 41411 |

Actual I<sup>2</sup>C SCL Frequency Generated 260.4 KHz 148.4 KHz

For details on I<sup>2</sup>C frequency calculation, refer to the application note AN2919 "Determining the I<sup>2</sup>C Frequency Divider Ratio for SCL".

- 3. The maximum t<sub>I2DXKL</sub> has only to be met if the device does not stretch the LOW period (t<sub>I2CL</sub>) of the SCL signal.

- 4. Guaranteed by design

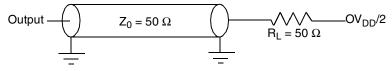

Figure 16 provides the AC test load for the  $I^2C$ .

Figure 16. I<sup>2</sup>C AC Test Load

Figure 17 shows the AC timing diagram for the  $I^2C$  bus.

Figure 17. I<sup>2</sup>C Bus AC Timing Diagram

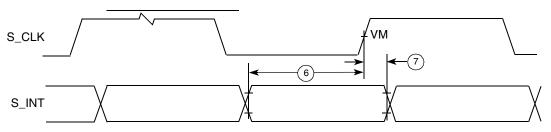

## 4.7 PIC Serial Interrupt Mode AC Timing Specifications

Table 14 provides the PIC serial interrupt mode AC timing specifications for the MPC8241 at recommended operating conditions (see Table 2) with  $GV_{DD}$ – $OV_{DD}$  = 3.3 V ± 5% and  $LV_{DD}$  = 3.3 V ± 0.3 V.

| Num | Characteristic                            | Characteristic Min                           |                                   | Unit | Notes |

|-----|-------------------------------------------|----------------------------------------------|-----------------------------------|------|-------|

| 1   | S_CLK frequency                           | S_CLK frequency 1/14 SDRAM_SYNC_IN 1/2 SDRAI |                                   | MHz  | 1     |

| 2   | S_CLK duty cycle                          | S_CLK duty cycle 40 60                       |                                   | %    | —     |

| 3   | S_CLK output valid time                   | —                                            | 6                                 | ns   | —     |

| 4   | Output hold time                          | 0                                            | —                                 | ns   | —     |

| 5   | S_FRAME, S_RST output valid time          | —                                            | 1 <i>sys_logic_clk</i> period + 6 | ns   | 2     |

| 6   | S_INT input setup time to S_CLK           | 1 sys_logic_clk period + 2 —                 |                                   | ns   | 2     |

| 7   | S_INT inputs invalid (hold time) to S_CLK | —                                            | 0                                 | ns   | 2     |

Table 14. PIC Serial Interrupt Mode AC Timing Specifications

Notes:

- 2. S\_RST, S\_FRAME, and S\_INT shown in Figure 18 and Figure 19, depict timing relationships to *sys\_logic\_clk* and S\_CLK and do not describe functional relationships between S\_RST, S\_FRAME, and S\_INT. The *MPC8245 Integrated Processor Reference Manual* describes the functional relationships between these signals.

- 3. The *sys\_logic\_clk* waveform is the clocking signal of the internal peripheral logic from the output of the peripheral logic PLL; *sys\_logic\_clk* is the same as SDRAM\_SYNC\_IN when the SDRAM\_SYNC\_OUT to SDRAM\_SYNC\_IN feedback loop is implemented and the DLL is locked. See the *MPC8245 Integrated Processor Reference Manual* for a complete clocking description.

<sup>1.</sup> See the *MPC8245 Integrated Processor Reference Manual* for a description of the PIC interrupt control register (ICR) and S\_CLK frequency programming.

Figure 18. PIC Serial Interrupt Mode Output Timing Diagram

Figure 19. PIC Serial Interrupt Mode Input Timing Diagram

### 4.7.1 IEEE 1149.1 (JTAG) AC Timing Specifications

Table 15 provides the JTAG AC timing specifications for the MPC8241 while in the JTAG operating mode at recommended operating conditions (see Table 2) with  $LV_{DD} = 3.3 V \pm 0.3 V$ . Timings are independent of the system clock (PCI\_SYNC\_IN).

| Num | Characteristic                          | Min | Мах | Unit | Notes |

|-----|-----------------------------------------|-----|-----|------|-------|

|     | TCK frequency of operation              | 0   | 25  | MHz  | —     |

| 1   | TCK cycle time                          | 40  | —   | ns   | —     |

| 2   | TCK clock pulse width measured at 1.5 V | 20  | —   | ns   | —     |

| 3   | TCK rise and fall times                 | 0   | 3   | ns   | —     |

| 4   | TRST setup time to TCK falling edge     | 10  | —   | ns   | 1     |

| 5   | TRST assert time                        | 10  | —   | ns   | —     |

| 6   | Input data setup time                   | 5   | —   | ns   | 2     |

| 7   | Input data hold time                    | 15  | —   | ns   | 2     |

| 8   | TCK to output data valid                | 0   | 30  | ns   | 3     |

| 9   | TCK to output high impedance            | 0   | 30  | ns   | 3     |

| 10  | TMS, TDI data setup time                | 5   | _   | ns   | —     |

Table 15. JTAG AC Timing Specification (Independent of PCI\_SYNC\_IN)

#### MPC8241 Integrated Processor Hardware Specifications, Rev. 10

|                                             |                                                                                                                                                                                                                                                                                     |                                                         | g (continued)                                                  |                       |           |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|-----------------------|-----------|

| Signal Name                                 | Package Pin Number                                                                                                                                                                                                                                                                  | Pin Type                                                | Power<br>Supply                                                | Output<br>Driver Type | Notes     |

| TMS                                         | T18                                                                                                                                                                                                                                                                                 | Input                                                   | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | _                     | 6, 13     |

| TRST                                        | R16                                                                                                                                                                                                                                                                                 | Input                                                   | $GV_{DD}OV_{DD}$                                               | —                     | 6, 13     |

|                                             | Power and                                                                                                                                                                                                                                                                           | Ground Sign                                             | als                                                            |                       |           |

| GNDRING/GND                                 | F07 F08 F09 F10 F11 F12 F13<br>G07 G08 G09 G10 G11 G12 G13<br>H07 H08 H09 H10 H11 H12 H13<br>J07 J08 J09 J10 J11 J12 J13 K07<br>K08 K09 K10 K11 K12 K13 L07<br>L08 L09 L10 L11 L12 L13 M07<br>M08 M09 M10 M11 M12 M13<br>N07 N08 N09 N10 N11 N12 N13<br>P08 P09 P10 P11 P12 P13 R15 | Ground                                                  | _                                                              | _                     | 17        |

| LV <sub>DD</sub>                            | R18 U18 T1 U4 T6 W11 T14                                                                                                                                                                                                                                                            | Reference<br>voltage<br>3.3 V,<br>5.0 V                 | LV <sub>DD</sub>                                               | _                     | _         |

| GV <sub>DD</sub> _OV <sub>DD</sub> /PWRRING | D09 D10 D11 E06 E07 E08 E09<br>E10 E11 E12 E13 E14 F06 F14<br>G06 G14 H06 H14 J06 J14 K06<br>K14 L06 L14 M06 M14 N06 N14<br>P06 P07 P14 R08 R09 R10 R11<br>R12                                                                                                                      | Power for<br>memory<br>drivers and<br>PCI/Stnd<br>3.3 V | GV <sub>DD</sub> OV <sub>DD</sub>                              | _                     | 18        |

| V <sub>DD</sub>                             | F03 H3 L5 N4 P5 V5 U8 W12<br>W16 R13 P19 L19 H19 F19 F15<br>C15 A13 A8 B5 A2                                                                                                                                                                                                        | Power for core 1.8 V                                    | V <sub>DD</sub>                                                | _                     | _         |

| No Connect                                  | N5 W2 B1                                                                                                                                                                                                                                                                            | —                                                       | —                                                              | —                     | —         |

| AV <sub>DD</sub>                            | M5                                                                                                                                                                                                                                                                                  | Power for<br>PLL (CPU<br>core logic)<br>1.8 V           | AV <sub>DD</sub>                                               | _                     | _         |

| AV <sub>DD</sub> 2                          | R14                                                                                                                                                                                                                                                                                 | Power for<br>PLL<br>(peripheral<br>logic)<br>1.8 V      | AV <sub>DD</sub> 2                                             | _                     | _         |

|                                             | Debug/Man                                                                                                                                                                                                                                                                           | ufacturing P                                            | ins                                                            |                       | 1         |

| DA0/QACK                                    | A3                                                                                                                                                                                                                                                                                  | Output                                                  | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_STD_MEM           | 5, 11, 12 |

| DA1/CKO                                     | L1                                                                                                                                                                                                                                                                                  | Output                                                  | $\mathrm{GV}_{\mathrm{DD}}\mathrm{-}\mathrm{OV}_{\mathrm{DD}}$ | DRV_STD_MEM           | 5         |

| DA2                                         | R5                                                                                                                                                                                                                                                                                  | Output                                                  | $GV_{DD}OV_{DD}$                                               | DRV_PCI               | 19        |

| DA3/PCI_CLK4                                | V17                                                                                                                                                                                                                                                                                 | Output                                                  | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | DRV_PCI_CLK           | 5         |

| DA4/REQ4                                    | W13                                                                                                                                                                                                                                                                                 | I/O                                                     | $\rm GV_{\rm DD} - \rm OV_{\rm DD}$                            | _                     | 5, 6      |

| DA5/GNT4                                    | T11                                                                                                                                                                                                                                                                                 | Output                                                  | GV <sub>DD</sub> OV <sub>DD</sub>                              | DRV_PCI               | 2, 4, 5   |

#### Table 16. MPC8241 Pinout Listing (continued)

|                  |                               | 166 MHz-Part <sup>2</sup>                                              |                                                            | 200-MHz Part <sup>2</sup>      |                                                                        |                                                            | Multipliers                    |                             |                             |

|------------------|-------------------------------|------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------|-----------------------------|-----------------------------|

| Ref <sup>2</sup> | PLL_CFG<br>[0:4] <sup>1</sup> | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>3</sup><br>(MHz) | Peripheral<br>Logic/<br>Mem<br>Bus Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI Clock<br>Input<br>(PCI_<br>SYNC_IN)<br>Range <sup>3</sup><br>(MHz) | Peripheral<br>Logic/<br>Mem Bus<br>Clock<br>Range<br>(MHz) | CPU<br>Clock<br>Range<br>(MHz) | PCI-to-<br>Mem<br>(Mem VCO) | Mem-to-<br>CPU<br>(CPU VCO) |

| 1E               | 11110 <sup>14</sup>           | Not usable                                                             |                                                            | Not usable                     |                                                                        | Off                                                        | Off                            |                             |                             |

| 1F               | 11111 <sup>14</sup>           | Not usable                                                             |                                                            |                                | Not usable                                                             |                                                            | Off                            | Off                         |                             |

#### Notes:

- 1. PLL\_CFG[0:4] settings not listed are reserved. Bits 7–4 of register offset <0xE2> contain the PLL\_CFG[0:4] setting value. Note the impact of the relevant revisions for mode 7.

- 2. Range values are shown rounded down to the nearest whole number (decimal place accuracy removed) for clarity.

- 3. Limited by maximum PCI input frequency (66 MHz).

- 4. Limited by minimum CPU VCO frequency (300 MHz).

- 5. Limited by maximum CPU operating frequency.

- 6. In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in PLL bypass mode.

- 7. Limited by minimum CPU operating frequency (100 MHz).

- 8. Limited due to maximum memory VCO frequency (352 MHz).

- 9. In dual PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal peripheral logic directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI\_SYNC\_IN:Mem) mode operation. In this mode, the OSC\_IN input signal clocks the internal processor directly in 1:1 (OSC\_IN:CPU) mode operation, and the processor PLL is disabled. The PCI\_SYNC\_IN and OSC\_IN input clocks must be externally synchronized. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in dual PLL bypass mode.

- 10.Limited by maximum CPU VCO frequency (704 MHz).

11.Limited by maximum system memory interface operating frequency (83 MHz @ 166 MHz CPU bus speed).

- 12.Limited by maximum system memory interface operating frequency (100 MHz @ 200 MHz CPU bus speed).

- 13.Limited by minimum memory VCO frequency (132 MHz).

14.In clock off mode, no clocking occurs inside the MPC8241, regardless of the PCI\_SYNC\_IN input.

| Ref <sup>2</sup> | PLL_<br>CFG[0:4] <sup>10,11</sup> | 266-MHz Part <sup>9</sup>                                       |                                                  |                             | Multipliers             |                         |  |

|------------------|-----------------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------|-------------------------|--|

|                  |                                   | PCI Clock Input<br>(PCI_SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph Logic/<br>Mem Bus<br>Clock Range<br>(MHz) | CPU Clock<br>Range<br>(MHz) | PCI-to-Mem<br>(Mem VCO) | Mem-to-CPU<br>(CPU VCO) |  |

| 0                | 00000                             | 25–35 <sup>5</sup>                                              | 75–105                                           | 188–263                     | 3 (2)                   | 2.5 (2)                 |  |

| 1                | 00001 25–29 <sup>5</sup>          |                                                                 | 75–88                                            | 225–264                     | 3 (2)                   | 3 (2)                   |  |

| 2                | 00010                             | 50 <sup>15</sup> –59 <sup>5</sup>                               | 50–59                                            | 225–266                     | 1 (4)                   | 4.5 (2)                 |  |

| 3                | 00011 <sup>12</sup>               | 50 <sup>14</sup> –66 <sup>1</sup>                               | 50–66                                            | 100–133                     | 1 (Bypass)              | 2 (4)                   |  |

| 4                | 00100                             | 25–44 <sup>4</sup>                                              | 50–88                                            | 100–176                     | 2 (4)                   | 2 (4)                   |  |

Table 18. PLL Configurations (266-MHz Parts)

| Ref <sup>2</sup> | PLL_<br>CFG[0:4] <sup>10,11</sup> | 266-MHz Part <sup>9</sup>                                       |                                                  |                             | Multipliers             |                         |

|------------------|-----------------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------|-------------------------|

|                  |                                   | PCI Clock Input<br>(PCI_SYNC_IN)<br>Range <sup>1</sup><br>(MHz) | Periph Logic/<br>Mem Bus<br>Clock Range<br>(MHz) | CPU Clock<br>Range<br>(MHz) | PCI-to-Mem<br>(Mem VCO) | Mem-to-CPU<br>(CPU VCO) |

| 1F               | 11111 <sup>8</sup>                | Not usable                                                      |                                                  |                             | Off                     | Off                     |

Table 18. PLL Configurations (266-MHz Parts) (continued)

#### Notes:

- 1. Limited by maximum PCI input frequency (66 MHz).

- 2. Note the impact of the relevant revisions for modes 7 and 1E.

- 3. Limited by minimum memory VCO frequency (132 MHz).

- 4. Limited due to maximum memory VCO frequency (352 MHz).

- 5. Limited by maximum CPU operating frequency.

- 6. Limited by minimum CPU VCO frequency (300 MHz).

- 7. Limited by maximum CPU VCO frequency (704 MHz).

- 8. In clock off mode, no clocking occurs inside the MPC8241, regardless of the PCI\_SYNC\_IN input.

- 9. Range values are shown rounded down to the nearest whole number (decimal place accuracy removed) for clarity.

- 10.PLL\_CFG[0:4] settings that are not listed are reserved.

- 11.Bits 7-4 of register offset <0xE2> contain the PLL\_CFG[0:4] setting value.

- 12.In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in PLL bypass mode.

- 13.In dual PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal peripheral logic directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI\_SYNC\_IN:Mem) mode operation. In this mode, the OSC\_IN input signal clocks the internal processor directly in 1:1 (OSC\_IN:CPU) mode operation and the processor PLL is disabled. The PCI\_SYNC\_IN and OSC\_IN input clocks must be externally synchronized. This mode is intended for hardware modeling. The AC timing specifications in this document do not apply in dual PLL bypass mode.

- 14.Limited by minimum CPU operating frequency (100 MHz).

- 15.Limited by minimum memory bus frequency (50 MHz).

# 7 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8241.

## 7.1 PLL Power Supply Filtering

The AV<sub>DD</sub> and AV<sub>DD</sub>2 power signals on the MPC8241 provide power to the peripheral logic/memory bus PLL and the MPC603e processor PLL. To ensure stability of the internal clocks, the power supplied to the AV<sub>DD</sub> and AV<sub>DD</sub>2 input signals should be filtered of any noise in the 500 kHz to 10 MHz resonant frequency range of the PLLs. Two separate circuits similar to the one shown in Figure 26 using surface mount capacitors with minimum effective series inductance (ESL) is recommended for AV<sub>DD</sub> and AV<sub>DD</sub>2 power signal pins. In *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), Dr. Howard Johnson recommends using multiple small capacitors of equal value instead of multiple values.

## 7.6 JTAG Configuration Signals

Boundary scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE 1149.1 specification, but is provided on all processors that implement the PowerPC architecture. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, more reliable power-on reset performance will be obtained if the TRST signal is asserted during power-on reset. Because the JTAG interface is also used for accessing the common on-chip processor (COP) function, simply tying TRST to HRESET is not practical.

The COP function of these processors allows a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port, with additional status monitoring signals. The COP port must independently assert HRESET or TRST to control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 27 allows the COP port to independently assert HRESET or TRST, while ensuring that the target can drive HRESET as well. If the JTAG interface and COP header will not be used, TRST should be tied to HRESET through a 0- $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during power-on. Although Freescale recommends that the COP header be designed into the system as shown in Figure 27, if this is not possible, the isolation resistor will allow future access to TRST in the case where a JTAG interface may need to be wired onto the system in debug situations.

The COP interface has a standard header for connection to the target system, based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). Typically, pin 14 is removed as a connector key.

There is no standardized way to number the COP header shown in Figure 27. Consequently, different emulator vendors number the pins differently. Some pins are numbered top-to-bottom and left-to-right while others use left-to-right then top-to-bottom and still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 27 is common to all known emulators.

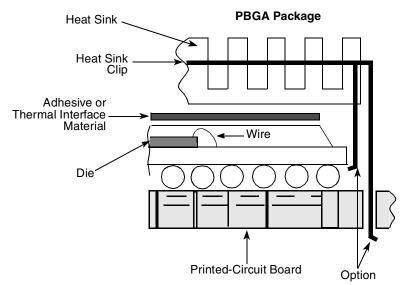

## 7.7 Thermal Management

This section provides thermal management information for the plastic ball grid array (PBGA) package for air-cooled applications. Depending on the application environment and the operating frequency, a heat sink may be required to maintain junction temperature within specifications. Proper thermal control design primarily depends on the system-level design: heat sink, airflow, and thermal interface material. To reduce the die-junction temperature, heat sinks can be attached to the package by several methods: adhesive, spring clip to holes in the printed-circuit board or package, or mounting clip and screw assembly (see Figure 28).

Figure 28. Package Exploded Cross-Sectional View with Several Heat Sink Options

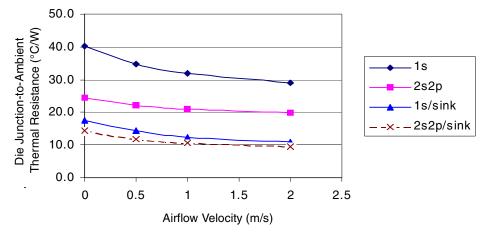

Figure 29 depicts the die junction-to-ambient thermal resistance for four typical cases:

- A heat sink is not attached to the PBGA package and a high board-level thermal loading from adjacent components exists (label used—1s).

- A heat sink is not attached to the PBGA package and a low board-level thermal loading from adjacent components exists (label used—2s2p).

- A large heat sink (cross cut extrusion,  $38 \times 38 \times 16.5$  mm) is attached to the PBGA package and a high board-level thermal loading from adjacent components exists (label used—1s/sink).

- A large heat sink (cross cut extrusion,  $38 \times 38 \times 16.5$  mm) is attached to the PBGA package and a low board-level thermal loading from adjacent components exists (label used—2s2p/sink).

System Design Information

Figure 29. Die Junction-to-Ambient Resistance

The board designer can choose among several types of heat sinks to place on the MPC8241. Several commercially available heat sinks for the MPC8241 are provided by the following vendors:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                               | 603-224-9988 |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #15<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                              | 408-749-7601 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com  | 818-842-7277 |

| Tyco Electronics<br>Chip Coolers <sup>TM</sup><br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com | 800-522-6752 |

| Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                     | 603-635-5102 |

Selection of an appropriate heat sink depends on thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost. Other heat sinks offered by Aavid Thermalloy, Alpha Novatech, IERC, Chip Coolers, and Wakefield Engineering offer different heat sink-to-ambient thermal resistances, and may or may not need airflow.

### 7.7.1 Internal Package Conduction Resistance

For the PBGA, die-up, packaging technology, shown in Figure 28, the intrinsic conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-ball thermal resistance

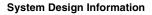

Figure 30 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.

<sup>(</sup>Note the internal versus external package resistance)

#### Figure 30. PBGA Package with Heat Sink Mounted to a Printed-Circuit Board

For this die-up, wire-bond PBGA package, heat generated on the active side of the chip is conducted mainly through the mold cap, the heat sink attach material (or thermal interface material), and finally through the heat sink where forced-air convection removes it.

### 7.7.2 Adhesives and Thermal Interface Materials

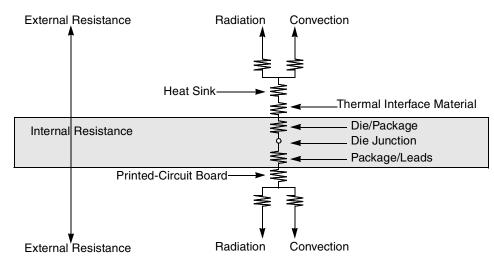

A thermal interface material should be used between the top of the mold cap and the bottom of the heat sink minimizes thermal contact resistance. For applications that attach the heat sink by a spring clip mechanism, Figure 31 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. Thermal grease significantly reduces the interface thermal resistance. That is, the bare joint offers a thermal resistance approximately seven times greater than the thermal grease joint.

A spring clip attaches heat sinks to holes in the printed-circuit board (see Figure 28). Therefore, the synthetic grease offers the best thermal performance, considering the low interface pressure. The selection of any thermal interface material depends on factors such as thermal performance requirements, manufacturability, service temperature, dielectric properties, and cost.

System Design Information

Figure 31. Thermal Performance of Select Thermal Interface Material

The board designer can choose among several types of thermal interface. Heat sink adhesive materials are selected on the basis of high conductivity and adequate mechanical strength to meet equipment shock/vibration requirements. Several commercially-available thermal interfaces and adhesive materials are provided by the following vendors:

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com | 800-347-4572 |

|------------------------------------------------------------------------------------------------------------------------|--------------|

| Chomerics, Inc.                                                                                                        | 781-935-4850 |

| 77 Dragon Ct.                                                                                                          |              |

| Woburn, MA 01888-4014                                                                                                  |              |

| Internet: www.chomerics.com                                                                                            |              |

| Dow-Corning Corporation                                                                                                | 800-248-2481 |

| Dow-Corning Electronic Materials                                                                                       |              |

| 2200 W. Salzburg Rd.                                                                                                   |              |

| Midland, MI 48686-0997                                                                                                 |              |

| Internet: www.dow.com                                                                                                  |              |

MPC8241 Integrated Processor Hardware Specifications, Rev. 10

## 8.1 Part Numbers Fully Addressed by This Document

Table 19 provides the Freescale part numbering nomenclature for the MPC8241. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier that may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number. Read the Revision ID register at address offset 0x08 to determine the revision level.

| MPC             | nnnn               | L                                 | XX                                                                                   | nnn                                          | X                       |

|-----------------|--------------------|-----------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|-------------------------|

| Product<br>Code | Part<br>Identifier | Process Descriptor                | Package <sup>1</sup>                                                                 | Processor<br>Frequency <sup>2</sup><br>(MHz) | Revision<br>Level       |

| MPC             | 8241               | L = Standard spec.<br>0° to 105°C | ZQ = thick substrate and thick<br>mold cap PBGA (two layers)                         | 166, 200<br>1.8 V ± 100 mV                   | D:1.4 = Rev.<br>ID:0x14 |

|                 |                    |                                   | ZQ = thick substrate and thick<br>mold cap PBGA (four layers,<br>thermally enhanced) | 266<br>1.8 V ± 100 mV                        |                         |

|                 |                    |                                   | VR = Lead-free version of package                                                    | 166, 200, 266<br>1.8 V ± 100 mV              |                         |

#### **Table 19. Part Numbering Nomenclature**

#### Notes:

.....

1. See Section 5, "Package Description," for more information on available package types.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by hardware specifications addendums may support other maximum core frequencies.

## 8.2 Part Numbers Not Fully Addressed by This Document

Parts with application modifiers or revision levels not fully addressed in this specification document are described in separate hardware specifications addendums that supplement and supersede this document (see Table 20).

| Table 20. Part Numbers Addressed by MPC8241TXXPNS Series |  |  |  |  |  |

|----------------------------------------------------------|--|--|--|--|--|

| (Document No. MPC8241ECSO1AD))                           |  |  |  |  |  |

| MPC             | nnnn               | т                  | XX                   | nnn                                          | X                 |                                           |

|-----------------|--------------------|--------------------|----------------------|----------------------------------------------|-------------------|-------------------------------------------|

| Product<br>Code | Part<br>Identifier | Process Descriptor | Package <sup>1</sup> | Processor<br>Frequency <sup>2</sup><br>(MHz) | Revision<br>Level | Processor<br>Version<br>Register<br>Value |