Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | 78K/0R                                                                                |

| Core Size                  | 16-Bit                                                                                |

| Speed                      | 20MHz                                                                                 |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                      |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 65                                                                                    |

| Program Memory Size        | 192KB (192K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 10K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                                   |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 80-LQFP                                                                               |

| Supplier Device Package    | -                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f1155agc-gad-ax |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

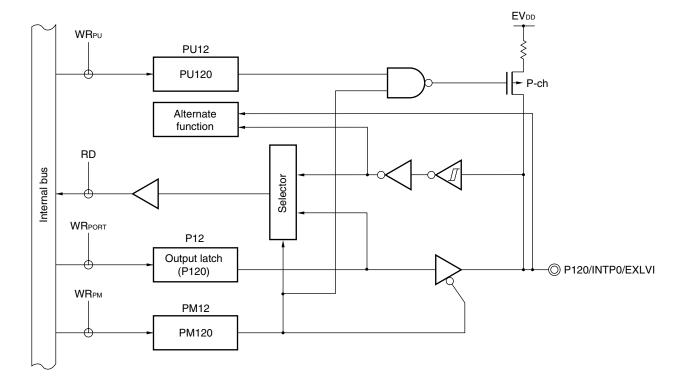

#### 4.2.11 Port 12

P120 is a 1-bit I/O port with an output latch. Port 12 can be set to the input mode or output mode in 1-bit units using port mode register 12 (PM12). When used as an input port, use of an on-chip pull-up resistor can be specified by pull-up resistor option register 12 (PU12).

P121 to P124 are 4-bit input ports.

This port can also be used for external interrupt request input, potential input for external low-voltage detection, connecting resonator for main system clock, connecting resonator for subsystem clock, and external clock input for main system clock.

Reset signal generation sets port 12 to input mode.

Figures 4-29 to 4-31 show block diagrams of port 12.

# Caution The function setting on P121 to P124 is available only once after the reset release. The port once set for connection to an oscillator cannot be used as an input port unless the reset is performed.

Figure 4-29. Block Diagram of P120

- P12: Port register 12

- PU12: Pull-up resistor option register 12

- PM12: Port mode register 12

- RD: Read signal

- WR××: Write signal

# (2) Port registers (P0 to P7, P9, P11 to P14)

These registers write the data that is output from the chip when data is output from a port. If the data is read in the input mode, the pin level is read. If it is read in the output mode, the output latch value is read<sup>Note</sup>.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

**Note** It is always 0 and never a pin level that is read out if a port is read during the input mode when P2 is set to function as an analog input for a A/D converter or P11 is set to function as an analog output for a D/A converter.

| Clock                                     | Condition Before Stopping Clock<br>(Invalidating External Clock Input)                                                                                                          | Setting of CSC<br>Register Flags |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| X1 clock<br>External main system<br>clock | <ul> <li>CLS = 0 and MCS = 0</li> <li>CLS = 1<br/>(CPU and peripheral hardware clocks operate with a clock other than the high-speed system clock.)</li> </ul>                  | MSTOP = 1                        |

| Subsystem clock                           | • CLS = 0<br>(CPU and peripheral hardware clocks operate with a clock<br>other than the subsystem clock.)                                                                       | XTSTOP = 1                       |

| Internal high-speed<br>oscillation clock  | <ul> <li>CLS = 0 and MCS = 1</li> <li>CLS = 1<br/>(CPU and peripheral hardware clocks operate with a clock<br/>other than the internal high-speed oscillator clock.)</li> </ul> | HIOSTOP = 1                      |

| Table 5-2. | Condition | Before | Stopping | Clock | Oscillation | and Flag Setting |  |

|------------|-----------|--------|----------|-------|-------------|------------------|--|

|------------|-----------|--------|----------|-------|-------------|------------------|--|

## (3) Oscillation stabilization time counter status register (OSTC)

This is the register that indicates the count status of the X1 clock oscillation stabilization time counter.

The X1 clock oscillation stabilization time can be checked in the following case,

- If the X1 clock starts oscillation while the internal high-speed oscillation clock or subsystem clock is being used as the CPU clock.

- If the STOP mode is entered and then released while the internal high-speed oscillation clock is being used as the CPU clock with the X1 clock oscillating.

OSTC can be read by a 1-bit or 8-bit memory manipulation instruction. When reset signal is generated, the STOP instruction and MSTOP (bit 7 of CSC register) = 1 clear OSTC to 00H.

**Remark** The oscillation stabilization time counter starts counting in the following cases.

- When oscillation of the X1 clock starts (EXCLK, OSCSEL = 0, 1  $\rightarrow$  MSTOP = 0)

- When the STOP mode is released

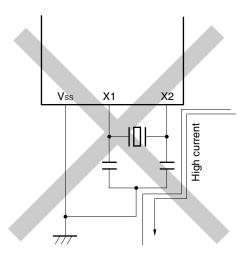

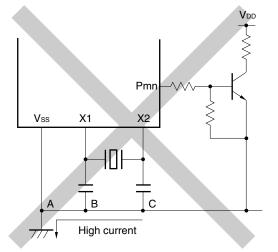

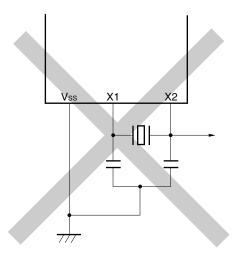

Figure 5-12. Examples of Incorrect Resonator Connection (2/2)

- (c) Wiring near high alternating current

- (d) Current flowing through ground line of oscillator (potential at points A, B, and C fluctuates)

#### (e) Signals are fetched

- **Remark** When using the subsystem clock, replace X1 and X2 with XT1 and XT2, respectively. Also, insert resistors in series on the XT2 side.

- Caution When X2 and XT1 are wired in parallel, the crosstalk noise of X2 may increase with XT1, resulting in malfunctioning.

# 6.2 Configuration of Timer Array Unit

The timer array unit includes the following hardware.

| Table 6-1. Configuration of Timer | Array Unit |

|-----------------------------------|------------|

|-----------------------------------|------------|

| Item              | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer/counter     | Timer counter register 0n (TCR0n)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Register          | Timer data register 0n (TDR0n)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Timer input       | TI00 to TI07 pins, RxD3 pin (for LIN-bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Timer output      | TO00 to TO07 pins, output controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Control registers | <registers block="" of="" setting="" unit=""> <ul> <li>Peripheral enable register 0 (PER0)</li> <li>Timer clock select register 0 (TPS0)</li> <li>Timer channel enable status register 0 (TE0)</li> <li>Timer channel start register 0 (TS0)</li> <li>Timer channel stop register 0 (TT0)</li> <li>Timer input select register 0 (TIS0)</li> <li>Timer output enable register 0 (TOE0)</li> <li>Timer output register 0 (TO0)</li> <li>Timer output level register 0 (TOL0)</li> <li>Timer output mode register 0 (TOM0)</li> </ul></registers> |

|                   | <registers channel="" each="" of=""> <ul> <li>Timer mode register 0n (TMR0n)</li> <li>Timer status register 0n (TSR0n)</li> <li>Input switch control register (ISC) (channel 7 only)</li> <li>Noise filter enable register 1 (NFEN1)</li> <li>Port mode registers 0, 1, 3, 4, 14 (PM0, PM1, PM3, PM4, PM14)</li> <li>Port registers 0, 1, 3, 4, 14 (P0, P1, P3, P4, P14)</li> </ul></registers>                                                                                                                                                 |

**Remark** n: Channel number (n = 0 to 7)

Figure 6-1 shows the block diagram.

|                               | Software Operation                                                                                                                                                                                                                                                    | Hardware Status                                                                                                                                                                                                                                                                                  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                                                                       | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                       |

|                               | Sets the TAU0EN bit of the PER0 register to 1.                                                                                                                                                                                                                        | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                                                                                                                                                          |

|                               | Sets the TPS0 register.<br>Determines clock frequencies of CK00 and CK01.                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                  |

| Channel<br>default<br>setting | Sets the TMR00 register (determines operation mode of channel).<br>Sets interval (period) value to the TDR00 register.                                                                                                                                                | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                      |

|                               | Clears the TOM00 bit of the TOM0 register to 0 (toggle mode).<br>Clears the TOL00 bit to 0.<br>Sets the TO00 bit and determines default level of the                                                                                                                  | The TO00 pin goes into Hi-Z output state.                                                                                                                                                                                                                                                        |

|                               | TO00 output.         Sets TOE00 to 1 and enables operation of TO00.         Clears the port register and port mode register to 0.                                                                                                                                     | <ul> <li>The TO00 default setting level is output when the port mode register is in output mode and the port register is 0.</li> <li>TO00 does not change because channel stops operating.</li> <li>The TO00 pin outputs the TO00 set level.</li> </ul>                                          |

| Operation<br>start            | Sets the TOE00 to 1 (only when operation is resumed).<br>Sets the TS00 bit to 1.<br>The TS00 bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                           | TE00 = 1, and count operation starts.<br>Value of TDR00 is loaded to TCR00 at the count clock<br>input. INTTM00 is generated and TO00 performs toggle<br>operation if the MD000 bit of the TMR00 register is 1.                                                                                  |

| During<br>operation           | Set value of the TDR00 register can be changed.<br>The TCR00 register can always be read.<br>The TSR00 register is not used.<br>Set values of TO0 and TOE0 registers can be changed.<br>Set values of the TMR00 register, TOM00, and TOL00<br>bits cannot be changed. | Counter (TCR00) counts down. When count value reaches<br>0000H, the value of TDR00 is loaded to TCR00 again, and<br>the count operation is continued. By detecting TCR00 =<br>0000H, INTTM00 is generated and TO00 performs toggle<br>operation.<br>After that, the above operation is repeated. |

| Operation<br>stop             | The TT00 bit is set to 1.<br>The TT00 bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                                                                  | <ul> <li>TE00 = 0, and count operation stops.</li> <li>TCR00 holds count value and stops.</li> <li>The TO00 output is not initialized but holds current status</li> </ul>                                                                                                                        |

|                               | TOE00 is cleared to 0 and value is set to the TO00 bit.                                                                                                                                                                                                               | The TO00 pin outputs the TO00 set level.                                                                                                                                                                                                                                                         |

| TAU stop                      | To hold the TO00 pin output level<br>Clears TO00 bit to 0 after the value to<br>be held is set to the port register.<br>When holding the TO00 pin output level is not<br>necessary                                                                                    | The TO00 pin output level is held by port function.                                                                                                                                                                                                                                              |

|                               | Switches the port mode register to input mode.                                                                                                                                                                                                                        | <ul> <li>The TO00 pin output level goes into Hi-Z output state.</li> <li>Power-off status <ul> <li>All circuits are initialized and SFR of each channel is also initialized.</li> <li>(The TO00 bit is cleared to 0 and the TO00 pin is set to port mode).</li> </ul> </li> </ul>                |

Operation is resumed.

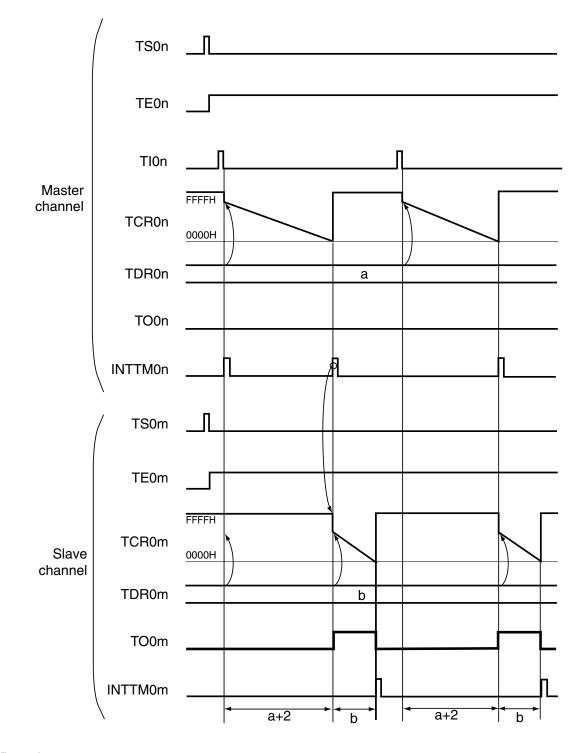

# Figure 6-46. Operation Procedure When Frequency Divider Function Is Used

Figure 6-61. Example of Basic Timing of Operation as One-Shot Pulse Output Function

**Remark** n = 0, 2, 4, 6 m = n + 1

#### Figure 7-4. Format of Real-Time Counter Control Register 1 (RTCC1) (2/2)

| RIFG                                                                                                                                              | Constant-period interrupt status flag       |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 0                                                                                                                                                 | Constant-period interrupt is not generated. |

| 1                                                                                                                                                 | Constant-period interrupt is generated.     |

| This flag indicates the status of generation of the constant-period interrupt. When the constant-period interrupt is generated, it is set to "1". |                                             |

This flag is cleared when "0" is written to it. Writing "1" to it is invalid.

| RWST                                                                                   | Wait status flag of real-time counter |

|----------------------------------------------------------------------------------------|---------------------------------------|

| 0                                                                                      | Counter is operating.                 |

| 1                                                                                      | Mode to read or write counter value   |

| This status flag indicates whether the setting of RWAIT is valid.                      |                                       |

| Before reading or writing the counter value, confirm that the value of this flag is 1. |                                       |

| RWAIT                                                                                                     | Wait control of real-time counter                                                                               |  |  |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| 0                                                                                                         | Sets counter operation.                                                                                         |  |  |

| 1                                                                                                         | Stops SEC to YEAR counters. Mode to read or write counter value                                                 |  |  |

| This bit contro                                                                                           | This bit controls the operation of the counter.                                                                 |  |  |

| Be sure to wr                                                                                             | ite "1" to it to read or write the counter value.                                                               |  |  |

| Because RSL                                                                                               | Because RSUBC continues operation, complete reading or writing of it in 1 second, and clear this bit back to 0. |  |  |

| When RWAIT = 1, it takes up to 1 clock (32.768 kHz) until the counter value can be read or written.       |                                                                                                                 |  |  |

| If RSUBC overflows when RWAIT = 1, it counts up after RWAIT = 0. If the second count register is written, |                                                                                                                 |  |  |

| however, it does not count up because RSUBC is cleared.                                                   |                                                                                                                 |  |  |

- Caution The RIFG and WAFG flags may be cleared when the RTCC1 register is written by using a 1-bit manipulation instruction. Use, therefore, an 8-bit manipulation instruction in order to write to the RTCC1 register. To prevent the RIFG and WAFG flags from being cleared during writing, disable writing by setting "1" to the corresponding bit. When the value may be rewritten because the RIFG and WAFG flags are not being used, the RTCC1 register may be written by using a 1-bit manipulation instruction.

- **Remark** Fixed-cycle interrupts and alarm match interrupts use the same interrupt source (INTRTC). When using these two types of interrupts at the same time, which interrupt occurred can be judged by checking the fixed-cycle interrupt status flag (RIFG) and the alarm detection status flag (WAFG) upon INTRTC occurrence.

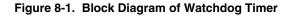

# 8.2 Configuration of Watchdog Timer

The watchdog timer includes the following hardware.

#### Table 8-1. Configuration of Watchdog Timer

| Item             | Configuration                         |

|------------------|---------------------------------------|

| Control register | Watchdog timer enable register (WDTE) |

How the counter operation is controlled, overflow time, window open period, and interval interrupt are set by the option byte.

| Setting of Watchdog Timer                                              | Option Byte (000C0H)            |

|------------------------------------------------------------------------|---------------------------------|

| Watchdog timer interval interrupt                                      | Bit 7 (WDTINT)                  |

| Window open period                                                     | Bits 6 and 5 (WINDOW1, WINDOW0) |

| Controlling counter operation of watchdog timer                        | Bit 4 (WDTON)                   |

| Overflow time of watchdog timer                                        | Bits 3 to 1 (WDCS2 to WDCS0)    |

| Controlling counter operation of watchdog timer<br>(in HALT/STOP mode) | Bit 0 (WDSTBYON)                |

Table 8-2. Setting of Option Bytes and Watchdog Timer

Remark For the option byte, see CHAPTER 23 OPTION BYTE.

Remark fil: Internal low-speed oscillation clock frequency

## 9.2 Configuration of Clock Output/Buzzer Output Controller

The clock output/buzzer output controller includes the following hardware.

### Table 9-1. Configuration of Clock Output/Buzzer Output Controller

| Item              | Configuration                                                                   |

|-------------------|---------------------------------------------------------------------------------|

| Control registers | Clock output select registers 0, 1 (CKS0, CKS1)<br>Port mode register 14 (PM14) |

|                   | Port register 14 (P14)                                                          |

# 9.3 Registers Controlling Clock Output/Buzzer Output Controller

The following two registers are used to control the clock output/buzzer output controller.

- Clock output select registers 0, 1 (CKS0, CSK1)

- Port mode register 14 (PM14)

## (1) Clock output select registers 0, 1 (CKS0, CKS1)

These registers set output enable/disable for clock output or for the buzzer frequency output pin (PCLBUZ0/PCLBUZ1), and set the output clock. Select the clock to be output from PCLBUZ0 by using CKS0.

Select the clock to be output from PCLBUZ1 by using CKS1.

CKS0 and CKS1 are set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

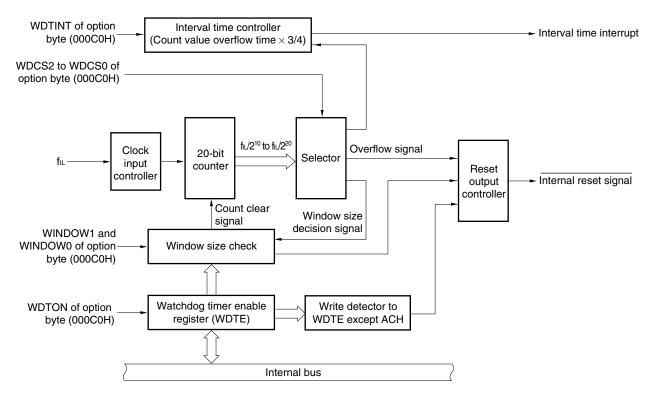

### (9) Interrupt request flag (ADIF)

The interrupt request flag (ADIF) is not cleared even if the analog input channel specification register (ADS) is changed.

Therefore, if an analog input pin is changed during A/D conversion, the A/D conversion result and ADIF for the pre-change analog input may be set just before the ADS rewrite. Caution is therefore required since, at this time, when ADIF is read immediately after the ADS rewrite, ADIF is set despite the fact A/D conversion for the postchange analog input has not ended.

When A/D conversion is stopped and then resumed, clear ADIF before the A/D conversion operation is resumed.

Figure 10-27. Timing of A/D Conversion End Interrupt Request Generation

**Remarks 1.** n = 0 to 7

**2.** m = 0 to 7

## (10) Conversion results just after A/D conversion start

The first A/D conversion value immediately after A/D conversion starts may not fall within the rating range if the ADCS bit is set to 1 within 1 us after the ADCE bit was set to 1. Take measures such as polling the A/D conversion end interrupt request (INTAD) and removing the first conversion result.

### (11) A/D conversion result register (ADCR, ADCRH) read operation

When a write operation is performed to the A/D converter mode register (ADM), analog input channel specification register (ADS), and A/D port configuration register (ADPC), the contents of ADCR and ADCRH may become undefined. Read the conversion result following conversion completion before writing to ADM, ADS, and ADPC. Using a timing other than the above may cause an incorrect conversion result to be read.

#### (1) Peripheral enable register 0 (PER0)

PER0 is used to enable or disable use of each peripheral hardware macro. Clock supply to a hardware macro that is not used is stopped in order to reduce the power consumption and noise. When serial array unit 0 is used, be sure to set bit 2 (SAU0EN) of this register to 1. When serial array unit 1 is used, be sure to set bit 3 (SAU1EN) of this register to 1. PER0 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 12-4. Format of Peripheral Enable Register 0 (PER0)

| Address: F00 | F0H After rea | set: 00H R/V | V     |        |        |        |   |        |

|--------------|---------------|--------------|-------|--------|--------|--------|---|--------|

| Symbol       | <7>           | <6>          | <5>   | <4>    | <3>    | <2>    | 1 | <0>    |

| PER0         | RTCEN         | DACEN        | ADCEN | IIC0EN | SAU1EN | SAU0EN | 0 | TAU0EN |

| SAUmEN | Control of serial array unit m input clock                                                                                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | <ul><li>Stops supply of input clock.</li><li>SFR used by serial array unit m cannot be written.</li><li>Serial array unit m is in the reset status.</li></ul> |

| 1      | Supplies input clock. <ul> <li>SFR used by serial array unit m can be read/written.</li> </ul>                                                                |

- Cautions 1. When setting serial array unit m, be sure to set SAUmEN to 1 first. If SAUmEN = 0, writing to a control register of serial array unit m is ignored, and, even if the register is read, only the default value is read (except for input switch control register (ISC), noise filter enable register (NFEN0), port input mode registers (PIM0, PIM4, PIM14), port output mode registers (POM0, POM4, POM14), port mode registers (PM0, PM1, PM4, PM14), and port registers (P0, P1, P4, P14)).

- 2. After setting the PER0 register to 1, be sure to set the SPSm register after 4 or more clocks have elapsed.

- 3. Be sure to clear bit 1 of PER0 register to 0.

**Remark** m: Unit number (m = 0, 1)

## (2) Serial clock select register m (SPSm)

SPSm is a 16-bit register that is used to select two types of operation clocks (CKm0, CKm1) that are commonly supplied to each channel. CKm1 is selected by bits 7 to 4 of SPSm, and CKm0 is selected by bits 3 to 0.

Rewriting SPSm is prohibited when the register is in operation (when SEmn = 1).

SPSm can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of SPSm can be set with an 8-bit memory manipulation instruction with SPSmL.

Reset signal generation clears this register to 0000H.

## (1) Register setting

<R>

<R>

# Figure 12-32. Example of Contents of Registers for Master Reception of 3-Wire Serial I/O (CSI00, CSI01, CSI10, CSI20)

0.

|                | 15      | 14     | 13       | 12      | 11      | 10           | 9                   | 8                   | 7                         | 6        | 5        | 4                      | 3        | 2         | 1         | 0        |

|----------------|---------|--------|----------|---------|---------|--------------|---------------------|---------------------|---------------------------|----------|----------|------------------------|----------|-----------|-----------|----------|

| SOm            | 0       | 0      | 0        | 0       | 1       | СКОт2<br>0/1 | CKOm1<br><b>0/1</b> | CKOm0<br><b>0/1</b> | 0                         | 0        | 0        | 0                      | 1        | SOm2<br>× | SOm1<br>× | SOr<br>× |

|                |         |        |          |         |         |              |                     |                     | Com                       | munica   | tion sta | rts whe                | en thes  | se bits a | are 1 if  | the c    |

|                |         |        |          |         |         |              |                     |                     | phase                     | e is for | ward (C  | KPmn                   | = 0). I  | f the ph  | nase is   | reve     |

|                |         |        |          |         |         |              |                     |                     | (CKP                      | 'mn = 1  | ), com   | munica                 | tion sta | arts whe  | en thes   | e bit    |

| (b) 5          | Serial  | outpu  | ıt enał  | ble reg | lister  | m (SC        | )Fm)                | The                 | reaist                    | er tha   | t not i  | used i                 | n this   | mode      |           |          |

| (~)            | 15      | 14     | 13       | 12      | 11      | 10           | 9                   | 8                   | 7                         | 6        | 5        | 4                      | 3        | 2         | 1         | 0        |

| SOEm           |         |        |          |         |         |              |                     |                     |                           |          |          |                        |          | SOEm2     | SOEm1     | SOE      |

|                | 0       | 0      | 0        | 0       | 0       | 0            | 0                   | 0                   | 0                         | 0        | 0        | 0                      | 0        | ×         | ×         | ×        |

|                |         |        |          |         |         |              |                     |                     |                           |          |          |                        |          |           |           |          |

| $(\mathbf{a})$ | Sorial  | ohanr  | nol eta  | art reg | ictor i | m (66)       | m)                  | Sate a              | nly th                    | o bito   | of the   | tora                   | ot obo   | nnol t    | o 1       |          |

| (0)            | 15      | 14     | 13       | 12      | 11      | 10           | 9                   | 8                   | 7 7                       | 6        | 5        | 2 taryo<br>4           | 3        | 2         | 1         | 0        |

| SSm            |         |        |          |         |         |              |                     |                     |                           |          |          |                        | SSm3     | SSm2      | SSm1      | SSn      |

|                | 0       | 0      | 0        | 0       | 0       | 0            | 0                   | 0                   | 0                         | 0        | 0        | 0                      | ×        | 0/1       | 0/1       | 0/       |

| (d) :          |         |        | -        | ter mr  | -       | -            |                     |                     |                           |          |          |                        |          |           |           |          |

|                | 15      | 14     | 13       | 12      | 11      | 10           | 9                   | 8                   | 7                         | 6        | 5        | 4                      | 3        | 2         | 1         | 0        |

| MRmn           | CKSmn   |        | _        |         | 0       | _            | 0                   | STSmn               | 0                         | SISmn0   |          | 0                      | 0        | MDmn2     |           | MDm      |

|                | 0/1     | 0      | 0        | 0       | 0       | 0            | 0                   | 0                   | 0                         | 0        | 1        | 0                      | 0        | 0         | 0         | 0/       |

|                |         |        |          |         |         |              |                     |                     |                           |          |          | Interru                | upt sou  | rces of   | chann     | el n     |

|                |         |        |          |         |         |              |                     |                     | 0: Transfer end interrupt |          |          |                        |          |           |           |          |

|                |         |        |          |         |         |              |                     |                     |                           |          |          | 1: Buf                 | fer emp  | oty inter | rrupt     |          |

| (e) (          | Serial  | comn   | nunica   | ation o | nerat   | ion se       | ettina              | reaist              | er mn                     | (SCB     | mn)      |                        |          |           |           |          |

| (0)            | 15      | 14     | 13       | 12      | 11      | 10           | 9                   | 8                   | 7                         | 6        | 5        | 4                      | 3        | 2         | 1         | 0        |

| CRmn           | TXEmn   | RXEmn  | DAPmn    | CKPmn   |         | FOCmn        | PTCmn1              | PTCmn0              | DIBmn                     |          | SLCmn1   | SLCmn0                 |          | DI Smn2   | DLSmn1    | DLSr     |

|                | 0       | 1      | 0/1      | 0/1     | 0       | 0            | 0                   | 0                   | 0/1                       | 0        | 0        | 0                      | 0        | 1         | 1         | 0/       |

|                | <u></u> |        | <u> </u> |         |         |              |                     |                     | J                         |          |          |                        | J        |           |           |          |

|                | Serial  | data r | registe  | er mn   | (SDR    | mn) (le      | ower 8              | B bits:             | SIOp)                     | )        |          |                        |          |           |           |          |

| (f)            |         |        |          | 12      | 11      | 10           | 9                   | 8                   | 7                         | 6        | 5        | 4                      | 3        | 2         | 1         | 0        |

| (f)            | 15      | 14     | 13       | 12      |         |              |                     |                     |                           |          |          |                        |          |           |           |          |

| <b>(f)</b>     | 15      | 14     |          | IZ      |         |              |                     | 0                   |                           |          |          | leceive da<br>e FFH as |          |           |           |          |

Remark

m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2), p: CSI number (p = 00, 01, 10, 20)

□: Setting is fixed in the CSI master reception mode,

: Setting disabled (set to the initial value)

×: Bit that cannot be used in this mode (set to the initial value when not used in any mode)

0/1: Set to 0 or 1 depending on the usage of the user

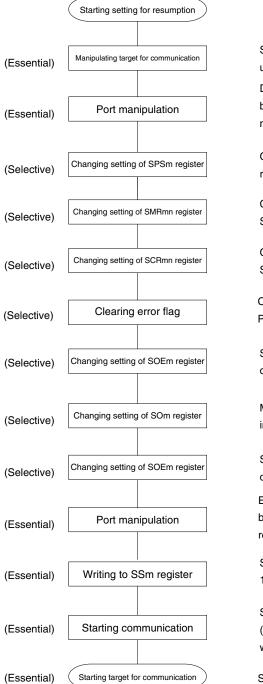

#### Figure 12-65. Procedure for Resuming Slave Transmission/Reception

Stop the target for communication or wait until the target completes its operation.

Disable data output of the target channel by setting a port register and a port mode register.

Change the setting if an incorrect division ratio of the operation clock is set.

Change the setting if the setting of the SMRmn register is incorrect.

Change the setting if the setting of the SCRmn register is incorrect.

Cleared by using SIRmn register if FEF, PEF, or OVF flag remains set.

Set the SOEm register and stop the output of the target channel.

Manipulate the SOmn bit and set an initial output level.

Set the SOEm register and enable the output of the target channel.

Enable data output of the target channel by setting a port register and a port mode register.

Set the SSmn bit of the target channel to 1 to set SEmn = 1.

Set transmit data to the SIOp register (bits 7 to 0 of the SDRmn register) and wait for a clock from the master.

Start the target for communication.

<R> Caution Be sure to set transmit data to the SIOp register before the clock from the master is started.

#### Figure 13-8. Format of IIC Flag Register 0 (IICF0)

| Address: FFF51H After re |      | eset: 00H | R/W <sup>№</sup> | te |   |   |       |        |

|--------------------------|------|-----------|------------------|----|---|---|-------|--------|

| Symbol                   | <7>  | <6>       | 5                | 4  | 3 | 2 | <1>   | <0>    |

| IICF0                    | STCF | IICBSY    | 0                | 0  | 0 | 0 | STCEN | IICRSV |

| STCF      | STT0 clear flag                              |                                                                                                                          |  |  |  |  |

|-----------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0         | Generate start condition                     |                                                                                                                          |  |  |  |  |

| 1         | Start condition generation unsuccessful: cle | ear STT0 flag                                                                                                            |  |  |  |  |

| Condition | n for clearing (STCF = 0)                    | Condition for setting (STCF = 1)                                                                                         |  |  |  |  |

|           | d by STT0 = 1<br>IICE0 = 0 (operation stop)  | • Generating start condition unsuccessful and STT0 cleared to 0 when communication reservation is disabled (IICRSV = 1). |  |  |  |  |

| IICBSY    | l <sup>2</sup> C bus status flag                    |                                                                                           |  |  |  |  |

|-----------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| 0         | Bus release status (communication initial st        | status when STCEN = 1)                                                                    |  |  |  |  |

| 1         | Bus communication status (communication             | on initial status when STCEN = 0)                                                         |  |  |  |  |

| Condition | n for clearing (IICBSY = 0)                         | Condition for setting (IICBSY = 1)                                                        |  |  |  |  |

|           | ion of stop condition<br>IICE0 = 0 (operation stop) | <ul> <li>Detection of start condition</li> <li>Setting of IICE0 when STCEN = 0</li> </ul> |  |  |  |  |

| STCEN     | Initial start enable trigger                                                                                       |                                                                                                                    |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0         | After operation is enabled (IICE0 = 1), enable generation of a start condition upon detection of a stop condition. |                                                                                                                    |  |  |  |  |  |

| 1         | After operation is enabled (IICE0 = 1), enabled a stop condition.                                                  | After operation is enabled (IICE0 = 1), enable generation of a start condition without detecting a stop condition. |  |  |  |  |  |

| Condition | for clearing (STCEN = 0)                                                                                           | Condition for setting (STCEN = 1)                                                                                  |  |  |  |  |  |

|           | d by instruction<br>on of start condition                                                                          | Set by instruction                                                                                                 |  |  |  |  |  |

| IICRSV                                  | Communication reservation function disable bit |                                    |  |  |  |

|-----------------------------------------|------------------------------------------------|------------------------------------|--|--|--|

| 0                                       | Enable communication reservation               |                                    |  |  |  |

| 1                                       | Disable communication reservation              |                                    |  |  |  |

| Condition                               | for clearing (IICRSV = 0)                      | Condition for setting (IICRSV = 1) |  |  |  |

| <ul><li>Cleared</li><li>Reset</li></ul> | d by instruction                               | Set by instruction                 |  |  |  |

Note Bits 6 and 7 are read-only.

Cautions 1. Write to STCEN only when the operation is stopped (IICE0 = 0).

- 2. As the bus release status (IICBSY = 0) is recognized regardless of the actual bus status when STCEN = 1, when generating the first start condition (STT0 = 1), it is necessary to verify that no third party communications are in progress in order to prevent such communications from being destroyed.

- 3. Write to IICRSV only when the operation is stopped (IICE0 = 0).

Remark STT0: Bit 1 of IIC control register 0 (IICC0) IICE0: Bit 7 of IIC control register 0 (IICC0)

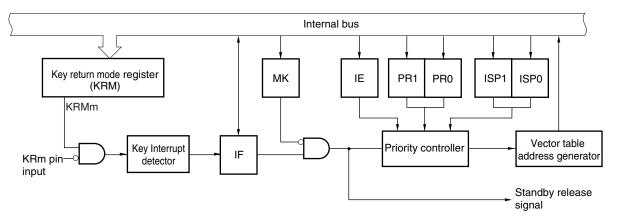

## Figure 16-1. Basic Configuration of Interrupt Function (2/2)

## (C) External maskable interrupt (INTKR)

<R>

(D) Software interrupt

- Remarks 1. IF: Interrupt request flag

- IE: Interrupt enable flag

- ISP0: In-service priority flag 0

- ISP1: In-service priority flag 1

- MK: Interrupt mask flag

- PR0: Priority specification flag 0

- PR1: Priority specification flag 1

**2.** m = 0 to 7

## 21.4 Operation of Low-Voltage Detector

The low-voltage detector can be used in the following two modes.

#### (1) Used as reset (LVIMD = 1)

- If LVISEL = 0, compares the supply voltage (VDD) and detection voltage (VLVI), generates an internal reset signal when VDD < VLVI, and releases internal reset when VDD ≥ VLVI.</li>

- If LVISEL = 1, compares the input voltage from external input pin (EXLVI) and detection voltage (VEXLVI), generates an internal reset signal when EXLVI < VEXLVI, and releases internal reset when EXLVI ≥ VEXLVI.

- **Remark** The low-voltage detector (LVI) can be set to ON by an option byte by default. If it is set to ON to raise the power supply from the POC detection voltage or lower, the internal reset signal is generated when the supply voltage (V<sub>DD</sub>) < detection voltage (V<sub>LVI</sub> = 2.07 V  $\pm$ 0.2 V). After that, the internal reset signal is generated when the supply voltage (V<sub>DD</sub>) < detection voltage (V<sub>LVI</sub> = 2.07 V  $\pm$ 0.2 V).

#### (2) Used as interrupt (LVIMD = 0)

- If LVISEL = 0, compares the supply voltage (VDD) and detection voltage (VLVI). When VDD drops lower than VLVI (VDD < VLVI) or when VDD becomes VLVI or higher (VDD ≥ VLVI), generates an interrupt signal (INTLVI).</li>

- If LVISEL = 1, compares the input voltage from external input pin (EXLVI) and detection voltage (VEXLVI = 1.21 V ±0.1 V). When EXLVI drops lower than VEXLVI (EXLVI < VEXLVI) or when EXLVI becomes VEXLVI or higher (EXLVI ≥ VEXLVI), generates an interrupt signal (INTLVI).</li>

While the low-voltage detector is operating, whether the supply voltage or the input voltage from an external input pin is more than or less than the detection level can be checked by reading the low-voltage detection flag (LVIF: bit 0 of LVIM).

Remark LVIMD: Bit 1 of low-voltage detection register (LVIM) LVISEL: Bit 2 of LVIM

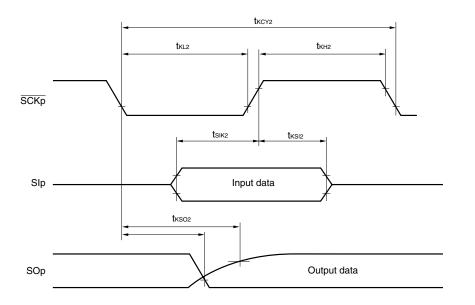

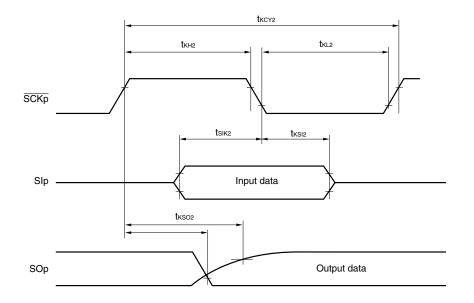

# (2) Serial interface: Serial array unit (2/18)

(TA = -40 to +85°C, 1.8 V  $\leq$  VDD = EVDD  $\leq$  5.5 V, Vss = EVss = AVss = 0 V)

| Parameter                                                               | Symbol        | Conditions                            | MIN.                  | TYP. | MAX. | Unit |

|-------------------------------------------------------------------------|---------------|---------------------------------------|-----------------------|------|------|------|

| SCKp cycle time                                                         | <b>t</b> ксү1 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 200 <sup>Note 1</sup> |      |      | ns   |

|                                                                         |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 300 Note 1            |      |      | ns   |

|                                                                         |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | 600 Note 1            |      |      | ns   |

| SCKp high-/low-level width                                              | tкнı,         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | tксү1/2 – 20          |      |      | ns   |

|                                                                         | tĸ∟1          | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | tксү1/2 – 35          |      |      | ns   |

|                                                                         |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | tkcy1/2 - 80          |      |      | ns   |

| SIp setup time (to $\overline{\text{SCKp}}^{\uparrow})^{\text{Note 2}}$ | tsiki         | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 70                    |      |      | ns   |

|                                                                         |               | $2.7~V \leq V_{\text{DD}} < 4.0~V$    | 100                   |      |      | ns   |

|                                                                         |               | $1.8~V \leq V_{\text{DD}} < 2.7~V$    | 190                   |      |      | ns   |

| SIp hold time (from $\overline{\text{SCKp}}\uparrow)^{\text{Note 3}}$   | tksii         |                                       | 30                    |      |      | ns   |

| Delay time from SCKp↓ to<br>SOp output <sup>Note 4</sup>                | tkso1         | C = 30 pF <sup>Note 5</sup>           |                       |      | 40   | ns   |

#### <R> (b) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output)

**Notes 1.** The value must also be 4/fclk or more.

**2.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to  $\overline{SCKp}\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **3.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from  $\overline{SCKp}\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **4.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from  $\overline{SCKp}$ <sup>↑</sup>" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- **5.** C is the load capacitance of the  $\overline{\text{SCKp}}$  and SOp output lines.

# Caution Select the normal input buffer for SIj and the normal output mode for SOj and SCKj by using the PIMg and POMg registers.

**Remarks 1.** p: CSI number (p = 00, 01, 10, 20), g: PIM and POM number (g = 0, 4, 14),

- j: CSI number for which communication at different potential can be selected (j = 01, 10, 20)

- **2.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2))

(A) Grade Products

#### (2) Serial interface: Serial array unit (16/18)

CSI mode serial transfer timing (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

CSI mode serial transfer timing (during communication at different potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

# Caution Select the TTL input buffer for SIp and SCKp and the N-ch open drain output (VDD tolerance) mode for SOp by using the PIMg and POMg registers.

**Remarks 1.** p: CSI number (p = 01, 10, 20), g: PIM and POM number (g = 0, 4, 14)

- **2.** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 2)

- **3.** CSI00 cannot communicate at different potential. Use CSI01, CSI10, and CSI20 for communication at different potential.

|            |                           |                                           |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (12/3          | 34) |

|------------|---------------------------|-------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|

| Chapter    | Classification            | Function                                  | Details of<br>Function                                                | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pag            | le  |

| Chapter 8  | Watchdog Setting of timer |                                           |                                                                       | The watchdog timer continues its operation during self-programming of the flash memory and EEPROM emulation. During processing, the interrupt acknowledge time is delayed. Set the overflow time and window size taking this delay into consideration.                                                                                                                                                                                                                                                                                                                                      | -              |     |

|            |                           |                                           | Setting window<br>open period                                         | When data is written to WDTE for the first time after reset release, the watchdog timer is cleared in any timing regardless of the window open time, as long as the register is written before the overflow time, and the watchdog timer starts counting again.                                                                                                                                                                                                                                                                                                                             | p.306          |     |

|            |                           |                                           |                                                                       | The watchdog timer continues its operation during self-programming of the flash memory and EEPROM emulation. During processing, the interrupt acknowledge time is delayed. Set the overflow time and window size taking this delay into consideration.                                                                                                                                                                                                                                                                                                                                      | p.306          |     |

|            |                           |                                           |                                                                       | When bit 0 (WDSTBYON) of the option byte (000C0H) = 0, the window open period is 100% regardless of the values of WINDOW1 and WINDOW0.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p.306          |     |

|            |                           |                                           |                                                                       | <ul> <li>Do not set the window open period to 25% if the watchdog timer corresponds to either of the conditions below.</li> <li>When used at a supply voltage (V<sub>DD</sub>) below 2.7 V.</li> <li>When stopping all main system clocks (internal high-speed oscillation clock, X1 clock, and external main system clock) by use of the STOP mode or software.</li> <li>Low-power consumption mode</li> </ul>                                                                                                                                                                             | p.306          |     |

|            |                           |                                           | Setting interval<br>interrupt                                         | When operating with the X1 oscillation clock after releasing the STOP mode, the CPU starts operating after the oscillation stabilization time has elapsed.<br>Therefore, if the period between the STOP mode release and the watchdog timer overflow is short, an overflow occurs during the oscillation stabilization time, causing a reset.<br>Consequently, set the overflow time in consideration of the oscillation stabilization time when operating with the X1 oscillation clock and when the watchdog timer is to be cleared after the STOP mode release by an interval interrupt. |                |     |

| r 9        | Soft                      | Clock                                     | CKS0, CKS1:                                                           | Change the output clock after disabling clock output (PCLOEn = 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | p.310          |     |

| Chapter 9  |                           | output/<br>buzzer<br>output<br>controller | Clock output<br>select registers<br>0, 1                              | If the selected clock (fmain or fsub) stops during clock output (PCLOEn = 1), the output becomes undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | p.310          |     |

| Chapter 10 | Soft                      | A/D<br>converter                          | PER0:<br>Peripheral<br>enable register 0                              | When setting the A/D converter, be sure to set ADCEN to 1 first. If $ADCEN = 0$ , writing to a control register of the A/D converter is ignored, and, even if the register is read, only the default value is read (except for port mode registers 2 (PM2)). Be sure to clear bit 1 of the PER0 register to 0.                                                                                                                                                                                                                                                                              | p.315<br>p.315 |     |

|            |                           |                                           | ADM: A/D<br>converter mode<br>register                                | A/D conversion must be stopped before rewriting bits FR0 to FR2, LV1, and LV0 to values other than the identical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p.316          |     |

|            |                           |                                           | A/D conversion<br>time selection<br>$(2.7 V \le AV_{REF0} \le 5.5 V)$ | Set the conversion times with the following conditions.<br>Conventional-specification products ( $\mu$ PD78F115x)<br>• 4.0 V $\leq$ AV <sub>REF0</sub> $\leq$ 5.5 V: f <sub>AD</sub> = 0.6 to 3.6 MHz<br>• 2.7 V $\leq$ AV <sub>REF0</sub> $<$ 4.0 V: f <sub>AD</sub> = 0.6 to 1.8 MHz<br>Functionally expanded products ( $\mu$ PD78F115xA)<br>• 4.0 V $\leq$ AV <sub>REF0</sub> $\leq$ 5.5 V: f <sub>AD</sub> = 0.33 to 3.6 MHz<br>• 2.7 V $\leq$ AV <sub>REF0</sub> $<$ 4.0 V: f <sub>AD</sub> = 0.33 to 1.8 MHz                                                                         | p.317          |     |