# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

# Details

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z80                                                    |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 6MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | -                                                      |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | -40°C ~ 100°C (TA)                                     |

| Security Features               | -                                                      |

| Package / Case                  | 100-QFP                                                |

| Supplier Device Package         | 100-QFP                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8401506fec |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

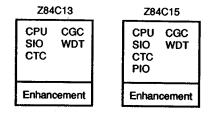

| Z84013                    | Z84015                           |

|---------------------------|----------------------------------|

| CPU CGC<br>SIO WDT<br>CTC | CPU CGC<br>SIO WDT<br>CTC<br>PIO |

Figure 1. Z84013/015 Version

Figure 2. Z84C13/C15 Version

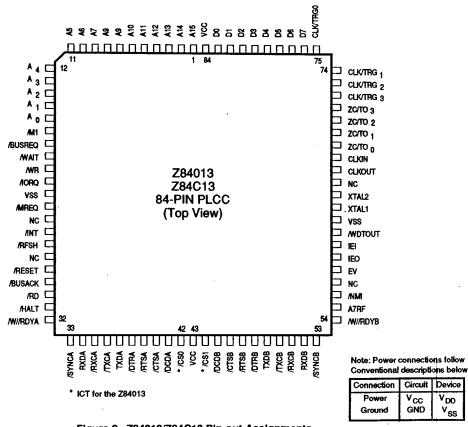

Figure 3. Z84013/Z84C13 Pin-out Assignments

| Pin Name                     | Pin # X13      | Pin # X15      | Function                                                         |

|------------------------------|----------------|----------------|------------------------------------------------------------------|

| /RESET                       | 28             | 9              | Functionality is different.                                      |

| /WAIT                        | 19             | 15             | Functionality is different.                                      |

| EV                           | 58             | 67             | Functionality is different.                                      |

| /WDTOUT                      | 61             | 73             | Push-pull output on Z84013/015, Open drain on Z84 C13/C15        |

| ICT                          | 40, 42         | 42, 40         | (Test pin) on Z84013/015; /CS0 and /CS1 on Z84C13/15.            |

| TxCA, TxCB,<br>RxCA and RxCB | 35, 36, 50, 51 | 33, 34, 48, 49 | On Z84C13/15; these signals have Schmitt-triggered inputs.       |

| /BUSACK                      | 29             | 12             | In EV mode, 3-stated on Z84C13/15; remains active on Z84013/015. |

# The following pins have different functions between 013/015 and C13/C15

#### **FUNCTIONAL DESCRIPTION**

Figure 5(a) shows the functional block diagram of the Z84013/015 and Figure 5(b) shows the functional block diagram of the Z84C13/C15. As described earlier, the only difference between the Z84x13 and the Z84x15 is the PIO not being available on the Z84x13.

Functionally, the on-chip SIO, PIO (not available on Z84x13), CTC, and the Z80 CPU are the same as the discrete devices. Therefore, for detailed description of each individual unit, refer to the Product Specification/Technical Manual of each discrete product.

The following subsections describe each individual functional unit of the IPC.

#### Z84C00/01 Logic Unit

The CPU provides all the capabilities and pins of the Zilog Z80 CPU. This allows 100% software compatibility with existing Z80 software. In addition, it has the pin called "A7RF" to extend DRAM refresh address to 8-bits. Refer to "Z84C01 Z80 CPU with CGC" Product Specification.

### Z84C20 Parallel Input/Output Logic Unit (Z84x15 Only)

This logic unit provides both TTL- and CMOS- compatible interfaces between peripheral devices and a CPU through the use of two 8-bit parallel ports (Figure 6). The CPU configures the logic to interface to a wide range of peripheral devices with no external logic. Typical devices that are compatible with this interface are keyboards, printers, and EPROM/PAL programmers.

The parallel ports (designated Port A and Port B) are byte wide and completely compatible with the Z84C20 PIO.

1

These two ports have several modes of operation; input, output, bi-directional, or bit control mode. Each port has two handshake signals (RDY and /STB) which are used to control data transfers. The RDY (ready) indicates that the port is ready for data transfer while /STB (strobe) is an input to the port that indicates when data transfer has occurred. Each of the ports can be programmed to interrupt the CPU upon the occurrence of specified status conditions, and generate unique interrupt vectors when the CPU responds (for more information on the operation of this portion of the logic, please refer to the Z84C20 PIO Product Specification and Technical Manual).

#### Z84C30 Counter/Timer Logic Unit

This logic unit provides the user with four individual 8-bit Counter/Timer Channels that are compatible with the Z84C30 CTC (Figure 7). The Counter/Timers can be programmed by the CPU for a broad range of counting and timing applications. Typical applications include event counting, interrupt and interval counting, and serial baud rate clock generation.

Each of the Counter/Timer Channels, designated Channels 0-3, have an 8-bit prescaler (when used in timer mode) and its own 8-bit counter to provide a wide range of count resolution. Each of the channels have their own Clock/Trigger input to quantify the counting process and an output to indicate zero crossing/timeout conditions. With only one interrupt vector programmed into the logic unit, each channel can generate a unique interrupt vector in response to the interrupt acknowledge cycle.

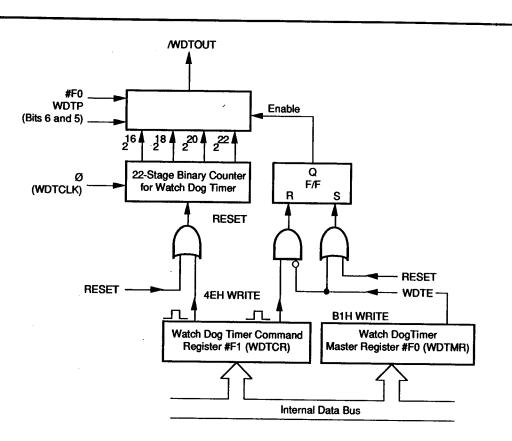

Figure 9. Block Diagram of Watch Dog Timer

**Z84013/015 Only.** If the system clock is provided on the CLKIN pin, none of the power-down mode (except RUN mode) is supported.

**Z84C13/C15 Only.** If the system clock is provided on the CLKIN pin, only the IDLE2 mode is applicable. In this mode, if the HALT instruction is executed, internal clock to the CTC is kept on "Continue", but the clock to the other components (CPU, PIO, SIO and Watch Dog Timer) are stopped. The divide-by-two circuit of the CGC unit can be skipped by programming bit D4 of the WDTMR (see "Programming" section). Upon Power-on Reset, it comes up in divide by two mode.

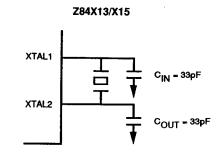

### System Clock Generation

The IPC has a built-in oscillator circuit and the required clock can be easily generated by connecting a crystal to the external terminals (XTAL1, XTAL2). Clock output is the same frequency as half the speed of the crystal frequency. Example of oscillator connections are shown in Figure 10.

**Z84C13/C15.** Clock output is the same, or half, of the external frequency.

#### Figure 10. Circuit Configuration For Crystal

| 1Eh PIO Port B Data Register (N   1Fh PIO Port B Command Register (N   F0h Watch-Dog Timer Master Register   F1h Watch-Dog Timer Control Register   F4h Interrupt Priority Register Control Register   EEh System Control F (Not with Z84013)   EFh Through SCRP and SCDP Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Register                 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| 11hCTCCh 1Control Register12hCTCCh 2Control Register13hCTCCh 3Control Register18hSIOCh. AData Register19hSIOCh. AControl Register18hSIOCh. BData Register18hSIOCh. BData Register18hSIOCh. BData Register18hSIOCh. BData Register18hSIOCh. BData Register18hSIOCh. BControl Register18hSIOCh. BData Register (N19hSIOPort AData Register (N10hPIOPort ACommand Regis11hPIOPort BData Register (N11hPIOPort BData Register (N11hPIOPort BCommand Regis11hPIOPort BControl Register11hWatch-Dog TimerControl Register11hWatch-Dog TimerControl Register11hWatch-Dog TimerControl Register12hInterrupt Priority RegisterSystem Control F<br>(Not with Z84013/015)12hThrough SCRP and SCDPControl Register12hThrough SCRP and SCDPControl Register |                          |  |  |

| 12hCTCCh 2Control Register13hCTCCh 3Control Register18hSIOCh. AData Register19hSIOCh. AControl Register1AhSIOCh. BData Register1BhSIOCh. BData Register (N1DhPIOPort AData Register (N1DhPIOPort ACommand Register (N1DhPIOPort BData Register (N1FhPIOPort BCommand Register (N1FhPIOPort BControl RegisterEEhSystem Control F(Not with Z84013/015)EFhThrough SCRP and SCDPControl RegisterThrough SCRP and SCDPControl Register                                                                                                                                                                  |                          |  |  |

| 13hCTCCh 3Control Register18hSIOCh. AData Register19hSIOCh. AControl Register1AhSIOCh. BData Register1BhSIOCh. BControl Register1ChPIOPort AData Register (N1DhPIOPort ACommand Register (N1DhPIOPort BData Register (N1FhPIOPort BData Register (N1FhPIOPort BCommand Register (N1FhPIOPort BCommand Register (N1FhPIOPort BCommand Register (N1FhPIOPort BControl RegisterEEhSystem Control FControl RegisterEEhSystem Control INaster RegisterEFhThrough SCRP and SCDPControl RegisterThrough SCRP and SCDPControl Register                                                                                                                                                                                                                 |                          |  |  |

| 19h SIO Ch. A Control Register   1Ah SIO Ch. B Data Register   1Bh SIO Ch. B Control Register   1Bh SIO Ch. B Control Register   1Ch PIO Port A Data Register (N   1Dh PIO Port A Command Register (N   1Eh PIO Port B Data Register (N   1Fh PIO Port B Data Register (N   1Fh PIO Port B Command Register (N   F0h Watch-Dog Timer Master Register   F1h Watch-Dog Timer Master Register   F4h Interrupt Priority Register Control Register   EEh System Control F (Not with Z84013)   EFh System Control F System Control F   Through SCRP and SCDP Control Register register (WCR)                                                                                                                                                         |                          |  |  |

| 19h   SIO   Ch. A   Control Register     1Ah   SIO   Ch. B   Data Register     1Bh   SIO   Ch. B   Control Register     1Bh   SIO   Ch. B   Control Register     1Ch   PIO   Port A   Data Register (N     1Dh   PIO   Port A   Command Register (N     1Eh   PIO   Port B   Data Register (N     1Fh   PIO   Port B   Command Register (N     1Fh   PIO   Port B   Command Register (N     FOh   Watch-Dog Timer   Master Register     F1h   Watch-Dog Timer   Control Register     EEh   System Control F   (Not with Z84013)     EFh   System Control F   with Z84013/015     Through SCRP and SCDP   Control Register   register (WCR)     Control Register   Control Register   register (WCR)                                            |                          |  |  |

| 1AhSIOCh. BData Register1BhSIOCh. BControl Register1ChPIOPort AData Register (N1DhPIOPort ACommand Register (N1EhPIOPort BData Register (N1FhPIOPort BCommand Register (N1FhPIOPort BCommand Register (N1FhPIOPort BCommand Register (NFOhWatch-Dog TimerMaster RegisterF1hWatch-Dog TimerControl RegisterF4hInterrupt Priority RegisterSystem Control FEEhSystem Control CSystem Control CEFhThrough SCRP and SCDPControl RegisterThrough SCRP and SCDPControl Register                                                                                                                                                                                                                                                                       |                          |  |  |

| 1Ch PIO Port A Data Register (N   1Dh PIO Port A Command Register (N   1Eh PIO Port B Data Register (N   1Fh PIO Port B Data Register (N   1Fh PIO Port B Command Register (N   FOh Watch-Dog Timer Master Register   F1h Watch-Dog Timer Control Register   F4h Interrupt Priority Register Control Register   EEh System Control F (Not with Z84013/015   EFh Through SCRP and SCDP Control Register                                                                                                                                                                                                                                                                                                                                         |                          |  |  |

| 1Dh   PIO   Port A   Command Regis     1Eh   PIO   Port B   Data Register (N     1Fh   PIO   Port B   Command Regis     F0h   Watch-Dog Timer   Master Register     F1h   Watch-Dog Timer   Control Register     F4h   Interrupt Priority Register   Control Register     EEh   System Control F<br>(Not with Z84013/015)   System Control F<br>with Z84013/015     Through SCRP and SCDP   Control Register                                                                                                                                                                                                                                                                                                                                   |                          |  |  |

| 1Eh PIO Port B Data Register (N   1Fh PIO Port B Command Register (N   F0h Watch-Dog Timer Master Register   F1h Watch-Dog Timer Control Register   F4h Interrupt Priority Register System Control F   EEh System Control F (Not with Z84013)   EFh Through SCRP and SCDP Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ot with Z84x13)          |  |  |

| 1Fh PIO Port B Command Register   F0h Watch-Dog Timer Master Register   F1h Watch-Dog Timer Control Register   F4h Interrupt Priority Register System Control F   EEh System Control F (Not with Z84013)   EFh System Control F with Z84013/015   Through SCRP and SCDP Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ter (Not with Z84x13)    |  |  |

| F0h Watch-Dog Timer Master Register   F1h Watch-Dog Timer Control Register   F4h Interrupt Priority Register System Control F   EEh System Control F (Not with Z84013)   EFh System Control F with Z84013/015   Through SCRP and SCDP Control Register   Through SCRP and SCDP Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                | ot with Z84x13)          |  |  |

| F1h Watch-Dog Timer Control Register   F4h Interrupt Priority Register System Control F   EEh System Control F (Not with Z84013)   EFh System Control I with Z84013/015   Through SCRP and SCDP Control Register   Through SCRP and SCDP Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ter (Not with Z84x13)    |  |  |

| F4h Interrupt Priority Register   EEh System Control F<br>(Not with Z84013)   EFh System Control I<br>with Z84013/015   Through SCRP and SCDP Control Register<br>register (WCR)<br>Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (WDTMR)                  |  |  |

| EEh System Control F<br>(Not with Z84013)<br>EFh System Control I<br>with Z84013/015<br>Through SCRP and SCDP Control Register<br>register (WCR)<br>Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (WDTCR)                  |  |  |

| EFh (Not with Z84013)<br>System Control I<br>with Z84013/015<br>Through SCRP and SCDP Control Register<br>register (WCR)<br>Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |  |  |

| EFh System Control I<br>with Z84013/015<br>Through SCRP and SCDP Control Register<br>register (WCR)<br>Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Register Pointer (SCRP)  |  |  |

| Through SCRP and SCDP Control Register<br>register (WCR)<br>Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |  |  |

| Through SCRP and SCDP Control Register<br>register (WCR)<br>Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Data Port (SCDP) (Not    |  |  |

| register (WCR)<br>Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | )                        |  |  |

| Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00 - Wait State Control  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |  |  |

| Boundary Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01 - Memory Wait state   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | er (MWBR)                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-Chip Select Boundary   |  |  |

| Register (CSBR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |  |  |

| Control Register C<br>(MCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-Misc. Control Register |  |  |

# **PIO REGISTERS**

For more detailed information, please refer to the PIO Technical Manual. These registers are not in the Z84x13.

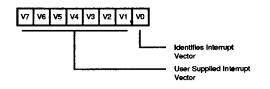

### Interrupt Vector Word

The PIO logic unit is designed to work with the Z80 CPU in interrupt Mode 2. The interrupt word must be programmed if interrupts are used. Bit D0 must be a zero (Figure 11).

Figure 11. PIO Interrupt Vector Word

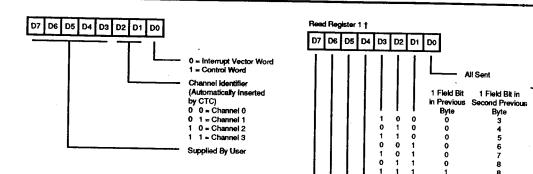

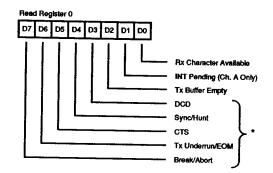

#### SIO REGISTERS

For more detailed information, refer to the SIO Technical Manual.

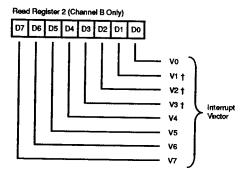

Read Registers. The SIO channel B contains three read registers while channel A contains only two that are read to obtain status information. To read the contents of a register (rather than RR0), the program must first write a pointer to WRO in exactly the same manner as a write operation. The next I/O read cycle will place the contents of the selected read registers onto the data bus (Figure 20a, b, c).

\* Used With "External/Status Interrupt" Modes

0 0

Figure 20b. SIO Read Register 1

2

8

CRC/Framing Error

Parity Error Rx Overrun Error

† Variable if "Status Affects Vector" is programmed

# Figure 20c. SIO Read Register 2

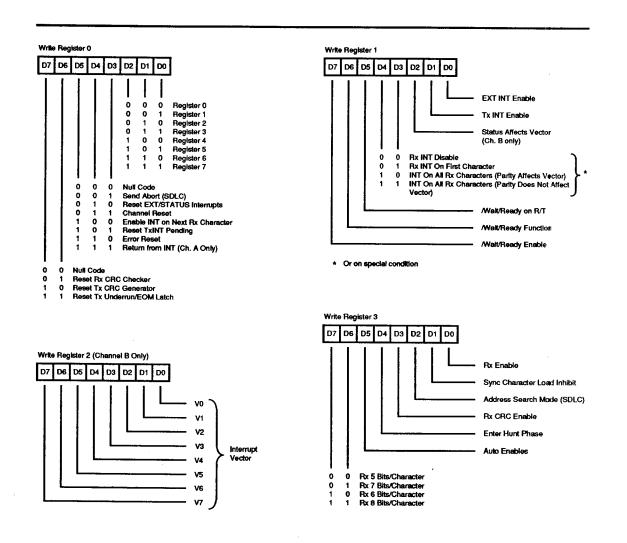

Write Registers. The SIO Channel B contains eight write registers while Channel A contains only seven that are programmed to configure the operating mode characteristics of each channel. With the exception of WRO, programming the write registers is a two step operation. The first operation is a pointer written to WRO which points to the selected register. The second operation is the actual control word that is written into the register to configure the SIO channel (Figure 21).

Figure 21. SIO Write Registers

| Table 3. Device status in Halt state       (When using on-chip CGC unit; CLKOUT and CLKIN are tied together) |     |     |     |    |     |     |        |

|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|-----|-----|--------|

| Mode                                                                                                         | CGC | CPU | стс | PЮ | SIO | WDT | CLKOUT |

| IDLE1                                                                                                        | 0   | Х   | x   | x  | X   | х   | x      |

| IDLE2                                                                                                        | 0   | х   | 0   | х  | х   | X   | 0      |

| STOP                                                                                                         | Х   | Х   | х   | х  | х   | x   | x      |

| RUN                                                                                                          | 0   | 0   | Ο·  | 0  | 0   | Ô   | 0      |

All of the operating modes listed here are valid with crystal input (Crystal connected between XTAL1/2 or external clock input on XTAL1). For the external clock on the CLKIN pin, only the IDLE2 and RUN modes are applicable.

O: Operating X: Stop

# TIMING

#### **Basic Timing**

The basic timing is explained here with emphasis placed on the halt function relative to the clock generator. The following items are identical to those for the Z84C00. Refer to the data sheet for the Z84C00.

- Operation code fetch cycle

- Memory Read/Write operation

- Input/Output operation

- Bus request/acknowledge operation

- Maskable interrupt request operation

- Non-Maskable interrupt request operation

- Reset Operation

**Operation When HALT Instruction is Executed.** When the CPU fetches a halt instruction in the operation code fetch cycle, /HALT goes active (Low) in synch with the falling edge of T4 state before the peripheral LSI and CPU stops the operation. After this, the system clock generation differs depending upon the operation mode (RUN Mode, IDLE 1/2 Mode or STOP Mode). If the internal system clock is running, the CPU continues to execute NOP instruction even in the halt state.

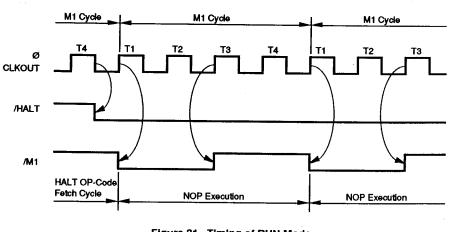

**RUN Mode (HALTM = 11).** Shown in Figure 31 is the basic timing when the halt instruction is executed in RUN Mode.

Figure 31. Timing of RUN Mode (at Halt Instruction Command Execution)

PS018201-0602

In RUN Mode, output from the CGC unit (CLKOUT) is not stopped and the internal system clock (Ø) continues even after the halt instruction is executed. Therefore, until the halt state is released by the interrupt signal (/NMI or /INT)

or /RESET signal, MPU continues to execute HALT instructions (internally executing NOP instructions).

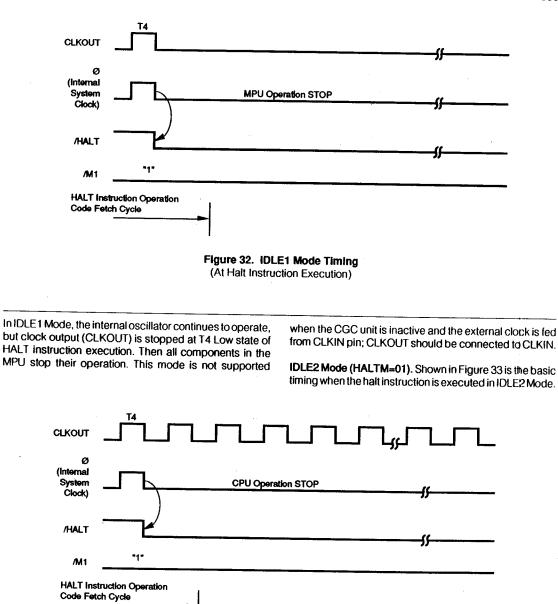

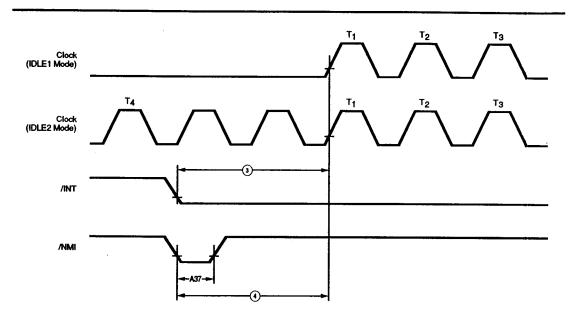

IDLE1 Mode (HALTM=00). Shown in Figure 32 is the basic timing when the halt instruction is executed in IDLE1 Mode.

Figure 33. IDLE2 Mode Timing (At Halt Instruction Execution)

PS018201-0602

323

In IDLE2 Mode, the internal oscillator and clock output (CLKOUT) continue to operate. The internal system clock, fed from CLKIN to the components other than CTC is stopped at the T4 Low state of HALT instruction execution.

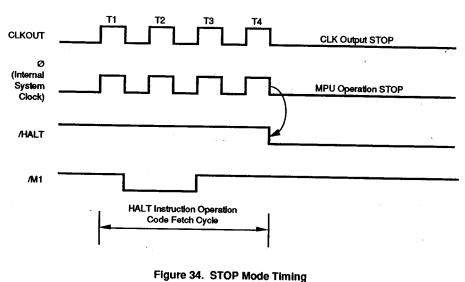

STOP Mode (HALTM=10). Shown in Figure 34 is the basic timing when the halt instruction is executed in STOP Mode.

(At Halt Instruction Execution)

In STOP Mode, the on-chip CGC unit is stopped at T4 Low state of HALT instruction execution. Therefore, clock output (CLKOUT), operation of Watch Dog Timer, CPU, PIO, CTC, SIO are stopped.

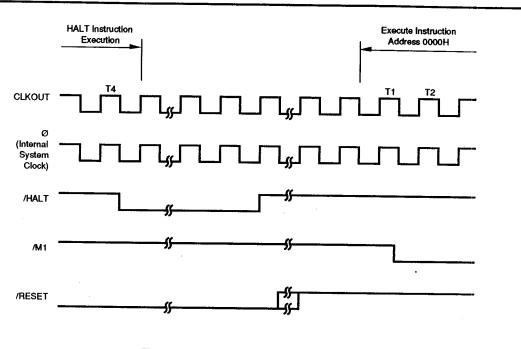

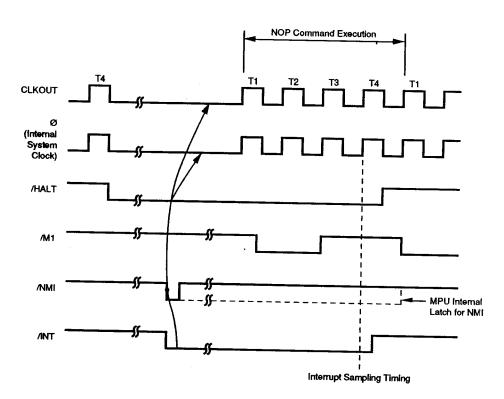

Release from Halt State. The halt state of the CPU is released when "0" is input to the /RESET signal and the MPU is reset or an interrupt request is accepted. An interrupt request signal is sampled at the leading edge of the last clock cycle (T4 state) of NOP instruction. In case of the maskable interrupt, interrupt will be accepted by an active /INT signal ("0" level). Also, the interrupt enable flipflop is set to "1". The accepted interrupt process is started from the next cycle.

Further, when the internal system clock is stopped (IDLE 1/ 2 Mode, STOP Mode), it is necessary first to restart the internal system clock. The internal system clock is restarted when /RESET or interrupt signal (/NMi or /INT) is asserted.

RUN Mode (HALTM=11). The halt release operation is enabled by interrupt request in RUN Mode (Figure 35).

Figure 36. Halt Release Operation Timing By Reset in RUN Mode

IDLE1 Mode (HALTM=00), IDLE2 Mode (HALTM=01). The halt release operation by interrupt signal in IDLE1 Mode is shown in Figure 37 (a) and in IDLE2 Mode in Figure 37 (b).

When /RESET signal at "0" level is input into the IPC, the internal system clock is restarted and the IPC will execute an instruction stored in address 0000H.

At time of /RESET signal input, it is necessary to take the same care as that in resetting the IPC in RUN Mode.

Halt release in STOP Mode (HALTM=10) by interrupt. The halt release operation by interrupt signal in STOP Mode is shown in Figure 39.

Figure 39. Halt Release Operation Timing By Interrupt Request Signal in STOP Mode

When the IPC receives an interrupt signal, the internal oscillator is restarted. To obtain stabilized oscillation, CLKOUT (and the internal system clock) are started after a start-up time of (2<sup>14</sup>+2.5) TcC (TcC: Clock Cycle) by the internal counter.

CPU executes one NOP instruction after the internal system clock is restarted. At the same time, it samples an interrupt signal at the rise of T4 state during the execution of this NOP instruction. If the interrupt signal is accepted, CPU executes the interrupt process operation from the next cycle. During interrupt signal input, it is necessary to take the same care as the interrupt signal input in IDLE1/2 Mode.

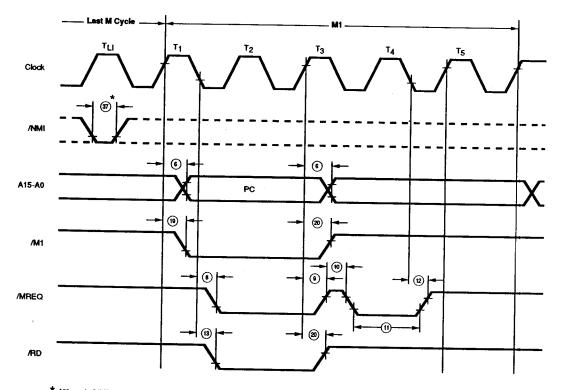

Halt release in STOP Mode (HALTM=10) by /RESET. When /RESET at "0" level is input into the IPC, the internal oscillator is restarted. However, the internal clock counter for warm-up does not operate. Therefore, the operation is not carried out properly due to unstable clock oscillation. It is necessary to hold /RESET at "0" level for sufficient time. The halt release operation by the IPC resetting in STOP Mode is shown in Figure 40. Non-Maskable Interrupt Request Cycle. /NMI is sampled at the same time as the maskable interrupt input /INT, but has higher priority and cannot be disabled under software control. The subsequent timing is similar to that of a normal memory read operation except that data put on the bus by the memory is ignored. The CPU instead executes a restart (RST) operation and jumps to the /NMI service routine located at the address 0066H (Figure 45).

\* Although /NMI is an asynchronous input, to guarantee its being recognized on the following machine cycle, /NMI's falling edge must occur no later than the rising edge of the clock cycle preceding the last state of any instruction cycle ( $T_{\rm L}$ ).

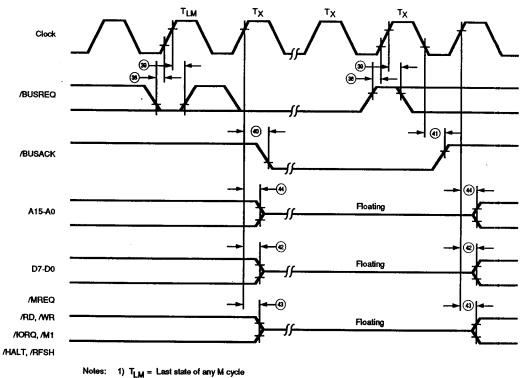

Figure 45. Non-Maskable Interrupt Request Operation (See Table A) Bus Request/Acknowledge Cycle. The CPU samples /BUSREQ with the rising edge of the last clock period of any machine cycle (Figure 46). If /BUSREQ is active, the CPU sets its address, data, and /MREQ to Inputs, and /IORQ, /RD and /WR lines set to an input for on-chip

peripheral access from an external bus master with the rising edge of the next clock pulse. At that time, any external device can take control of these lines, usually to transfer data between memory and I/O devices.

2) T<sub>X</sub> = An arbitrary clock cycle used by requesting device

Figure 46. BUS Request/Acknowledge Cycle (See Table A)

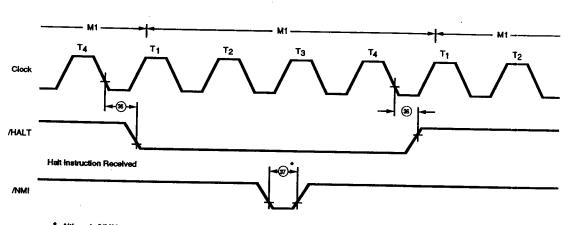

Halt acknowledge cycle. Figure 47 shows the timing for Halt acknowledge cycle.

Although /NMI is an asynchronous input, to guarantee its being recognized on the following machine cycle, /NMI's falling edge must occur no later than the rising edge of the clock preceding the last state of any instruction cycle (TLI).

Figure 47. Halt Acknowledge (See Table A)

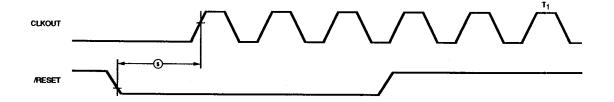

Reset Cycle. /RESET must be active for at least three clock cycles for the CPU to properly accept it. As long as /RESET remains active, the address and data buses float, and the control outputs are inactive.

Once /RESET goes inactive, two internal T cycles are consumed before the CPU resumes normal processing operation. /RESET clears the PC register, so the first op-code fetch location is 0000H (Figure 48).

Z84C13/C15 Only. If Reset output is disabled, /RESET must be active for at least three clock cycles for the CPU to properly accept it. Otherwise, /RESET must be active for at least two clock cycles and the on-chip reset circuit extends /RESET signal to at least a minimum of 16-clock cycles.

.

(a) Clock Restart Timing by /INT, /NMI (IDLE1/2 Mode)

(b) Clock Restart Timing by /RESET (IDLE 1/2 Mode)

Figure 51. Clock Restart Timing (IDLE1/2 Mode) (See Table B)

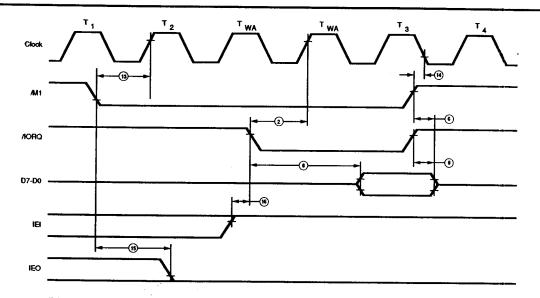

(b) Interrupt Acknowledge Cycle Timing for On-chip peripheral from External Bus master (See Table C)

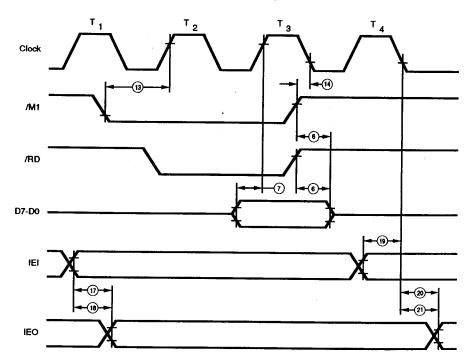

(c) Op-code fetch Cycle Timing for On-chip peripheral from External Bus master (See Table C)

Figure 53. On-chip Peripheral Timing from External Bus master (Continued)

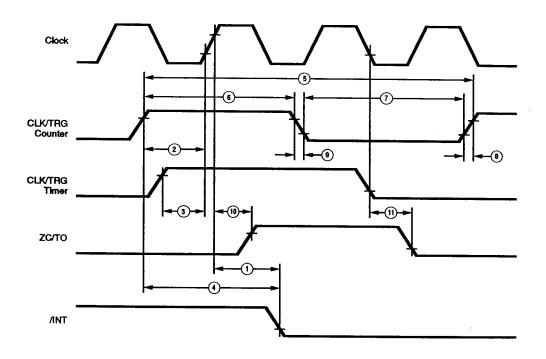

CTC Timing Figure 55 shows the timing for on-chip CTC.

Figure 55. Counter/Timer Timing (See Table E)

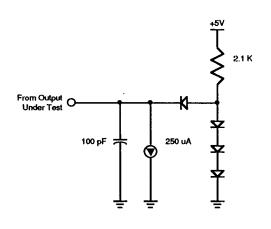

# **STANDARD TEST CONDITIONS**

The DC Characteristics and capacitance sections below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND (0V). Positive current flows into the referenced pin.

Available operating temperature range is:  $E = -40^{\circ}C$  to 100°C Voltage Supply Range:  $+4.50V \le Vcc \le +5.50V$

All AC parameters assume a load capacitance of 100 pf. Add 10 ns delay for each 50 pf increase in load up to a maximum of 150 pf for the data bus and 100 pf for address and control lines. AC timing measurements are referenced to 1.5 volts (except for clock, which is referenced to the 10% and 90% points). Maximum capacitive load for CLK is 125 pf.

The Ordering Information section lists temperature ranges and product numbers. Package drawings are in the Package Information section. Refer to the Literature List for additional documentation.

# CAPACITANCE

Guaranteed by design and characterization

| Symbol             | Parameter          | Min | Max | Unit |

|--------------------|--------------------|-----|-----|------|

| C <sub>olock</sub> | Clock Capacitance  | 35  | pF  |      |

| C <sub>n</sub>     | Input Capacitance  | 5   | pF  |      |

| C <sub>out</sub>   | Output Capacitance | 15  | pF  |      |

**DC CHARACTERISTICS**  $V_{cc}$ =5.0V ± 10%, unless otherwise specified

| Symbol           | Parameter                                                           | Min                     | Max             | Unit | Condition                                 |

|------------------|---------------------------------------------------------------------|-------------------------|-----------------|------|-------------------------------------------|

| Volc             | Clock Output High Voltage                                           | V <sub>cc</sub> -0.6    | ·····           | V    | ~2.0mA                                    |

| V <sub>онс</sub> | Clock Output Low Voltage                                            |                         | 0.4             | V    | +2.0mA                                    |

| V <sub>HC</sub>  | Clock Input High Voltage                                            | V <sub>cc</sub> -0.6    |                 | V    |                                           |

| V                | Clock Input Low Voltage                                             | а.<br>С                 | 0.4             | V    |                                           |

| V <sub>H</sub>   | Input High Voltage                                                  | 2.2                     | V <sub>cc</sub> | V    |                                           |

| V <sub>rL</sub>  | Input Low Voltage                                                   | -0.3                    | 0.8             | V    |                                           |

| V <sub>ol</sub>  | Output Low Voltage                                                  |                         | 0.4 [5]         | V    | l <sub>Lo</sub> =2.0mA                    |

| V <sub>oH1</sub> | Output High Voltage                                                 | 2.4                     |                 | v    | I <sub>он</sub> =-1.6mA                   |

| V <sub>OH2</sub> | Output High Voltage                                                 | V <sub>∞</sub> -0.8 [5] |                 | V    | I <sub>он</sub> =-250µА                   |

| CC1              | Power Supply Current                                                |                         |                 |      | $V_{cc} = 5V$                             |

|                  | XTALIN =10MHz                                                       |                         | 50              | mA   | $V_{H} = V_{cc} - 0.2V$                   |

|                  | XTALIN = 6MHz                                                       |                         | 30              | mA   | V <sub>IL</sub> =0.2V                     |

| I <sub>CC2</sub> | Power Supply Current (STOP Mode)                                    |                         | 50              | μA   | V <sub>cc</sub> =5V                       |

| I <sub>CC3</sub> | Power Supply Current (IDLE1 Mode)                                   |                         |                 | •    | $V_{\infty}^{\alpha}=5V$                  |

|                  | XTALIN =10MHz                                                       |                         | 6               | mA   | $V_{H} = V_{\infty} = 0.2V$               |

|                  | XTALIN = 6MHz                                                       |                         | 4               | mA   | V <mark>⊮</mark> =0.2V                    |

| CC4              | Power Supply Current (IDLE2 Mode)                                   |                         | ······          |      | V <sub>cc</sub> =5V                       |

|                  | XTALIN =10MHz                                                       |                         | TBD [1]         | mΑ   | $V_{H}^{\infty} = V_{\infty} - 0.2V$      |

|                  | XTALIN = 6MHz                                                       |                         | TBD [1]         | mA   | V <b>"</b> "=0.2℃                         |

| Li<br>Li         | Input Leakage Current                                               | -10                     | 10 [4]          | μA   | V <sub>IN</sub> =0.4V to V <sub>cc</sub>  |

| L(SY)            | SYNC pin Leakage Current                                            | -40                     | 10              | μA   | V <sub>our</sub> =0.4V to V <sub>tc</sub> |

| ιο               | 3-state Output Leakage Current in Float<br>Darlington Drive Current | -10                     | 10 [2]          | μA   | $V_{out} = 0.4V$ to $V_{cc}$              |

| онр              | (Port B and CTC ZC/TO)                                              | -1.5                    |                 | mA   | V <sub>oH</sub> =1.5V<br>REXT = 390 Ohm   |

Notes: [1] Measurements made with outputs floating. [2] A15-A0, D7-D0, /MREQ, /IORQ, /RD and /WR. [3] I<sub>ccc</sub> Standby Current is guaranteed when the /HALT pin is low in STOP mode. [4] All Pins except XTALI, where I<sub>u</sub>=±25µA. [5] A15-A0, D7-D0, /MREQ, /IORQ, /RD, /WR, /HALT, /M1 and /BUSACK.

| Table H. Footnote to Table A. |              |                         |                      |                      |                       |  |

|-------------------------------|--------------|-------------------------|----------------------|----------------------|-----------------------|--|

| No                            | Symbol       | Parameter               | Z84X1306<br>Z84X1506 | Z84X1310<br>Z84X1510 | Z84C1316*<br>Z84C1516 |  |

| 1                             | TcC          | TwCh + TwCl + TrC + TfC |                      |                      |                       |  |

| 7                             | TdA(MREQf)   | TwCh + TfC              | -50                  | -50                  | -45                   |  |

| 10                            | TwMREQh      | TwCh + TfC              | -20                  | -20                  | -20                   |  |

| 11                            | TwMREQI      | TcC                     | -30                  | -25                  | -25                   |  |

| 26                            | TdA(IORQf)   | TcC                     | -55                  | -50                  | -50                   |  |

| 29                            | TdD(WRf)     | TcC                     | -140                 | -60                  | -60                   |  |

| 31                            | TwWR         | TcC                     | -30                  | -25                  | -25                   |  |

| 33                            | TdD(WRf)     | TwCl + TrC              | -140                 | -60                  | -60                   |  |

| 35                            | TdWRr(D)     | TwCl + TrC              | -55                  | -40                  | -25                   |  |

| 45                            | TdCTr(A)     | TwCI + TrC              | -50                  | -30                  | -30                   |  |

| 50                            | TdM1f(IORQf) | 2TcC + TwCh + TfC       | -50                  | -30                  | -30                   |  |

.