Welcome to <u>E-XFL.COM</u>

# Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells |                                                                          |

| Total RAM Bits                 | 110592                                                                   |

| Number of I/O                  | 172                                                                      |

| Number of Gates                | 600000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -55°C ~ 100°C (TJ)                                                       |

| Package / Case                 | 484-BGA                                                                  |

| Supplier Device Package        | 484-FPBGA (23x23)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/afs600-1fg484k |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Fusion Device Family Overview

The on-chip crystal and RC oscillators work in conjunction with the integrated phase-locked loops (PLLs) to provide clocking support to the FPGA array and on-chip resources. In addition to supporting typical RTC uses such as watchdog timer, the Fusion RTC can control the on-chip voltage regulator to power down the device (FPGA fabric, flash memory block, and ADC), enabling a low power standby mode.

The Fusion family offers revolutionary features, never before available in an FPGA. The nonvolatile flash technology gives the Fusion solution the advantage of being a secure, low power, single-chip solution that is Instant On. Fusion is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost. These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

# **Flash Advantages**

# Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, high performance, and ease of use. Flashbased Fusion devices are Instant On and do not need to be loaded from an external boot PROM. Onboard security mechanisms prevent access to the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades, with confidence that valuable IP cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm with MAC data authentication on the device. The Fusion family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the Fusion family a cost-effective ASIC replacement solution for applications in the consumer, networking and communications, computing, and avionics markets.

# Security

As the nonvolatile, flash-based Fusion family requires no boot PROM, there is no vulnerable external bitstream. Fusion devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

Fusion devices utilize a 128-bit flash-based key lock and a separate AES key to provide the highest level of protection in the FPGA industry for programmed IP and configuration data. The FlashROM data in Fusion devices can also be encrypted prior to loading. Additionally, the flash memory blocks can be programmed during runtime using the industry-leading AES-128 block cipher encryption standard (FIPS Publication 192). The AES standard was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the DES standard, which was adopted in 1977. Fusion devices have a built-in AES decryption engine and a flash-based AES key that make Fusion devices with AES-based security provide a high level of protection for remote field updates over public networks, such as the Internet, and are designed to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves. As an additional security measure, the FPGA configuration data of a programmed Fusion device cannot be read back, although secure design verification is possible. During design, the user controls and defines both internal and external access to the flash memory blocks.

Security, built into the FPGA fabric, is an inherent component of the Fusion family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. Fusion with FlashLock and AES security is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry-standard security, making remote ISP possible. A Fusion device provides the best available security for programmable logic designs.

# Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based Fusion FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

Fusion Device Family Overview

FPGA logic or an on-chip soft microprocessor can access flash memory through the parallel interface. Since the flash parallel interface is implemented in the FPGA fabric, it can potentially be customized to meet special user requirements. For more information, refer to the *CoreCFI Handbook*. The flash memory parallel interface provides configurable byte-wide (×8), word-wide (×16), or dual-word-wide (×32) data port options. Through the programmable flash parallel interface, the on-chip and off-chip memories can be cascaded for wider or deeper configurations.

The flash memory has built-in security. The user can configure either the entire flash block or the small blocks to prevent unintentional or intrusive attempts to change or destroy the storage contents. Each onchip flash memory block has a dedicated controller, enabling each block to operate independently.

The flash block logic consists of the following sub-blocks:

- Flash block Contains all stored data. The flash block contains 64 sectors and each sector contains 33 pages of data.

- Page Buffer Contains the contents of the current page being modified. A page contains 8 blocks of data.

- Block Buffer Contains the contents of the last block accessed. A block contains 128 data bits.

- ECC Logic The flash memory stores error correction information with each block to perform single-bit error correction and double-bit error detection on all data blocks.

# User Nonvolatile FlashROM

In addition to the flash blocks, Fusion devices have 1 Kbit of user-accessible, nonvolatile FlashROM onchip. The FlashROM is organized as 8×128-bit pages. The FlashROM can be used in diverse system applications:

- Internet protocol addressing (wireless or fixed)

- System calibration settings

- Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- · Version management

The FlashROM is written using the standard IEEE 1532 JTAG programming interface. Pages can be individually programmed (erased and written). On-chip AES decryption can be used selectively over public networks to securely load data such as security keys stored in the FlashROM for a user design.

The FlashROM can be programmed (erased and written) via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing.

The FlashPoint tool in the Fusion development software solutions, Libero SoC and Designer, has extensive support for flash memory blocks and FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using the Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

# SRAM and FIFO

Fusion devices have embedded SRAM blocks along the north and south sides of the device. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be written through a 4-bit port and read as a single bitstream. The SRAM blocks can be initialized from the flash memory blocks or via the device JTAG port (ROM emulation mode), using the UJTAG macro.

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and

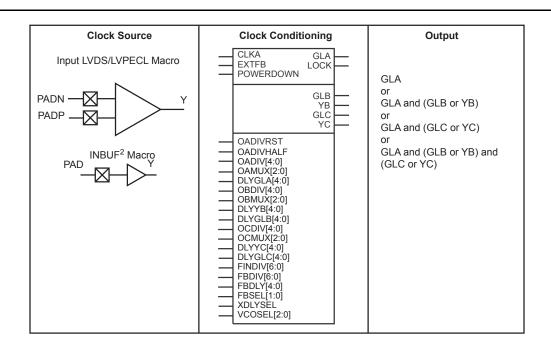

# Clock Conditioning Circuits

In Fusion devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides.

Each CCC can implement up to three independent global buffers (with or without programmable delay), or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output cannot be reused if the YB (or YC) output is used (Figure 2-19). Refer to the "PLL Macro" section on page 2-27 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- · 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- The FPGA core

The CCC block is fully configurable, either via flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the Fusion device to permit changes of parameters (such as divide ratios) during device operation. To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation. This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi's Low-Power Flash Devices" chapter of the *Fusion FPGA Fabric User's Guide* and the "CCC and PLL Characteristics" section on page 2-28 for more information.

#### Notes:

- 1. Visit the Microsemi SoC Products Group website for future application notes concerning dynamic PLL reconfiguration. Refer to the "PLL Macro" section on page 2-27 for signal descriptions.

- 2. Many specific INBUF macros support the wide variety of single-ended and differential I/O standards for the Fusion family.

- 3. Refer to the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide for more information.

#### Figure 2-19 • Fusion CCC Options: Global Buffers with the PLL Macro

#### Table 2-10 • Available Selections of I/O Standards within CLKBUF and CLKBUF\_LVDS/LVPECL Macros

| CLKBUF Macros                |

|------------------------------|

| CLKBUF_LVCMOS5               |

| CLKBUF_LVCMOS33 <sup>1</sup> |

| CLKBUF_LVCMOS18              |

| CLKBUF_LVCMOS15              |

| CLKBUF_PCI                   |

| CLKBUF_LVDS <sup>2</sup>     |

| CLKBUF_LVPECL                |

Notes:

1. This is the default macro. For more details, refer to the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.

2. The B-LVDS and M-LVDS standards are supported with CLKBUF\_LVDS.

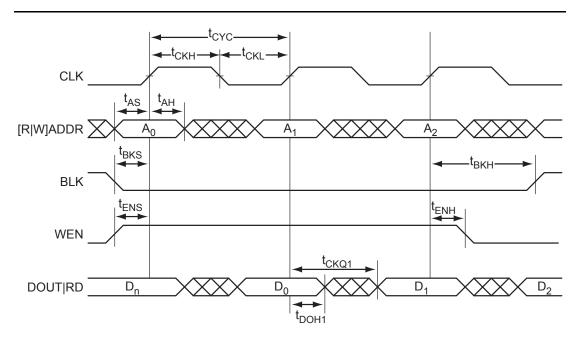

The following signals are used to configure the RAM4K9 memory element:

# WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 2-26).

| WIDTHA1, WIDTHA0 | WIDTHB1, WIDTHB0 | D×W   |

|------------------|------------------|-------|

| 00               | 00               | 4k×1  |

| 01               | 01               | 2k×2  |

| 10               | 10               | 1k×4  |

| 11               | 11               | 512×9 |

# Table 2-26 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

*Note:* The aspect ratio settings are constant and cannot be changed on the fly.

# BLKA and BLKB

These signals are active low and will enable the respective ports when asserted. When a BLKx signal is deasserted, the corresponding port's outputs hold the previous value.

# WENA and WENB

These signals switch the RAM between read and write mode for the respective ports. A Low on these signals indicates a write operation, and a High indicates a read.

# **CLKA and CLKB**

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

# PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A Low on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A High indicates a pipelined, read and data appears on the corresponding output in the next clock cycle.

### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A Low on these signals makes the output retain data from the previous read. A High indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

### RESET

This active low signal resets the output to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 2-27).

# Table 2-27 • Address Pins Unused/Used for Various Supported Bus Widths

|       | ADDRx   |        |  |

|-------|---------|--------|--|

| D×W   | Unused  | Used   |  |

| 4k×1  | None    | [11:0] |  |

| 2k×2  | [11]    | [10:0] |  |

| 1k×4  | [11:10] | [9:0]  |  |

| 512×9 | [11:9]  | [8:0]  |  |

Note: The "x" in ADDRx implies A or B.

# SRAM Characteristics

**Timing Waveforms**

Figure 2-51 • RAM Read for Pipelined Output. Applicable to Both RAM4K9 and RAM512x18.

Device Architecture

| Signal Name     | Number<br>of Bits | Direction | Function                                                     | Location of<br>Details |

|-----------------|-------------------|-----------|--------------------------------------------------------------|------------------------|

| AG6             | 1                 | Output    |                                                              | Analog Quad            |

| AT6             | 1                 | Input     |                                                              | Analog Quad            |

| ATRETURN67      | 1                 | Input     | Temperature monitor return shared by<br>Analog Quads 6 and 7 | Analog Quad            |

| AV7             | 1                 | Input     | Analog Quad 7                                                | Analog Quad            |

| AC7             | 1                 | Input     |                                                              | Analog Quad            |

| AG7             | 1                 | Output    |                                                              | Analog Quad            |

| AT7             | 1                 | Input     |                                                              | Analog Quad            |

| AV8             | 1                 | Input     | Analog Quad 8                                                | Analog Quad            |

| AC8             | 1                 | Input     |                                                              | Analog Quad            |

| AG8             | 1                 | Output    |                                                              | Analog Quad            |

| AT8             | 1                 | Input     |                                                              | Analog Quad            |

| ATRETURN89      | 1                 | Input     | Temperature monitor return shared by<br>Analog Quads 8 and 9 | Analog Quad            |

| AV9             | 1                 | Input     | Analog Quad 9                                                | Analog Quad            |

| AC9             | 1                 | Input     |                                                              | Analog Quad            |

| AG9             | 1                 | Output    |                                                              | Analog Quad            |

| AT9             | 1                 | Input     |                                                              | Analog Quad            |

| RTCMATCH        | 1                 | Output    | МАТСН                                                        | RTC                    |

| RTCPSMMATCH     | 1                 | Output    | MATCH connected to VRPSM                                     | RTC                    |

| RTCXTLMODE[1:0] | 2                 | Output    | Drives XTLOSC RTCMODE[1:0] pins                              | RTC                    |

| RTCXTLSEL       | 1                 | Output    | Drives XTLOSC MODESEL pin                                    | RTC                    |

| RTCCLK          | 1                 | Input     | RTC clock input                                              | RTC                    |

# **Analog Quad**

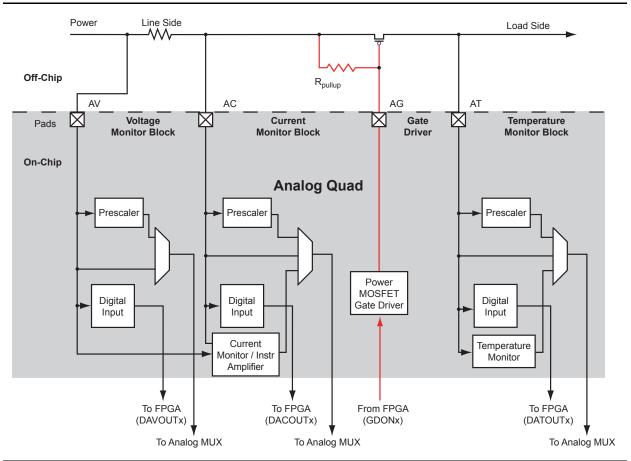

With the Fusion family, Microsemi introduces the Analog Quad, shown in Figure 2-64 on page 2-81, as the basic analog I/O structure. The Analog Quad is a four-channel system used to precondition a set of analog signals before sending it to the ADC for conversion into a digital signal. To maximize the usefulness of the Analog Quad, the analog input signals can also be configured as LVTTL digital input signals. The Analog Quad is divided into four sections.

The first section is called the Voltage Monitor Block, and its input pin is named AV. It contains a twochannel analog multiplexer that allows an incoming analog signal to be routed directly to the ADC or allows the signal to be routed to a prescaler circuit before being sent to the ADC. The prescaler can be configured to accept analog signals between -12 V and 0 or between 0 and +12 V. The prescaler circuit scales the voltage applied to the ADC input pad such that it is compatible with the ADC input voltage range. The AV pin can also be used as a digital input pin.

The second section of the Analog Quad is called the Current Monitor Block. Its input pin is named AC. The Current Monitor Block contains all the same functions as the Voltage Monitor Block with one addition, which is a current monitoring function. A small external current sensing resistor (typically less than 1  $\Omega$ ) is connected between the AV and AC pins and is in series with a power source. The Current Monitor Block contains a current monitor circuit that converts the current through the external resistor to a voltage that can then be read using the ADC.

# Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-73). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-74 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDON*x* pin in the Analog Block macro, where *x* is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{gs} \leq I_g \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ 5

The rate at which the gate voltage of the external MOSFET slews is determined by the current,  $I_g$ , sourced or sunk by the AG pin and the gate-to-source capacitance,  $C_{GS}$ , of the external MOSFET. As an approximation, the slew rate is given by EQ 6.

$$dv/dt = I_g / C_{GS}$$

EQ 6

Device Architecture

| Table 2-39 • | Analog MUX Channels (continued) |

|--------------|---------------------------------|

|--------------|---------------------------------|

| Analog MUX Channel | Signal                       | Analog Quad Number |

|--------------------|------------------------------|--------------------|

| 16                 | AV5                          | Analog Quad 5      |

| 17                 | AC5                          |                    |

| 18                 | AT5                          |                    |

| 19                 | AV6                          | Analog Quad 6      |

| 20                 | AC6                          |                    |

| 21                 | AT6                          |                    |

| 22                 | AV7                          | Analog Quad 7      |

| 23                 | AC7                          |                    |

| 24                 | AT7                          |                    |

| 25                 | AV8                          | Analog Quad 8      |

| 26                 | AC8                          |                    |

| 27                 | AT8                          |                    |

| 28                 | AV9                          | Analog Quad 9      |

| 29                 | AC9                          |                    |

| 30                 | AT9                          |                    |

| 31                 | Internal temperature monitor |                    |

The ADC can be powered down independently of the FPGA core, as an additional control or for powersaving considerations, via the PWRDWN pin of the Analog Block. The PWRDWN pin controls only the comparators in the ADC.

# ADC Modes

The Fusion ADC can be configured to operate in 8-, 10-, or 12-bit modes, power-down after conversion, and dynamic calibration. This is controlled by MODE[3:0], as defined in Table 2-40.

The output of the ADC is the RESULT[11:0] signal. In 8-bit mode, the Most Significant 8 Bits RESULT[11:4] are used as the ADC value and the Least Significant 4 Bits RESULT[3:0] are logical '0's. In 10-bit mode, RESULT[11:2] are used the ADC value and RESULT[1:0] are logical 0s.

| Name | Bits | Function                                                                                          |  |

|------|------|---------------------------------------------------------------------------------------------------|--|

| MODE | 3    | 0 – Internal calibration after every conversion; two ADCCLK cycles are used after the conversion. |  |

|      |      | 1 – No calibration after every conversion                                                         |  |

| MODE | 2    | 0 – Power-down after conversion                                                                   |  |

|      |      | 1 – No Power-down after conversion                                                                |  |

| MODE | 1:0  | 00 – 10-bit                                                                                       |  |

|      |      | 01 – 12-bit                                                                                       |  |

|      |      | 10 – 8-bit                                                                                        |  |

|      |      | 11 – Unused                                                                                       |  |

#### Table 2-40 • Mode Bits Function

# Integrated Voltage Reference

The Fusion device has an integrated on-chip 2.56 V reference voltage for the ADC. The value of this reference voltage was chosen to make the prescaling and postscaling factors for the prescaler blocks change in a binary fashion. However, if desired, an external reference voltage of up to 3.3 V can be

# Table 2-45 • STC Bits Function

| Name | Bits  | Function            |

|------|-------|---------------------|

| STC  | [7:0] | Sample time control |

Sample time is computed based on the period of ADCCLK.

### **Distribution Phase**

The second phase is called the distribution phase. During distribution phase, the ADC computes the equivalent digital value from the value stored in the input capacitor. In this phase, the output signal SAMPLE goes back to '0', indicating the sample is completed; but the BUSY signal remains '1', indicating the ADC is still busy for distribution. The distribution time depends strictly on the number of bits. If the ADC is configured as a 10-bit ADC, then 10 ADCCLK cycles are needed. EQ 8 describes the distribution time.

$$t_{distrib} = N \times t_{ADCCLK}$$

EQ 21

EQ 22

EQ 23

N: Number of bits

### **Post-Calibration Phase**

The last phase is the post-calibration phase. This is an optional phase. The post-calibration phase takes two ADCCLK cycles. The output BUSY signal will remain '1' until the post-calibration phase is completed. If the post-calibration phase is skipped, then the BUSY signal goes to '0' after distribution phase. As soon as BUSY signal goes to '0', the DATAVALID signal goes to '1', indicating the digital result is available on the RESULT output signals. DATAVAILD will remain '1' until the next ADCSTART is asserted. Microsemi recommends enabling post-calibration to compensate for drift and temperature-dependent effects. This ensures that the ADC remains consistent over time and with temperature. The post-calibration phase is enabled by bit 3 of the Mode register. EQ 9 describes the post-calibration time.

$$t_{post-cal} = MODE[3] \times (2 \times t_{ADCCLK})$$

MODE[3]: Bit 3 of the Mode register, described in Table 2-40.

The calculation for the conversion time for the ADC is summarized in EQ 23.

$t_{conv} = t_{sync\_read} + t_{sample} + t_{distrib} + t_{post-cal} + t_{sync\_write}$

#### t<sub>conv</sub>: conversion time

$t_{sync\_read}$ : maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{SYSCLK}$ .

t<sub>sample</sub>: Sample time

t<sub>distrib</sub>: Distribution time

t<sub>post-cal</sub>: Post-calibration time

$t_{sync\_write}$ : Maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{SYSCLK}$ .

### Intra-Conversion

Performing a conversion during power-up calibration is possible but should be avoided, since the performance is not guaranteed, as shown in Table 2-49 on page 2-117. This is described as intraconversion. Figure 2-91 on page 2-112 shows intra-conversion (conversion that starts during power-up calibration).

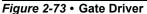

### Injected Conversion

A conversion can be interrupted by another conversion. Before the current conversion is finished, a second conversion can be started by issuing a pulse on signal ADCSTART. When a second conversion is issued before the current conversion is completed, the current conversion would be dropped and the ADC would start the second conversion on the rising edge of the SYSCLK. This is known as injected conversion. Since the ADC is synchronous, the minimum time to issue a second conversion is two clock cycles of SYSCLK after the previous one. Figure 2-92 on page 2-113 shows injected conversion

Extended Temperature Fusion Family of Mixed Signal FPGAs

Note: \* See EQ 23 on page 2-109 for calculation on the conversion time, t<sub>CONV</sub>.

Figure 2-92 • Injected-Conversion Timing Diagram

# **Analog Configuration MUX**

The ACM is the interface between the FPGA, the Analog Block configurations, and the real-time counter. Libero SoC will generate IP that will load and configure the Analog Block via the ACM. However, users are not limited to using the Libero SoC IP. This section provides a detailed description of the ACM's register map, truth tables for proper configuration of the Analog Block and RTC, as well as timing waveforms so users can access and control the ACM directly from their designs.

The Analog Block contains four 8-bit latches per Analog Quad that are initialized through the ACM. These latches act as configuration bits for Analog Quads. The ACM block runs from the core voltage supply (1.5 V).

Access to the ACM is achieved via 8-bit address and data busses with enables. The pin list is provided in Table 2-35 on page 2-78. The ACM clock speed is limited to a maximum of 10 MHz, more than sufficient to handle the low-bandwidth requirements of configuring the Analog Block and the RTC (sub-block of the Analog Block).

Table 2-54 decodes the ACM address space and maps it to the corresponding Analog Quad and configuration byte for that quad.

| ACMADDR [7:0]<br>in Decimal | Name       | Description               | Associated<br>Peripheral |

|-----------------------------|------------|---------------------------|--------------------------|

| 0                           | -          | -                         | Analog Quad              |

| 1                           | AQ0        | Byte 0                    | Analog Quad              |

| 2                           | AQ0        | Byte 1                    | Analog Quad              |

| 3                           | AQ0        | Byte 2                    | Analog Quad              |

| 4                           | AQ0        | Byte 3                    | Analog Quad              |

| 5                           | AQ1        | Byte 0                    | Analog Quad              |

| :                           | :          | :                         | Analog Quad              |

| 36                          | AQ8        | Byte 3                    | Analog Quad              |

| 37                          | AQ9        | Byte 0                    | Analog Quad              |

| 38                          | AQ9        | Byte 1                    | Analog Quad              |

| 39                          | AQ9        | Byte 2                    | Analog Quad              |

| 40                          | AQ9        | Byte 3                    | Analog Quad              |

| 41                          |            | Undefined                 | Analog Quad              |

| :                           | :          | Undefined                 | Analog Quad              |

| 63                          |            | Undefined                 | RTC                      |

| 64                          | COUNTER0   | Counter bits 7:0          | RTC                      |

| 65                          | COUNTER1   | Counter bits 15:8         | RTC                      |

| 66                          | COUNTER2   | Counter bits 23:16        | RTC                      |

| 67                          | COUNTER3   | Counter bits 31:24        | RTC                      |

| 68                          | COUNTER4   | Counter bits 39:32        | RTC                      |

| 72                          | MATCHREG0  | Match register bits 7:0   | RTC                      |

| 73                          | MATCHREG1  | Match register bits 15:8  | RTC                      |

| 74                          | MATCHREG2  | Match register bits 23:16 | RTC                      |

| 75                          | MATCHREG3  | Match register bits 31:24 | RTC                      |

| 76                          | MATCHREG4  | Match register bits 39:32 | RTC                      |

| 80                          | MATCHBITS0 | Individual match bits 7:0 | RTC                      |

Table 2-54 • ACM Address Decode Table for Analog Quad

Device Architecture

**Result: No Bus Contention**

Figure 2-111 • Timing Diagram (with skew circuit selected)

# Weak Pull-Up and Weak Pull-Down Resistors

Fusion devices support optional weak pull-up and pull-down resistors for each I/O pin. When the I/O is pulled up, it is connected to the VCCI of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to Table 2-95 on page 2-171 for more information.

# Slew Rate Control and Drive Strength

Fusion devices support output slew rate control: high and low. The high slew rate option is recommended to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected. Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 2.5 V, 5.0 V input, LVCMOS 1.8 V, and LVCMOS 1.5 V. All other I/O standards have a high output slew rate by default.

For Fusion slew rate and drive strength specifications, refer to the appropriate I/O bank table:

- Fusion Advanced I/O (Table 2-79 on page 2-153)

- Fusion Pro I/O (Table 2-80 on page 2-153)

Table 2-83 on page 2-156 lists the default values for the above selectable I/O attributes as well as those that are preset for each I/O standard.

Device Architecture

# Summary of I/O Timing Characteristics – Default I/O Software Settings

| Table 2-89 • | Summary of AC Measuring Points Applicable to All I/O Bank Types |

|--------------|-----------------------------------------------------------------|

|--------------|-----------------------------------------------------------------|

| Standard                   | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage<br>(VTT_REF) | Measuring Trip Point<br>(Vtrip)         |

|----------------------------|---------------------------------------|----------------------------------------|-----------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | _                                     | -                                      | 1.4 V                                   |

| 2.5 V LVCMOS               | -                                     | -                                      | 1.2 V                                   |

| 1.8 V LVCMOS               | _                                     | -                                      | 0.90 V                                  |

| 1.5 V LVCMOS               | _                                     | -                                      | 0.75 V                                  |

| 3.3 V PCI                  | -                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)) |

| 3.3 V PCI-X                | -                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)  |

| 3.3 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |

| 2.5 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |

| 3.3 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |

| 2.5 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |

| HSTL (I)                   | 0.75 V                                | 0.75 V                                 | VREF                                    |

| HSTL (II)                  | 0.75 V                                | 0.75 V                                 | VREF                                    |

| SSTL2 (I)                  | 1.25 V                                | 1.25 V                                 | VREF                                    |

| SSTL2 (II)                 | 1.25 V                                | 1.25 V                                 | VREF                                    |

| SSTL3 (I)                  | 1.5 V                                 | 1.485 V                                | VREF                                    |

| SSTL3 (II)                 | 1.5 V                                 | 1.485 V                                | VREF                                    |

| LVDS                       | -                                     | -                                      | Cross point                             |

| LVPECL                     | _                                     | -                                      | Cross point                             |

# Table 2-90 • I/O AC Parameter Definitions

| Parameter         | Definition                                                                  |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer with Schmitt trigger disabled    |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>PYS</sub>  | Pad to Data delay through the Input Buffer with Schmitt trigger enabled     |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

|                   |                |                   |                 |                  | -               |                  |                   |                 |                 |                 |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 4 mA              | Std.           | 0.68              | 8.31            | 0.05             | 1.27            | 1.65             | 0.44              | 8.47            | 7.07            | 2.84            | 2.73            | 10.82            | 9.43             | ns    |

|                   | -1             | 0.58              | 7.07            | 0.04             | 1.08            | 1.40             | 0.38              | 7.20            | 6.01            | 2.41            | 2.32            | 9.21             | 8.02             | ns    |

|                   | -2             | 0.51              | 6.21            | 0.03             | 0.95            | 1.23             | 0.33              | 6.32            | 5.28            | 2.12            | 2.04            | 8.08             | 7.04             | S     |

| 8 mA              | Std.           | 0.68              | 5.35            | 0.05             | 1.27            | 1.65             | 0.44              | 5.45            | 4.37            | 3.21            | 3.39            | 7.81             | 6.73             | ns    |

|                   | -1             | 0.58              | 4.55            | 0.04             | 1.08            | 1.40             | 0.38              | 4.64            | 3.72            | 2.73            | 2.88            | 6.64             | 5.72             | ns    |

|                   | -2             | 0.51              | 4.00            | 0.03             | 0.95            | 1.23             | 0.33              | 4.07            | 3.26            | 2.40            | 2.53            | 5.83             | 5.02             | ns    |

| 12 mA             | Std.           | 0.68              | 3.87            | 0.05             | 1.27            | 1.65             | 0.44              | 3.94            | 3.03            | 3.45            | 3.81            | 6.30             | 5.38             | ns    |

|                   | -1             | 0.58              | 3.29            | 0.04             | 1.08            | 1.40             | 0.38              | 3.35            | 2.57            | 2.94            | 3.24            | 5.36             | 4.58             | ns    |

|                   | -2             | 0.51              | 2.89            | 0.03             | 0.95            | 1.23             | 0.33              | 2.94            | 2.26            | 2.58            | 2.85            | 4.70             | 4.02             | ns    |

| 16 mA             | Std.           | 0.68              | 3.65            | 0.05             | 1.27            | 1.65             | 0.44              | 3.72            | 2.75            | 3.51            | 3.93            | 6.08             | 5.11             | ns    |

|                   | -1             | 0.58              | 3.11            | 0.04             | 1.08            | 1.40             | 0.38              | 3.16            | 2.34            | 2.99            | 3.34            | 5.17             | 4.34             | ns    |

|                   | -2             | 0.51              | 2.73            | 0.03             | 0.95            | 1.23             | 0.33              | 2.78            | 2.05            | 2.62            | 2.93            | 4.54             | 3.81             | ns    |

| 24 mA             | Std.           | 0.68              | 3.38            | 0.05             | 1.27            | 1.65             | 0.44              | 3.44            | 2.27            | 3.57            | 4.35            | 5.80             | 4.63             | ns    |

|                   | -1             | 0.58              | 2.88            | 0.04             | 1.08            | 1.40             | 0.38              | 2.93            | 1.93            | 3.04            | 3.70            | 4.94             | 3.94             | ns    |

|                   | -2             | 0.51              | 2.53            | 0.03             | 0.95            | 1.23             | 0.33              | 2.57            | 1.70            | 2.67            | 3.25            | 4.33             | 3.46             | ns    |

Table 2-103 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew, Extended Temperature Case Conditions: T<sub>J</sub> =100°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Pro I/O Banks

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-10.

# 3.3 V PCI, 3.3 V PCI-X

The Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

Table 2-123 • Minimum and Maximum DC Input and Output Levels

| 3.3 V PCI/PCI-X       | VIL       |                | L VIH     |           | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-----------------------|-----------|----------------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength        | Min.<br>V | Max.<br>V      | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| Per PCI specification |           | Per PCI curves |           |           |           |           |     |     | 10                      | 10                      |                  |                  |

Notes:

1.  $I_{IL}$  is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2.  $I_{IH}$  is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

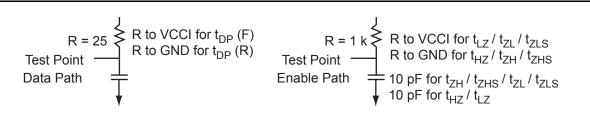

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-121.

# Figure 2-121 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the data path; Microsemi loading for tristate is described in Table 2-124.

#### Table 2-124 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                                                                   | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------------------------------------------------------------------------|-----------------|------------------------|

| 0             | 3.3            | 0.285 * VCC <sub>I</sub> for t <sub>DP(R)</sub><br>0.615 * VCCI for t <sub>DP(E)</sub> | -               | 10                     |

|               |                |                                                                                        |                 |                        |

*Note:* \**Measuring point* = V<sub>trip</sub>. See Table 2-89 on page 2-166 for a complete table of trip points.

# Voltage Referenced I/O Characteristics

# 3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

| 3.3 V GTL          | VIL       |             | L VIH       |           | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>4</sup> | IIH <sup>5</sup> |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA²              | μA²              |

| 20 mA <sup>3</sup> | -0.3      | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | -         | 20  | 20  | 181                     | 268                     | 15               | 15               |

Table 2-127 • Minimum and Maximum DC Input and Output Levels

Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 85°C junction temperature.

- 3. Output drive strength is below JEDEC specification.

- 4.  $I_{II}$  is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL

- 5. *I<sub>IH</sub>* is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

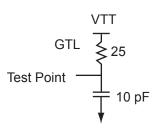

# Figure 2-122 • AC Loading

Table 2-128 • 3.3 V GTL AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | CLOAD (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                  | 0.8             | 1.2            | 10         |

Note: \*Measuring point = Vtrip. See Table 2-80 on page 2-153 for a complete table of trip points.

# Timing Characteristics

Table 2-129 • 3.3 V GTL

Extended Temperature Case Conditions:  $T_J = 100$  °C, Worst Case VCC = 1.425 V, Worst Case VCCI = 3.0 V, VREF = 0.8 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.68              | 2.19            | 0.05             | 3.09            | 0.44              | 2.15            | 2.19            |                 |                 | 4.51             | 4.55             | ns    |

| –1             | 0.58              | 1.86            | 0.04             | 2.63            | 0.38              | 1.83            | 1.86            |                 |                 | 3.83             | 3.87             | ns    |

| -2             | 0.51              | 1.63            | 0.03             | 2.31            | 0.33              | 1.60            | 1.63            |                 |                 | 3.36             | 3.40             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-10.

Extended Temperature Fusion Family of Mixed Signal FPGAs

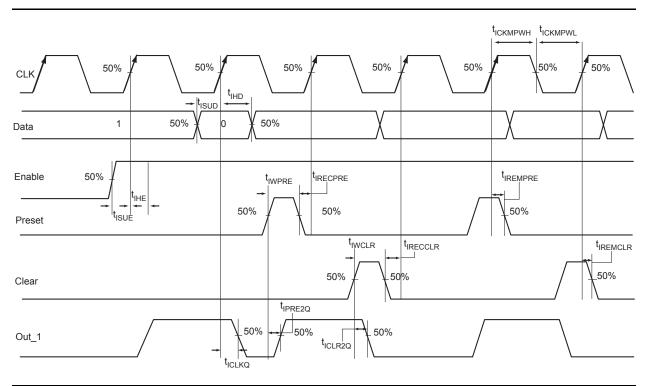

# Figure 2-137 • Input Register Timing Diagram

Input Register

# **Timing Characteristics**

# Table 2-167 • Input Data Register Propagation DelaysExtended Temperature Case Conditions: TJ = 100°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.27 | 0.31 | 0.36 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.38 | 0.44 | 0.51 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.47 | 0.53 | 0.63 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.47 | 0.53 | 0.63 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.23 | 0.26 | 0.31 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.23 | 0.26 | 0.31 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.37 | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-10.

# **Special Function Pins**

## NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

# DC Don't Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

### NCAP Negative Capacitor

Negative Capacitor is where the negative terminal of the charge pump capacitor is connected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

### PCAP Positive Capacitor

*Positive Capacitor* is where the positive terminal of the charge pump capacitor is connected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

# PUB Push Button

*Push button* is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.

#### PTBASE Pass Transistor Base

*Pass Transistor Base* is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

# PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the emitter of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

### XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

# XTAL2 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

Datasheet Information

| Revision                  | Changes                                                                                                                                                                                                                                                                         | Page  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Revision 1<br>(continued) | An incomplete, duplicate sentence was removed from the end of the "GNDAQ Ground (analog quiet)" pin description (SAR 38706).                                                                                                                                                    | 2-222 |

|                           | Information about configuration of unused I/Os was added to the "User Pins" section (SAR 34903).                                                                                                                                                                                | 2-224 |

|                           | The following information was added to the pin description for "XTAL1 Crystal Oscillator Circuit Input" and "XTAL2 Crystal Oscillator Circuit Input" (SAR 34900):                                                                                                               | 2-226 |

|                           | In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.                                                                                                                                 |       |

|                           | The input resistance to ground value in Table 3-3 • Input Resistance of Analog Pads for Analog Input (direct input to ADC), was corrected from 1 M $\Omega$ (typical) to 2 k $\Omega$ (typical) (SAR 38707).                                                                    | 3-5   |

|                           | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Dynamic Contribution—PCLOCK" section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>Fusion FPGA Fabric User's Guide</i> (SAR 34740). | 3-20  |

|                           | Package names used in the "Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 38711).                                                                                                                                    | 4-1   |