Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 276480                                                                       |

| Number of I/O                  | 119                                                                          |

| Number of Gates                | 1500000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -55°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-1fgg256k |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 - Fusion Device Family Overview

## Introduction

The Fusion<sup>®</sup> mixed signal FPGA satisfies the demand from system architects for a device that simplifies design and unleashes their creativity. As the world's first mixed signal programmable logic family, Fusion integrates mixed signal analog, flash memory, and FPGA fabric in a monolithic device. Fusion devices enable designers to quickly move from concept to completed design and then deliver feature-rich systems to market. This new technology takes advantage of the unique properties of Microsemi flash-based FPGAs, including a high-isolation, triple-well process and the ability to support high-voltage transistors to meet the demanding requirements of mixed signal system design.

Fusion mixed signal FPGAs bring the benefits of programmable logic to many application areas, including power management, smart battery charging, clock generation and management, and motor control. Until now, these applications have only been implemented with costly and space-consuming discrete analog components or mixed signal ASIC solutions. Fusion mixed signal FPGAs present new capabilities for system development by allowing designers to integrate a wide range of functionality into a single device, while at the same time offering the flexibility of upgrades late in the manufacturing process or after the device is in the field. Fusion devices provide an excellent alternative to costly and time-consuming mixed signal ASIC designs. In addition, when used in conjunction with the Cortex-M1, Fusion technology represents the definitive mixed signal FPGA platform.

Flash-based Fusion devices are Instant On. As soon as the system power is applied, within normal operating specifications, Fusion devices start working. Fusion devices have a 128-bit flash-based lock and industry-leading AES decryption, used to secure programmed intellectual property (IP) and configuration data. Fusion devices are the most comprehensive single-chip analog and digital programmable logic solution available today.

To support this new ground-breaking technology, Microsemi has developed a series of major tool innovations to help maximize designer productivity. Implemented as extensions to the popular Libero<sup>®</sup> System-on-Chip (SoC), these new tools allow designers to easily instantiate and configure peripherals within a design, establish links between peripherals, create or import building blocks or reference designs, and perform hardware verification. This tool suite will also add comprehensive hardware/software debug capability as well as a suite of utilities to simplify development of embedded soft-processor-based solutions.

## **General Description**

The Fusion family, based on the highly successful ProASIC®3 and ProASIC3E flash FPGA architecture, has been designed as a high-performance, programmable, mixed signal platform. By combining an advanced flash FPGA core with flash memory blocks and analog peripherals, Fusion devices dramatically simplify system design and, as a result, dramatically reduce overall system cost and board space.

The state-of-the-art flash memory technology offers high-density integrated flash memory blocks, enabling savings in cost, power, and board area relative to external flash solutions, while providing increased flexibility and performance. The flash memory blocks and integrated analog peripherals enable true mixed-mode programmable logic designs. Two examples are using an on-chip soft processor to implement a fully functional flash microcontroller (MCU) and using high-speed FPGA logic to offer system and power supervisory capabilities. Instant On and capable of operating from a single 3.3 V supply, the Fusion family is ideally suited for system management and control applications.

The devices in the Fusion family are categorized by FPGA core density. The two family members contain many peripherals, including flash memory blocks, an analog-to-digital-converter (ADC), high-drive outputs, both RC and crystal oscillators, and a real-time counter (RTC). This provides the user with a high level of flexibility and integration to support a wide variety of mixed signal applications. The flash memory block capacity ranges from 4 Mbits to 8 Mbits. The integrated 12-bit ADC supports up to 30 independently configurable input channels.

Revision 2 1-1

## **Clock Conditioning Circuits**

In Fusion devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides.

Each CCC can implement up to three independent global buffers (with or without programmable delay), or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output cannot be reused if the YB (or YC) output is used (Figure 2-19). Refer to the "PLL Macro" section on page 2-27 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- · The FPGA core

The CCC block is fully configurable, either via flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the Fusion device to permit changes of parameters (such as divide ratios) during device operation. To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation. This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi's Low-Power Flash Devices" chapter of the *Fusion FPGA Fabric User's Guide* and the "CCC and PLL Characteristics" section on page 2-28 for more information.

Revision 2 2-21

## **CCC Physical Implementation**

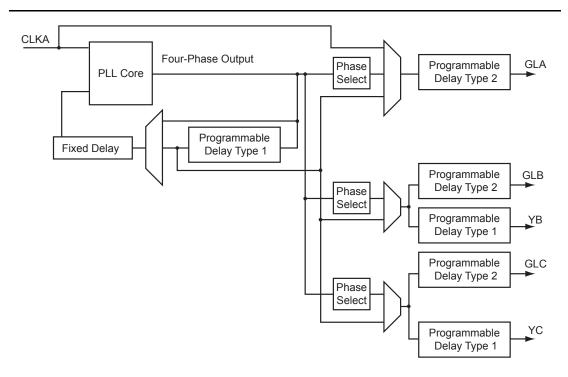

The CCC circuit is composed of the following (Figure 2-23):

- PLL core

- · 3 phase selectors

- · 6 programmable delays and 1 fixed delay

- 5 programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 2-23 because they are automatically configured based on the user's required frequencies)

- 1 dynamic shift register that provides CCC dynamic reconfiguration capability (not shown)

#### **CCC Programming**

The CCC block is fully configurable. It is configured via static flash configuration bits in the array, set by the user in the programming bitstream, or configured through an asynchronous dedicated shift register, dynamically accessible from inside the Fusion device. The dedicated shift register permits changes of parameters such as PLL divide ratios and delays during device operation. This latter mode allows the user to dynamically reconfigure the PLL without the need for core programming. The register file is accessed through a simple serial interface.

Note: Clock divider and multiplier blocks are not shown in this figure or in SmartGen. They are automatically configured based on the user's required frequencies.

Figure 2-23 • PLL Block

2-26 Revision 2

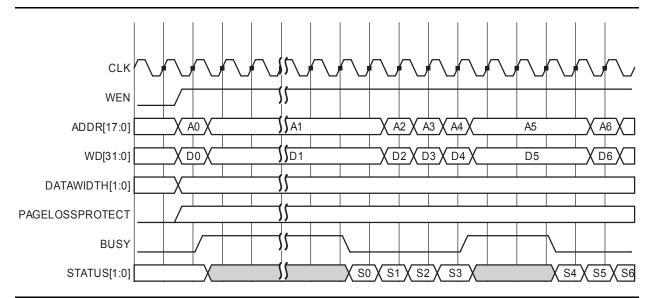

Access to the FB is controlled by the BUSY signal. The BUSY output is synchronous to the CLK signal. FB operations are only accepted in cycles where BUSY is logic 0.

#### Write Operation

Write operations are initiated with the assertion of the WEN signal. Figure 2-35 illustrates the multiple Write operations.

Figure 2-35 • FB Write Waveform

When a Write operation is initiated to a page that is currently not in the Page Buffer, the FB control logic will issue a BUSY signal to the user interface while the page is loaded from the FB Array into the Page Buffer. A Copy Page operation takes no less than 55 cycles and could take more if a Write or Unprotect Page operation is started while the NVM is busy pre-fetching a block. The basic operation is to read a block from the array into the block register (5 cycles) and then write the block register to the page buffer (1 cycle) and if necessary, when the copy is complete, reading the block being written from the page buffer into the block buffer (1 cycle). A page contains 9 blocks, so 9 blocks multiplied by 6 cycles to read/write each block, plus 1 is 55 cycles total. Subsequent writes to the same block of the page will incur no busy cycles. A write to another block in the page will assert BUSY for four cycles (five cycles when PIPE is asserted), to allow the data to be written to the Page Buffer and have the current block loaded into the Block Buffer.

Write operations are considered successful as long as the STATUS output is '00'. A non-zero STATUS indicates that an error was detected during the operation and the write was not performed. Note that the STATUS output is "sticky"; it is unchanged until another operation is started.

Only one word can be written at a time. Write word width is controlled by the DATAWIDTH bus. Users are responsible for keeping track of the contents of the Page Buffer and when to program it to the array. Just like a regular RAM, writing to random addresses is possible. Users can write into the Page Buffer in any order but will incur additional BUSY cycles. It is not necessary to modify the entire Page Buffer before saving it to nonvolatile memory.

Write errors include the following:

- 1. Attempting to write a page that is Overwrite Protected (STATUS = '01'). The write is not performed.

- 2. Attempting to write to a page that is not in the Page Buffer when Page Loss Protection is enabled (STATUS = '11'). The write is not performed.

Revision 2 2-45

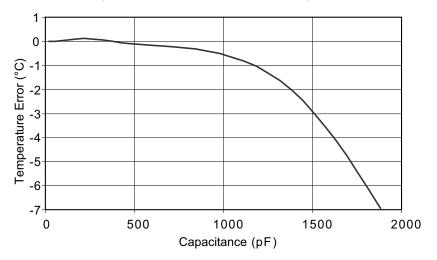

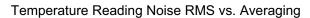

## Temperature Error vs. Interconnect Capacitance

Figure 2-94 • Effect of External Sensor Capacitance

Figure 2-95 • Temperature Reading Noise When Averaging is Used

2-116 Revision 2

Table 2-73 • Maximum I/O Frequency for Single-Ended, Voltage-Referenced, and Differential I/Os; All I/O Bank Types (maximum drive strength and high slew selected)

| Specification      | Performance Up To |

|--------------------|-------------------|

| LVTTL/LVCMOS 3.3 V | 200 MHz           |

| LVCMOS 2.5 V       | 250 MHz           |

| LVCMOS 1.8 V       | 200 MHz           |

| LVCMOS 1.5 V       | 130 MHz           |

| PCI                | 200 MHz           |

| PCI-X              | 200 MHz           |

| HSTL-I             | 300 MHz           |

| HSTL-II            | 300 MHz           |

| SSTL2-I            | 300 MHz           |

| SSTL2-II           | 300 MHz           |

| SSTL3-I            | 300 MHz           |

| SSTL3-II           | 300 MHz           |

| GTL+ 3.3 V         | 300 MHz           |

| GTL+ 2.5 V         | 300 MHz           |

| GTL 3.3 V          | 300 MHz           |

| GTL 2.5 V          | 300 MHz           |

| LVDS               | 350 MHz           |

| LVPECL             | 300 MHz           |

Table 2-74 • Maximum I/O Frequency for Single-Ended and Differential I/Os for Advanced I/Os (maximum drive strength and high slew selected)

| Specification      | Performance Up To |

|--------------------|-------------------|

| LVTTL/LVCMOS 3.3 V | 250 MHz           |

| LVCMOS 2.5 V       | 300 MHz           |

| LVCMOS 1.8 V       | 250 MHz           |

| LVCMOS 1.5 V       | 180 MHz           |

| PCI                | 300 MHz           |

| PCI-X              | 300 MHz           |

| LVDS               | 350 MHz           |

| LVPECL             | 300 MHz           |

2-138 Revision 2

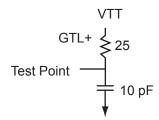

Figure 2-111 • Timing Diagram (with skew circuit selected)

## Weak Pull-Up and Weak Pull-Down Resistors

Fusion devices support optional weak pull-up and pull-down resistors for each I/O pin. When the I/O is pulled up, it is connected to the VCCI of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to Table 2-95 on page 2-171 for more information.

## **Slew Rate Control and Drive Strength**

Fusion devices support output slew rate control: high and low. The high slew rate option is recommended to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected. Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS  $3.3\,V$ , LVCMOS  $2.5\,V$ , LVCMOS  $2.5\,V$ , LVCMOS  $2.5\,V$ ,  $2.5\,V$ , and LVCMOS  $2.5\,V$ , and LVCMOS  $2.5\,V$ . All other I/O standards have a high output slew rate by default.

For Fusion slew rate and drive strength specifications, refer to the appropriate I/O bank table:

- Fusion Advanced I/O (Table 2-79 on page 2-153)

- Fusion Pro I/O (Table 2-80 on page 2-153)

Table 2-83 on page 2-156 lists the default values for the above selectable I/O attributes as well as those that are preset for each I/O standard.

2-152 Revision 2

Table 2-98 • Schmitt Trigger Input Hysteresis, Hysteresis Voltage Value (Typ.) for Schmitt Mode Input Buffers

| Input Buffer Configuration                          | Hysteresis Value (Typ.) |

|-----------------------------------------------------|-------------------------|

| 3.3 V LVTTL/LVCMOS/PCI/PCI-X (Schmitt trigger mode) | 240 mV                  |

| 2.5 V LVCMOS (Schmitt trigger mode)                 | 140 mV                  |

| 1.8 V LVCMOS (Schmitt trigger mode)                 | 80 mV                   |

| 1.5 V LVCMOS (Schmitt trigger mode)                 | 60 mV                   |

#### Table 2-97 • Short Current Event Duration before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| –55°C       | >20 years           |

| -40°C       | >20 years           |

| 0°C         | >20 years           |

| 25°C        | >20 years           |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

Table 2-99 • I/O Input Rise Time, Fall Time, and Related I/O Reliability

| Input Buffer                            | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.)                                                    | Reliability      |

|-----------------------------------------|-----------------------------|--------------------------------------------------------------------------------|------------------|

| LVTTL/LVCMOS (Schmitt trigger disabled) | No requirement              | 10 ns*                                                                         | 20 years (100°C) |

| LVTTL/LVCMOS (Schmitt trigger enabled)  | No requirement              | No requirement, but input<br>noise voltage cannot exceed<br>Schmitt hysteresis | 20 years (100°C) |

| HSTL/SSTL/GTL                           | No requirement              | 10 ns*                                                                         | 10 years (100°C) |

| LVDS/B-LVDS/M-LVDS/LVPECL               | No requirement              | 10 ns*                                                                         | 10 years (100°C) |

Note: \*The maximum input rise/fall time is related only to the noise induced into the input buffer trace. If the noise is low, the rise time and fall time of input buffers, when Schmitt trigger is disabled, can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure there is no excessive noise coupling into input signals.

2-174 Revision 2

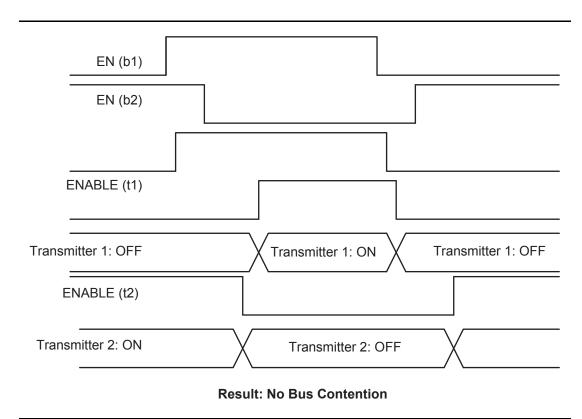

## 3.3 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-133 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL+        | VIL       |            | VIH        |           | V <sub>OL</sub> | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>3</sup> | IIH <sup>4</sup> |

|-------------------|-----------|------------|------------|-----------|-----------------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V       | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>2</sup>  | μA <sup>2</sup>  |

| 35 mA             | -0.3      | VREF - 0.1 | VREF + 0.1 | 3.6       | 0.6             | _         | 35  | 35 | 181                     | 268                     | 15               | 15               |

#### Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 85°C junction temperature.

- 3. I<sub>II</sub> is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 4. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

Figure 2-124 • AC Loading

Table 2-134 • 3.3 V GTL+ AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | CLOAD<br>(pF) |

|---------------|----------------|----------------------|-----------------|----------------|---------------|

| VREF - 0.1    | VREF + 0.1     | 1.0                  | 1.0             | 1.5            | 10            |

Note: \*Measuring point =  $V_{trip}$ . See Table 2-80 on page 2-153 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-135 • 3.3 V GTL+

Extended Temperature Case Conditions:  $T_J$  = 100°C, Worst Case VCC = 1.425 V, Worst Case VCCI = 3.0 V, VREF = 1.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zhs</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.68              | 2.17            | 0.05             | 1.68            | 0.44              | 2.21            | 2.17            |                 |                 | 4.57             | 4.53             | ns    |

| <b>–</b> 1     | 0.58              | 1.84            | 0.04             | 1.43            | 0.38              | 1.88            | 1.84            |                 |                 | 3.88             | 3.85             | ns    |

| -2             | 0.51              | 1.62            | 0.03             | 1.25            | 0.33              | 1.65            | 1.62            |                 |                 | 3.41             | 3.38             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-10.

Revision 2 2-199

## **Output Register**

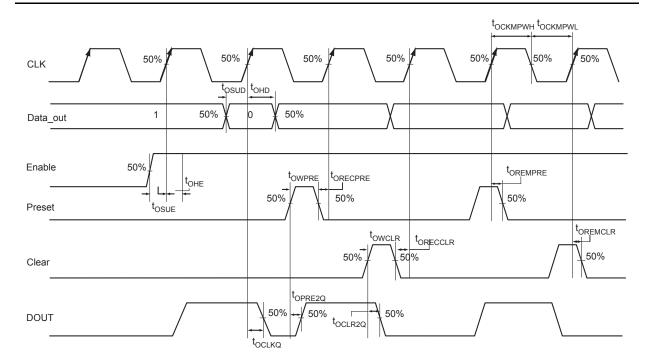

Figure 2-138 • Output Register Timing Diagram

**Timing Characteristics**

Table 2-168 • Output Data Register Propagation Delays

Extended Temperature Case Conditions: T<sub>J</sub> = 100°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -2   | <b>-</b> 1 | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|------------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 0.61 | 0.69       | 0.81 | ns    |

| tosud                | Data Setup Time for the Output Data Register                         | 0.32 | 0.37       | 0.43 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00       | 0.00 | ns    |

| t <sub>OSUE</sub>    | Enable Setup Time for the Output Data Register                       | 0.45 | 0.51       | 0.60 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00       | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.83 | 0.94       | 1.11 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.83 | 0.94       | 1.11 | ns    |

| toremclr             | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00       | 0.00 | ns    |

| torecclr             | Asynchronous Clear Recovery Time for the Output Data Register        | 0.23 | 0.26       | 0.31 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | 0.00       | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.23 | 0.26       | 0.31 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.22 | 0.25       | 0.30 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.22 | 0.25       | 0.30 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.36 | 0.41       | 0.48 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.32 | 0.37       | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-10.

2-216 Revision 2

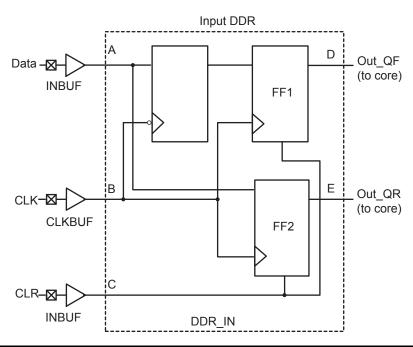

## **DDR Module Specifications**

Input DDR Module

Figure 2-140 • Input DDR Timing Model

Table 2-170 • Parameter Definitions

| Parameter Name          | Parameter Definition         | Measuring Nodes (from, to) |

|-------------------------|------------------------------|----------------------------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR          | B, D                       |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF          | B, E                       |

| t <sub>DDRISUD</sub>    | Data Setup Time of DDR Input | A, B                       |

| t <sub>DDRIHD</sub>     | Data Hold Time of DDR Input  | A, B                       |

| t <sub>DDRICLR2Q1</sub> | Clear-to-Out Out_QR          | C, D                       |

| t <sub>DDRICLR2Q2</sub> | Clear-to-Out Out_QF          | C, E                       |

| t <sub>DDRIREMCLR</sub> | Clear Removal                | C, B                       |

| t <sub>DDRIRECCLR</sub> | Clear Recovery               | C, B                       |

2-218 Revision 2

## **Special Function Pins**

#### NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC Don't Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

#### NCAP Negative Capacitor

Negative Capacitor is where the negative terminal of the charge pump capacitor is connected. A capacitor, with a 2.2 µF recommended value, is required to connect between PCAP and NCAP.

#### PCAP Positive Capacitor

Positive Capacitor is where the positive terminal of the charge pump capacitor is connected. A capacitor, with a 2.2 µF recommended value, is required to connect between PCAP and NCAP.

#### PUB Push Button

*Push button* is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.

#### PTBASE Pass Transistor Base

Pass Transistor Base is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

#### PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the emitter of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

#### XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

#### XTAL2 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

2-226 Revision 2

Table 3-1 • Absolute Maximum Ratings (continued)

| Symbol                        | Parameter                                                    | Limit         | Units |

|-------------------------------|--------------------------------------------------------------|---------------|-------|

| AV                            | Unpowered, ADC reset asserted or unconfigured                | -11.0 to 12.0 | V     |

|                               | Analog input (+16 V to +2 V prescaler range)                 | -0.4 to 12.0  | V     |

|                               | Analog input (+1 V to +0.125 V prescaler range)              | -0.4 to 3.75  | V     |

|                               | Analog input (–16 V to –2 V prescaler range) <sup>5</sup>    | -11.0 to 0.4  | V     |

|                               | Analog input (–1 V to –0.125 V prescaler range) <sup>5</sup> | -3.75 to 0.4  | V     |

|                               | Analog input (direct input to ADC)                           | -0.4 to 3.75  | V     |

|                               | Analog input (positive current monitor) <sup>6</sup>         | -0.4 to 12.0  | V     |

|                               | Analog input (negative current monitor) <sup>5</sup>         | -11.0 to 0.4  | V     |

|                               | Digital input                                                | -0.4 to 12.0  | V     |

| AC                            | Unpowered, ADC reset asserted or unconfigured                | -11.0 to 12.0 | V     |

|                               | Analog input (+16 V to +2 V prescaler range)                 | -0.4 to 12.0  | V     |

|                               | Analog input (+1 V to +0.125 V prescaler range)              | -0.4 to 3.75  | V     |

|                               | Analog input (–16 V to –2 V prescaler range) <sup>5</sup>    | -11.0 to 0.4  | V     |

|                               | Analog input (–1 V to –0.125 V prescaler range) <sup>5</sup> | -3.75 to 0.4  | V     |

|                               | Analog input (direct input to ADC)                           | -0.4 to 3.75  | V     |

|                               | Analog input (positive current monitor) <sup>6</sup>         | -0.4 to 12.0  | V     |

|                               | Analog input (negative current monitor) <sup>5</sup>         | -11.0 to 0.4  | V     |

|                               | Digital input                                                | -0.4 to 12.0  | V     |

| AG                            | Unpowered, ADC reset asserted or unconfigured                | -11.0 to 12.0 | V     |

|                               | Low Current Mode (1 μA, 3 μA, 10 μA, 30 μA)                  | -0.4 to 12.0  | V     |

|                               | Low Current Mode (–1 μA, –3 μA, –10 μA, –30 μA)              | -11.0 to 0.4  | V     |

|                               | High Current Mode <sup>3</sup>                               | -11.0 to 12.0 | V     |

| AT                            | Unpowered, ADC reset asserted or unconfigured                | -0.4 to 15.0  | V     |

|                               | Analog input (+16 V, 4 V prescaler range)                    | -0.4 to 15.0  | V     |

|                               | Analog input (direct input to ADC)                           | -0.4 to 3.75  | V     |

|                               | Digital input                                                | -0.4 to 1650  | V     |

| T <sub>STG</sub> <sup>4</sup> | Storage temperature                                          | -65 to 150    | °C    |

| T <sub>J</sub> <sup>4</sup>   | Junction temperature                                         | 125           | °C    |

#### Notes:

- 5. Negative input is not supported between –40°C and –55°C.

- 6. Positive input is not supported between -40°C and -55°C.

3-2 Revision 2

<sup>1.</sup> The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-5.

<sup>2.</sup> Analog data not valid beyond 3.65 V.

<sup>3.</sup> The high current mode has a maximum power limit of 15 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

<sup>4.</sup> For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

Table 3-2 • Recommended Operating Conditions<sup>1</sup>

| Symbol              | Parameter <sup>2</sup>                     |                               | Ext. Temperature | Units |

|---------------------|--------------------------------------------|-------------------------------|------------------|-------|

| T <sub>J</sub>      | Junction temperature                       |                               | -55 to +100      | °C    |

| VCC                 | 1.5 V DC core supply voltage               |                               | 1.425 to 1.575   | V     |

| VJTAG               | JTAG DC voltage                            |                               | 1.4 to 3.6       | V     |

| VPUMP               | Programming voltage                        | Programming mode <sup>3</sup> | 3.15 to 3.45     | V     |

|                     |                                            | Operation <sup>4</sup>        | 0 to 3.6         | V     |

| VCCPLL              | Analog power supply (PLL)                  | •                             | 1.425 to 1.575   | V     |

| VCCI                | 1.5 V DC supply voltage                    | 1.425 to 1.575                | V                |       |

|                     | 1.8 V DC supply voltage                    |                               | 1.7 to 1.9       | V     |

|                     | 2.5 V DC supply voltage                    |                               | 2.3 to 2.7       | V     |

|                     | 3.3 V DC supply voltage                    | 3.0 to 3.6                    | V                |       |

|                     | LVDS differential I/O                      | 2.375 to 2.625                | V                |       |

|                     | LVPECL differential I/O                    |                               | 3.0 to 3.6       | V     |

| VCC33A              | +3.3 V power supply                        |                               | 2.97 to 3.63     | V     |

| VCC33PMP            | +3.3 V power supply                        |                               | 2.97 to 3.63     | V     |

| VAREF               | Voltage reference for ADC                  |                               | 2.527 to 2.593   | V     |

| VCC15A <sup>6</sup> | Digital power supply for the analog system |                               | 1.425 to 1.575   | V     |

| VCCNVM              | Embedded flash power supply                |                               | 1.425 to 1.575   | V     |

| vccosc              | Oscillator power supply                    |                               | 2.97 to 3.63     | V     |

| AV <sup>5</sup>     | Unpowered, ADC reset asserted or           | -10.5 to 11.6                 | V                |       |

|                     | Analog input (+16 V to +2 V presca         | -0.3 to 11.6                  | V                |       |

|                     | Analog input (+1 V to + 0.125 V pre        | -0.3 to 3.6                   | V                |       |

|                     | Analog input (–16 V to –2 V presca         | -10.5 to 0.3                  | V                |       |

|                     | Analog input (-1 V to -0.125 V pre         | -3.6 to 0.3                   | V                |       |

|                     | Analog input (direct input to ADC)         | -0.3 to 3.6                   | V                |       |

|                     | Analog input (positive current moni        | -0.3 to 11.6                  | V                |       |

|                     | Analog input (negative current mon         | -10.5 to 0.3                  | V                |       |

|                     | Digital input                              |                               | -0.3 to 11.6     | V     |

|                     |                                            |                               |                  |       |

#### Notes:

- 1. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-85 on page 2-158.

- 2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 3. The programming temperature range supported is  $T_{ambient} = 0$ °C to 85°C.

- 4. VPUMP can be left floating during normal operation (not programming mode).

- 5. The input voltage may overshoot by up to 500 mV above the Recommended Maximum (150 mV in Direct mode), provided the duration of the overshoot is less than 50% of the operating lifetime of the device.

- 6. Violating the VCC15A recommended voltage supply during an embedded flash program cycle can corrupt the page being programmed.

- 7. Negative input is not supported between -40°C and -55°C.

- 8. Positive input is not supported between -40°C and -55°C.

Revision 2 3-3

Table 3-2 • Recommended Operating Conditions<sup>1</sup>

| Symbol            | Parameter <sup>2</sup>                               | Ext. Temperature | Units |

|-------------------|------------------------------------------------------|------------------|-------|

| AC                | Unpowered, ADC reset asserted or unconfigured        | -10.5 to 11.6    | V     |

|                   | Analog input (+16 V to +2 V prescaler range)         | -0.3 to 11.6     | V     |

|                   | Analog input (+1 V to +0.125 V prescaler range)      | -0.3 to 3.6      | V     |

|                   | Analog input (–16 V to –2 V prescaler range)         | -10.5 to 0.3     | V     |

|                   | Analog input (-1 V to -0.125 V prescaler range)      | -3.6 to 0.3      | V     |

|                   | Analog input (direct input to ADC)                   | -0.3 to 3.6      | V     |

|                   | Analog input (positive current monitor) <sup>8</sup> | -0.3 to 11.6     | V     |

|                   | Analog input (negative current monitor) <sup>7</sup> | -10.5 to 0.3     | V     |

|                   | Digital input                                        | -0.3 to 11.6     | V     |

| AG <sup>4,5</sup> | Unpowered, ADC reset asserted or unconfigured        | -10.5 to 11.6    | V     |

|                   | Low Current Mode (1 μA, 3 μA, 10 μA, 30 μA)          | -0.3 to 11.6     | V     |

|                   | Low Current Mode (–1 μA, –3 μA, –10 μA, –30 μA)      | -10.5 to 0.3     | V     |

|                   | High Current Mode <sup>5</sup>                       | -10.5 to 11.6    | V     |

| AT <sup>4</sup>   | Unpowered, ADC reset asserted or unconfigured        | -0.3 to 14.5     | V     |

|                   | Analog input (+16 V, +4 V prescaler range)           | -0.3 to 14.5     | V     |

|                   | Analog input (direct input to ADC)                   | -0.3 to 3.6      | V     |

|                   | Digital input                                        | -0.3 to 14.5     | V     |

#### Notes:

- 1. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-85 on page 2-158.

- 2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 3. The programming temperature range supported is  $T_{ambient} = 0$ °C to 85°C.

- 4. VPUMP can be left floating during normal operation (not programming mode).

- 5. The input voltage may overshoot by up to 500 mV above the Recommended Maximum (150 mV in Direct mode), provided the duration of the overshoot is less than 50% of the operating lifetime of the device.

- 6. Violating the VCC15A recommended voltage supply during an embedded flash program cycle can corrupt the page being programmed.

- 7. Negative input is not supported between -40°C and -55°C.

- 8. Positive input is not supported between -40°C and -55°C.

3-4 Revision 2

## I/O Power-Up and Supply Voltage Thresholds for Power-On Reset

Sophisticated power-up management circuitry is designed into every Fusion device. These circuits ensure easy transition from the powered off state to the powered up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 3-1 on page 3-7.

There are five regions to consider during power-up.

Fusion I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 3-1).

- 2. VCCI > VCC 0.75 V (typical).

- 3. Chip is in the operating mode.

#### **VCCI Trip Point:**

Ramping up: 0.6 V < trip\_point\_up < 1.2 V Ramping down: 0.5 V < trip\_point\_down < 1.1 V

**VCC Trip Point:**

Ramping up: 0.6 V < trip\_point\_up < 1.1 V Ramping down: 0.5 V < trip\_point\_down < 1 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- · During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

## Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

#### PLL Behavior at Brownout Condition

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper power-up behavior. Power ramp-up should be monotonic at least until VCC and VCCPLX exceed brownout activation levels. The VCC activation level is specified as 1.1 V worst-case (see Figure 3-1 on page 3-7 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels (0.75 V  $\pm$  0.25 V), the PLL output lock signal goes low and/or the output clock is lost.

3-6 Revision 2

#### **Thermal Characteristics**

#### Introduction

The temperature variable in the Microsemi Designer software refers to the junction temperature, not the ambient, case, or board temperatures. This is an important distinction because dynamic and static power consumption will cause the chip's junction temperature to be higher than the ambient, case, or board temperatures. EQ 1 through EQ 3 give the relationship between thermal resistance, temperature gradient, and power.

$$\theta_{JA} = \frac{T_J - \theta_A}{P}$$

EQ 1

$$\theta_{JB} = \frac{T_J - T_B}{P}$$

EQ 2

$$\theta_{JC} = \frac{T_J - T_C}{P}$$

EQ3

where

$\theta_{JA}$  = Junction-to-air thermal resistance

$\theta_{JB}$  = Junction-to-board thermal resistance

$\theta_{JC}$  = Junction-to-case thermal resistance

$T_J$  = Junction temperature

T<sub>A</sub> = Ambient temperature

T<sub>B</sub> = Board temperature (measured 1.0 mm away from the package edge)

T<sub>C</sub> = Case temperature

P = Total power dissipated by the device

Table 3-6 • Package Thermal Resistance

|               | $\theta_{	extsf{JA}}$ |         |         |             |      |       |

|---------------|-----------------------|---------|---------|-------------|------|-------|

| Product       | Still Air             | 1.0 m/s | 2.5 m/s | $\theta$ JC | θЈВ  | Units |

| AFS600-FG256  | 28.9                  | 25.2    | 23.5    | 6.8         | 19.9 | °C/W  |

| AFS1500-FG256 | 23.3                  | 19.6    | 18.0    | 4.3         | 14.2 | °C/W  |

| AFS600-FG484  | 21.8                  | 18.2    | 16.7    | 7.7         | 16.8 | °C/W  |

| AFS1500-FG484 | 21.6                  | 16.8    | 15.2    | 5.6         | 14.9 | °C/W  |

| AFS1500-FG676 | TBD                   | TBD     | TBD     | TBD         | TBD  | °C/W  |

3-8 Revision 2

## Static Power Consumption of Various Internal Resources

Table 3-13 • Different Components Contributing to the Static Power Consumption in Fusion Devices

|           |                                                                      | Power Supply |                             | Device-Specific<br>Static<br>Contributions |        |       |

|-----------|----------------------------------------------------------------------|--------------|-----------------------------|--------------------------------------------|--------|-------|

| Parameter | Definition                                                           | Name         | Setting                     | AFS1500                                    | AFS600 | Units |

| PDC1      | Core static power contribution in operating mode                     | VCC          | 1.5 V                       | 18                                         | 7.5    | mW    |

| PDC2      | Device static power contribution in sleep mode*                      | VCC33A       | 3.3 V                       | 0.66                                       |        | mW    |

| PDC3      | Device static power contribution in standby mode                     | VCC33A       | 3.3 V                       | 0.03                                       |        | mW    |

| PDC4      | NVM static power contribution                                        | VCC          | 1.5 V                       | 1.19                                       |        | mW    |

| PDC5      | Analog Block static power contribution of ADC                        | VCC33A       | 3.3 V                       | 8.25                                       |        | mW    |

| PDC6      | Analog Block static power contribution per Quad                      | VCC33A       | 3.3 V                       | 3.3                                        |        | mW    |

| PDC7      | Static contribution per input pin – standard dependent contribution  | VCCI         | See Table 3-10 on page 3-15 |                                            |        |       |

| PDC8      | Static contribution per output pin – standard dependent contribution | VCCI         | See Table 3-11 on page 3-17 |                                            |        | -17   |

| PDC9      | Static contribution for PLL                                          | VCC          | 1.5 V                       | 2.                                         | 55     | mW    |

Note: \*Sleep mode is not supported between -40°C and -55°C.

## **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in the Libero SoC software.

The power calculation methodology described below uses the following variables:

- · The number of PLLs as well as the number and the frequency of each output clock generated

- The number of combinatorial and sequential cells used in the design

- The internal clock frequencies

- · The number and the standard of I/O pins used in the design

- The number of RAM blocks used in the design

- · The number of NVM blocks used in the design

- · The number of Analog Quads used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 3-14 on page 3-23.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 3-15 on page 3-23.

- Read rate and write rate to the RAM—guidelines are provided for typical applications in Table 3-15 on page 3-23.

- · Read rate to the NVM blocks

The calculation should be repeated for each clock domain defined in the design.

Revision 2 3-19

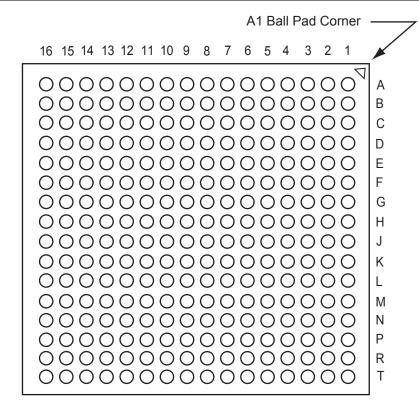

# 4 - Pin Assignments

## **FG256**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at www.microsemi.com/soc/products/solutions/package/default.aspx.

Revision 2 4-1

## **Datasheet Categories**

## **Categories**

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "Fusion Device Status" table on page III, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

#### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

## **Preliminary**

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

## Unmarked (production)

This version contains information that is considered to be final.

## **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.

Revision 2 5-5