#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I²C, SCI, SPI, USB OTG                                                           |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 10K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                      |

| Data Converters            | A/D 14x12b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f51113adfm-3a |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1.4 | Pin Functions (3/3) |

|-----------|---------------------|

|           |                     |

| Classifications         | Pin Name                                 | I/O    | Description                                                               |

|-------------------------|------------------------------------------|--------|---------------------------------------------------------------------------|

| USB 2.0 host/           | USB0_DP                                  | I/O    | D+ I/O pin of the USB on-chip transceiver.                                |

| function module         | USB0_DM                                  | I/O    | D- I/O pin of the USB on-chip transceiver.                                |

|                         | USB0_VBUS                                | Input  | USB cable connection monitor pin.                                         |

|                         | USB0_EXICEN                              | Output | Low-power control signal for the OTG chip.                                |

|                         | USB0_VBUSEN                              | Output | VBUS (5 V) supply enable signal for the OTG chip.                         |

|                         | USB0_OVRCURA,<br>USB0_OVRCURB            | Input  | External overcurrent detection pins.                                      |

|                         | USB0_ID                                  | Input  | Mini-AB connector ID input pin during operation in OTG mode.              |

| 12-bit A/D<br>converter | AN000 to AN004, AN006,<br>AN008 to AN015 | Input  | Input pins for the analog signals to be processed by the A/D converter.   |

|                         | ADTRG0#                                  | Input  | Input pin for the external trigger signals that start the A/D conversion. |

| D/A converter           | DA0, DA1                                 | Output | Output pins for the analog signals to be processed by the D/A converted   |

| I/O ports               | P03, P05                                 | I/O    | 2-bit input/output pins.                                                  |

|                         | P14 to P17                               | I/O    | 4-bit input/output pins.                                                  |

|                         | P26, P27                                 | I/O    | 2-bit input/output pins.                                                  |

|                         | P30 to P32, P35                          | I/O    | 4-bit input/output pins (P35 input pin).                                  |

|                         | P40 to P44, P46                          | I/O    | 6-bit input/output pins.                                                  |

|                         | P54, P55                                 | I/O    | 2-bit input/output pins.                                                  |

|                         | PA0, PA1, PA3, PA4, PA6                  | I/O    | 5-bit input/output pins.                                                  |

|                         | PB0, PB1, PB3, PB5 to PB7                | I/O    | 6-bit input/output pins.                                                  |

|                         | PC0 to PC7                               | I/O    | 8-bit input/output pins.                                                  |

|                         | PE0 to PE7                               | I/O    | 8-bit input/output pins.                                                  |

|                         | PH7                                      | Input  | 1-bit input pin.                                                          |

|                         | PJ6, PJ7                                 | I/O    | 2-bit input/output pins.                                                  |

Note 1. For external clock input.

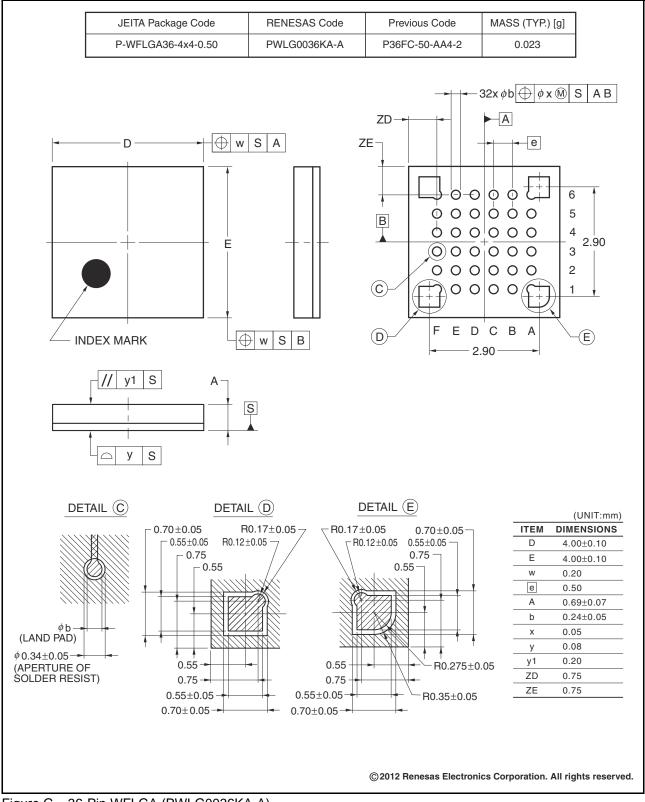

| Table 1.6 | List of Pins and Pin Functions (64-Pin WFLGA) (1/2) |

|-----------|-----------------------------------------------------|

|           |                                                     |

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port          | Timers<br>(MTU, POE, RTC)         | Communication<br>(SCle, SClf, RSPI, RIIC, USB) | Others                       |

|------------|-------------------------------------------|-------------------|-----------------------------------|------------------------------------------------|------------------------------|

| A1         | AVSS0                                     |                   | - · · ·                           | · · · <b>·</b>                                 |                              |

| A2         | AVCC0                                     |                   |                                   |                                                |                              |

| A3         | VREFH0                                    | PJ6*2             |                                   |                                                |                              |

| A4         | VREFL0                                    | PJ7* <sup>2</sup> |                                   |                                                |                              |

| A5         |                                           | P43* <sup>2</sup> |                                   |                                                | AN003                        |

| A6         |                                           | P46*2             |                                   |                                                | AN006                        |

| A7         |                                           | PE2               | MTIOC4A                           | RXD12/RXDX12/SMISO12/SSCL12                    | IRQ7/AN010                   |

| A8         |                                           | PE3               | MTIOC0A/MTIOC1B/<br>MTIOC4B/POE8# | CTS12#/RTS12#/SS12#/RSPCKA                     | IRQ3/AN011                   |

| B1         | XCOUT                                     |                   |                                   |                                                |                              |

| B2         |                                           | P03               |                                   |                                                | DA0                          |

| B3         |                                           | P40* <sup>2</sup> |                                   |                                                | AN000                        |

| B4         |                                           | P42* <sup>2</sup> |                                   |                                                | AN002                        |

| B5         |                                           | P44* <sup>2</sup> |                                   |                                                | AN004                        |

| B6         |                                           | PE6               |                                   |                                                | IRQ6/AN014                   |

| B7         |                                           | PE1               | MTIOC4C                           | TXD12/TXDX12/SIOX12/SMOSI12/<br>SSDA12         | IRQ1/AN009                   |

| B8         |                                           | PE4               | MTIOC1A/MTIOC3A/<br>MTIOC4D       | MOSIA                                          | IRQ4/AN012                   |

| C1         | XCIN                                      | PH7               |                                   |                                                |                              |

| C2         |                                           | P05               |                                   |                                                | DA1                          |

| C3         |                                           | P27               | MTIOC2B                           | SCK1/SCK12                                     | IRQ3/CMPA2/CACREF<br>ADTRG0# |

| C4         |                                           | P41* <sup>2</sup> |                                   |                                                | AN001                        |

| C5         |                                           | PE7               |                                   |                                                | IRQ7/AN015                   |

| C6         |                                           | PE5               | MTIOC2B/MTIOC4C                   |                                                | IRQ5/AN013                   |

| C7         |                                           | PA1               | MTIOC0B/MTCLKC/<br>RTCOUT         | SCK5/SSLA2                                     |                              |

| C8         |                                           | PA0               | MTIOC4A                           | SSLA1                                          | CACREF                       |

| D1         | RES#                                      |                   |                                   |                                                |                              |

| D2         |                                           | P30               | MTIOC4B/POE8#                     | RXD1/SMISO1/SSCL1                              | IRQ0                         |

| D3         |                                           | P26               | MTIOC2A                           | TXD1/SMOSI1/SSDA1/<br>USB0_VBUSEN              |                              |

| D4         |                                           | PE0               | MTIOC2A/POE3#                     | SCK12                                          | IRQ0/AN008                   |

| D5         |                                           | PA6               | MTIC5V/MTIOC2A/MTCLKB/<br>POE2#   | CTS5#/RTS5#/SS5#/SDA0/MOSIA                    | IRQ3                         |

| D6         |                                           | PA4               | MTIC5U/MTIOC2B/MTCLKA             | TXD5/SMOSI5/SSDA5/SSLA0                        | IRQ5                         |

| D7         |                                           | PA3               | MTIOC0D/MTCLKD/<br>MTIOC1B/POE0#  | RXD5/SMISO5/SSCL5/MISOA                        | IRQ6                         |

| D8         | VSS                                       |                   |                                   |                                                |                              |

| E1         | XTAL                                      |                   |                                   |                                                |                              |

| E2         | MD                                        |                   |                                   |                                                | FINED                        |

| E3         |                                           | P31               | MTIOC4D                           | CTS1#/RTS1#/SS1#                               | IRQ1                         |

| E4         |                                           | P55               | MTIOC4D                           |                                                |                              |

| E5         |                                           | PB3               | MTIOC0A/MTIOC3B/<br>MTIOC4A/POE3# | USB0_OVRCURA                                   |                              |

| E6         |                                           | PB1               | MTIOC0C/MTIOC4C                   |                                                | IRQ4                         |

| E7         |                                           | PB0               | MTIC5W/MTIOC0C/<br>RTCOUT         | SCL0/RSPCKA                                    | IRQ2/ADTRG0#                 |

| E8         | VCC                                       |                   |                                   |                                                |                              |

| F1         | EXTAL                                     |                   |                                   |                                                |                              |

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, POE, RTC)         | Communication<br>(SCIe, SCIf, RSPI, RIIC, USB)                          | Others       |

|------------|-------------------------------------------|----------|-----------------------------------|-------------------------------------------------------------------------|--------------|

| F2         |                                           | P32      | MTIOC0C/RTCOUT                    |                                                                         | IRQ2         |

| F3         | UPSEL                                     | P35      |                                   |                                                                         | NMI          |

| F4         | UB#                                       | P14      | MTIOC0A/MTIOC3A/<br>MTCLKA        |                                                                         |              |

| F5         |                                           | P54      | MTIOC4B                           |                                                                         |              |

| F6         |                                           | PC7      | MTIOC3A/MTCLKB                    | TXD1/SMOSI1/SSDA1/MISOA/<br>USB0_OVRCURB                                | CACREF       |

| F7         |                                           | PC4      | MTCLKC/MTIOC3D/POE0#              | SCK5/SSLA0/USB0_VBUSEN/<br>USB0_VBUS*1                                  | IRQ2/CLKOUT  |

| F8         |                                           | PB5      | MTIOC1B/MTIOC2A/POE1#             |                                                                         |              |

| G1         | VCL                                       |          |                                   |                                                                         |              |

| G2         |                                           | P17      | MTIOC0C/MTIOC3A/<br>MTIOC3B/POE8# | SCK1/MISOA/SDA0/RXD12/<br>RXDX12/SMISO12/SSCL12                         | IRQ7         |

| G3         |                                           | P16      | MTIOC3C/MTIOC3D/<br>RTCOUT        | TXD1/SMOSI1/SSDA1/SCL0/<br>MOSIA/USB0_VBUSEN/<br>USB0_OVRCURB/USB0_VBUS | IRQ6/ADTRG0# |

| G4         |                                           | P15      | MTIOC0B/MTCLKB                    | RXD1/SMISO1/SSCL1/RSPCKA                                                | IRQ5/CLKOUT  |

| G5         |                                           | PC6      | MTIOC3C/MTCLKA                    | RXD1/SMISO1/SSCL1/MOSIA/<br>USB0_EXICEN                                 |              |

| G6         |                                           | PC5      | MTIOC3B/MTCLKD                    | SCK1/RSPCKA/USB0_ID                                                     |              |

| G7         |                                           | PC3      | MTIOC4D                           | TXD5/SMOSI5/SSDA5                                                       |              |

| G8         |                                           | PB6/PC0  | MTIOC3D                           |                                                                         |              |

| H1         | VSS                                       |          |                                   |                                                                         |              |

| H2         | VCC                                       |          |                                   |                                                                         |              |

| H3         | VCC_USB                                   |          |                                   |                                                                         |              |

| H4         |                                           |          |                                   | USB0_DM                                                                 |              |

| H5         |                                           |          |                                   | USB0_DP                                                                 |              |

| H6         | VSS_USB                                   |          |                                   |                                                                         |              |

| H7         |                                           | PC2      | MTIOC4B                           | RXD5/SMISO5/SSCL5/SSLA3                                                 |              |

| H8         |                                           | PB7/PC1  | MTIOC3B                           |                                                                         |              |

Table 1.6

List of Pins and Pin Functions (64-Pin WFLGA) (2/2)

Note 1. Not 5 V tolerant.

Note 2. The power source of the I/O buffer for these pins is AVCC0.

# 4. I/O Registers

This section provides information on the on-chip I/O register addresses and bit configuration. The information is given as shown below. Notes on writing to I/O registers are also given below.

## (1) I/O register addresses (address order)

- Registers are listed from the lower allocation addresses.

- Registers are classified according to module symbols.

- Numbers of cycles for access indicate numbers of cycles of the given base clock.

- Among the internal I/O register area, addresses not listed in the list of registers are reserved. Reserved addresses must not be accessed. Do not access these addresses; otherwise, the operation when accessing these bits and subsequent operations cannot be guaranteed.

### (2) Notes on writing to I/O registers

While writing to an I/O register, the CPU starts executing subsequent instructions before the I/O register write access is completed. This may cause the subsequent instructions to be executed before the write value is reflected in the operation. The examples below show how subsequent instructions must be executed after a write access to an I/O register is completed.

#### [Examples of cases requiring special care]

- The subsequent instruction must be executed while an interrupt request is disabled with the IENj bit in IERn of the ICU (interrupt request enable bit) set to 0.

- A WAIT instruction is executed immediately after the preprocessing for causing a transition to the low power consumption state.

In the above cases, after writing to an I/O register, wait until the write operation is completed using the following procedure and then execute the subsequent instruction.

- (a) Write to an I/O register.

- (b) Read the value in the I/O register and write it to a general register.

- (c) Execute the operation using the value read.

- (d) Execute the subsequent instruction.

Example of instructions

• Byte-size I/O registers

MOV.L #SFR\_ADDR, R1 MOV.B #SFR\_DATA, [R1] CMP [R1].UB, R1 ;; Next process

• Word-size I/O registers

MOV.L #SFR\_ADDR, R1 MOV.W #SFR\_DATA, [R1] CMP [R1].W, R1 ;; Next process

| Table 4.1 | List of I/O Registers (Address Order) (9/16) |

|-----------|----------------------------------------------|

|-----------|----------------------------------------------|

| Address                | Module<br>Symbol | Register Name                                                          | Register<br>Symbol | Number of<br>Bits | Access<br>Size | Number of Acces<br>States                    |

|------------------------|------------------|------------------------------------------------------------------------|--------------------|-------------------|----------------|----------------------------------------------|

| 0008 88A2h             | MTU5             | Timer General Register W                                               | TGRW               | 16                | 16             | 2 or 3 PCLKB                                 |

| 0008 88A4h             | MTU5             | Timer Control Register W                                               | TCRW               | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 88A6h             | MTU5             | Timer I/O Control Register W                                           | TIORW              | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 88B2h             | MTU5             | Timer Interrupt Enable Register                                        | TIER               | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 88B4h             | MTU5             | Timer Start Register                                                   | TSTR               | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 88B6h             | MTU5             | Timer Compare Match Clear Register                                     | TCNTCMPCLR         | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 8900h             | POE              | Input Level Control/Status Register 1                                  | ICSR1              | 16                | 8, 16          | 2 or 3 PCLKB                                 |

| 0008 8902h             | POE              | Output Level Control/Status Register 1                                 | OCSR1              | 16                | 8, 16          | 2 or 3 PCLKB                                 |

| 0008 8908h             | POE              | Input Level Control/Status Register 2                                  | ICSR2              | 16                | 8, 16          | 2 or 3 PCLKB                                 |

| 0008 890Ah             | POE              | Software Port Output Enable Register                                   | SPOER              | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 890Bh             | POE              | Port Output Enable Control Register 1                                  | POECR1             | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 890Ch             | POE              | Port Output Enable Control Register 2                                  | POECR2             | 8                 | 8              | 2 or 3 PCLKB                                 |

| 0008 890Eh             | POE              | Input Level Control/Status Register 3                                  | ICSR3              | 16                | 8, 16          | 2 or 3 PCLKB                                 |

| 0008 9000h             | S12AD            | A/D Control Register                                                   | ADCSR              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9004h              | S12AD            | A/D Channel Select Register A                                          | ADANSA             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9008h              | S12AD            | A/D-Converted Value Addition Mode Select Register                      | ADADS              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 900Ch              | S12AD            | A/D-Converted Value Addition Count Select Register                     | ADADC              | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 900Eh              | S12AD            | A/D Control Extended Register                                          | ADCER              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9010h              | S12AD            | A/D Start Trigger Select Register                                      | ADSTRGR            | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9012h              | S12AD            | A/D Converted Extended Input Control Register                          | ADEXICR            | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9014h              | S12AD            | A/D Channel Select Register B                                          | ADANSB             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9018h              | S12AD            | A/D Data Duplication Register                                          | ADDBLDR            | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 901Ah              | S12AD            | A/D Temperature Sensor Data Register                                   | ADTSDR             | 16                | 16             | 2 or 3 PCLKB                                 |

|                        |                  | •                                                                      |                    |                   |                |                                              |

| 008 901Ch              | S12AD            | A/D Internal Reference Voltage Data Register                           | ADOCDR             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9020h              | S12AD            | A/D Data Register 0                                                    | ADDR0              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9022h              | S12AD            | A/D Data Register 1                                                    | ADDR1              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9024h              | S12AD            | A/D Data Register 2                                                    | ADDR2              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9026h              | S12AD            | A/D Data Register 3                                                    | ADDR3              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9028h              | S12AD            | A/D Data Register 4                                                    | ADDR4              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 902Ch              | S12AD            | A/D Data Register 6                                                    | ADDR6              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9030h              | S12AD            | A/D Data Register 8                                                    | ADDR8              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9032h              | S12AD            | A/D Data Register 9                                                    | ADDR9              | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9034h              | S12AD            | A/D Data Register 10                                                   | ADDR10             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9036h              | S12AD            | A/D Data Register 11                                                   | ADDR11             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9038h              | S12AD            | A/D Data Register 12                                                   | ADDR12             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 903Ah              | S12AD            | A/D Data Register 13                                                   | ADDR13             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 903Ch              | S12AD            | A/D Data Register 14                                                   | ADDR14             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 903Eh              | S12AD            | A/D Data Register 15                                                   | ADDR15             | 16                | 16             | 2 or 3 PCLKB                                 |

| 008 9060h              | S12AD            | A/D Sampling State Register 0                                          | ADSSTR0            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9061h              | S12AD            | A/D Sampling State Register L                                          | ADSSTRL            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9070h              | S12AD            | A/D Sampling State Register T                                          | ADSSTRT            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9071h              | S12AD            | A/D Sampling State Register O                                          | ADSSTRO            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9073h              | S12AD            | A/D Sampling State Register 1                                          | ADSSTR1            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9074h              | S12AD            | A/D Sampling State Register 2                                          | ADSSTR2            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9075h              | S12AD            | A/D Sampling State Register 3                                          | ADSSTR3            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9076h              | S12AD            | A/D Sampling State Register 4                                          | ADSSTR4            | 8                 | 8              | 2 or 3 PCLKB                                 |

|                        | S12AD            | A/D Sampling State Register 6                                          | ADSSTR6            | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 9078h              |                  | Serial Mode Register                                                   | SMR                | 8                 | 8              | 2 or 3 PCLKB                                 |

|                        | SCI1             |                                                                        |                    | -                 | -              |                                              |

| 008 A020h              | SCI1<br>SCI1     | Bit Rate Register                                                      | BRR                | 8                 | 8              | 2 or 3 PCI KR                                |

| 008 A020h<br>008 A021h | SCI1             | Bit Rate Register                                                      | BRR                | 8                 | 8              | 2 or 3 PCLKB                                 |

| 008 A020h              |                  | Bit Rate Register<br>Serial Control Register<br>Transmit Data Register | BRR<br>SCR<br>TDR  | 8<br>8<br>8       | 8<br>8<br>8    | 2 or 3 PCLKB<br>2 or 3 PCLKB<br>2 or 3 PCLKB |

| Address    | Module<br>Symbol | Register Name                                    | Register<br>Symbol | Number of<br>Bits | Access<br>Size | Number of Access<br>States |

|------------|------------------|--------------------------------------------------|--------------------|-------------------|----------------|----------------------------|

| 000A 0098h | USB0             | PIPE3 Transaction Counter Enable Register        | PIPE3TRE           | 16                | 16             | 9 PCLKB or more            |

| 000A 009Ah | USB0             | PIPE3 Transaction Counter Register               | PIPE3TRN           | 16                | 16             | 9 PCLKB or more            |

| 000A 009Ch | USB0             | PIPE4 Transaction Counter Enable Register        | PIPE4TRE           | 16                | 16             | 9 PCLKB or more            |

| 000A 009Eh | USB0             | PIPE4 Transaction Counter Register               | PIPE4TRN           | 16                | 16             | 9 PCLKB or more            |

| 000A 00A0h | USB0             | PIPE5 Transaction Counter Enable Register        | PIPE5TRE           | 16                | 16             | 9 PCLKB or more            |

| 000A 00A2h | USB0             | PIPE5 Transaction Counter Register               | PIPE5TRN           | 16                | 16             | 9 PCLKB or more            |

| 000A 00B0h | USB0             | BC Control Register 0                            | USBBCCTRL0         | 16                | 16             | 9 PCLKB or more            |

| 000A 00CCh | USB0             | USB Module Control Register                      | USBMC              | 16                | 16             | 9 PCLKB or more            |

| 000A 00D0h | USB0             | Device Address 0 Configuration Register          | DEVADD0            | 16                | 16             | 9 PCLKB or more            |

| 000A 00D2h | USB0             | Device Address 1 Configuration Register          | DEVADD1            | 16                | 16             | 9 PCLKB or more            |

| 000A 00D4h | USB0             | Device Address 2 Configuration Register          | DEVADD2            | 16                | 16             | 9 PCLKB or more            |

| 000A 00D6h | USB0             | Device Address 3 Configuration Register          | DEVADD3            | 16                | 16             | 9 PCLKB or more            |

| 000A 00D8h | USB0             | Device Address 4 Configuration Register          | DEVADD4            | 16                | 16             | 9 PCLKB or more            |

| 000A 00DAh | USB0             | Device Address 5 Configuration Register          | DEVADD5            | 16                | 16             | 9 PCLKB or more            |

| 007F C090h | FLASH            | E2 DataFlash Control Register                    | DFLCTL             | 8                 | 8              | 2 or 3 FCLK                |

| 007F C0ACh | TEMPS            | Temperature Sensor Calibration Data Register     | TSCDRL             | 8                 | 8              | 1 or 2 PCLKB               |

| 007F C0ADh | TEMPS            | Temperature Sensor Calibration Data Register     | TSCDRH             | 8                 | 8              | 1 or 2 PCLKB               |

| 07F C0B0h  | FLASH            | Flash Start-Up Setting Monitor Register          | FSCMR              | 16                | 16             | 2 or 3 FCLK                |

| 07F C0B2h  | FLASH            | Flash Access Window Start Address Monitor        | FAWSMR             | 16                | 16             | 2 or 3 FCLK                |

| 007F C0B4h | FLASH            | Flash Access Window End Address Monitor Register | FAWEMR             | 16                | 16             | 2 or 3 FCLK                |

| 007F C0B6h | FLASH            | Flash Initial Setting Register                   | FISR               | 8                 | 8              | 2 or 3 FCLK                |

| 007F C0B7h | FLASH            | Flash Extra Area Control Register                | FEXCR              | 8                 | 8              | 2 or 3 FCLK                |

| 007F C0B8h | FLASH            | Flash Error Address Monitor Register L           | FEAML              | 16                | 16             | 2 or 3 FCLK                |

| 007F C0BAh | FLASH            | Flash Error Address Monitor Register H           | FEAMH              | 8                 | 8              | 2 or 3 FCLK                |

| 007F C0C0h | FLASH            | Protection Unlock Register                       | FPR                | 8                 | 8              | 2 or 3 FCLK                |

| 007F C0C1h | FLASH            | Protection Unlock Status Register                | FPSR               | 8                 | 8              | 2 or 3 FCLK                |

| 007F C0C2h | FLASH            | Flash Read Buffer Register L                     | FRBL               | 16                | 16             | 2 or 3 FCLK                |

| 007F C0C4h | FLASH            | Flash Read Buffer Register H                     | FRBH               | 16                | 16             | 2 or 3 FCLK                |

| 007F FF80h | FLASH            | Flash P/E Mode Control Register                  | FPMCR              | 8                 | 8              | 2 or 3 FCLK                |

| 007F FF81h | FLASH            | Flash Area Select Register                       | FASR               | 8                 | 8              | 2 or 3 FCLK                |

| 007F FF82h | FLASH            | Flash Processing Start Address Register L        | FSARL              | 16                | 16             | 2 or 3 FCLK                |

| 007F FF84h | FLASH            | Flash Processing Start Address Register H        | FSARH              | 8                 | 8              | 2 or 3 FCLK                |

| 007F FF85h | FLASH            | Flash Control Register                           | FCR                | 8                 | 8              | 2 or 3 FCLK                |

| 07F FF86h  | FLASH            | Flash Processing End Address Register L          | FEARL              | 16                | 16             | 2 or 3 FCLK                |

| 07F FF88h  | FLASH            | Flash Processing End Address Register H          | FEARH              | 8                 | 8              | 2 or 3 FCLK                |

| 07F FF89h  | FLASH            | Flash Reset Register                             | FRESETR            | 8                 | 8              | 2 or 3 FCLK                |

| 07F FF8Ah  | FLASH            | Flash Status Register 0                          | FSTATR0            | 8                 | 8              | 2 or 3 FCLK                |

| 07F FF8Bh  | FLASH            | Flash Status Register 1                          | FSTATR1            | 8                 | 8              | 2 or 3 FCLK                |

| 007F FF8Ch | FLASH            | Flash Write Buffer Register L                    | FWBL               | 16                | 16             | 2 or 3 FCLK                |

| 007F FF8Eh | FLASH            | Flash Write Buffer Register H                    | FWBH               | 16                | 16             | 2 or 3 FCLK                |

| 07F FFB2h  | FLASH            | Flash P/E Mode Entry Register                    | FENTRYR            | 16                | 16             | 2 or 3 FCLK                |

#### Table 4.1 List of I/O Registers (Address Order) (16/16)

Note 1. Odd addresses cannot be accessed in 16-bit units. When accessing a register in 16-bit units, access the address of the TMOCNTL register. Table 27.6 lists register allocation for 16-bit access in the User's Manual: Hardware.

### Table 5.4DC Characteristics (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} < 2.7 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} < 2.7 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                            | Item                                                                                                                                                                                                                         | Symbol          | Min.        | Тур. | Max.        | Unit | Test<br>Conditions |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------|-------------|------|--------------------|

| Schmitt trigger<br>input voltage           | Ports P16, P17, port PA6, port PB0<br>(5 V tolerant)                                                                                                                                                                         | V <sub>IH</sub> | VCC × 0.8   | —    | 5.8         | V    |                    |

|                                            | Ports P03, P05,<br>ports P14,P15,<br>ports P26, P27,<br>ports P30 to P32, P35,<br>ports P54, P55,<br>ports PA0, PA1, PA3, PA4,<br>ports PB1, PB3, PB5 to PB7,<br>ports PC2 to PC7,<br>ports PE0 to PE7,<br>port PH7,<br>RES# |                 | VCC × 0.8   | _    | VCC + 0.3   |      |                    |

|                                            | All pins                                                                                                                                                                                                                     |                 | -0.3        | —    | VCC × 0.2   |      |                    |

|                                            | All pins                                                                                                                                                                                                                     | $\Delta V_T$    | VCC × 0.01  | _    | —           |      |                    |

| Input voltage                              | MD                                                                                                                                                                                                                           | V <sub>IH</sub> | VCC × 0.9   | _    | VCC + 0.3   | V    |                    |

| (except for Schmitt<br>trigger input pins) | XTAL (external clock input)                                                                                                                                                                                                  |                 | VCC × 0.8   | _    | VCC + 0.3   | -    |                    |

|                                            | Ports P40 to P44, P46, ports PJ6,<br>PJ7                                                                                                                                                                                     | -               | AVCC0 × 0.7 | —    | AVCC0 + 0.3 |      |                    |

|                                            | MD                                                                                                                                                                                                                           | V <sub>IL</sub> | -0.3        | _    | VCC × 0.1   |      |                    |

|                                            | XTAL (external clock input)                                                                                                                                                                                                  | 1               | -0.3        | —    | VCC × 0.2   |      |                    |

|                                            | Ports P40 to P44, P46, ports PJ6,<br>PJ7                                                                                                                                                                                     |                 | -0.3        | —    | AVCC0 × 0.3 |      |                    |

### Table 5.5DC Characteristics (3)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                | Item                                                                   |                  |   | Тур. | Max. | Unit | Test Conditions                                                       |

|--------------------------------|------------------------------------------------------------------------|------------------|---|------|------|------|-----------------------------------------------------------------------|

| Input leakage<br>current       | RES#, MD, port P35, port PH7                                           | I <sub>in</sub>  |   | —    | 1.0  | μA   | V <sub>in</sub> = 0 V, VCC                                            |

| Three-state                    | Ports for 5 V tolerant                                                 | I <sub>TSI</sub> |   | —    | 1.0  | μA   | V <sub>in</sub> = 0 V, 5.8 V                                          |

| leakage current<br>(off-state) | Pins other than above                                                  |                  | _ | —    | 1.0  |      | V <sub>in</sub> = 0 V, VCC                                            |

| Input capacitance              | All input pins<br>(except for port P16, port P35, USB0_DM,<br>USB0_DP) | C <sub>in</sub>  | _ | _    | 15   | pF   | V <sub>in</sub> = 0 mV,<br>Frequency: 1 MHz,<br>T <sub>a</sub> = 25°C |

|                                | Port P16, port P35, USB0_DM, USB0_DP                                   |                  |   | —    | 30   |      |                                                                       |

### Table 5.6DC Characteristics (4)

```

Conditions: 1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{\text{USB}} = 0 \text{ V}, \text{ T}_{\text{a}} = -40 \text{ to } +105^{\circ}\text{C}

```

| Item                      |                                              |                | Min. | Тур. | Max. | Unit | Test Conditions       |

|---------------------------|----------------------------------------------|----------------|------|------|------|------|-----------------------|

| Input pull-up<br>resistor | All ports<br>(except for port P35, port PH7) | R <sub>U</sub> | 10   | 20   | 100  | kΩ   | V <sub>in</sub> = 0 V |

## Table 5.17 Permissible Output Currents (1)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{T}_a = -40 \text{ to } +85^{\circ}\text{C} \text{ (D version)}$

|                                 | Item                                                                                                   | Symbol           | Max. | Unit |

|---------------------------------|--------------------------------------------------------------------------------------------------------|------------------|------|------|

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  | I <sub>OL</sub>  | 0.4  | mA   |

| (average value per pin)         | Ports other than above                                                                                 | -                | 8.0  |      |

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  | -                | 0.4  |      |

| (maximum value per pin)         | Ports other than above                                                                                 |                  | 8.0  |      |

| Permissible output low current  | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                         | $\Sigma I_{OL}$  | 2.4  |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                |                  | 30   |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7 |                  | 30   |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                               | -                | 30   |      |

|                                 | Total of all output pins                                                                               | -                | 60   |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  | I <sub>ОН</sub>  | -0.1 |      |

| (average value per pin)         | Ports other than above                                                                                 | -                | -4.0 |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  | -                | -0.1 |      |

| (maximum value per pin)         | Ports other than above                                                                                 |                  | -4.0 |      |

| Permissible output high current | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                         | ΣΙ <sub>ΟΗ</sub> | -0.6 |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                |                  | -10  |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7 | -                | -15  |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                               | Ī                | -15  |      |

|                                 | Total of all output pins                                                                               |                  | -40  |      |

Note: Do not exceed the permissible total supply current.

## Table 5.18 Permissible Output Currents (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{T}_a = -40 \text{ to } +105^{\circ}\text{C} \text{ (G version)}$

|                                 | Item                                                                                                   | Symbol           | Max. | Unit |

|---------------------------------|--------------------------------------------------------------------------------------------------------|------------------|------|------|

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  | I <sub>OL</sub>  | 0.4  | mA   |

| (average value per pin)         | Ports other than above                                                                                 | -                | 8.0  |      |

| Permissible output low current  | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  |                  | 0.4  |      |

| (maximum value per pin)         | Ports other than above                                                                                 |                  | 8.0  |      |

| Permissible output low current  | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                         | $\Sigma I_{OL}$  | 1.6  |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                |                  | 20   |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7 |                  | 20   |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                               | -                | 20   |      |

|                                 | Total of all output pins                                                                               | -                | 40   |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  | I <sub>OH</sub>  | -0.1 |      |

| (average value per pin)         | Ports other than above                                                                                 | -                | -4.0 |      |

| Permissible output high current | Ports P40 to P44, P46, ports PJ6, PJ7                                                                  | -                | -0.1 |      |

| (maximum value per pin)         | Ports other than above                                                                                 |                  | -4.0 |      |

| Permissible output high current | Total of ports P40 to P44, P46, ports PJ6, PJ7                                                         | Σl <sub>OH</sub> | -0.6 |      |

|                                 | Total of ports P03, P05, ports P26, P27, ports P30, P31                                                |                  | -10  |      |

|                                 | Total of ports P14 to P17, port P32, ports P54, P55, ports PB0, PB1, PB3, PB5 to PB7, ports PC2 to PC7 |                  | -15  |      |

|                                 | Total of ports PA0, PA1, PA3, PA4, PA6, ports PE0 to PE7                                               |                  | -15  |      |

|                                 | Total of all output pins                                                                               |                  | -40  |      |

Note: Do not exceed the permissible total supply current.

## 5.2.3 Standard I/O Pin Output Characteristics (3)

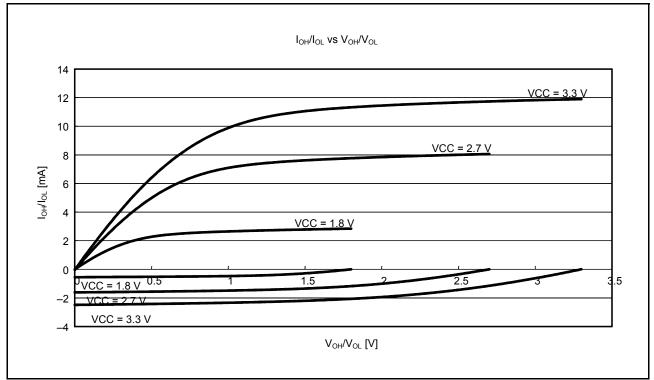

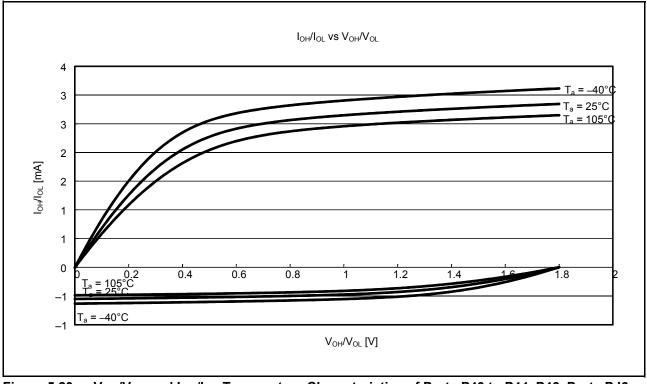

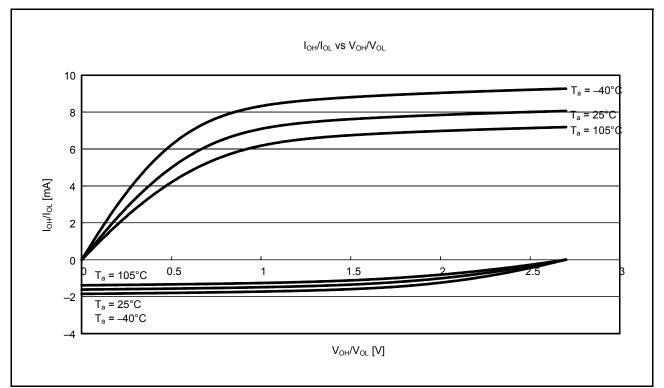

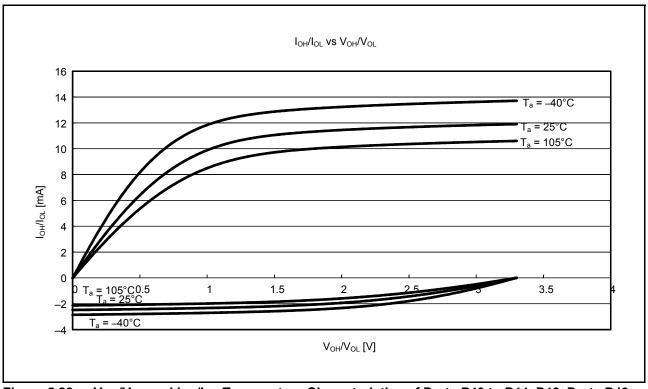

Figure 5.19 to Figure 5.22 show the characteristics of ports P40 to P44, P46, ports PJ6, PJ7.

Figure 5.19  $V_{OH}/V_{OL}$  and  $I_{OH}/I_{OL}$  Voltage Characteristics of Ports P40 to P44, P46, Ports PJ6, PJ7 at  $T_a = 25^{\circ}C$  (Reference Data)

Figure 5.20 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> Temperature Characteristics of Ports P40 to P44, P46, Ports PJ6, PJ7 at VCC = 1.8 V (Reference Data)

Figure 5.21 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> Temperature Characteristics of Ports P40 to P44, P46, Ports PJ6, PJ7 at VCC = 2.7 V (Reference Data)

Figure 5.22 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> Temperature Characteristics of Ports P40 to P44, P46, Ports PJ6, PJ7 at VCC = 3.3 V (Reference Data)

RENESAS

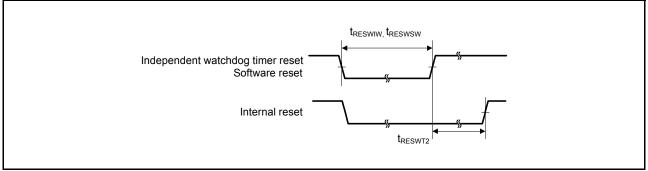

Figure 5.33 Reset Input Timing (2)

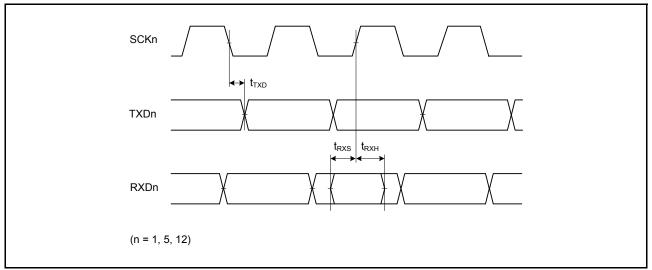

Figure 5.43 SCI Input/Output Timing: Clock Synchronous Mode

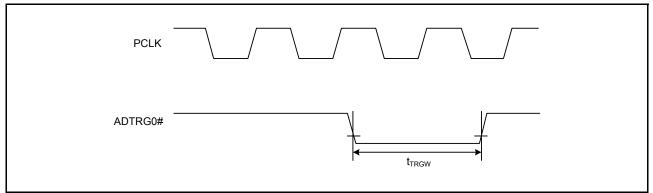

Figure 5.44 A/D Converter External Trigger Input Timing

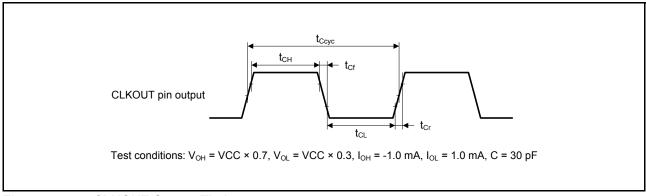

Figure 5.45 CLKOUT Output Timing

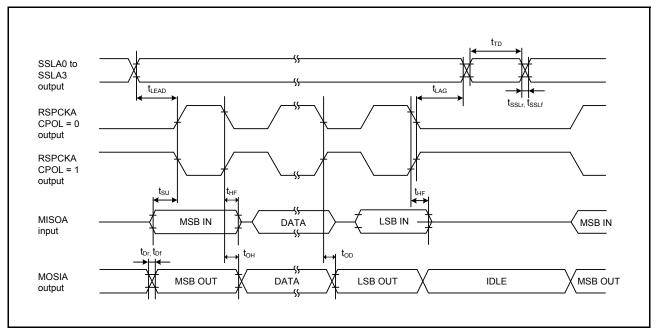

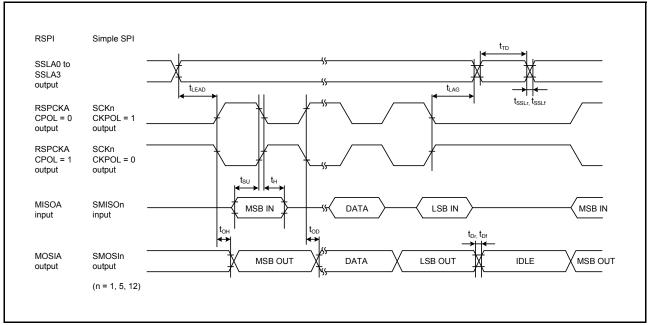

Figure 5.49 RSPI Timing (Master, CPHA = 1) (Bit Rate: PCLKB Set to Division Ratio Other Than Divided by 2) and Simple SPI Timing (Master, CKPH = 0)

## 5.8 Power-On Reset Circuit and Voltage Detection Circuit Characteristics

| Item                    |                      | Symbol              | Min. | Тур. | Max. | Unit | Test Conditions             |

|-------------------------|----------------------|---------------------|------|------|------|------|-----------------------------|

| Voltage detection level | Power-on reset (POR) | V <sub>POR</sub>    | 1.35 | 1.50 | 1.65 | V    | Figure 5.58,<br>Figure 5.59 |

|                         | Voltage detection    | V <sub>det1_4</sub> | 3.00 | 3.10 | 3.20 | V    | Figure 5.60                 |

|                         | circuit (LVD1)*1     | V <sub>det1_5</sub> | 2.91 | 3.00 | 3.09 |      | At falling edge VCC         |

|                         |                      | V <sub>det1_6</sub> | 2.81 | 2.90 | 2.99 |      |                             |

|                         |                      | V <sub>det1_7</sub> | 2.70 | 2.79 | 2.88 |      |                             |

|                         |                      | V <sub>det1_8</sub> | 2.60 | 2.68 | 2.76 |      |                             |

|                         |                      | V <sub>det1_9</sub> | 2.50 | 2.58 | 2.66 |      |                             |

|                         |                      | V <sub>det1_A</sub> | 2.40 | 2.48 | 2.56 |      |                             |

|                         |                      | V <sub>det1_B</sub> | 1.99 | 2.06 | 2.13 |      |                             |

|                         |                      | V <sub>det1_C</sub> | 1.90 | 1.96 | 2.02 |      |                             |

|                         |                      | V <sub>det1_D</sub> | 1.80 | 1.86 | 1.92 |      |                             |

#### Table 5.45 Power-On Reset Circuit and Voltage Detection Circuit Characteristics (1)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

Note: • These characteristics apply when noise is not superimposed on the power supply. When a setting is made so that the voltage detection level overlaps with that of the voltage detection circuit (LVD2), it cannot be specified which of LVD1 and LVD2 is used for voltage detection.

Note 1. n in the symbol Vdet1\_n denotes the value of the LVDLVLR.LVD1LVL[3:0] bits.

#### Table 5.46 Power-On Reset Circuit and Voltage Detection Circuit Characteristics (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVCC0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                            | Item                                                          | Symbol                 | Min.           | Тур. | Max. | Unit                        | Test Conditions                            |  |

|--------------------------------------------|---------------------------------------------------------------|------------------------|----------------|------|------|-----------------------------|--------------------------------------------|--|

| Voltage detection level                    | Voltage detection circuit                                     | V <sub>det2_0</sub>    | 2.71           | 2.90 | 3.09 | V                           | Figure 5.61                                |  |

|                                            | (LVD2)*1                                                      | V <sub>det2_1</sub>    | 2.43           | 2.60 | 2.77 |                             | At falling edge VCC                        |  |

|                                            |                                                               | V <sub>det2_2</sub>    | 1.87 2.00 2.13 |      |      |                             |                                            |  |

|                                            |                                                               | V <sub>det2_3</sub> *2 | 1.69           | 1.80 | 1.91 |                             |                                            |  |

| Wait time after power-on                   | At normal startup*3                                           | t <sub>POR</sub>       | _              | 9.1  | —    | ms                          | Figure 5.59                                |  |

| reset cancellation                         | During fast startup time*4                                    | t <sub>POR</sub>       | _              | 1.6  | —    |                             |                                            |  |

| Wait time after voltage monitoring 1 reset | Power-on voltage monitoring<br>1 reset disabled* <sup>3</sup> | t <sub>LVD1</sub>      | _              | 568  | —    | μs                          | Figure 5.60                                |  |

| cancellation                               | Power-on voltage monitoring<br>1 reset enabled* <sup>4</sup>  |                        | _              | 100  | —    |                             |                                            |  |

| Wait time after voltage mo                 | nitoring 2 reset cancellation                                 | t <sub>LVD2</sub>      |                | 100  | —    | μs                          | Figure 5.61                                |  |

| Response delay time                        |                                                               | t <sub>det</sub>       | _              | —    | 350  | μs                          | Figure 5.58                                |  |

| Minimum VCC down time*                     | 5                                                             | t <sub>VOFF</sub>      | 350            | —    | —    | μs                          | Figure 5.58,<br>VCC = 1.0 V or above       |  |

| Power-on reset enable time                 |                                                               | t <sub>W(POR)</sub>    | 1              | —    | —    | ms                          | Figure 5.59,<br>VCC = below 1.0 V          |  |

| LVD operation stabilization                | n time (after LVD is enabled)                                 | Td <sub>(E-A)</sub>    | _              | —    | 300  | μs                          | Figure 5.60, Figure 5.61                   |  |

| Hysteresis width (LVD1 and LVD2)           |                                                               | V <sub>LVH</sub>       | _              | 70   | —    | mV                          | Vdet1_4 selected                           |  |

|                                            |                                                               | _                      | 60             | —    |      | Vdet1_5 to 9, LVD2 selected |                                            |  |

|                                            |                                                               |                        | _              | 50   | —    |                             | When selection is from among Vdet1_A to B. |  |

|                                            |                                                               |                        | —              | 40   | —    |                             | When selection is from among Vdet1_C to D. |  |

Note: • These characteristics apply when noise is not superimposed on the power supply. When a setting is made so that the voltage detection level overlaps with that of the voltage detection circuit (LVD1), it cannot be specified which of LVD1 and LVD2 is used for voltage detection.

Note 1. n in the symbol Vdet2\_n denotes the value of the LVDLVLR.LVD2LVL[3:0] bits.

Note 2. Vdet2\_3 selection can be used only when the CMPA2 pin input voltage is selected and cannot be used when the power supply voltage (VCC) is selected.

Note 3. When OFS1.(STUPLVD1REN, FASTSTUP) = 11b.

Note 4. When OFS1.(STUPLVD1REN, FASTSTUP) ≠ 11b.

Note 5. The minimum VCC down time indicates the time when VCC is below the minimum value of voltage detection levels  $V_{POR}$ ,  $V_{det0}$ ,  $V_{det1}$ , and  $V_{det2}$  for the POR/LVD.

## 5.11 E2 DataFlash Characteristics

### Table 5.51 E2 DataFlash Characteristics (1)

| Item                          |                                          | Symbol            | Min.                | Тур.                | Max. | Unit  | Conditions |

|-------------------------------|------------------------------------------|-------------------|---------------------|---------------------|------|-------|------------|

| Reprogramming/erasure cycle*1 |                                          | N <sub>DPEC</sub> | 100000              | 1000000             | _    | Times |            |

| Data hold time                | After 10000 times of N <sub>DPEC</sub>   | t <sub>DDRP</sub> | 20*2, *3            | —                   |      | Year  | Ta = +85°C |

|                               | After 100000 times of N <sub>DPEC</sub>  |                   | 5* <sup>2, *3</sup> | —                   |      | Year  |            |

|                               | After 1000000 times of N <sub>DPEC</sub> |                   | _                   | 1* <sup>2, *3</sup> | _    | Year  | Ta = +25°C |

Note 1. The reprogram/erase cycle is the number of erasing for each block. When the reprogram/erase cycle is n times (n = 100000), erasing can be performed n times for each block. For instance, when 1-byte programming is performed 1000 times for different addresses in 1-byte block and then the entire block is erased, the reprogram/erase cycle is counted as one. However, programming the same address for several times as one erasing is not enabled (overwriting is prohibited).

programming the same address for several times as one erasing is not enabled (overwriting is prohibited). Note 2. Characteristics when using the flash memory programmer and the self-programming library provided from Renesas Electronics.

Note 3. These results are obtained from reliability testing.

# Table 5.52 E2 DataFlash Characteristics (2) : high-speed operating mode

Conditions:  $2.7 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 2.7 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}$

Temperature range for the programming/erasure operation:  $T_a = -40$  to  $+105^{\circ}C$

| Item                    |                              | Symbol             | FCL  | K = 1 MHz |      | FCL  | Unit |       |      |

|-------------------------|------------------------------|--------------------|------|-----------|------|------|------|-------|------|

| iten                    | 1                            | Symbol             | Min. | Тур.      | Max. | Min. | Тур. | Max.  | Unit |

| Programming time        | 1-byte                       | t <sub>DP1</sub>   | _    | 86        | 761  | _    | 40.5 | 374   | μs   |

| Erasure time            | 1-Kbyte                      | t <sub>DE1K</sub>  | _    | 17.4      | 456  | —    | 6.15 | 228   | ms   |

|                         | 8-Kbyte                      | t <sub>DE8K</sub>  | _    | 60.4      | 499  | —    | 9.3  | 231   | ms   |

| Blank check time        | 1-byte                       | t <sub>DBC1</sub>  | _    | _         | 48   | —    | —    | 15.9  | μs   |

|                         | 1-Kbyte                      | t <sub>DBC1K</sub> | _    | _         | 1.58 | —    | —    | 0.127 | μs   |

| Erase operation forcibl | e stop time                  | t <sub>DSED</sub>  | _    | _         | 21.5 | —    | —    | 12.8  | μs   |

| DataFlash STOP recov    | DataFlash STOP recovery time |                    | 5    | —         | —    | 5    | —    | —     | μs   |

Note: Does not include the time until each operation of the flash memory is started after instructions are executed by software.

The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note: • The frequency accuracy of FCLK should be ±3.5%. Confirm the frequency accuracy of the clock source.

# Table 5.53E2 DataFlash Characteristics (3): middle-speed operating mode

Conditions:  $1.8 V \le VCC \le 3.6 V$ ,  $1.8 V \le AVSS0 \le 3.6 V$ ,  $VSS = AVSS0 = VSS_USB = 0 V$

Temperature range for the programming/erasure operation:  $T_a = -40$  to +85°C

| Item                     |           | Symbol             | FCL  | K = 1 MHz |      | FCL  | Unit |       |      |

|--------------------------|-----------|--------------------|------|-----------|------|------|------|-------|------|

| liem                     |           | Symbol             | Min. | Тур.      | Max. | Min. | Тур. | Max.  | Unit |

| Programming time         | 1-byte    | t <sub>DP1</sub>   | —    | 126       | 1160 | —    | 85.4 | 818   | μs   |

| Erasure time             | 1-Kbyte   | t <sub>DE1K</sub>  | —    | 17.5      | 457  | —    | 7.76 | 259   | ms   |

|                          | 8-Kbyte   | t <sub>DE8K</sub>  | —    | 60.5      | 500  | _    | 16.7 | 267.6 | ms   |

| Blank check time         | 1-byte    | t <sub>DBC1</sub>  | —    | _         | 78   | _    | —    | 50    | μs   |

|                          | 1-Kbyte   | t <sub>DBC1K</sub> | —    | _         | 1.61 | _    | —    | 0.369 | ms   |

| Erase operation forcible | stop time | t <sub>DSED</sub>  | —    |           | 33.5 | —    | _    | 25.5  | μs   |

| DataFlash STOP recover   | ery time  | t <sub>DSTOP</sub> | 720  |           | _    | 720  | _    | _     | ns   |

Note: • Does not include the time until each operation of the flash memory is started after instructions are executed by software. Note: • The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below

4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note: • The frequency accuracy of FCLK should be ±3.5%. Confirm the frequency accuracy of the clock source.

**REVISION HISTORY**

# **RX111 Group Datasheet**

| _    | _            |             | Description                                                                                                            |

|------|--------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| Rev. | Date         | Page        | Summary                                                                                                                |

| 0.60 | Apr 15, 2013 |             | First edition, issued                                                                                                  |

| 0.90 | May 15, 2013 | Features    |                                                                                                                        |

|      |              | 1           | Changed                                                                                                                |

|      |              | 1. Overviev |                                                                                                                        |

|      |              | 2 to 4      | Table 1.1 Outline of Specifications changed                                                                            |

|      |              | 10 to 12    | Table 1.4 Pin Functions changed                                                                                        |

|      |              | 13          | Figure 1.3 Pin Assignments of the 64-Pin LQFP changed                                                                  |

|      |              | 14          | Figure 1.4 Pin Assignments of the 64-Pin WFLGA changed                                                                 |

|      |              | 15          | Figure 1.5 Pin Assignments of the 48-Pin LQFP/HWQFN changed                                                            |

|      |              | 18, 19      | Table 1.5 List of Pins and Pin Functions (64-Pin LQFP) changed, Note 1 added                                           |

|      |              | 20, 21      | Table 1.6 List of Pins and Pin Functions (64-Pin WFLGA) changed, Note 1 added                                          |

|      |              | 22, 23      | Table 1.7 List of Pins and Pin Functions (48-Pin LQFP/HWQFN) changed, Note 1 added                                     |

|      |              | 24, 25      | Table 1.8 List of Pins and Pin Functions (40-Pin HWQFN) changed, Note 1 added                                          |

|      |              | 26          | Table 1.9 List of Pins and Pin Functions (36-Pin WFLGA) changed, Note 1 added                                          |

|      |              | 4. I/O Regi |                                                                                                                        |

|      |              | 33 to 48    | Table 5.1 List of I/O Registers (Address Order) changed                                                                |

| 1.00 | Jun 19. 2013 | 1. Overviev |                                                                                                                        |

|      |              | 9           | Figure 1.2 Block Diagram changed                                                                                       |

|      |              | 20, 21      | Table 1.6 List of Pins and Pin Functions (64-Pin WFLGA) changed                                                        |

|      |              | 26          | Table 1.9 List of Pins and Pin Functions (36-Pin WFLGA) changed                                                        |

|      |              | 4. I/O Regi |                                                                                                                        |

|      |              | 33 to 48    | Table 4.1 List of I/O Registers (Address Order) changed                                                                |

|      |              |             | al Characteristics                                                                                                     |