Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, USB OTG                                              |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                      |

| Data Converters            | A/D 14x12b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f51115adfk-3a |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

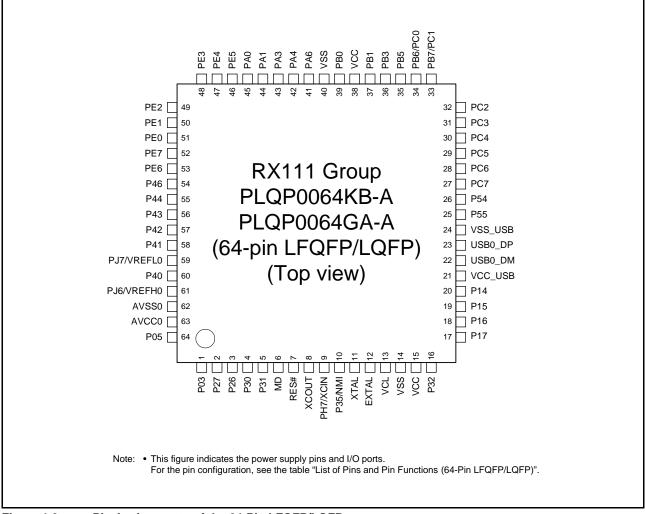

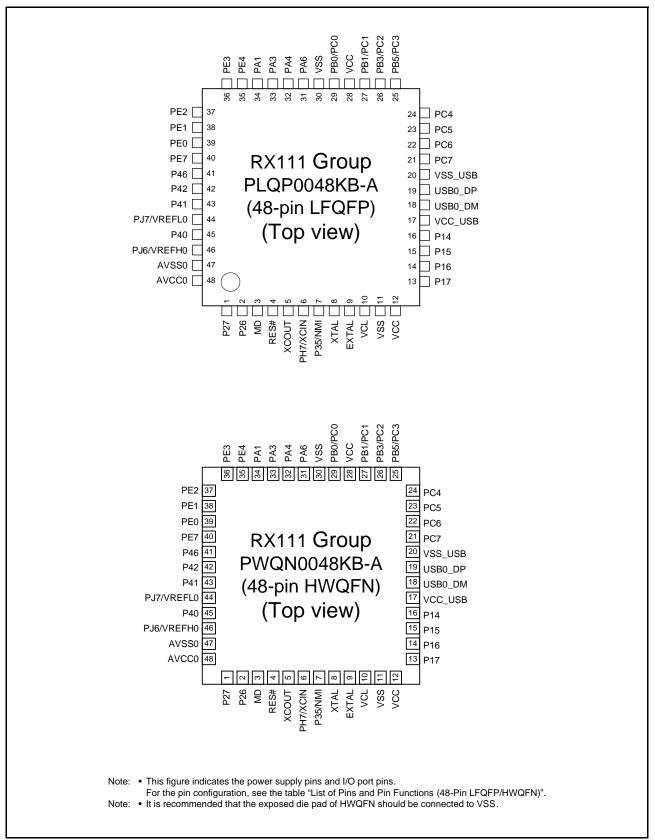

## 1.5 Pin Assignments

Figure 1.3 to Figure 1.7 show the pin assignments. Table 1.5 to Table 1.9 show the lists of pins and pin functions.

Figure 1.3 Pin Assignments of the 64-Pin LFQFP/LQFP

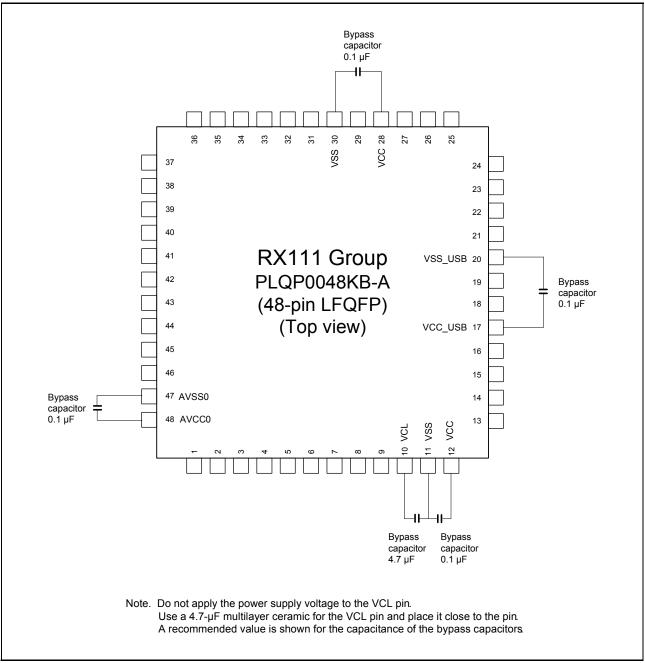

Figure 1.5 Pin Assignments of the 48-Pin LFQFP/HWQFN

RENESAS

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, POE, RTC)         | Communication<br>(SCIe, SCIf, RSPI, RIIC, USB)                                 | Others       |

|------------|-------------------------------------------|----------|-----------------------------------|--------------------------------------------------------------------------------|--------------|

| F2         |                                           | P32      | MTIOC0C/RTCOUT                    |                                                                                | IRQ2         |

| F3         | UPSEL                                     | P35      |                                   |                                                                                | NMI          |

| F4         | UB#                                       | P14      | MTIOC0A/MTIOC3A/<br>MTCLKA        | CTS1#/RTS1#/SS1#/TXD12/<br>TXDX12/SIOX12/SMOSI12/<br>SSDA12/SSLA0/USB0_OVRCURA | IRQ4         |

| F5         |                                           | P54      | MTIOC4B                           |                                                                                |              |

| F6         |                                           | PC7      | MTIOC3A/MTCLKB                    | TXD1/SMOSI1/SSDA1/MISOA/<br>USB0_OVRCURB                                       | CACREF       |

| F7         |                                           | PC4      | MTCLKC/MTIOC3D/POE0#              | SCK5/SSLA0/USB0_VBUSEN/<br>USB0_VBUS*1                                         | IRQ2/CLKOUT  |

| F8         |                                           | PB5      | MTIOC1B/MTIOC2A/POE1#             |                                                                                |              |

| G1         | VCL                                       |          |                                   |                                                                                |              |

| G2         |                                           | P17      | MTIOC0C/MTIOC3A/<br>MTIOC3B/POE8# | SCK1/MISOA/SDA0/RXD12/<br>RXDX12/SMISO12/SSCL12                                | IRQ7         |

| G3         |                                           | P16      | MTIOC3C/MTIOC3D/<br>RTCOUT        | TXD1/SMOSI1/SSDA1/SCL0/<br>MOSIA/USB0_VBUSEN/<br>USB0_OVRCURB/USB0_VBUS        | IRQ6/ADTRG0# |

| G4         |                                           | P15      | MTIOC0B/MTCLKB                    | RXD1/SMISO1/SSCL1/RSPCKA                                                       | IRQ5/CLKOUT  |

| G5         |                                           | PC6      | MTIOC3C/MTCLKA                    | RXD1/SMISO1/SSCL1/MOSIA/<br>USB0_EXICEN                                        |              |

| G6         |                                           | PC5      | MTIOC3B/MTCLKD                    | SCK1/RSPCKA/USB0_ID                                                            |              |

| G7         |                                           | PC3      | MTIOC4D                           | TXD5/SMOSI5/SSDA5                                                              |              |

| G8         |                                           | PB6/PC0  | MTIOC3D                           |                                                                                |              |

| H1         | VSS                                       |          |                                   |                                                                                |              |

| H2         | VCC                                       |          |                                   |                                                                                |              |

| H3         | VCC_USB                                   |          |                                   |                                                                                |              |

| H4         |                                           |          |                                   | USB0_DM                                                                        |              |

| H5         |                                           |          |                                   | USB0_DP                                                                        |              |

| H6         | VSS_USB                                   |          |                                   |                                                                                |              |

| H7         |                                           | PC2      | MTIOC4B                           | RXD5/SMISO5/SSCL5/SSLA3                                                        |              |

| H8         |                                           | PB7/PC1  | MTIOC3B                           |                                                                                |              |

Table 1.6

List of Pins and Pin Functions (64-Pin WFLGA) (2/2)

Note 1. Not 5 V tolerant.

Note 2. The power source of the I/O buffer for these pins is AVCC0.

## 2. CPU

Figure 2.1 shows the register set of the CPU.

|                       | R15                      |                                                                                                      |    |

|-----------------------|--------------------------|------------------------------------------------------------------------------------------------------|----|

| Control regist<br>b31 | ISP<br>USP<br>INTB<br>PC | (Interrupt stack pointer)<br>(User stack pointer)<br>(Interrupt table register)<br>(Program counter) | b( |

|                       | PSW                      | (Processor status word)                                                                              |    |

|                       | BPC                      | (Backup PC)                                                                                          |    |

|                       | BPSW                     | (Backup PSW)                                                                                         |    |

|                       |                          |                                                                                                      |    |

## 5. Electrical Characteristics

## 5.1 Absolute Maximum Ratings

#### Table 5.1 Absolute Maximum Ratings

Conditions: VSS = AVSS0 = VREFL0 = VSS\_USB = 0 V

| Item                           |                                          | Symbol           | Value                                                                                                          | Unit |  |

|--------------------------------|------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------|------|--|

| Power supply voltag            | e                                        | VCC, VCC_USB     | -0.3 to +4.6                                                                                                   | V    |  |

| Input voltage                  | Ports for 5 V tolerant*1                 | V <sub>in</sub>  | -0.3 to +6.5                                                                                                   | V    |  |

|                                | Ports P40 to P44, P46,<br>ports PJ6, PJ7 | V <sub>in</sub>  | -0.3 to AVCC0 +0.3                                                                                             | V    |  |

|                                | Ports other than above                   | V <sub>in</sub>  | -0.3 to VCC +0.3                                                                                               | V    |  |

| Reference power supply voltage |                                          | VREFH0           | -0.3 to AVCC0 +0.3                                                                                             | V    |  |

| Analog power supply            | y voltage                                | AVCC0            | -0.3 to +4.6                                                                                                   |      |  |

| Analog input voltage           |                                          | V <sub>AN</sub>  | -0.3 to AVCC0 + 0.3<br>(when AN000 to AN004 and AN006 used)<br>-0.3 to VCC + 0.3<br>(when AN008 to AN015 used) | V    |  |

| Operating temperature*2        |                                          | T <sub>opr</sub> | -40 to +85<br>-40 to +105                                                                                      | °C   |  |

| Storage temperature            | 9                                        | T <sub>stg</sub> | -55 to +125                                                                                                    | °C   |  |

Caution: Permanent damage to the MCU may result if absolute maximum ratings are exceeded.

To preclude any malfunctions due to noise interference, insert capacitors of high frequency characteristics between the VCC and VSS pins, between the AVCC0 and AVSS0 pins, between the VCC\_USB and VSS\_USB pins, and between the VREFH0 and VREFL0 pins. Place capacitors of about 0.1  $\mu$ F as close as possible to every power supply pin and use the shortest and heaviest possible traces. Also, connect capacitors as stabilization capacitance.

Connect the VCL pin to a VSS pin via a 4.7 µF capacitor. The capacitor must be placed close to the pin, refer to section 5.12.1, Connecting VCL Capacitor and Bypass Capacitors.

Do not input signals or an I/O pull-up power supply to ports other than 5-V tolerant ports while the device is not powered. The current injection that results from input of such a signal or I/O pull-up may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements.

If input voltage (within the specified range from -0.3 to + 6.5V) is applied to 5-V tolerant ports, it will not cause problems such as damage to the MCU.

Note 1. Ports P16, P17, PA6, and PB0 are 5 V tolerant. Note 2. The upper limit of operating temperature is 85°C or 105°C, depending on the product. For details, refer to 1.2 List of Products.

| Table 5.2 | <b>Operating Conditions</b> |

|-----------|-----------------------------|

|-----------|-----------------------------|

| Item                         | Symbol      | Conditions        | Min. | Тур. | Max.  | Unit |

|------------------------------|-------------|-------------------|------|------|-------|------|

| Power supply voltages        | VCC*1       | When USB not used | 1.8  | —    | 3.6   | V    |

|                              |             | When USB used     | 3.0  | —    | 3.6   | V    |

|                              | VSS         |                   | _    | 0    | —     | V    |

| USB power supply voltages    | VCC_USB     |                   | _    | VCC  | —     | V    |

|                              | VSS_USB     |                   |      | 0    | —     | V    |

| Analog power supply voltages | AVCC0*1, *2 |                   | 1.8  | —    | 3.6   | V    |

|                              | AVSS0       |                   | _    | 0    | —     | V    |

|                              | VREFH0      |                   | 1.8  | —    | AVCC0 | V    |

|                              | VREFL0      |                   | _    | 0    | —     | V    |

Note 1. When powering on AVCC0 and VCC, power them on at the same time or VCC first.

Note 2. For details, refer to section 30.7.10, Voltage Range of Analog Power Supply Pins in the User's Manual: Hardware.

### [128-Kbyte or less flash memory]

Table 5.7DC Characteristics (5) (1/2)

Conditions: 1.8 V  $\leq$  VCC = VCC\_USB  $\leq$  3.6 V, 1.8 V  $\leq$  AVSS0  $\leq$  3.6 V, VSS = AVSS0 = VSS\_USB = 0 V, T<sub>a</sub> = -40 to +105°C

|           |                 | It                                                | em                                                |               | Symbol          | Тур<br>*4   | Max | Unit | Test<br>Conditions |

|-----------|-----------------|---------------------------------------------------|---------------------------------------------------|---------------|-----------------|-------------|-----|------|--------------------|

| Supply    | High-speed      | Normal                                            | No peripheral operation*2                         | ICLK = 32 MHz | I <sub>CC</sub> | 3.2         |     | mA   |                    |

| current*1 | operating mode  | operating<br>mode                                 |                                                   | ICLK = 16 MHz |                 | 2.2         | _   |      |                    |

|           |                 | mode                                              |                                                   | ICLK = 8 MHz  |                 | 1.7         | _   |      |                    |

|           |                 |                                                   | All peripheral operation:                         | ICLK = 32 MHz |                 | 10.6        | _   |      |                    |

|           |                 |                                                   | Normal* <sup>3</sup>                              | ICLK = 16 MHz |                 | 6.1         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  |                 | 3.7         | _   |      |                    |

|           |                 |                                                   | All peripheral operation:<br>Max.* <sup>3</sup>   | ICLK = 32 MHz |                 | _           | 24  |      |                    |

|           |                 | Sleep mode                                        | No peripheral operation*2                         | ICLK = 32 MHz |                 | 1.8         |     |      |                    |

|           |                 |                                                   |                                                   | ICLK = 16 MHz |                 | 1.4         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  |                 | 1.1         | _   |      |                    |

|           |                 |                                                   | All peripheral operation:                         | ICLK = 32 MHz |                 | 6.4         | _   |      |                    |

|           |                 |                                                   | Normal* <sup>3</sup>                              | ICLK = 16 MHz |                 | 3.7         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  |                 | 2.4         | _   |      |                    |

|           |                 | Deep sleep                                        | No peripheral operation*2                         | ICLK = 32 MHz |                 | 1.2         | _   |      |                    |

|           |                 | mode                                              |                                                   | ICLK = 16 MHz | -               | 1.0         |     |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  | -               | 0.90        |     |      |                    |

|           |                 |                                                   | All peripheral operation:                         | ICLK = 32 MHz |                 | 4.6         | _   |      |                    |

|           |                 |                                                   | Normal* <sup>3</sup>                              | ICLK = 16 MHz |                 | 2.8         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  |                 | 1.8         | _   |      |                    |

|           |                 | Increase during                                   | flash rewrite*5                                   |               |                 | 2.5         | _   |      |                    |

|           | Middle-speed    | Normal                                            |                                                   | ICLK = 12 MHz |                 | 2.0         | _   | mA   |                    |

|           | operating modes | operating<br>mode                                 | All peripheral operation:<br>Normal* <sup>7</sup> | ICLK = 8 MHz  |                 | 1.3         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 1 MHz  |                 | 0.75        | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 12 MHz |                 | 4.9         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  |                 | 3.5         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 1 MHz  |                 | 1.2         | _   |      |                    |

|           |                 |                                                   | All peripheral operation:<br>Max.*7               | ICLK = 12 MHz | -               | _           | 11  |      |                    |

|           |                 | Sleep mode                                        | No peripheral operation*6                         | ICLK = 12 MHz |                 | 1.4         | —   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  |                 | 0.85        | —   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 1 MHz  |                 | 0.65        | _   |      |                    |

|           |                 |                                                   | All peripheral operation:                         | ICLK = 12 MHz |                 | 3.2         | _   |      |                    |

|           |                 |                                                   | Normal* <sup>7</sup>                              | ICLK = 8 MHz  |                 | 2.2         | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 1 MHz  |                 | 1.0         |     |      |                    |

|           |                 | Deep sleep                                        | No peripheral operation*6                         | ICLK = 12 MHz |                 | 1.2         | _   |      |                    |

|           |                 | mode                                              |                                                   | ICLK = 8 MHz  |                 | 0.70        | _   |      |                    |

|           |                 |                                                   |                                                   | ICLK = 1 MHz  |                 | 0.60        | _   |      |                    |

|           |                 | All peripheral operation:                         | ICLK = 12 MHz                                     |               | 2.5             | _           |     |      |                    |

|           |                 | All peripheral operation:<br>Normal* <sup>7</sup> |                                                   |               |                 |             |     |      |                    |

|           |                 |                                                   |                                                   | ICLK = 8 MHz  |                 | 1.8         | _   |      |                    |

|           |                 |                                                   |                                                   |               |                 | 1.8<br>0.90 |     |      |                    |

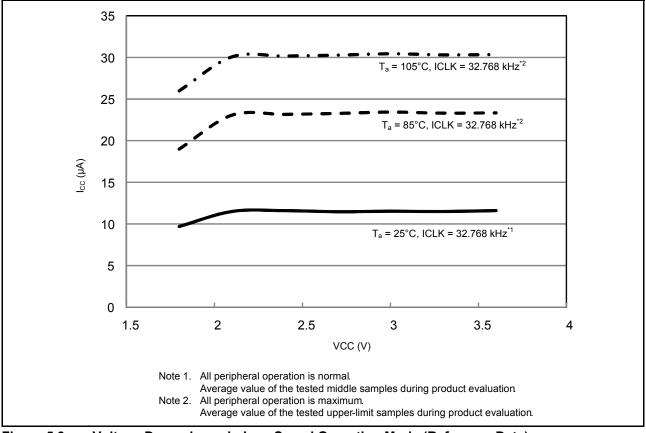

Figure 5.3 Voltage Dependency in Low-Speed Operating Mode (Reference Data)

#### Table 5.8DC Characteristics (6) (2/2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                  |                             |                                                        | Item                                                 | Symbol            | Typ<br>*4       | Max | Unit | Test<br>Conditions |  |

|------------------|-----------------------------|--------------------------------------------------------|------------------------------------------------------|-------------------|-----------------|-----|------|--------------------|--|

| Supply current*1 | rrent*1 operating operating |                                                        | No peripheral operation* <sup>8</sup>                | ICLK = 32.768 kHz | I <sub>CC</sub> | 4.3 | _    | μA                 |  |

| mode             | mode                        | All peripheral operation:<br>Normal* <sup>9, *10</sup> | ICLK = 32.768 kHz                                    |                   | 14.7            | -   |      |                    |  |

|                  |                             |                                                        | All peripheral operation:<br>Max.* <sup>9, *10</sup> | ICLK = 32.768kHz  |                 |     | 60   |                    |  |

|                  |                             | Sleep mode<br>Deep sleep<br>mode                       | No peripheral operation* <sup>8</sup>                | ICLK = 32.768 kHz |                 | 2.2 | _    |                    |  |

|                  |                             |                                                        | All peripheral operation:<br>Normal* <sup>9</sup>    | ICLK = 32.768 kHz | _               | 8.3 |      | -                  |  |

|                  |                             |                                                        | No peripheral operation* <sup>8</sup>                | ICLK = 32.768 kHz |                 | 1.7 | -    |                    |  |

|                  |                             |                                                        | All peripheral operation:<br>Normal* <sup>9</sup>    | ICLK = 32.768 kHz |                 | 6.7 | _    |                    |  |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL. FCLK and PCLK are set to divided by 64.

Note 3. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL. FCLK and PCLK are set to the same frequency as ICLK.

Note 4. Values when VCC = 3.3 V.

Note 5. This is the increase for programming or erasure of the ROM or E2 DataFlash during program execution.

Note 6. Clock supply to the peripheral functions is stopped. The clock source is PLL when ICLK = 12 MHz, and HOCO otherwise. FCLK and PCLK are set to divided by 64.

Note 7. Clocks are supplied to the peripheral functions. The clock source is PLL when ICLK = 12 MHz, and HOCO otherwise. FCLK and PCLK are set to the same frequency as ICLK.

Note 8. Clock supply to the peripheral functions is stopped. The clock source is the sub-clock oscillator. FCLK and PCLK are set to divided by 64.

Note 9. Clocks are supplied to the peripheral functions. The clock source is the sub-clock oscillator. FCLK and PCLK are set to the same frequency as ICLK.

Note 10. Values when the MSTPCRA.MSTPA17 bit (12-bit A/D converter module stop bit) is set to "transition to the module stop state is made".

#### [128-Kbyte or less flash memory]

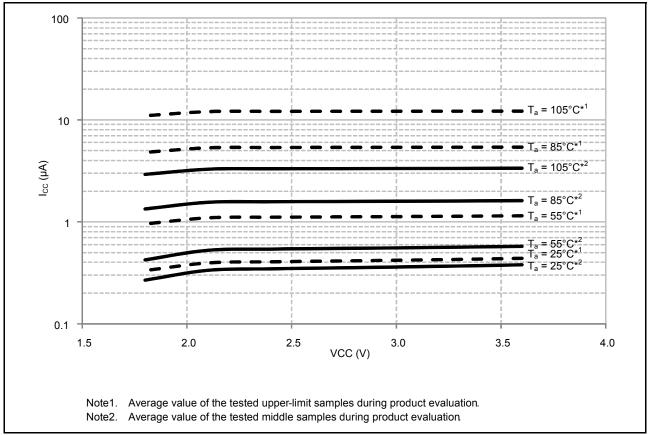

#### Table 5.9DC Characteristics (7)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|           | Item                         |                        | Symbol          | Typ.* <sup>3</sup> | Max.  | Unit | Test Conditions        |

|-----------|------------------------------|------------------------|-----------------|--------------------|-------|------|------------------------|

| Supply    | Software standby             | T <sub>a</sub> = 25°C  | I <sub>CC</sub> | 0.35               | 0.53  | μA   |                        |

| current*1 | mode* <sup>2</sup>           | T <sub>a</sub> = 55°C  |                 | 0.58               | 1.45  |      |                        |

|           |                              | T <sub>a</sub> = 85°C  |                 | 1.60               | 7.30  |      |                        |

|           |                              | T <sub>a</sub> = 105°C |                 | 3.30               | 16.50 |      |                        |

|           | Increment for RTC of         | peration*4             |                 | 0.31               | _     |      | RCR3.RTCDV[2:0] = 010b |

|           |                              |                        |                 | 1.09               | _     |      | RCR3.RTCDV[2:0] = 100b |

|           | Increment for IWDT operation |                        |                 | 0.37               |       |      |                        |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. The IWDT and LVD are stopped.

Note 3. VCC = 3.3 V.

Note 4. Includes the oscillation circuit.

Figure 5.7 Voltage Dependency in Software Standby Mode (Reference Data)

#### Table 5.12 DC Characteristics (10)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                     | Item                                                                                                                                                                                                                                                                                                              | Symbol               | Min. | Typ.* <sup>7</sup>                      | Max. | Unit | Test<br>Conditions |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----------------------------------------|------|------|--------------------|

| Analog power                        | During A/D conversion (at high-speed conversion)                                                                                                                                                                                                                                                                  | I <sub>AVCC</sub>    | —    | 0.7                                     | 1.2  | mA   |                    |

| supply current                      | Waiting for A/D (all units)                                                                                                                                                                                                                                                                                       |                      |      | —                                       | 0.3  | μA   |                    |

|                                     | During D/A conversion (per channel)*5                                                                                                                                                                                                                                                                             |                      |      | —                                       | 1.5  | mA   |                    |

| Reference                           | During A/D conversion (at high-speed conversion)                                                                                                                                                                                                                                                                  | I <sub>REFH0</sub>   |      | 25                                      | 52   | μA   |                    |

| power supply<br>current             | Waiting for A/D conversion (all units)                                                                                                                                                                                                                                                                            |                      |      | —                                       | 60   | nA   |                    |

| Temperature<br>sensor* <sup>6</sup> |                                                                                                                                                                                                                                                                                                                   | I <sub>TEMP</sub>    | —    | 75                                      | -    | μA   |                    |

| LDV1, 2                             | Per channel                                                                                                                                                                                                                                                                                                       | I <sub>LVD</sub>     | —    | 0.15                                    | —    | μA   |                    |

| USB<br>operating<br>current         | <ul> <li>During USB communication operation under the following settings and conditions</li> <li>Host controller operation is set to full-speed mode Bulk OUT transfer (64 bytes) × 1, bulk IN transfer (64 bytes) × 1</li> <li>Connect peripheral devices via a 1-meter USB cable from the USB port.</li> </ul>  | I <sub>USBH</sub> *2 | _    | 4.3<br>(VCC)<br>0.9<br>(VCC_USB)<br>*4  | _    | mA   |                    |

|                                     | <ul> <li>During USB communication operation under the following settings and conditions</li> <li>Function controller operation is set to full-speed mode Bulk OUT transfer (64 bytes) × 1, bulk IN transfer (64 bytes) × 1</li> <li>Connect the host device via a 1-meter USB cable from the USB port.</li> </ul> | I <sub>USBF</sub> *2 |      | 3.6<br>(VCC)<br>1.1<br>(VCC_USB)<br>*4  |      | mA   |                    |

|                                     | <ul> <li>During suspended state under the following setting and conditions</li> <li>Function controller operation is set to full-speed mode<br/>(pull up the USB0_DP pin)</li> <li>Software standby mode</li> <li>Connect the host device via a 1-meter USB cable from the<br/>USB port.</li> </ul>               | I <sub>SUSP</sub> *3 |      | 0.35<br>(VCC)<br>170<br>(VCC_USB)<br>*4 | _    | μA   |                    |

Note 1. The reference power supply current is included in the power supply current value for D/A conversion.

Note 2. Current consumed only by the USB module.

Note 3. Includes the current supplied from the pull-up resistor of the USB0\_DP pin to the pull-down resistor of the host device, in addition to the current consumed by this MCU during the suspended state.

Note 4. When VCC = VCC\_USB = 3.3 V.

Note 5. The value of the current flowing to VCC.

Note 6. Current consumed by the power supply (VCC). Note 7. When VCC = AVCC0 = VCC\_USB = 3.3 V.

### Table 5.13DC Characteristics (11)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                | Symbol           | Min. | Тур. | Max. | Unit | Test Conditions |

|---------------------|------------------|------|------|------|------|-----------------|

| RAM standby voltage | V <sub>RAM</sub> | 1.8  | —    |      | V    |                 |

## 5.2.2 Standard I/O Pin Output Characteristics (2)

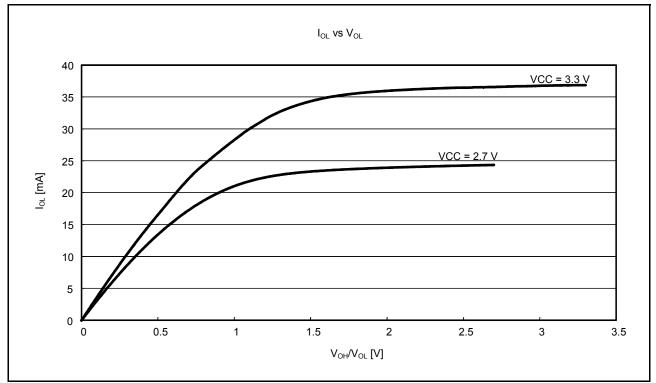

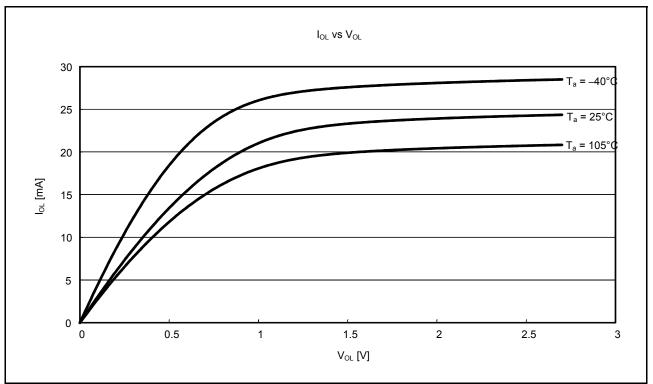

Figure 5.16 to Figure 5.18 show the characteristics of the RIIC output pin.

Figure 5.16 V<sub>OL</sub> and I<sub>OL</sub> Voltage Characteristics of RIIC Output Pin at T<sub>a</sub> = 25°C (Reference Data)

Figure 5.17 V<sub>OL</sub> and I<sub>OL</sub> Temperature Characteristics of RIIC Output Pin at VCC = 2.7 V (Reference Data)

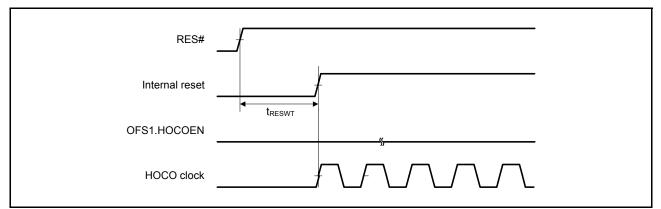

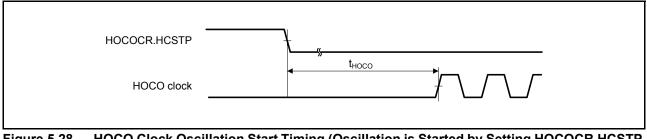

Figure 5.28 HOCO Clock Oscillation Start Timing (Oscillation is Started by Setting HOCOCR.HCSTP Bit)

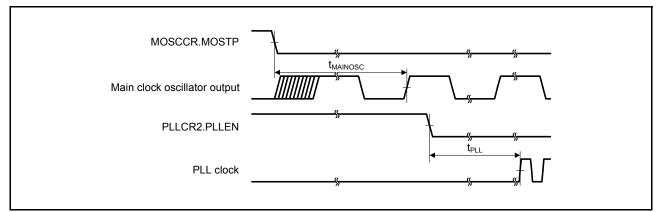

Figure 5.29 PLL Clock Oscillation Start Timing (PLL is Operated after Main Clock Oscillation Has Settled)

## 5.3.3 Timing of Recovery from Low Power Consumption Modes

#### Table 5.26 Timing of Recovery from Low Power Consumption Modes (1)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}$ ,  $1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}$ ,  $\text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}$ ,  $\text{T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                |                    | Item                                                | Symbol                                                        | Min.               | Тур. | Max. | Unit | Test<br>Conditions |             |

|--------------------------------|--------------------|-----------------------------------------------------|---------------------------------------------------------------|--------------------|------|------|------|--------------------|-------------|

| Recovery time<br>from software | High-speed<br>mode | Crystal connected to                                | Main clock oscillator<br>operating* <sup>2</sup>              | t <sub>SBYMC</sub> | _    | 2    | 3    | ms                 | Figure 5.34 |

| standby mode*1                 |                    | main clock<br>oscillator                            | Main clock oscillator and PLL circuit operating* <sup>3</sup> | t <sub>SBYPC</sub> |      | 2    | 3    | ms                 |             |

|                                |                    | External clock<br>input to main<br>clock oscillator | Main clock oscillator<br>operating* <sup>4</sup>              | t <sub>SBYEX</sub> | _    | 35   | 50   | μs                 |             |

|                                |                    |                                                     | Main clock oscillator and PLL circuit operating* <sup>5</sup> | t <sub>SBYPE</sub> |      | 70   | 95   | μs                 |             |

|                                |                    | Sub-clock oscillate                                 | Sub-clock oscillator operating                                |                    | -    | 650  | 800  | μs                 |             |

|                                |                    | HOCO clock oscill                                   | lator operating*6                                             | t <sub>SBYHO</sub> | _    | 40   | 55   | μs                 |             |

|                                |                    | LOCO clock oscill                                   | ator operating                                                | t <sub>SBYLO</sub> | _    | 40   | 55   | μs                 |             |

Note: When the division ratios of PCLKB, PCLKD, FCLK, and ICLK are all set to 1.

Note 1. The recovery time varies depending on the state of each oscillator when the WAIT instruction is executed. The recovery time when multiple oscillators are operating varies depending on the operating state of the oscillators that are not selected as the system clock source. This applies when only the oscillator listed in each item is operating and the other oscillators are stopped.

Note 2. When the frequency of the crystal is 20 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 04h. Note 3. When the frequency of PLL is 32 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 04h.

Note 4. When the frequency of the external clock is 20 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 00h. Note 5. When the frequency of PLL is 32 MHz.

When the main clock oscillator wait control register (MOSCWTCR) is set to 00h. Note 6. When the frequency of HOCO is 32 MHz.

When the high-speed clock oscillator wait control register (HOCOWTCR) is set to 05h.

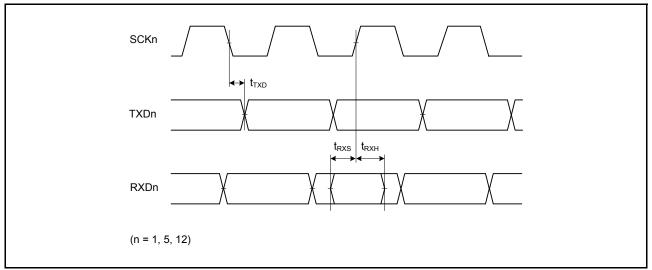

Figure 5.43 SCI Input/Output Timing: Clock Synchronous Mode

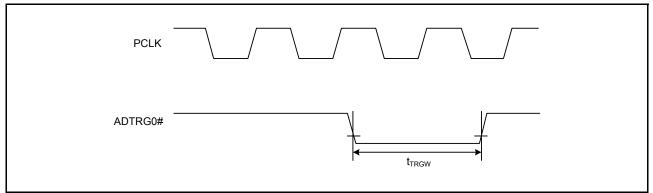

Figure 5.44 A/D Converter External Trigger Input Timing

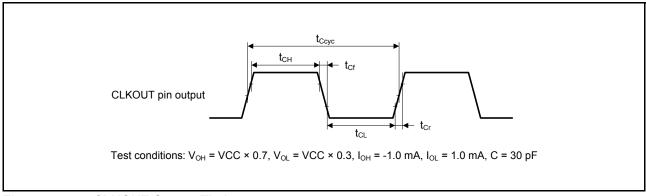

Figure 5.45 CLKOUT Output Timing

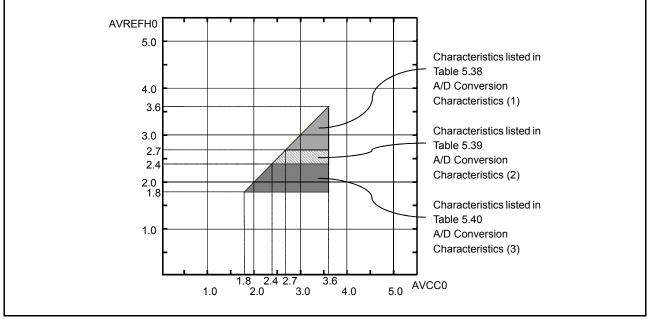

Figure 5.56 AVCC0 to AVREFH0 Voltage Range

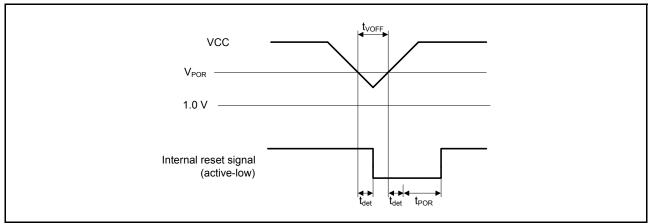

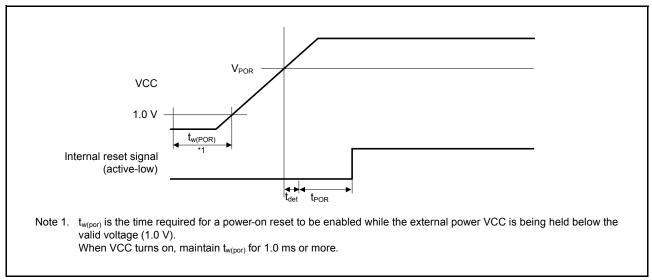

Figure 5.59 Power-On Reset Timing

#### Table 5.50 ROM (Flash Memory for Code Storage) Characteristics (3)

Middle-speed operating mode Conditions: 1.8 V ≤ VCC ≤ 3.6 V, 1.8 V ≤ AVSS0 ≤ 3.6 V, VSS = AVSS0 = VSS\_USB = 0 V Temperature range for the programming/erasure operation:  $T_a = -40$  to +85°C

| Item                                 |           | Symbol             | FC   | CLK = 1 MH | lz   |      | Unit |       |      |

|--------------------------------------|-----------|--------------------|------|------------|------|------|------|-------|------|

|                                      |           | Symbol             | Min. | Тур.       | Max. | Min. | Тур. | Max.  | Unit |

| Programming time                     | 4-byte    | t <sub>P4</sub>    |      | 143        | 1330 | _    | 96.8 | 932   | μs   |

| Erasure time                         | 1-Kbyte   | t <sub>E1K</sub>   |      | 8.3        | 269  | —    | 5.85 | 219   | ms   |

|                                      | 256-Kbyte | t <sub>E256K</sub> | _    | 407        | 928  | —    | 93   | 520   | ms   |

| Blank check time                     | 4-byte    | t <sub>BC4</sub>   |      | —          | 78   | _    | _    | 50    | μs   |

|                                      | 1-Kbyte   | t <sub>BC1K</sub>  |      | —          | 1.61 | —    | —    | 0.369 | ms   |

| Erase operation forcible stop time   |           | t <sub>SED</sub>   |      | —          | 33.6 | —    | —    | 25.6  | μs   |

| Start-up area switching setting time |           | t <sub>SAS</sub>   |      | 13.2       | 549  | —    | 7.6  | 445   | ms   |

| Access window time                   |           | t <sub>AWS</sub>   |      | 13.2       | 549  | —    | 7.6  | 445   | ms   |

| ROM mode transition wait time 1      |           | t <sub>DIS</sub>   | 2    | —          | —    | 2    | —    | —     | μs   |

| ROM mode transition wait time 2      |           | t <sub>MS</sub>    | 3    | —          |      | 3    | _    | —     | μs   |

Note: • Does not include the time until each operation of the flash memory is started after instructions are executed by software.

Note: • The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note: • The frequency accuracy of FCLK should be ±3.5%. Confirm the frequency accuracy of the clock source.

## 5.11 E2 DataFlash Characteristics

#### Table 5.51 E2 DataFlash Characteristics (1)

| Item                          |                                          | Symbol            | Min.                | Тур.                | Max. | Unit  | Conditions |

|-------------------------------|------------------------------------------|-------------------|---------------------|---------------------|------|-------|------------|

| Reprogramming/erasure cycle*1 |                                          | N <sub>DPEC</sub> | 100000              | 1000000             | _    | Times |            |

| Data hold time                | After 10000 times of N <sub>DPEC</sub>   | t <sub>DDRP</sub> | 20*2, *3            | —                   |      | Year  | Ta = +85°C |

|                               | After 100000 times of N <sub>DPEC</sub>  |                   | 5* <sup>2, *3</sup> | —                   |      | Year  |            |

|                               | After 1000000 times of N <sub>DPEC</sub> |                   | _                   | 1* <sup>2, *3</sup> | _    | Year  | Ta = +25°C |

Note 1. The reprogram/erase cycle is the number of erasing for each block. When the reprogram/erase cycle is n times (n = 100000), erasing can be performed n times for each block. For instance, when 1-byte programming is performed 1000 times for different addresses in 1-byte block and then the entire block is erased, the reprogram/erase cycle is counted as one. However, programming the same address for several times as one erasing is not enabled (overwriting is prohibited).

programming the same address for several times as one erasing is not enabled (overwriting is prohibited). Note 2. Characteristics when using the flash memory programmer and the self-programming library provided from Renesas Electronics.

Note 3. These results are obtained from reliability testing.

## Table 5.52 E2 DataFlash Characteristics (2) : high-speed operating mode

Conditions:  $2.7 \text{ V} \le \text{VCC} \le 3.6 \text{ V}, 2.7 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}$

Temperature range for the programming/erasure operation:  $T_a = -40$  to  $+105^{\circ}C$

| Item                               |         | Symbol             | FCL  | K = 1 MHz |      | FCL  | Unit |       |      |

|------------------------------------|---------|--------------------|------|-----------|------|------|------|-------|------|

|                                    |         | Symbol             | Min. | Тур.      | Max. | Min. | Тур. | Max.  | Unit |

| Programming time                   | 1-byte  | t <sub>DP1</sub>   | _    | 86        | 761  | _    | 40.5 | 374   | μs   |

| Erasure time                       | 1-Kbyte | t <sub>DE1K</sub>  | _    | 17.4      | 456  | —    | 6.15 | 228   | ms   |

|                                    | 8-Kbyte | t <sub>DE8K</sub>  | _    | 60.4      | 499  | —    | 9.3  | 231   | ms   |

| Blank check time                   | 1-byte  | t <sub>DBC1</sub>  | _    | _         | 48   | —    | —    | 15.9  | μs   |

|                                    | 1-Kbyte | t <sub>DBC1K</sub> | _    | _         | 1.58 | —    | —    | 0.127 | μs   |

| Erase operation forcible stop time |         | t <sub>DSED</sub>  | _    | _         | 21.5 | —    | —    | 12.8  | μs   |

| DataFlash STOP recovery time       |         | t <sub>DSTOP</sub> | 5    | —         | —    | 5    | —    | —     | μs   |

Note: Does not include the time until each operation of the flash memory is started after instructions are executed by software.

The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note: • The frequency accuracy of FCLK should be ±3.5%. Confirm the frequency accuracy of the clock source.

# Table 5.53E2 DataFlash Characteristics (3): middle-speed operating mode

Conditions:  $1.8 V \le VCC \le 3.6 V$ ,  $1.8 V \le AVSS0 \le 3.6 V$ ,  $VSS = AVSS0 = VSS_USB = 0 V$

Temperature range for the programming/erasure operation:  $T_a = -40$  to +85°C

| Item                               |         | Symbol             | FCL  | K = 1 MHz |      | FCL  | Unit |       |      |

|------------------------------------|---------|--------------------|------|-----------|------|------|------|-------|------|

|                                    |         | Symbol             | Min. | Тур.      | Max. | Min. | Тур. | Max.  | Onit |

| Programming time                   | 1-byte  | t <sub>DP1</sub>   | —    | 126       | 1160 | —    | 85.4 | 818   | μs   |

| Erasure time                       | 1-Kbyte | t <sub>DE1K</sub>  | —    | 17.5      | 457  | —    | 7.76 | 259   | ms   |

|                                    | 8-Kbyte | t <sub>DE8K</sub>  | —    | 60.5      | 500  | _    | 16.7 | 267.6 | ms   |

| Blank check time                   | 1-byte  | t <sub>DBC1</sub>  | —    | _         | 78   | _    | —    | 50    | μs   |

|                                    | 1-Kbyte | t <sub>DBC1K</sub> | —    | _         | 1.61 | _    | —    | 0.369 | ms   |

| Erase operation forcible stop time |         | t <sub>DSED</sub>  | —    |           | 33.5 | —    | _    | 25.5  | μs   |

| DataFlash STOP recovery time       |         | t <sub>DSTOP</sub> | 720  |           | _    | 720  | _    | _     | ns   |

Note: • Does not include the time until each operation of the flash memory is started after instructions are executed by software. Note: • The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below

4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note: • The frequency accuracy of FCLK should be ±3.5%. Confirm the frequency accuracy of the clock source.

Figure 5.64 Connecting Capacitors (48-pin LFQFP)

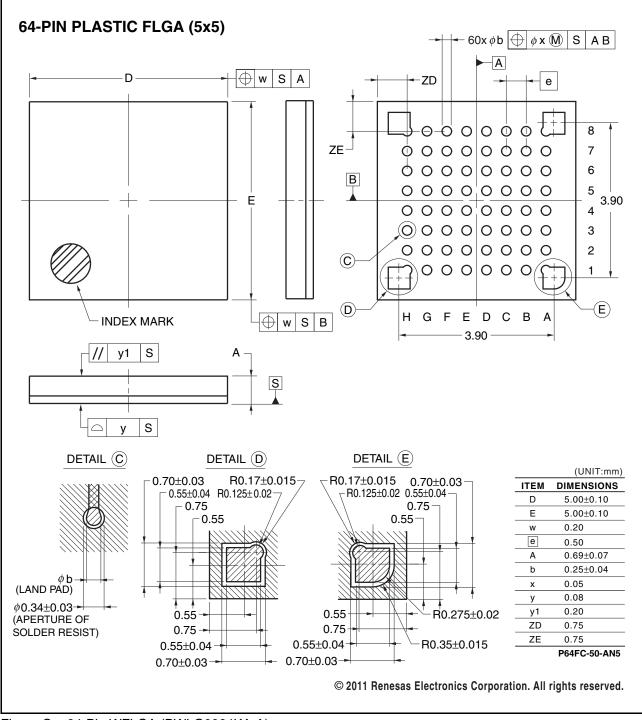

Figure C 64-Pin WFLGA (PWLG0064KA-A)