#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | RX                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 32MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, USB OTG                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 8K x 8                                                                            |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                       |

| Data Converters            | A/D 14x12b; D/A 2x8b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f51115adfm-yb2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Overview

## 1.1 Outline of Specifications

Table 1.1 lists the specifications, and Table 1.2 gives a comparison of the functions of the products in different packages.

Table 1.1 is for products with the greatest number of functions, so the number of peripheral modules and channels will differ in accordance with the package type. For details, see Table 1.2, Comparison of Functions for Different Packages.

| Classification        | Module/Function                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CPU                   | CPU                                            | <ul> <li>Maximum operating frequency: 32 MHz</li> <li>32-bit RX CPU</li> <li>Minimum instruction execution time: One instruction per clock cycle</li> <li>Address space: 4-Gbyte linear</li> <li>Register set</li> <li>General purpose: Sixteen 32-bit registers</li> <li>Control: Eight 32-bit registers</li> <li>Accumulator: One 64-bit register</li> <li>Basic instructions: 73</li> <li>DSP instructions: 9</li> <li>Addressing modes: 10</li> <li>Data arrangement<br/>Instructions: Little endian</li> <li>Data: Selectable as little endian or big endian</li> <li>On-chip 32-bit multiplier: 32-bit × 32-bit → 64-bit</li> <li>On-chip divider: 32-bit ÷ 32-bit → 32 bits</li> <li>Barrel shifter: 32 bits</li> </ul>                                                                                                                                        |  |  |  |  |

| Memory                | ROM                                            | <ul> <li>Capacity: 16 K /32 K /64 K /96 K /128 K /256 K /384 K /512 Kbytes</li> <li>32 MHz, no-wait memory access</li> <li>Programming/erasing method:<br/>Serial programming (asynchronous serial communication/USB communication), self-programming</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                       | RAM                                            | <ul> <li>Capacity: 8 K /10 K /16 K /32 K /64 Kbytes</li> <li>32 MHz, no-wait memory access</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                       | E2 DataFlash                                   | <ul> <li>Capacity: 8 Kbytes</li> <li>Number of erase/write cycles: 1,000,000 (typ)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| MCU operating mode    |                                                | Single-chip mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Clock                 | Clock generation circuit                       | <ul> <li>Main clock oscillator, sub-clock oscillator, low-speed on-chip oscillator, high-speed on-chip oscillator, PLL frequency synthesizer, and IWDT-dedicated on-chip oscillator</li> <li>Oscillation stop detection: Available</li> <li>Clock frequency accuracy measurement circuit (CAC)</li> <li>Independent settings for the system clock (ICLK), peripheral module clock (PCLK), and FlashIF clock (FCLK)</li> <li>The CPU and system sections such as other bus masters run in synchronization with the system clock (ICLK): 32 MHz (at max.)</li> <li>Peripheral modules run in synchronization with the PCLK: 32 MHz (at max.)</li> <li>The flash peripheral circuit runs in synchronization with the FCLK: 32 MHz (at max.)</li> <li>The ICLK frequency can only be set to FCLK, PCLKB, or PCLKD multiplied by n (n: 1, 2, 4, 8, 16, 32, 64).</li> </ul> |  |  |  |  |

| Resets                |                                                | RES# pin reset, power-on reset, voltage monitoring reset, independent watchdog timer reset, and software reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Voltage detection     | Voltage detection circuit<br>(LVDAa)           | When the voltage on VCC falls below the voltage detection level, an internal reset or internal interrupt is generated.     Voltage detection circuit 1 is capable of selecting the detection voltage from 10 levels     Voltage detection circuit 2 is capable of selecting the detection voltage from 4 levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Low power consumption | Low power consumption<br>functions             | <ul> <li>Module stop function</li> <li>Three low power consumption modes</li> <li>Sleep mode, deep sleep mode, and software standby mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                       | Function for lower operating power consumption | <ul> <li>Operating power control modes<br/>High-speed operating mode, middle-speed operating mode, and low-speed operating mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Interrupt             | Interrupt controller (ICUb)                    | <ul> <li>Interrupt vectors: 82</li> <li>External interrupts: 9 (NMI, IRQ0 to IRQ7 pins)</li> <li>Non-maskable interrupts: 4 (NMI pin, voltage monitoring 1 interrupt, voltage monitoring 2 interrupt, and IWDT interrupt)</li> <li>16 levels specifiable for the order of priority</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

Table 1.1Outline of Specifications (1/3)

| Classification        | Module/Function                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                       | JSB 2.0 host/function<br>module (USBc) | <ul> <li>USB Device Controller (UDC) and transceiver for USB 2.0 are incorporated.</li> <li>Host (32-Kbyte or more ROM)/function module: 1 port</li> <li>Compliant with USB version 2.0</li> <li>Transfer speed: Full-speed (12 Mbps), low-speed (1.5 Mbps)</li> <li>OTG (On-The-Go) is supported.</li> <li>Isochronous transfer is supported.</li> <li>BC (Battery Charger) is supported.</li> </ul>                                                                            |  |  |  |  |  |

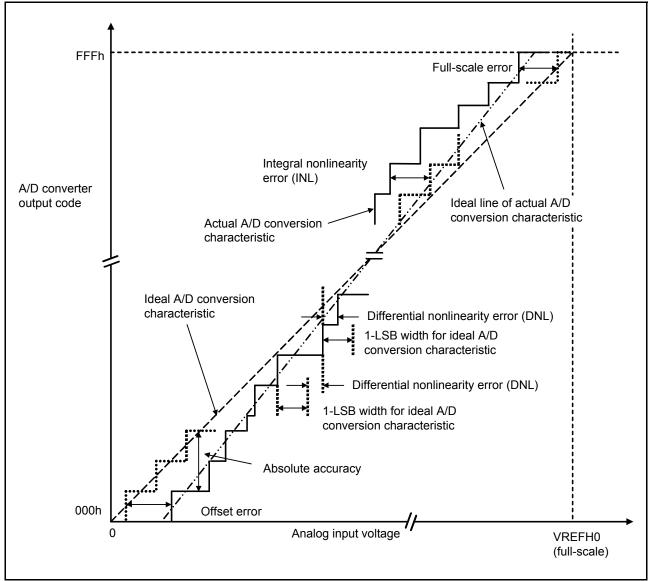

| 12-bit A/D converter  | (S12ADb)                               | <ul> <li>1 unit (1 unit × 14 channels)</li> <li>12-bit resolution</li> <li>Minimum conversion time: 1.0 µs per channel when the ADCLK is operating at 32 MHz</li> <li>Operating modes<br/>Scan mode (single scan mode, continuous scan mode, and group scan mode)</li> <li>Double trigger mode (duplication of A/D conversion data)</li> <li>A/D conversion start conditions<br/>A software trigger, a trigger from a timer (MTU), an external trigger signal, or ELC</li> </ul> |  |  |  |  |  |

| Temperature sensor    | (TEMPSA)                               | <ul> <li>1 channel</li> <li>The voltage of the temperature is converted into a digital value by the 12-bit A/D converter.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| D/A converter (DA)    |                                        | <ul> <li>2 channels</li> <li>8-bit resolution</li> <li>Output voltage: 0 V to VCC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CRC calculator (CRC)  |                                        | <ul> <li>CRC code generation for arbitrary amounts of data in 8-bit units</li> <li>Select any of three generating polynomials:<br/>X<sup>8</sup> + X<sup>2</sup> + X + 1, X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1, or X<sup>16</sup> + X<sup>12</sup> + X<sup>5</sup> + 1</li> <li>Generation of CRC codes for use with LSB first or MSB first communications is selectable.</li> </ul>                                                                              |  |  |  |  |  |

| Data operation circui | t (DOC)                                | Comparison, addition, and subtraction of 16-bit data                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Unique ID             |                                        | 32-byte ID code for the MCU                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Power supply voltage  | es/Operating frequencies               | VCC = 1.8 to 2.4 V: 8 MHz, VCC = 2.4 to 2.7 V: 16 MHz, VCC = 2.7 to 3.6 V: 32 MHz                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Supply current        |                                        | 3.2 mA at 32 MHz (typ.)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Operating temperatu   | re range                               | D version: -40 to +85°C, G version: -40 to +105°C                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

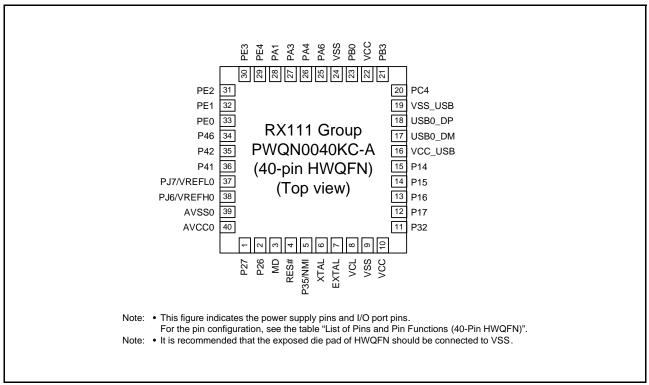

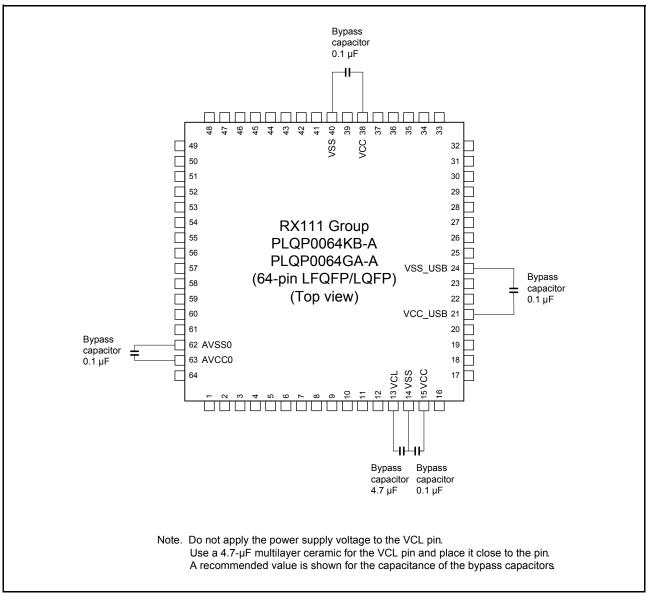

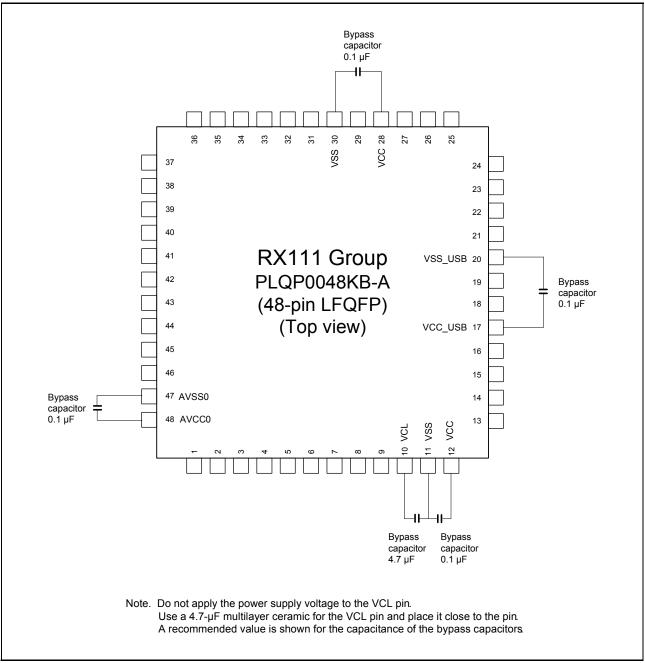

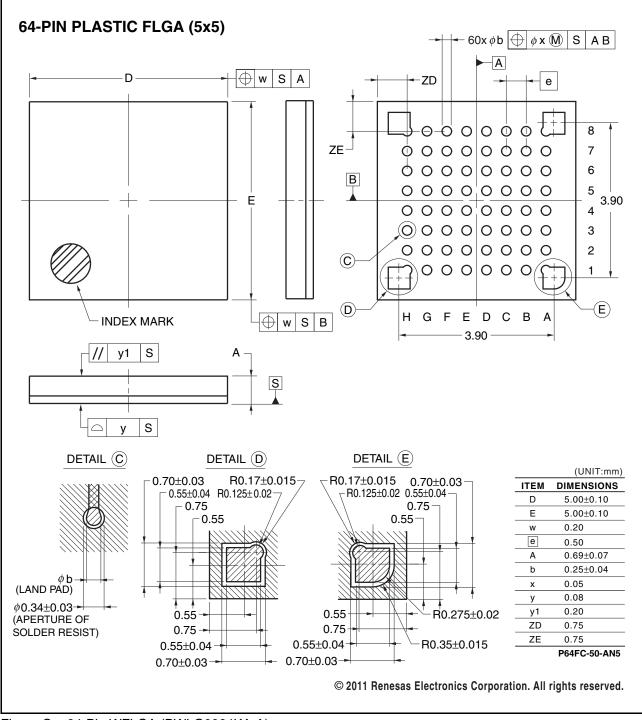

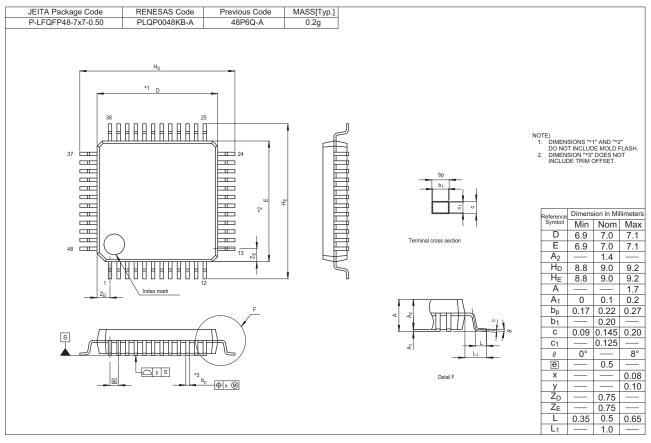

| Packages              |                                        | 64-pin LFQFP (PLQP0064KB-A) 10 × 10 mm, 0.5 mm pitch<br>64-pin LQFP (PLQP0064GA-A) 14 × 14 mm, 0.8 mm pitch<br>64-pin WFLGA (PWLG0064KA-A) 5 × 5 mm, 0.5 mm pitch<br>48-pin LFQFP (PLQP0048KB-A) 7 × 7 mm, 0.5 mm pitch<br>48-pin HWQFN (PWQN0048KB-A) 7 × 7 mm, 0.5 mm pitch<br>40-pin HWQFN (PWQN0040KC-A) 6 × 6 mm, 0.50 mm pitch<br>36-pin WFLGA (PWLG0036KA-A) 4 × 4 mm, 0.5 mm pitch                                                                                       |  |  |  |  |  |

| On-chip debugging s   | system                                 | E1 emulator (FINE interface)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

# Table 1.1Outline of Specifications (3/3)

Figure 1.6 Pin Assignments of the 40-Pin HWQFN

| Table 1.6 | List of Pins and Pin Functions (64-Pin WFLGA) (1/2) |

|-----------|-----------------------------------------------------|

|           |                                                     |

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port          | Timers<br>(MTU, POE, RTC)         | Communication<br>(SCle, SClf, RSPI, RIIC, USB) | Others                       |

|------------|-------------------------------------------|-------------------|-----------------------------------|------------------------------------------------|------------------------------|

| A1         | AVSS0                                     |                   | - · · ·                           | · · · <b>·</b>                                 |                              |

| A2         | AVCC0                                     |                   |                                   |                                                |                              |

| A3         | VREFH0                                    | PJ6*2             |                                   |                                                |                              |

| A4         | VREFL0                                    | PJ7* <sup>2</sup> |                                   |                                                |                              |

| A5         |                                           | P43* <sup>2</sup> |                                   |                                                | AN003                        |

| A6         |                                           | P46*2             |                                   |                                                | AN006                        |

| A7         |                                           | PE2               | MTIOC4A                           | RXD12/RXDX12/SMISO12/SSCL12                    | IRQ7/AN010                   |

| A8         |                                           | PE3               | MTIOC0A/MTIOC1B/<br>MTIOC4B/POE8# | CTS12#/RTS12#/SS12#/RSPCKA                     | IRQ3/AN011                   |

| B1         | XCOUT                                     |                   |                                   |                                                |                              |

| B2         |                                           | P03               |                                   |                                                | DA0                          |

| B3         |                                           | P40* <sup>2</sup> |                                   |                                                | AN000                        |

| B4         |                                           | P42* <sup>2</sup> |                                   |                                                | AN002                        |

| B5         |                                           | P44* <sup>2</sup> |                                   |                                                | AN004                        |

| B6         |                                           | PE6               |                                   |                                                | IRQ6/AN014                   |

| B7         |                                           | PE1               | MTIOC4C                           | TXD12/TXDX12/SIOX12/SMOSI12/<br>SSDA12         | IRQ1/AN009                   |

| B8         |                                           | PE4               | MTIOC1A/MTIOC3A/<br>MTIOC4D       | MOSIA                                          | IRQ4/AN012                   |

| C1         | XCIN                                      | PH7               |                                   |                                                |                              |

| C2         |                                           | P05               |                                   |                                                | DA1                          |

| C3         |                                           | P27               | MTIOC2B                           | SCK1/SCK12                                     | IRQ3/CMPA2/CACREF<br>ADTRG0# |

| C4         |                                           | P41* <sup>2</sup> |                                   |                                                | AN001                        |

| C5         |                                           | PE7               |                                   |                                                | IRQ7/AN015                   |

| C6         |                                           | PE5               | MTIOC2B/MTIOC4C                   |                                                | IRQ5/AN013                   |

| C7         |                                           | PA1               | MTIOC0B/MTCLKC/<br>RTCOUT         | SCK5/SSLA2                                     |                              |

| C8         |                                           | PA0               | MTIOC4A                           | SSLA1                                          | CACREF                       |

| D1         | RES#                                      |                   |                                   |                                                |                              |

| D2         |                                           | P30               | MTIOC4B/POE8#                     | RXD1/SMISO1/SSCL1                              | IRQ0                         |

| D3         |                                           | P26               | MTIOC2A                           | TXD1/SMOSI1/SSDA1/<br>USB0_VBUSEN              |                              |

| D4         |                                           | PE0               | MTIOC2A/POE3#                     | SCK12                                          | IRQ0/AN008                   |

| D5         |                                           | PA6               | MTIC5V/MTIOC2A/MTCLKB/<br>POE2#   | CTS5#/RTS5#/SS5#/SDA0/MOSIA                    | IRQ3                         |

| D6         |                                           | PA4               | MTIC5U/MTIOC2B/MTCLKA             | TXD5/SMOSI5/SSDA5/SSLA0                        | IRQ5                         |

| D7         |                                           | PA3               | MTIOC0D/MTCLKD/<br>MTIOC1B/POE0#  | RXD5/SMISO5/SSCL5/MISOA                        | IRQ6                         |

| D8         | VSS                                       |                   |                                   |                                                |                              |

| E1         | XTAL                                      |                   |                                   |                                                |                              |

| E2         | MD                                        |                   |                                   |                                                | FINED                        |

| E3         |                                           | P31               | MTIOC4D                           | CTS1#/RTS1#/SS1#                               | IRQ1                         |

| E4         |                                           | P55               | MTIOC4D                           |                                                |                              |

| E5         |                                           | PB3               | MTIOC0A/MTIOC3B/<br>MTIOC4A/POE3# | USB0_OVRCURA                                   |                              |

| E6         |                                           | PB1               | MTIOC0C/MTIOC4C                   |                                                | IRQ4                         |

| E7         |                                           | PB0               | MTIC5W/MTIOC0C/<br>RTCOUT         | SCL0/RSPCKA                                    | IRQ2/ADTRG0#                 |

| E8         | VCC                                       |                   |                                   |                                                |                              |

| F1         | EXTAL                                     |                   |                                   |                                                |                              |

• Longword-size I/O registers

MOV.L #SFR\_ADDR, R1 MOV.L #SFR\_DATA, [R1] CMP [R1].L, R1 ;; Next process

When executing an instruction after writing to multiple registers, only read the last I/O register written to and execute the instruction using that value; it is not necessary to execute the instruction using the values written to all the registers.

### (3) Number of cycles necessary for accessing I/O registers

See Table 4.1 for details on the number of clock cycles necessary for accessing I/O registers. The number of access cycles to I/O registers is obtained by following equation.<sup>\*1</sup>

Number of access cycles to I/O registers = Number of bus cycles for internal main bus 1 + Number of divided clock synchronization cycles + Number of bus cycles for internal peripheral buses 1 to 6

The number of bus cycles of internal peripheral buses 1 to 6 differs according to the register to be accessed. When peripheral functions connected to internal peripheral buses 2 to 6 or registers for the external bus control unit (except for bus error related registers) are accessed, the number of divided clock synchronization cycles is added. The number of divided clock synchronization cycles differs depending on the frequency ratio between ICLK and PCLK (or FCLK) or bus access timing.

In the peripheral function unit, when the frequency ratio of ICLK is equal to or greater than that of PCLK (or FCLK), the sum of the number of bus cycles for internal main bus 1 and the number of the divided clock synchronization cycles will be one cycle of PCLK (or FCLK) at a maximum. Therefore, one PCLK (or FCLK) has been added to the number of access cycles shown in Table 4.1.

When the frequency ratio of ICLK is lower than that of PCLK (or FCLK), the subsequent bus access is started from the ICLK cycle following the completion of the access to the peripheral functions. Therefore, the access cycles are described on an ICLK basis.

Note 1. This applies to the number of cycles when the access from the CPU does not conflict with the bus access from the different bus master (DTC).

#### (4) Notes on sleep mode and mode transitions

During sleep mode or mode transitions, do not write to the system control related registers (indicated by 'SYSTEM' in the Module Symbol column in Table 4.1, List of I/O Registers (Address Order)).

# 4.1 I/O Register Addresses (Address Order)

|  | Table 4.1 | List of I/O | Registers | (Address | Order) (1/16) |

|--|-----------|-------------|-----------|----------|---------------|

|--|-----------|-------------|-----------|----------|---------------|

| Address    | Module<br>Symbol | Register Name                                       | Register<br>Symbol | Number of<br>Bits | Access<br>Size | Number of Access<br>States |

|------------|------------------|-----------------------------------------------------|--------------------|-------------------|----------------|----------------------------|

| 0008 0000h | SYSTEM           | Mode Monitor Register                               | MDMONR             | 16                | 16             | 3 ICLK                     |

| 0008 0008h | SYSTEM           | System Control Register 1                           | SYSCR1             | 16                | 16             | 3 ICLK                     |

| 0008 000Ch | SYSTEM           | Standby Control Register                            | SBYCR              | 16                | 16             | 3 ICLK                     |

| 0008 0010h | SYSTEM           | Module Stop Control Register A                      | MSTPCRA            | 32                | 32             | 3 ICLK                     |

| 0008 0014h | SYSTEM           | Module Stop Control Register B                      | MSTPCRB            | 32                | 32             | 3 ICLK                     |

| 0008 0018h | SYSTEM           | Module Stop Control Register C                      | MSTPCRC            | 32                | 32             | 3 ICLK                     |

| 0008 0020h | SYSTEM           | System Clock Control Register                       | SCKCR              | 32                | 32             | 3 ICLK                     |

| 0008 0026h | SYSTEM           | System Clock Control Register 3                     | SCKCR3             | 16                | 16             | 3 ICLK                     |

| 0008 0028h | SYSTEM           | PLL Control Register                                | PLLCR              | 16                | 16             | 3 ICLK                     |

| 0008 002Ah | SYSTEM           | PLL Control Register 2                              | PLLCR2             | 8                 | 8              | 3 ICLK                     |

| 0008 0032h | SYSTEM           | Main Clock Oscillator Control Register              | MOSCCR             | 8                 | 8              | 3 ICLK                     |

| 0008 0033h | SYSTEM           | Sub-Clock Oscillator Control Register               | SOSCCR             | 8                 | 8              | 3 ICLK                     |

| 0008 0034h | SYSTEM           | Low-Speed On-Chip Oscillator Control Register       | LOCOCR             | 8                 | 8              | 3 ICLK                     |

| 0008 0035h | SYSTEM           | IWDT-Dedicated On-Chip Oscillator Control Register  | ILOCOCR            | 8                 | 8              | 3 ICLK                     |

| 0008 0036h | SYSTEM           | High-Speed On-Chip Oscillator Control Register      | HOCOCR             | 8                 | 8              | 3 ICLK                     |

| 0008 003Ch | SYSTEM           | Oscillation Stabilization Flag Register             | OSCOVFSR           | 8                 | 8              | 3 ICLK                     |

| 0008 003Eh | SYSTEM           | CLKOUT Output Control Register                      | CKOCR              | 16                | 16             | 3 ICLK                     |

| 0008 0040h | SYSTEM           | Oscillation Stop Detection Control Register         | OSTDCR             | 8                 | 8              | 3 ICLK                     |

| 0008 0041h | SYSTEM           | Oscillation Stop Detection Status Register          | OSTDSR             | 8                 | 8              | 3 ICLK                     |

| 0008 00A0h | SYSTEM           | Operating Power Control Register                    | OPCCR              | 8                 | 8              | 3 ICLK                     |

| 0008 00A1h | SYSTEM           | Sleep Mode Return Clock Source Switching Register   | RSTCKCR            | 8                 | 8              | 3 ICLK                     |

| 0008 00A2h | SYSTEM           | Main Clock Oscillator Wait Control Register         | MOSCWTCR           | 8                 | 8              | 3 ICLK                     |

| 0008 00A5h | SYSTEM           | High-Speed On-Chip Oscillator Wait Control Register | HOCOWTCR           | 8                 | 8              | 3 ICLK                     |

| 0008 00AAh | SYSTEM           | Sub Operating Power Control Register                | SOPCCR             | 8                 | 8              | 3 ICLK                     |

| 0008 00C0h | SYSTEM           | Reset Status Register 2                             | RSTSR2             | 8                 | 8              | 3 ICLK                     |

| 0008 00C2h | SYSTEM           | Software Reset Register                             | SWRR               | 16                | 16             | 3 ICLK                     |

| 0008 00E0h | SYSTEM           | Voltage Monitoring 1 Circuit Control Register 1     | LVD1CR1            | 8                 | 8              | 3 ICLK                     |

| 0008 00E1h | SYSTEM           | Voltage Monitoring 1 Circuit Status Register        | LVD1SR             | 8                 | 8              | 3 ICLK                     |

| 0008 00E2h | SYSTEM           | Voltage Monitoring 2 Circuit Control Register 1     | LVD2CR1            | 8                 | 8              | 3 ICLK                     |

| 0008 00E3h | SYSTEM           | Voltage Monitoring 2 Circuit Status Register        | LVD2SR             | 8                 | 8              | 3 ICLK                     |

| 0008 03FEh | SYSTEM           | Protect Register                                    | PRCR               | 16                | 16             | 3 ICLK                     |

| 0008 1300h | BSC              | Bus Error Status Clear Register                     | BERCLR             | 8                 | 8              | 2 ICLK                     |

| 0008 1304h | BSC              | Bus Error Monitoring Enable Register                | BEREN              | 8                 | 8              | 2 ICLK                     |

| 0008 1308h | BSC              | Bus Error Status Register 1                         | BERSR1             | 8                 | 8              | 2 ICLK                     |

| 0008 130Ah | BSC              | Bus Error Status Register 2                         | BERSR2             | 16                | 16             | 2 ICLK                     |

| 0008 1310h | BSC              | Bus Priority Control Register                       | BUSPRI             | 16                | 16             | 2 ICLK                     |

| 0008 2400h | DTC              | DTC Control Register                                | DTCCR              | 8                 | 8              | 2 ICLK                     |

| 0008 2404h | DTC              | DTC Vector Base Register                            | DTCVBR             | 32                | 32             | 2 ICLK                     |

| 0008 2408h | DTC              | DTC Address Mode Register                           | DTCADMOD           | 8                 | 8              | 2 ICLK                     |

| 0008 240Ch | DTC              | DTC Module Start Register                           | DTCST              | 8                 | 8              | 2 ICLK                     |

| 0008 240Eh | DTC              | DTC Status Register                                 | DTCSTS             | 16                | 16             | 2 ICLK                     |

| 0008 7010h | ICU              | Interrupt Request Register 016                      | IR016              | 8                 | 8              | 2 ICLK                     |

| 0008 701Bh | ICU              | Interrupt Request Register 027                      | IR027              | 8                 | 8              | 2 ICLK                     |

| 0008 701Ch | ICU              | Interrupt Request Register 028                      | IR028              | 8                 | 8              | 2 ICLK                     |

| 0008 701Dh | ICU              | Interrupt Request Register 029                      | IR029              | 8                 | 8              | 2 ICLK                     |

| 0008 7020h | ICU              | Interrupt Request Register 032                      | IR032              | 8                 | 8              | 2 ICLK                     |

| 0008 7021h | ICU              | Interrupt Request Register 033                      | IR033              | 8                 | 8              | 2 ICLK                     |

| 0008 7022h | ICU              | Interrupt Request Register 034                      | IR034              | 8                 | 8              | 2 ICLK                     |

| 0008 7024h | ICU              | Interrupt Request Register 036                      | IR036              | 8                 | 8              | 2 ICLK                     |

| 0008 7025h | ICU              | Interrupt Request Register 037                      | IR037              | 8                 | 8              | 2 ICLK                     |

|            |                  | · · · · · · · · ·                                   |                    | -                 | -              |                            |

| Table 4.1 | List of I/O Registers (Address Order) (11/16) |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Address    | Module<br>Symbol | Register Name                                 | Register<br>Symbol | Number of<br>Bits | Access<br>Size | Number of Acces<br>States |

|------------|------------------|-----------------------------------------------|--------------------|-------------------|----------------|---------------------------|

| 0008 B127h | ELC              | Port Buffer Register 1                        | PDBF1              | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B129h | ELC              | Event Link Port Setting Register 0            | PEL0               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B12Ah | ELC              | Event Link Port Setting Register 1            | PEL1               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B12Dh | ELC              | Event Link Software Event Generation Register | ELSEGR             | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B300h | SCI12            | Serial Mode Register                          | SMR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B301h | SCI12            | Bit Rate Register                             | BRR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B302h | SCI12            | Serial Control Register                       | SCR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B303h | SCI12            | Transmit Data Register                        | TDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B304h | SCI12            | Serial Status Register                        | SSR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B305h | SCI12            | Receive Data Register                         | RDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B306h | SCI12            | Smart Card Mode Register                      | SCMR               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B307h | SCI12            | Serial Extended Mode Register                 | SEMR               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B308h | SCI12            | Noise Filter Setting Register                 | SNFR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B309h  | SCI12            | I <sup>2</sup> C Mode Register 1              | SIMR1              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Ah  | SCI12            | I <sup>2</sup> C Mode Register 2              | SIMR2              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Bh  | SCI12            | I <sup>2</sup> C Mode Register 3              | SIMR3              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Ch  | SCI12            | I <sup>2</sup> C Status Register              | SISR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Dh  | SCI12            | SPI Mode Register                             | SPMR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B320h  | SCI12            | Extended Serial Mode Enable Register          | ESMER              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B321h  | SCI12            | Control Register 0                            | CR0                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B322h  | SCI12            | Control Register 1                            | CR1                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B323h  | SCI12            | Control Register 2                            | CR2                | 8                 | 8              | 2 or 3 PCLKB              |

|            | SCI12            |                                               | CR3                | 8                 | 8              |                           |

| 008 B324h  |                  | Control Register 3 Port Control Register      | PCR                |                   |                | 2 or 3 PCLKB              |

| 008 B325h  | SCI12            | Port Control Register                         |                    | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B326h  | SCI12            | Interrupt Control Register                    | ICR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B327h  | SCI12            | Status Register                               | STR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B328h  | SCI12            | Status Clear Register                         | STCR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B329h  | SCI12            | Control Field 0 Data Register                 | CF0DR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Ah  | SCI12            | Control Field 0 Compare Enable Register       | CF0CR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Bh  | SCI12            | Control Field 0 Receive Data Register         | CF0RR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Ch  | SCI12            | Primary Control Field 1 Data Register         | PCF1DR             | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Dh  | SCI12            | Secondary Control Field 1 Data Register       | SCF1DR             | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Eh  | SCI12            | Control Field 1 Compare Enable Register       | CF1CR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Fh  | SCI12            | Control Field 1 Receive Data Register         | CF1RR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B330h  | SCI12            | Timer Control Register                        | TCR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B331h  | SCI12            | Timer Mode Register                           | TMR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B332h  | SCI12            | Timer Prescaler Register                      | TPRE               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B333h  | SCI12            | Timer Count Register                          | TCNT               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C000h  | PORT0            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C001h  | PORT1            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C002h  | PORT2            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C003h  | PORT3            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C004h  | PORT4            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C005h  | PORT5            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Ah  | PORTA            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Bh  | PORTB            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Ch  | PORTC            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Eh  | PORTE            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C012h  | PORTJ            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C020h  | PORT0            | Port Output Data Register                     | PODR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C021h  | PORT1            | Port Output Data Register                     | PODR               | 8                 | 8              | 2 or 3 PCLKB              |

|            | PORT2            | Port Output Data Register                     | PODR               | 8                 | 8              | 2 or 3 PCLKB              |

## 5.2 DC Characteristics

## Table 5.3DC Characteristics (1)

Conditions:  $2.7 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 2.7 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                    |                                                                                                                                                                                                                              | Symbol          | Min.        | Тур. | Max.        | Unit | Test<br>Conditions |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------|-------------|------|--------------------|

| Schmitt trigger<br>input voltage        | RIIC input pin<br>(except for SMBus, 5 V tolerant)                                                                                                                                                                           | V <sub>IH</sub> | VCC × 0.7   | —    | 5.8         | V    |                    |

|                                         | Ports P16, P17,<br>port PA6, port PB0 (5 V tolerant)                                                                                                                                                                         |                 | VCC × 0.8   | _    | 5.8         |      |                    |

|                                         | Ports P03, P05,<br>ports P14,P15,<br>ports P26, P27,<br>ports P30 to P32, P35,<br>ports P54, P55,<br>ports PA0, PA1, PA3, PA4,<br>ports PB1, PB3, PB5 to PB7,<br>ports PC2 to PC7,<br>ports PE0 to PE7,<br>port PH7,<br>RES# |                 | VCC × 0.8   | _    | VCC + 0.3   |      |                    |

|                                         | RIIC input pin<br>(except for SMBus)                                                                                                                                                                                         | V <sub>IL</sub> | -0.3        | _    | VCC × 0.3   |      |                    |

|                                         | Other than RIIC input pin                                                                                                                                                                                                    |                 | -0.3        | _    | VCC × 0.2   |      |                    |

|                                         | RIIC input pin<br>(except for SMBus)                                                                                                                                                                                         | ΔV <sub>T</sub> | VCC × 0.05  | _    | _           | -    |                    |

|                                         | Other than RIIC input pin                                                                                                                                                                                                    |                 | VCC × 0.1   | _    | —           |      |                    |

| Input voltage                           | MD                                                                                                                                                                                                                           | V <sub>IH</sub> | VCC × 0.9   |      | VCC + 0.3   | V    |                    |

| (except for Schmitt trigger input pins) | XTAL (external clock input)                                                                                                                                                                                                  |                 | VCC × 0.8   |      | VCC + 0.3   |      |                    |

| uiggei input pins <i>)</i>              | Ports P40 to P44, P46, ports PJ6,<br>PJ7                                                                                                                                                                                     |                 | AVCC0 × 0.7 | —    | AVCC0 + 0.3 |      |                    |

|                                         | RIIC input pin (SMBus)                                                                                                                                                                                                       |                 | 2.1         |      | VCC + 0.3   |      |                    |

|                                         | MD                                                                                                                                                                                                                           | V <sub>IL</sub> | -0.3        | _    | VCC × 0.1   |      |                    |

|                                         | XTAL (external clock input)                                                                                                                                                                                                  | 1               | -0.3        |      | VCC × 0.2   |      |                    |

|                                         | Ports P40 to P44, P46, ports PJ6,<br>PJ7                                                                                                                                                                                     |                 | -0.3        | —    | AVCC0 × 0.3 |      |                    |

|                                         | RIIC input pin (SMBus)                                                                                                                                                                                                       |                 | -0.3        | _    | 0.8         |      |                    |

### [256-Kbyte or more flash memory]

Table 5.8DC Characteristics (6) (1/2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|        |              |                                 | Item                                              |               | Symbol          | Typ<br>*4 | Max  | Unit | Test<br>Conditions |

|--------|--------------|---------------------------------|---------------------------------------------------|---------------|-----------------|-----------|------|------|--------------------|

| Supply | High-speed   | Normal                          | No peripheral                                     | ICLK = 32 MHz | I <sub>CC</sub> | 3.6       | _    | mA   |                    |

|        | operating    | operating mode                  | operation*2                                       | ICLK = 16 MHz |                 | 2.4       | —    |      |                    |

|        | mode         | mode                            |                                                   | ICLK = 8 MHz  | -               | 1.8       | _    |      |                    |

|        |              |                                 | All peripheral operation:                         | ICLK = 32 MHz |                 | 13.4      | —    |      |                    |

|        |              |                                 | Normal* <sup>3</sup>                              | ICLK = 16 MHz |                 | 7.5       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 8 MHz  |                 | 4.5       | —    |      |                    |

|        |              |                                 | All peripheral operation:<br>Max.* <sup>3</sup>   | ICLK = 32 MHz |                 | —         | 27   |      |                    |

|        |              | Sleep mode                      | No peripheral                                     | ICLK = 32 MHz |                 | 1.9       | —    |      |                    |

|        |              |                                 | operation*2                                       | ICLK = 16 MHz |                 | 1.5       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 8 MHz  |                 | 1.3       | —    |      |                    |

|        |              |                                 | All peripheral operation:                         | ICLK = 32 MHz |                 | 7.6       | —    |      |                    |

|        |              |                                 | Normal* <sup>3</sup>                              | ICLK = 16 MHz |                 | 4.4       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 8 MHz  |                 | 2.8       | —    |      |                    |

|        |              | Deep sleep                      | No peripheral                                     | ICLK = 32 MHz |                 | 1.1       | —    |      |                    |

|        |              | mode                            | operation*2                                       | ICLK = 16 MHz |                 | 1.0       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 8 MHz  |                 | 0.9       | —    |      |                    |

|        |              |                                 | All peripheral operation:<br>Normal* <sup>3</sup> | ICLK = 32 MHz |                 | 5.8       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 16 MHz |                 | 3.4       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 8 MHz  |                 | 2.1       | _    |      |                    |

|        |              | Increase during flash rewrite*5 |                                                   |               |                 | 2.5       | —    |      |                    |

|        | Middle-speed |                                 | No peripheral                                     | ICLK = 12 MHz | I <sub>CC</sub> | 2.1       | —    | mA   |                    |

|        | modes mc     |                                 | operation* <sup>6</sup>                           | ICLK = 8 MHz  |                 | 1.4       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 1 MHz  |                 | 0.8       | —    |      |                    |

|        |              |                                 | All peripheral operation:<br>Normal* <sup>7</sup> | ICLK = 12 MHz |                 | 5.9       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 8 MHz  |                 | 4.2       | _    |      |                    |

|        |              |                                 |                                                   | ICLK = 1 MHz  |                 | 1.3       | _    |      |                    |

|        |              |                                 | All peripheral operation: Max.* <sup>7</sup>      | ICLK = 12 MHz |                 | —         | 12.2 |      |                    |

|        |              |                                 | No peripheral operation* <sup>6</sup>             | ICLK = 12 MHz |                 | 1.4       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 8 MHz  |                 | 0.9       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 1 MHz  |                 | 0.7       |      |      |                    |

|        |              |                                 | All peripheral operation:                         | ICLK = 12 MHz |                 | 3.6       | —    |      |                    |

|        |              |                                 | Normal* <sup>7</sup>                              | ICLK = 8 MHz  |                 | 2.5       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 1 MHz  |                 | 1.1       | —    |      |                    |

|        |              | Deep sleep                      | No peripheral                                     | ICLK = 12 MHz | ]               | 1.1       | —    |      |                    |

|        |              | mode                            | operation* <sup>6</sup>                           | ICLK = 8 MHz  | 1 1             | 0.6       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 1 MHz  | 1               | 0.6       | —    |      |                    |

|        |              |                                 | All peripheral operation:                         | ICLK = 12 MHz | 1 1             | 2.9       | —    |      |                    |

|        |              |                                 | Normal* <sup>7</sup>                              | ICLK = 8 MHz  |                 | 2.0       | —    |      |                    |

|        |              |                                 |                                                   | ICLK = 1 MHz  |                 | 0.9       | —    |      |                    |

|        |              | Incroaco duri                   | ng flash rewrite* <sup>5</sup>                    |               | 1 1             | 2.5       | L    | 1    |                    |

#### Table 5.8DC Characteristics (6) (2/2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                  | Item                           |                    |                                                        |                   |                 |      | Max | Unit | Test<br>Conditions |

|------------------|--------------------------------|--------------------|--------------------------------------------------------|-------------------|-----------------|------|-----|------|--------------------|

| Supply current*1 | Low-speed<br>operating<br>mode | perating operating | No peripheral operation* <sup>8</sup>                  | ICLK = 32.768 kHz | I <sub>CC</sub> | 4.3  | _   | Αų   |                    |

|                  |                                |                    | All peripheral operation:<br>Normal* <sup>9, *10</sup> | ICLK = 32.768 kHz |                 | 14.7 | -   |      |                    |

|                  |                                |                    | All peripheral operation:<br>Max.* <sup>9, *10</sup>   | ICLK = 32.768kHz  |                 |      | 60  |      |                    |

|                  |                                | Sleep mode         | No peripheral operation* <sup>8</sup>                  | ICLK = 32.768 kHz |                 | 2.2  | _   |      |                    |

|                  |                                | Deep sleep<br>mode | All peripheral operation:<br>Normal* <sup>9</sup>      | ICLK = 32.768 kHz |                 | 8.3  |     |      |                    |

|                  |                                |                    | No peripheral operation* <sup>8</sup>                  | ICLK = 32.768 kHz |                 | 1.7  | -   |      |                    |

|                  |                                |                    | All peripheral operation:<br>Normal* <sup>9</sup>      | ICLK = 32.768 kHz |                 | 6.7  | _   |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL. FCLK and PCLK are set to divided by 64.

Note 3. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL. FCLK and PCLK are set to the same frequency as ICLK.

Note 4. Values when VCC = 3.3 V.

Note 5. This is the increase for programming or erasure of the ROM or E2 DataFlash during program execution.

Note 6. Clock supply to the peripheral functions is stopped. The clock source is PLL when ICLK = 12 MHz, and HOCO otherwise. FCLK and PCLK are set to divided by 64.

Note 7. Clocks are supplied to the peripheral functions. The clock source is PLL when ICLK = 12 MHz, and HOCO otherwise. FCLK and PCLK are set to the same frequency as ICLK.

Note 8. Clock supply to the peripheral functions is stopped. The clock source is the sub-clock oscillator. FCLK and PCLK are set to divided by 64.

Note 9. Clocks are supplied to the peripheral functions. The clock source is the sub-clock oscillator. FCLK and PCLK are set to the same frequency as ICLK.

Note 10. Values when the MSTPCRA.MSTPA17 bit (12-bit A/D converter module stop bit) is set to "transition to the module stop state is made".

#### Table 5.24 Clock Timing

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                                  |                      | Symbol               | Min.  | Тур.   | Max.  | Unit        | Test Conditions   |

|-------------------------------------------------------|----------------------|----------------------|-------|--------|-------|-------------|-------------------|

| XTAL external clock input cycle time                  |                      |                      | 50    | —      | —     | ns          | Figure 5.23       |

| XTAL external clock input high pulse width            |                      |                      | 20    | —      | _     | ns          |                   |

| XTAL external clock input low pulse width             |                      | t <sub>XL</sub>      | 20    | _      | _     | ns          |                   |

| XTAL external clock rising time                       |                      | t <sub>Xr</sub>      |       | _      | 5     | ns          |                   |

| XTAL external clock falling time                      |                      | t <sub>Xf</sub>      |       | —      | 5     | ns          |                   |

| XTAL external clock input wait time*1                 |                      | t <sub>EXWT</sub>    | 0.5   | —      | _     | μs          |                   |

| Main clock oscillator oscillation frequency           | 2.4 ≤ VCC ≤ 3.6      | f <sub>MAIN</sub>    | 1     | —      | 20    | MHz         |                   |

|                                                       | 1.8 ≤ VCC < 2.4      |                      | 1     | —      | 8     |             |                   |

| Main clock oscillation stabilization time (crystal)*2 |                      | t <sub>MAINOSC</sub> |       | 3      |       | ms          | Figure 5.25       |

| Main clock oscillation stabilization time (ceran      | t <sub>MAINOSC</sub> |                      | 50    |        | μs    |             |                   |

| LOCO clock oscillation frequency                      |                      | f <sub>LOCO</sub>    | 3.44  | 4.0    | 4.56  | MHz         |                   |

| LOCO clock oscillation stabilization time             | t <sub>LOCO</sub>    |                      | —     | 0.5    | μs    | Figure 5.26 |                   |

| IWDT-dedicated clock oscillation frequency            |                      | f <sub>ILOCO</sub>   | 12.75 | 15     | 17.25 | kHz         |                   |

| IWDT-dedicated clock oscillation stabilization time   |                      | t <sub>ILOCO</sub>   | _     | —      | 50    | μs          | Figure 5.24       |

| HOCO clock oscillation frequency                      |                      | f <sub>HOCO</sub>    | 31.52 | 32     | 32.48 | MHz         | Ta = -40 to 85°C  |

|                                                       |                      |                      | 31.68 | 32     | 32.32 |             | Ta = -20 to 85°C  |

|                                                       |                      |                      | 31.36 | 32     | 32.64 |             | Ta = -40 to 105°C |

| HOCO clock oscillation stabilization time             |                      | t <sub>HOCO2</sub>   |       | —      | 56    | μs          | Figure 5.28       |

| PLL input frequency*3                                 | f <sub>PLLIN</sub>   | 4                    | —     | 8      | MHz   |             |                   |

| PLL circuit oscillation frequency*3                   |                      | f <sub>PLL</sub>     | 32    |        | 48    | MHz         |                   |

| PLL clock oscillation stabilization time              |                      | t <sub>PLL</sub>     | _     | —      | 50    | μs          | Figure 5.29       |

| PLL free-running oscillation frequency                |                      | f <sub>PLLFR</sub>   | _     | 8      | _     | MHz         |                   |

| Sub-clock oscillator oscillation frequency*5          |                      | f <sub>SUB</sub>     |       | 32.768 |       | kHz         |                   |

| Sub-clock oscillation stabilization time*4            |                      | t <sub>SUBOSC</sub>  | _     | 0.5    | _     | s           | Figure 5.30       |

Note 1. Time until the clock can be used after the main clock oscillator stop bit (MOSCCR.MOSTP) is set to 0 (operating) when the external clock is stable.

Note 2. Reference values when an 8-MHz oscillator is used. When specifying the main clock oscillator stabilization time, set the MOSCWTCR register with a stabilization time value that is equal to or greater than the oscillator-manufacturer-recommended value. After changing the setting of the MOSCCR.MOSTP bit so that the main clock oscillator operates, read the OSCOVFSR.MOOVF flag to confirm that is has become 1, and then start using the main clock.

Note 3. The VCC range that the PLL can be used is 2.4 to 3.6 V.

Note 4. After changing the setting of the SOSCCR.SOSTP bit or RCR3.RTCEN bit so that the sub-clock oscillator operates, only start using the sub-clock after the sub-clock oscillation stabilization wait time that is equal to or greater than the oscillator-manufacturer-recommended value has elapsed. Reference value when a 32.768-kHz resonator is used.

Note 5. Only 32.768 kHz can be used.

#### 5.3.5 **Timing of On-Chip Peripheral Modules**

#### **Timing of On-Chip Peripheral Modules (1)** Table 5.32

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                  | I                                                  | tem                   |                                                     | Symbol              | Min.                                       | Max. | Unit*1            | Test<br>Conditions       |