Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, USB OTG                                              |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                      |

| Data Converters            | A/D 14x12b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-WFLGA                                                                         |

| Supplier Device Package    | 64-FLGA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f51116adlf-ua |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification        | Module/Function                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

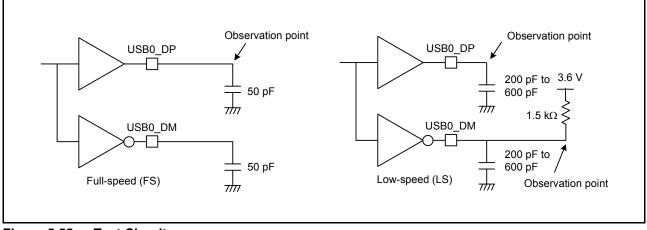

|                       | JSB 2.0 host/function<br>module (USBc) | <ul> <li>USB Device Controller (UDC) and transceiver for USB 2.0 are incorporated.</li> <li>Host (32-Kbyte or more ROM)/function module: 1 port</li> <li>Compliant with USB version 2.0</li> <li>Transfer speed: Full-speed (12 Mbps), low-speed (1.5 Mbps)</li> <li>OTG (On-The-Go) is supported.</li> <li>Isochronous transfer is supported.</li> <li>BC (Battery Charger) is supported.</li> </ul>                                                                            |

| 12-bit A/D converter  | (S12ADb)                               | <ul> <li>1 unit (1 unit × 14 channels)</li> <li>12-bit resolution</li> <li>Minimum conversion time: 1.0 µs per channel when the ADCLK is operating at 32 MHz</li> <li>Operating modes<br/>Scan mode (single scan mode, continuous scan mode, and group scan mode)</li> <li>Double trigger mode (duplication of A/D conversion data)</li> <li>A/D conversion start conditions<br/>A software trigger, a trigger from a timer (MTU), an external trigger signal, or ELC</li> </ul> |

| Temperature sensor    | (TEMPSA)                               | <ul> <li>1 channel</li> <li>The voltage of the temperature is converted into a digital value by the 12-bit A/D converter.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

| D/A converter (DA)    |                                        | <ul> <li>2 channels</li> <li>8-bit resolution</li> <li>Output voltage: 0 V to VCC</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                     |

| CRC calculator (CRC   | 2)                                     | <ul> <li>CRC code generation for arbitrary amounts of data in 8-bit units</li> <li>Select any of three generating polynomials:<br/>X<sup>8</sup> + X<sup>2</sup> + X + 1, X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1, or X<sup>16</sup> + X<sup>12</sup> + X<sup>5</sup> + 1</li> <li>Generation of CRC codes for use with LSB first or MSB first communications is selectable.</li> </ul>                                                                              |

| Data operation circui | t (DOC)                                | Comparison, addition, and subtraction of 16-bit data                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Unique ID             |                                        | 32-byte ID code for the MCU                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power supply voltage  | es/Operating frequencies               | VCC = 1.8 to 2.4 V: 8 MHz, VCC = 2.4 to 2.7 V: 16 MHz, VCC = 2.7 to 3.6 V: 32 MHz                                                                                                                                                                                                                                                                                                                                                                                                |

| Supply current        |                                        | 3.2 mA at 32 MHz (typ.)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operating temperatu   | re range                               | D version: -40 to +85°C, G version: -40 to +105°C                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Packages              |                                        | 64-pin LFQFP (PLQP0064KB-A) 10 × 10 mm, 0.5 mm pitch<br>64-pin LQFP (PLQP0064GA-A) 14 × 14 mm, 0.8 mm pitch<br>64-pin WFLGA (PWLG0064KA-A) 5 × 5 mm, 0.5 mm pitch<br>48-pin LFQFP (PLQP0048KB-A) 7 × 7 mm, 0.5 mm pitch<br>48-pin HWQFN (PWQN0048KB-A) 7 × 7 mm, 0.5 mm pitch<br>40-pin HWQFN (PWQN0040KC-A) 6 × 6 mm, 0.50 mm pitch<br>36-pin WFLGA (PWLG0036KA-A) 4 × 4 mm, 0.5 mm pitch                                                                                       |

| On-chip debugging s   | system                                 | E1 emulator (FINE interface)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# Table 1.1Outline of Specifications (3/3)

### 1.4 Pin Functions

Table 1.4 lists the pin functions.

### Table 1.4Pin Functions (1/3)

| Classifications                      | Pin Name                             | I/O                 | Description                                                                                                                                                |  |  |  |  |  |

|--------------------------------------|--------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Power supply                         | VCC                                  | Input               | Power supply pin. Connect it to the system power supply.                                                                                                   |  |  |  |  |  |

|                                      | VCL                                  | _                   | Connect this pin to the VSS pin via the 4.7 $\mu$ F smoothing capacitor used to stabilize the internal power supply. Place the capacitor close to the pin. |  |  |  |  |  |

|                                      | VSS                                  | Input               | Ground pin. Connect it to the system power supply (0 V).                                                                                                   |  |  |  |  |  |

|                                      | VCC_USB                              | Input               | Power supply pin for USB. Connect this pin to VCC.                                                                                                         |  |  |  |  |  |

|                                      | VSS_USB                              | Input               | Ground pin for USB. Connect this pin to VSS.                                                                                                               |  |  |  |  |  |

| Analog power<br>supply               | AVCC0                                | Input               | Analog voltage supply pin for the 12-bit A/D converter. Connect this pin to VCC when not using the 12-bit A/D converter.                                   |  |  |  |  |  |

|                                      | AVSS0                                | Input               | Analog ground pin for the 12-bit A/D converter. Connect this pin to VSS when not using the 12-bit A/D converter.                                           |  |  |  |  |  |

|                                      | VREFH0                               | Input               | Analog reference voltage supply pin for the 12-bit A/D converter. Connect this pin to VCC when not using the 12-bit A/D converter.                         |  |  |  |  |  |

|                                      | VREFL0                               | Input               | Analog reference ground pin for the 12-bit A/D converter. Connect this pin to VSS when not using the 12-bit A/D converter.                                 |  |  |  |  |  |

| Clock                                | XTAL                                 | Output/<br>Input *1 | Pins for connecting a crystal. An external clock can be input through the XTAL pin.                                                                        |  |  |  |  |  |

|                                      | EXTAL                                | Input               |                                                                                                                                                            |  |  |  |  |  |

|                                      | XCIN                                 | Input               | Input/output pins for the sub-clock oscillator. Connect a crystal between                                                                                  |  |  |  |  |  |

|                                      | XCOUT                                | Output              | - XCIN and XCOUT.                                                                                                                                          |  |  |  |  |  |

|                                      | CLKOUT                               | Output              | Clock output pin.                                                                                                                                          |  |  |  |  |  |

| Dperating mode<br>control            | MD                                   | Input               | Pin for setting the operating mode. The signal levels on this pin must not be changed during operation.                                                    |  |  |  |  |  |

|                                      | UB#                                  | Input               | Pin used for boot mode (USB interface).                                                                                                                    |  |  |  |  |  |

|                                      | UPSEL                                | Input               | Pin used for boot mode (USB interface).                                                                                                                    |  |  |  |  |  |

| System control                       | RES#                                 | Input               | Reset pin. This MCU enters the reset state when this signal goes low.                                                                                      |  |  |  |  |  |

| CAC                                  | CACREF                               | Input               | Input pin for the clock frequency accuracy measurement circuit.                                                                                            |  |  |  |  |  |

| On-chip<br>emulator                  | FINED                                | I/O                 | FINE interface pin.                                                                                                                                        |  |  |  |  |  |

| LVD                                  | CMPA2                                | Input               | Detection target voltage pin for voltage detection 2                                                                                                       |  |  |  |  |  |

| Interrupts                           | NMI                                  | Input               | Non-maskable interrupt request pin.                                                                                                                        |  |  |  |  |  |

|                                      | IRQ0 to IRQ7                         | Input               | Interrupt request pins.                                                                                                                                    |  |  |  |  |  |

| Multi-function<br>timer pulse unit 2 | MTIOC0A, MTIOC0B<br>MTIOC0C, MTIOC0D | I/O                 | The TGRA0 to TGRD0 input capture input/output compare output/PWM output pins.                                                                              |  |  |  |  |  |

|                                      | MTIOC1A, MTIOC1B                     | I/O                 | The TGRA1 and TGRB1 input capture input/output compare output/PWM output pins.                                                                             |  |  |  |  |  |

|                                      | MTIOC2A, MTIOC2B                     | I/O                 | The TGRA2 and TGRB2 input capture input/output compare output/PWM output pins.                                                                             |  |  |  |  |  |

|                                      | MTIOC3A, MTIOC3B<br>MTIOC3C, MTIOC3D | I/O                 | The TGRA3 to TGRD3 input capture input/output compare output/PWM output pins.                                                                              |  |  |  |  |  |

|                                      | MTIOC4A, MTIOC4B<br>MTIOC4C, MTIOC4D | I/O                 | The TGRA4 to TGRD4 input capture input/output compare output/PWM output pins.                                                                              |  |  |  |  |  |

|                                      | MTIC5U, MTIC5V, MTIC5W               | Input               | The TGRU5, TGRV5, and TGRW5 input capture input/external pulse input pins.                                                                                 |  |  |  |  |  |

|                                      | MTCLKA, MTCLKB,<br>MTCLKC, MTCLKD    | Input               | Input pins for the external clock.                                                                                                                         |  |  |  |  |  |

| Port output<br>enable 2              | POE0# to POE3#, POE8#                | Input               | Input pins for request signals to place the MTU pins in the high impedance state.                                                                          |  |  |  |  |  |

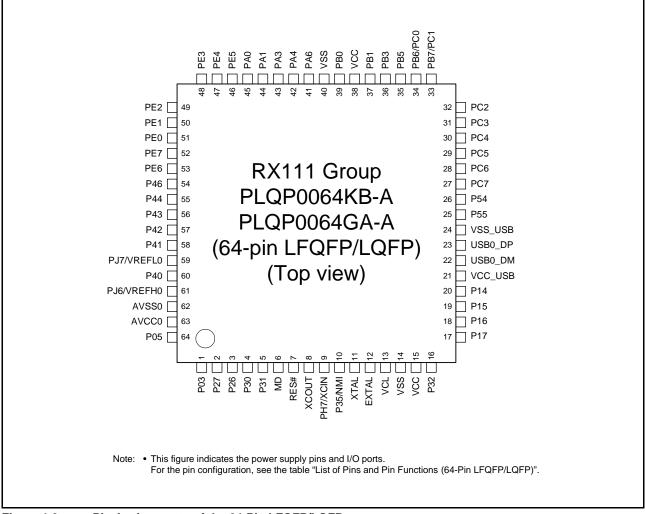

### 1.5 Pin Assignments

Figure 1.3 to Figure 1.7 show the pin assignments. Table 1.5 to Table 1.9 show the lists of pins and pin functions.

Figure 1.3 Pin Assignments of the 64-Pin LFQFP/LQFP

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port          | Timers<br>(MTU, POE, RTC)         | Communication<br>(SCIe, SCIf, RSPI, RIIC, USB)                                 | Others                        |

|------------|-------------------------------------------|-------------------|-----------------------------------|--------------------------------------------------------------------------------|-------------------------------|

|            |                                           | I/O Port          | (MIU, POE, RIC)                   | (Scie, Scif, RSPI, Riic, USB)                                                  | Others                        |

| A1         | AVSS0                                     |                   |                                   |                                                                                |                               |

| 42         | AVCC0                                     | <b>D</b> 10*2     |                                   |                                                                                |                               |

| 43         | VREFH0                                    | PJ6*2             |                                   |                                                                                | 414000                        |

| A4         |                                           | P42*2             |                                   |                                                                                | AN002                         |

| A5         |                                           | P41* <sup>2</sup> |                                   |                                                                                | AN001                         |

| A6         |                                           | PE2               | MTIOC4A                           | RXD12/RXDX12/SMISO12/SSCL12                                                    | IRQ7/AN010                    |

| 31         | RES#                                      |                   |                                   |                                                                                |                               |

| B2         |                                           | P27               | MTIOC2B                           | SCK1/SCK12                                                                     | IRQ3/CMPA2/CACREF/<br>ADTRG0# |

| 33         | VREFL0                                    | PJ7*2             |                                   |                                                                                |                               |

| 34         |                                           | PE0               | MTIOC2A/POE3#                     | SCK12                                                                          | IRQ0/AN008                    |

| B5         |                                           | PE1               | MTIOC4C                           | TXD12/TXDX12/SIOX12/SMOSI12/<br>SSDA12                                         | IRQ1/AN009                    |

| B6         |                                           | PA3               | MTIOC0D/MTCLKD/<br>MTIOC1B/POE0#  | RXD5/SMISO5/SSCL5/MISOA                                                        | IRQ6                          |

| C1         | XTAL                                      |                   |                                   |                                                                                |                               |

| C2         | MD                                        |                   |                                   |                                                                                | FINED                         |

| C3         |                                           | PE3               | MTIOC0A/MTIOC1B/<br>MTIOC4B/POE8# | CTS12#/RTS12#/SS12#/RSPCKA                                                     | IRQ3/AN011                    |

| C4         |                                           | PE4               | MTIOC1A/MTIOC3A/<br>MTIOC4D       | MOSIA                                                                          | IRQ4/AN012                    |

| C5         |                                           | PA4               | MTIOC2B/MTIC5U/MTCLKA             | TXD5/SMOSI5/SSDA5/SSLA0                                                        | IRQ5                          |

| C6         | VSS                                       |                   |                                   |                                                                                |                               |

| D1         | EXTAL                                     |                   |                                   |                                                                                |                               |

| D2         | UPSEL                                     | P35               |                                   |                                                                                | NMI                           |

| D3         | UB#                                       | P14               | MTIOC0A/MTIOC3A/<br>MTCLKA        | CTS1#/RTS1#/SS1#/SSLA0/TXD12/<br>TXDX12/SIOX12/SMOSI12/<br>SSDA12/USB0_OVRCURA | IRQ4                          |

| D4         |                                           | PA6               | MTIC5V/MTCLKB/MTIOC2A/<br>POE2#   | CTS5#/RTS5#/SS5#/SDA0/MOSIA                                                    | IRQ3                          |

| D5         |                                           | PB3               | MTIOC0A/MTIOC3B/<br>MTIOC4A/POE3# | USB0_OVRCURA                                                                   |                               |

| D6         |                                           | PB0               | MTIOC0C/MTIC5W                    | SCL0/RSPCKA                                                                    | IRQ2/ADTRG0#                  |

| Ξ1         | VCL                                       |                   |                                   |                                                                                |                               |

| E2         |                                           | P17               | MTIOC0C/MTIOC3A/<br>MTIOC3B/POE8# | SCK1/MISOA/SDA0/RXD12/<br>RXDX12/SMISO12/SSCL12                                | IRQ7                          |

| E3         |                                           | P16               | MTIOC3C/MTIOC3D                   | TXD1/SMOSI1/SSDA1/SCL0/<br>MOSIA/USB0_VBUSEN/<br>USB0_OVRCURB/USB0_VBUS        | IRQ6/ADTRG0#                  |

| E4         |                                           | P15               | MTIOC0B/MTCLKB                    | RXD1/SMISO1/SSCL1/RSPCKA                                                       | IRQ5/CLKOUT                   |

| E5         |                                           | PC4               | MTIOC3D/MTCLKC/POE0#              | SCK5/SSLA0/USB0_VBUSEN/<br>USB0_VBUS*1                                         | IRQ2/CLKOUT                   |

| E6         | VCC                                       |                   |                                   |                                                                                |                               |

| =1         | VSS                                       |                   |                                   |                                                                                |                               |

| F2         | VCC                                       |                   |                                   |                                                                                |                               |

| F3         | VCC_USB                                   |                   |                                   |                                                                                |                               |

| F4         |                                           |                   |                                   | USB0_DM                                                                        |                               |

| -5         |                                           |                   |                                   | USB0_DP                                                                        |                               |

| -6         | VSS_USB                                   |                   |                                   |                                                                                |                               |

|            | Not 5 V tolerant.                         |                   |                                   |                                                                                |                               |

Table 1.9

List of Pins and Pin Functions (36-Pin WFLGA)

Note 1. Not 5 V tolerant.

Note 2. The power source of the I/O buffer for these pins is AVCC0.

| Table 4.1 | List of I/O Registers (Address Order) (11/16) |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Address    | Module<br>Symbol | Register Name                                 | Register<br>Symbol | Number of<br>Bits | Access<br>Size | Number of Acces<br>States |

|------------|------------------|-----------------------------------------------|--------------------|-------------------|----------------|---------------------------|

| 0008 B127h | ELC              | Port Buffer Register 1                        | PDBF1              | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B129h | ELC              | Event Link Port Setting Register 0            | PEL0               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B12Ah | ELC              | Event Link Port Setting Register 1            | PEL1               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B12Dh | ELC              | Event Link Software Event Generation Register | ELSEGR             | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B300h | SCI12            | Serial Mode Register                          | SMR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B301h | SCI12            | Bit Rate Register                             | BRR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B302h | SCI12            | Serial Control Register                       | SCR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B303h | SCI12            | Transmit Data Register                        | TDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B304h | SCI12            | Serial Status Register                        | SSR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B305h | SCI12            | Receive Data Register                         | RDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B306h | SCI12            | Smart Card Mode Register                      | SCMR               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B307h | SCI12            | Serial Extended Mode Register                 | SEMR               | 8                 | 8              | 2 or 3 PCLKB              |

| 0008 B308h | SCI12            | Noise Filter Setting Register                 | SNFR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B309h  | SCI12            | I <sup>2</sup> C Mode Register 1              | SIMR1              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Ah  | SCI12            | I <sup>2</sup> C Mode Register 2              | SIMR2              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Bh  | SCI12            | I <sup>2</sup> C Mode Register 3              | SIMR3              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Ch  | SCI12            | I <sup>2</sup> C Status Register              | SISR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B30Dh  | SCI12            | SPI Mode Register                             | SPMR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B320h  | SCI12            | Extended Serial Mode Enable Register          | ESMER              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B321h  | SCI12            | Control Register 0                            | CR0                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B322h  | SCI12            | Control Register 1                            | CR1                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B323h  | SCI12            | Control Register 2                            | CR2                | 8                 | 8              | 2 or 3 PCLKB              |

|            | SCI12            |                                               | CR3                | 8                 | 8              |                           |

| 008 B324h  |                  | Control Register 3 Port Control Register      | PCR                |                   |                | 2 or 3 PCLKB              |

| 008 B325h  | SCI12            | Port Control Register                         |                    | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B326h  | SCI12            | Interrupt Control Register                    | ICR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B327h  | SCI12            | Status Register                               | STR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B328h  | SCI12            | Status Clear Register                         | STCR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B329h  | SCI12            | Control Field 0 Data Register                 | CF0DR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Ah  | SCI12            | Control Field 0 Compare Enable Register       | CF0CR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Bh  | SCI12            | Control Field 0 Receive Data Register         | CF0RR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Ch  | SCI12            | Primary Control Field 1 Data Register         | PCF1DR             | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Dh  | SCI12            | Secondary Control Field 1 Data Register       | SCF1DR             | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Eh  | SCI12            | Control Field 1 Compare Enable Register       | CF1CR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B32Fh  | SCI12            | Control Field 1 Receive Data Register         | CF1RR              | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B330h  | SCI12            | Timer Control Register                        | TCR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B331h  | SCI12            | Timer Mode Register                           | TMR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B332h  | SCI12            | Timer Prescaler Register                      | TPRE               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 B333h  | SCI12            | Timer Count Register                          | TCNT               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C000h  | PORT0            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C001h  | PORT1            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C002h  | PORT2            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C003h  | PORT3            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C004h  | PORT4            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C005h  | PORT5            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Ah  | PORTA            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Bh  | PORTB            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Ch  | PORTC            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C00Eh  | PORTE            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C012h  | PORTJ            | Port Direction Register                       | PDR                | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C020h  | PORT0            | Port Output Data Register                     | PODR               | 8                 | 8              | 2 or 3 PCLKB              |

| 008 C021h  | PORT1            | Port Output Data Register                     | PODR               | 8                 | 8              | 2 or 3 PCLKB              |

|            | PORT2            | Port Output Data Register                     | PODR               | 8                 | 8              | 2 or 3 PCLKB              |

## 5.2 DC Characteristics

### Table 5.3DC Characteristics (1)

Conditions:  $2.7 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 2.7 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                         | Item                                                                                                                                                                                                                         | Symbol          | Min.        | Тур. | Max.        | Unit | Test<br>Conditions |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------|-------------|------|--------------------|

| Schmitt trigger<br>input voltage        | RIIC input pin<br>(except for SMBus, 5 V tolerant)                                                                                                                                                                           | V <sub>IH</sub> | VCC × 0.7   | —    | 5.8         | V    |                    |

|                                         | Ports P16, P17,<br>port PA6, port PB0 (5 V tolerant)                                                                                                                                                                         |                 | VCC × 0.8   | _    | 5.8         |      |                    |

|                                         | Ports P03, P05,<br>ports P14,P15,<br>ports P26, P27,<br>ports P30 to P32, P35,<br>ports P54, P55,<br>ports PA0, PA1, PA3, PA4,<br>ports PB1, PB3, PB5 to PB7,<br>ports PC2 to PC7,<br>ports PE0 to PE7,<br>port PH7,<br>RES# |                 | VCC × 0.8   | _    | VCC + 0.3   |      |                    |

|                                         | RIIC input pin<br>(except for SMBus)                                                                                                                                                                                         | V <sub>IL</sub> | -0.3        | _    | VCC × 0.3   |      |                    |

|                                         | Other than RIIC input pin                                                                                                                                                                                                    |                 | -0.3        | _    | VCC × 0.2   |      |                    |

|                                         | RIIC input pin<br>(except for SMBus)                                                                                                                                                                                         | ΔV <sub>T</sub> | VCC × 0.05  | _    | -           |      |                    |

|                                         | Other than RIIC input pin                                                                                                                                                                                                    |                 | VCC × 0.1   | _    | —           |      |                    |

| Input voltage                           | MD                                                                                                                                                                                                                           | V <sub>IH</sub> | VCC × 0.9   |      | VCC + 0.3   | V    |                    |

| (except for Schmitt trigger input pins) | XTAL (external clock input)                                                                                                                                                                                                  |                 | VCC × 0.8   |      | VCC + 0.3   |      |                    |

| ingger input pins)                      | Ports P40 to P44, P46, ports PJ6,<br>PJ7                                                                                                                                                                                     |                 | AVCC0 × 0.7 | —    | AVCC0 + 0.3 |      |                    |

|                                         | RIIC input pin (SMBus)                                                                                                                                                                                                       |                 | 2.1         |      | VCC + 0.3   |      |                    |

|                                         | MD                                                                                                                                                                                                                           | V <sub>IL</sub> | -0.3        | _    | VCC × 0.1   |      |                    |

|                                         | XTAL (external clock input)                                                                                                                                                                                                  | 1               | -0.3        |      | VCC × 0.2   |      |                    |

|                                         | Ports P40 to P44, P46, ports PJ6,<br>PJ7                                                                                                                                                                                     |                 | -0.3        | —    | AVCC0 × 0.3 |      |                    |

|                                         | RIIC input pin (SMBus)                                                                                                                                                                                                       |                 | -0.3        | _    | 0.8         |      |                    |

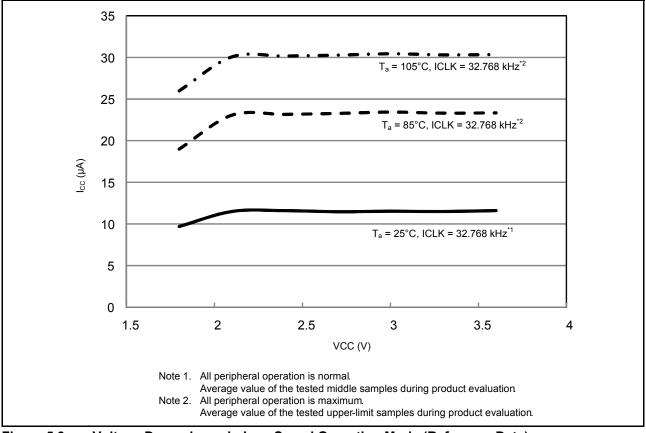

Figure 5.3 Voltage Dependency in Low-Speed Operating Mode (Reference Data)

### [256-Kbyte or more flash memory]

Table 5.8DC Characteristics (6) (1/2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|           |                    |                   | Item                                              |               | Symbol          | Typ<br>*4 | Max  | Unit | Test<br>Conditions |

|-----------|--------------------|-------------------|---------------------------------------------------|---------------|-----------------|-----------|------|------|--------------------|

| Supply    | High-speed         | Normal            | No peripheral                                     | ICLK = 32 MHz | I <sub>CC</sub> | 3.6       | _    | mA   |                    |

| current*1 | operating<br>mode  | operating<br>mode | operation*2                                       | ICLK = 16 MHz |                 | 2.4       | —    |      |                    |

|           | mode               |                   |                                                   | ICLK = 8 MHz  | -               | 1.8       | _    |      |                    |

|           |                    |                   | All peripheral operation:                         | ICLK = 32 MHz |                 | 13.4      | —    |      |                    |

|           |                    |                   | Normal* <sup>3</sup>                              | ICLK = 16 MHz |                 | 7.5       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 8 MHz  |                 | 4.5       | —    |      |                    |

|           |                    |                   | All peripheral operation:<br>Max.* <sup>3</sup>   | ICLK = 32 MHz |                 | —         | 27   |      |                    |

|           |                    | Sleep mode        | No peripheral                                     | ICLK = 32 MHz |                 | 1.9       | —    |      |                    |

|           |                    |                   | operation*2                                       | ICLK = 16 MHz |                 | 1.5       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 8 MHz  |                 | 1.3       | —    |      |                    |

|           |                    |                   | All peripheral operation:                         | ICLK = 32 MHz |                 | 7.6       | —    |      |                    |

|           |                    |                   | Normal* <sup>3</sup>                              | ICLK = 16 MHz |                 | 4.4       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 8 MHz  |                 | 2.8       | —    |      |                    |

|           |                    | Deep sleep        | No peripheral                                     | ICLK = 32 MHz |                 | 1.1       | —    |      |                    |

|           |                    | mode              | operation*2                                       | ICLK = 16 MHz |                 | 1.0       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 8 MHz  |                 | 0.9       | —    |      |                    |

|           |                    |                   | All peripheral operation:<br>Normal* <sup>3</sup> | ICLK = 32 MHz |                 | 5.8       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 16 MHz |                 | 3.4       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 8 MHz  |                 | 2.1       | _    |      |                    |

|           |                    | Increase duri     | Increase during flash rewrite*5                   |               |                 |           | —    |      |                    |

|           | Middle-speed       |                   | No peripheral                                     | ICLK = 12 MHz | I <sub>CC</sub> | 2.1       | —    | mA   |                    |

|           | operating<br>modes | operating<br>mode | operation* <sup>6</sup>                           | ICLK = 8 MHz  |                 | 1.4       | —    |      |                    |

|           | modes              |                   |                                                   | ICLK = 1 MHz  |                 | 0.8       | —    |      |                    |

|           |                    |                   | All peripheral operation:<br>Normal* <sup>7</sup> | ICLK = 12 MHz |                 | 5.9       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 8 MHz  |                 | 4.2       | _    |      |                    |

|           |                    |                   |                                                   | ICLK = 1 MHz  |                 | 1.3       | _    |      |                    |

|           |                    |                   | All peripheral operation: Max.* <sup>7</sup>      | ICLK = 12 MHz |                 | —         | 12.2 |      |                    |

|           |                    | Sleep mode        |                                                   | ICLK = 12 MHz | -               | 1.4       | —    | -    |                    |

|           |                    |                   | operation*6                                       | ICLK = 8 MHz  |                 | 0.9       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 1 MHz  |                 | 0.7       |      |      |                    |

|           |                    |                   | All peripheral operation:                         | ICLK = 12 MHz |                 | 3.6       | —    | -    |                    |

|           |                    |                   | Normal* <sup>7</sup>                              | ICLK = 8 MHz  |                 | 2.5       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 1 MHz  |                 | 1.1       | —    |      |                    |

|           |                    | Deep sleep        | No peripheral                                     | ICLK = 12 MHz | ]               | 1.1       | —    |      |                    |

|           |                    | mode              | operation* <sup>6</sup>                           | ICLK = 8 MHz  | 1 1             | 0.6       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 1 MHz  | 1               | 0.6       | —    |      |                    |

|           |                    |                   | All peripheral operation:                         | ICLK = 12 MHz | 1 1             | 2.9       | —    |      |                    |

|           |                    |                   | Normal* <sup>7</sup>                              | ICLK = 8 MHz  |                 | 2.0       | —    |      |                    |

|           |                    |                   |                                                   | ICLK = 1 MHz  |                 | 0.9       | —    |      |                    |

|           |                    | Incroaco duri     | ng flash rewrite* <sup>5</sup>                    |               | 1 1             | 2.5       | L    | 1    |                    |

#### [256-Kbyte or more flash memory]

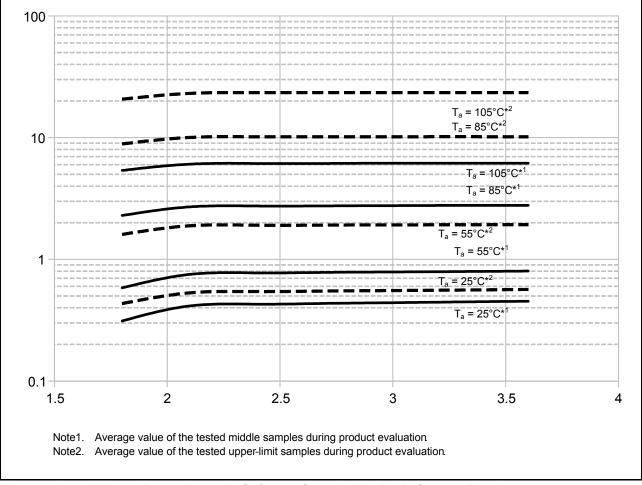

#### Table 5.10DC Characteristics (8)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item             |                               |                        | Symbol          | Typ.* <sup>3</sup> | Max. | Unit | Test Conditions        |

|------------------|-------------------------------|------------------------|-----------------|--------------------|------|------|------------------------|

| Supply current*1 | Software standby              | T <sub>a</sub> = 25°C  | I <sub>CC</sub> | 0.44               | 0.98 | μA   |                        |

|                  | mode*2                        | T <sub>a</sub> = 55°C  |                 | 0.80               | 3.47 |      |                        |

|                  |                               | T <sub>a</sub> = 85°C  |                 | 2.7                | 12.0 |      |                        |

|                  |                               | T <sub>a</sub> = 105°C |                 | 6.17               | 42.7 |      |                        |

|                  | Increment for RTC operation*4 |                        |                 | 0.31               | _    |      | RCR3.RTCDV[2:0] = 010b |

|                  |                               |                        |                 | 1.09               |      |      | RCR3.RTCDV[2:0] = 100b |

|                  | Increment for IWD             | T operation            |                 | 0.37               |      |      |                        |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. The IWDT and LVD are stopped.

Note 3. VCC = 3.3 V.

Note 4. Includes the oscillation circuit.

#### Table 5.12 DC Characteristics (10)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

|                                     | Item                                                                                                                                                                                                                                                                                                              | Symbol               | Min. | Typ.* <sup>7</sup>                      | Max. | Unit | Test<br>Conditions |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----------------------------------------|------|------|--------------------|

| Analog power                        | During A/D conversion (at high-speed conversion)                                                                                                                                                                                                                                                                  | I <sub>AVCC</sub>    | —    | 0.7                                     | 1.2  | mA   |                    |

| supply current                      | Waiting for A/D (all units)                                                                                                                                                                                                                                                                                       |                      |      | —                                       | 0.3  | μA   |                    |

|                                     | During D/A conversion (per channel)*5                                                                                                                                                                                                                                                                             |                      |      | —                                       | 1.5  | mA   |                    |

| Reference                           | During A/D conversion (at high-speed conversion)                                                                                                                                                                                                                                                                  | I <sub>REFH0</sub>   |      | 25                                      | 52   | μA   |                    |

| power supply<br>current             | Waiting for A/D conversion (all units)                                                                                                                                                                                                                                                                            |                      |      | —                                       | 60   | nA   |                    |

| Temperature<br>sensor* <sup>6</sup> |                                                                                                                                                                                                                                                                                                                   | I <sub>TEMP</sub>    | —    | 75                                      | -    | μA   |                    |

| LDV1, 2                             | Per channel                                                                                                                                                                                                                                                                                                       | I <sub>LVD</sub>     | —    | 0.15                                    | —    | μA   |                    |

| USB<br>operating<br>current         | <ul> <li>During USB communication operation under the following settings and conditions</li> <li>Host controller operation is set to full-speed mode Bulk OUT transfer (64 bytes) × 1, bulk IN transfer (64 bytes) × 1</li> <li>Connect peripheral devices via a 1-meter USB cable from the USB port.</li> </ul>  |                      | _    | 4.3<br>(VCC)<br>0.9<br>(VCC_USB)<br>*4  | _    | mA   |                    |

|                                     | <ul> <li>During USB communication operation under the following settings and conditions</li> <li>Function controller operation is set to full-speed mode Bulk OUT transfer (64 bytes) × 1, bulk IN transfer (64 bytes) × 1</li> <li>Connect the host device via a 1-meter USB cable from the USB port.</li> </ul> | I <sub>USBF</sub> *2 |      | 3.6<br>(VCC)<br>1.1<br>(VCC_USB)<br>*4  |      | mA   |                    |

|                                     | <ul> <li>During suspended state under the following setting and conditions</li> <li>Function controller operation is set to full-speed mode<br/>(pull up the USB0_DP pin)</li> <li>Software standby mode</li> <li>Connect the host device via a 1-meter USB cable from the<br/>USB port.</li> </ul>               | I <sub>SUSP</sub> *3 |      | 0.35<br>(VCC)<br>170<br>(VCC_USB)<br>*4 | _    | μA   |                    |

Note 1. The reference power supply current is included in the power supply current value for D/A conversion.

Note 2. Current consumed only by the USB module.

Note 3. Includes the current supplied from the pull-up resistor of the USB0\_DP pin to the pull-down resistor of the host device, in addition to the current consumed by this MCU during the suspended state.

Note 4. When VCC = VCC\_USB = 3.3 V.

Note 5. The value of the current flowing to VCC.

Note 6. Current consumed by the power supply (VCC). Note 7. When VCC = AVCC0 = VCC\_USB = 3.3 V.

### Table 5.13 DC Characteristics (11)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                | Symbol           | Min. | Тур. | Max. | Unit | Test Conditions |

|---------------------|------------------|------|------|------|------|-----------------|

| RAM standby voltage | V <sub>RAM</sub> | 1.8  | —    |      | V    |                 |

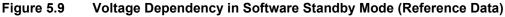

Figure 5.14 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> Temperature Characteristics of General Ports (Except for the RIIC Output Pin, Ports P40 to P44, P46, Ports PJ6, PJ7) at VCC = 2.7 V (Reference Data)

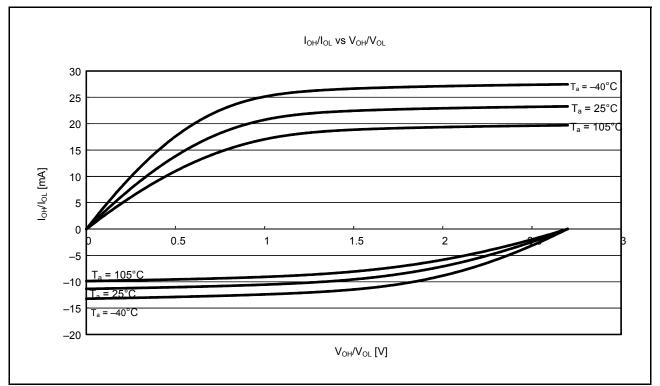

Figure 5.15 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> Temperature Characteristics of General Ports (Except for the RIIC Output Pin, Ports P40 to P44, P46, Ports PJ6, PJ7) at VCC = 3.3 V (Reference Data)

RENESAS

### 5.3 AC Characteristics

### 5.3.1 Clock Timing

#### Table 5.21 Operation Frequency Value (High-Speed Operating Mode)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{\text{USB}} = 0 \text{ V}, \text{ T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

|                   |                                   |                  | VCC          |              |              |                      |      |  |

|-------------------|-----------------------------------|------------------|--------------|--------------|--------------|----------------------|------|--|

| Item              |                                   | Symbol           | 1.8 to 2.4 V | 2.4 to 2.7 V | 2.7 to 3.6 V | When USB<br>in Use*4 | Unit |  |

| Maximum operating | System clock (ICLK)               | f <sub>max</sub> | 8            | 16           | 32           | 24                   | MHz  |  |

| frequency         | FlashIF clock (FCLK)*1, *2        |                  | 8            | 16           | 32           | 24                   |      |  |

|                   | Peripheral module clock (PCLKB)   |                  | 8            | 16           | 32           | 24                   |      |  |

|                   | Peripheral module clock (PCLKD)*3 |                  | 8            | 16           | 32           | 24                   |      |  |

|                   | USB clock (UCLK)                  | f <sub>usb</sub> | _            | —            | _            | 48                   |      |  |

Note 1. The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note 2. The frequency accuracy of FCLK should be ±3.5%. Confirm the frequency accuracy of the clock source.

Note 3. The lower-limit frequency of PCLKD is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the A/D converter is in use. Note 4. The VCC\_USB range is 3.0 to 3.6 V when the USB clock is in use.

#### Table 5.22 Operation Frequency Value (Middle-Speed Operating Mode)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item              |                                   |                  | VCC          |              |              |                      |      |  |

|-------------------|-----------------------------------|------------------|--------------|--------------|--------------|----------------------|------|--|

|                   |                                   |                  | 1.8 to 2.4 V | 2.4 to 2.7 V | 2.7 to 3.6 V | When USB<br>in Use*4 | Unit |  |

| Maximum operating | System clock (ICLK)               | f <sub>max</sub> | 8            | 12           | 12           | 12                   | MHz  |  |

| frequency         | FlashIF clock (FCLK)*1, *2        |                  | 8            | 12           | 12           | 12                   |      |  |

|                   | Peripheral module clock (PCLKB)   |                  | 8            | 12           | 12           | 12                   |      |  |

|                   | Peripheral module clock (PCLKD)*3 |                  | 8            | 12           | 12           | 12                   |      |  |

|                   | USB clock (UCLK)                  | f <sub>usb</sub> | _            | —            | _            | 48                   |      |  |

Note 1. The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note 2. The frequency accuracy of FCLK should be  $\pm 3.5\%$ .

Note 3. The lower-limit frequency of PCLKD is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the A/D converter is in use.

Note 4. The VCC\_USB range is 3.0 to 3.6 V when the USB clock is in use.

### Table 5.23 Operation Frequency Value (Low-Speed Operating Mode)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{USB} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{USB} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                     |                        |                  |              | Unit         |              |  |  |

|------------------------------------------|------------------------|------------------|--------------|--------------|--------------|--|--|

|                                          |                        |                  | 1.8 to 2.4 V | 2.4 to 2.7 V | 2.7 to 3.6 V |  |  |

| Maximum operating                        | System clock (ICLK)    | f <sub>max</sub> |              |              | kHz          |  |  |

| frequency                                | FlashIF clock (FCLK)*1 |                  |              |              |              |  |  |

| Peripheral module clock (PCLKB) 32.76    |                        |                  |              | 32.768       | 68           |  |  |

| Peripheral module clock (PCLKD)*2 32.768 |                        |                  |              |              |              |  |  |

Note 1. Programming and erasing the flash memory is impossible.

Note 2. The A/D converter cannot be used.

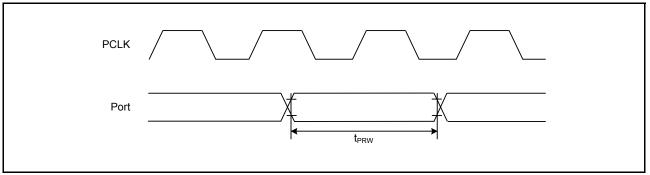

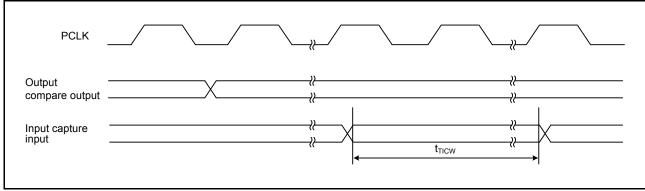

#### Table 5.33 Timing of On-Chip Peripheral Modules (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{VCC}_{\text{USB}} \le 3.6 \text{ V}, 1.8 \text{ V} \le \text{AVSS0} \le 3.6 \text{ V}, \text{VSS} = \text{AVSS0} = \text{VSS}_{\text{USB}} = 0 \text{ V},$  $T_a = -40$  to +105°C, C = 30 pF

|                                          |                                 | Item                                                                                |                                                                   | Symbol                           | Min.                                                                     | Max.                                           | Unit              | Test<br>Conditions |  |

|------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------|------------------------------------------------|-------------------|--------------------|--|

| יו                                       | RSPCK clock                     | Master                                                                              |                                                                   | t <sub>SPcyc</sub>               | 2                                                                        | 4096                                           | t <sub>Pcyc</sub> | Figure 5.46        |  |

|                                          | cycle                           | Slave                                                                               | Slave                                                             |                                  | 8                                                                        | 4096                                           | *1                |                    |  |

|                                          | RSPCK clock<br>high pulse width | Master                                                                              |                                                                   | t <sub>SPCKWH</sub>              | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 | _                                              | ns                |                    |  |

|                                          |                                 | Slave                                                                               |                                                                   |                                  | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     | —                                              |                   |                    |  |

|                                          | RSPCK clock<br>low pulse width  | Master                                                                              |                                                                   | t <sub>SPCKWL</sub>              | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 | —                                              | ns                |                    |  |

|                                          |                                 | Slave                                                                               |                                                                   |                                  | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     | _                                              |                   |                    |  |

| ſ                                        | RSPCK clock                     | Output                                                                              | 2.7 V or above                                                    | t <sub>SPCKr,</sub>              | —                                                                        | 10                                             | ns                |                    |  |

|                                          | rise/fall time                  |                                                                                     | 1.8 V or above                                                    | t <sub>SPCKf</sub>               | _                                                                        | 15                                             |                   |                    |  |

|                                          |                                 | Input                                                                               |                                                                   |                                  | _                                                                        | 1                                              | μs                |                    |  |

| Ī                                        | Data input setup                | Master                                                                              | 2.7 V or above                                                    | t <sub>SU</sub>                  | 10                                                                       | _                                              | ns                | Figure 5.47 to     |  |

|                                          | time                            |                                                                                     | 1.8 V or above                                                    |                                  | 30                                                                       | _                                              |                   | Figure 5.52        |  |

|                                          |                                 | Slave                                                                               |                                                                   |                                  | 25 – t <sub>Pcyc</sub>                                                   | _                                              |                   |                    |  |

|                                          | Data input hold time            | Master                                                                              | RSPCK set to a<br>division ratio other than<br>PCLKB divided by 2 | t <sub>H</sub>                   | t <sub>Pcyc</sub>                                                        | _                                              | ns                |                    |  |

|                                          |                                 |                                                                                     | RSPCK set to PCLKB divided by 2                                   | t <sub>HF</sub>                  | 0                                                                        | _                                              |                   |                    |  |

|                                          |                                 | Slave                                                                               |                                                                   | t <sub>H</sub>                   | 20 + 2 × t <sub>Pcyc</sub>                                               | _                                              |                   |                    |  |

| Ē                                        | SSL setup time                  | Master                                                                              |                                                                   | t <sub>LEAD</sub>                | -30 + N*2 × t <sub>SPcyc</sub>                                           | _                                              | ns                | +                  |  |

|                                          |                                 | Slave                                                                               |                                                                   |                                  | 2                                                                        | _                                              | t <sub>Pcyc</sub> | -                  |  |

| Ē                                        | SSL hold time                   | Master                                                                              |                                                                   | t <sub>LAG</sub>                 | –30 + N* <sup>3</sup> × t <sub>SPcyc</sub>                               | _                                              | ns                | ĺ                  |  |

|                                          |                                 | Slave                                                                               |                                                                   |                                  | 2                                                                        | _                                              | t <sub>Pcyc</sub> |                    |  |