# E. Renesas Electronics America Inc - <u>R5S72660W144FP#V0 Datasheet</u>

#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IEBus, SCI, SIO, SPI, USB                               |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 80                                                                                 |

| Program Memory Size        |                                                                                    |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 1.5M x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.15V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 144-LQFP                                                                           |

| Supplier Device Package    | 144-LFQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72660w144fp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics. Renesas Electronics product for any application application categorized as "Specific" or for which the prior written consent of Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronic data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

| Instruction Formats                      | Source<br>Operand                                                                                                                                                     | Destination<br>Operand                            | Example                 |           |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------|-----------|--|--|

| m format                                 | mmmm: Register<br>direct                                                                                                                                              | Control register or<br>system register            | LDC                     | Rm,SR     |  |  |

| XXXX mmmm XXXX XXXX                      | mmmm: Register<br>indirect with post-<br>increment                                                                                                                    | Control register or system register               | LDC.L                   | @Rm+,SR   |  |  |

|                                          | mmmm: Register indirect                                                                                                                                               |                                                   | JMP                     | @Rm       |  |  |

|                                          | mmmm: Register<br>indirect with pre-<br>decrement                                                                                                                     | R0 (Register direct)                              | MOV.L                   | @-Rm,R0   |  |  |

|                                          | mmmm: PC relative using Rm                                                                                                                                            |                                                   | BRAF                    | Rm        |  |  |

| nm format                                | mmmm: Register<br>direct                                                                                                                                              | nnnn: Register<br>direct                          | ADD                     | Rm,Rn     |  |  |

| xxxx nnnn mmmm xxxx                      | mmmm: Register<br>direct                                                                                                                                              | nnnn: Register<br>indirect                        | MOV.L                   | Rm,@Rn    |  |  |

|                                          | mmmm: Register<br>indirect with post-<br>increment (multiply-<br>and-accumulate)<br>nnnn*: Register<br>indirect with post-<br>increment (multiply-<br>and-accumulate) | MACH, MACL                                        | MAC.W                   | @Rm+,@Rn+ |  |  |

|                                          | mmmm: Register<br>indirect with post-<br>increment                                                                                                                    | nnnn: Register<br>direct                          | MOV.L                   | @Rm+,Rn   |  |  |

|                                          | mmmm: Register<br>direct                                                                                                                                              | nnnn: Register<br>indirect with pre-<br>decrement | MOV.L                   | Rm,@−Rn   |  |  |

| _                                        | mmmm: Register<br>direct                                                                                                                                              | nnnn: Indexed<br>register indirect                | MOV.L<br>Rm,@(R0,Rn)    |           |  |  |

| md format<br>15 0<br>xxxx xxxx mmmm dddd | mmmmdddd:<br>Register indirect<br>with displacement                                                                                                                   | R0 (Register direct)                              | MOV.B<br>@(dis <u>r</u> | o,Rm),RO  |  |  |

# Section 11 Multi-Function Timer Pulse Unit 2

This LSI has an on-chip multi-function timer pulse unit 2 that comprises five 16-bit timer channels.

# 11.1 Features

- Maximum 16 pulse input/output lines

- Selection of eight counter input clocks for each channel

- The following operations can be set:

- Waveform output at compare match

- Input capture function

- Counter clear operation

- Multiple timer counters (TCNT) can be written to simultaneously

- Simultaneous clearing by compare match and input capture is possible

- Register simultaneous input/output is possible by synchronous counter operation

- A maximum 12-phase PWM output is possible in combination with synchronous operation

- Buffer operation settable for channels 0, 3, and 4

- Phase counting mode settable independently for each of channels 1 and 2

- Cascade connection operation

- Fast access via internal 16-bit bus

- 25 interrupt sources

- Automatic transfer of register data

- A/D converter start trigger can be generated

- Module standby mode can be settable

- A total of six-phase waveform output, which includes complementary PWM output, and positive and negative phases of reset PWM output by interlocking operation of channels 3 and 4, is possible.

- AC synchronous motor (brushless DC motor) drive mode using complementary PWM output and reset PWM output is settable by interlocking operation of channels 0, 3, and 4, and the selection of two types of waveform outputs (chopping and level) is possible.

- In complementary PWM mode, interrupts at the crest and trough of the counter value and A/D converter start triggers can be skipped.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                 |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------|

| 4   | TCIEV    | 0                | R/W | Overflow Interrupt Enable                                                                                                   |

|     |          |                  |     | Enables or disables interrupt requests (TCIV) by the TCFV flag when the TCFV flag in TSR is set to 1.                       |

|     |          |                  |     | 0: Interrupt requests (TCIV) by TCFV disabled                                                                               |

|     |          |                  |     | 1: Interrupt requests (TCIV) by TCFV enabled                                                                                |

| 3   | TGIED    | 0                | R/W | TGR Interrupt Enable D                                                                                                      |

|     |          |                  |     | Enables or disables interrupt requests (TGID) by the TGFD bit when the TGFD bit in TSR is set to 1 in channels 0, 3, and 4. |

|     |          |                  |     | In channels 1 and 2, bit 3 is reserved. It is always read as 0 and the write value should always be 0.                      |

|     |          |                  |     | 0: Interrupt requests (TGID) by TGFD bit disabled                                                                           |

|     |          |                  |     | 1: Interrupt requests (TGID) by TGFD bit enabled                                                                            |

| 2   | TGIEC    | 0                | R/W | TGR Interrupt Enable C                                                                                                      |

|     |          |                  |     | Enables or disables interrupt requests (TGIC) by the TGFC bit when the TGFC bit in TSR is set to 1 in channels 0, 3, and 4. |

|     |          |                  |     | In channels 1 and 2, bit 2 is reserved. It is always read as 0 and the write value should always be 0.                      |

|     |          |                  |     | 0: Interrupt requests (TGIC) by TGFC bit disabled                                                                           |

|     |          |                  |     | 1: Interrupt requests (TGIC) by TGFC bit enabled                                                                            |

| 1   | TGIEB    | 0                | R/W | TGR Interrupt Enable B                                                                                                      |

|     |          |                  |     | Enables or disables interrupt requests (TGIB) by the TGFB bit when the TGFB bit in TSR is set to 1.                         |

|     |          |                  |     | 0: Interrupt requests (TGIB) by TGFB bit disabled                                                                           |

|     |          |                  |     | 1: Interrupt requests (TGIB) by TGFB bit enabled                                                                            |

| 0   | TGIEA    | 0                | R/W | TGR Interrupt Enable A                                                                                                      |

|     |          |                  |     | Enables or disables interrupt requests (TGIA) by the TGFA bit when the TGFA bit in TSR is set to 1.                         |

|     |          |                  |     | 0: Interrupt requests (TGIA) by TGFA bit disabled                                                                           |

|     |          |                  |     | 1: Interrupt requests (TGIA) by TGFA bit enabled                                                                            |

## 11.3.6 Timer Buffer Operation Transfer Mode Register (TBTM)

The TBTM registers are 8-bit readable/writable registers that specify the timing for transferring data from the buffer register to the timer general register in PWM mode. This module has three TBTM registers, one each for channels 0, 3, and 4.

| TTSE TTSB                  | 7 | 6      | 5 | 4 | 3 | 2        | 1        | 0        |

|----------------------------|---|--------|---|---|---|----------|----------|----------|

| Initial value: 0 0 0 0 0 0 | - | -      | - | - | - | TTSE     | TTSB     | TTSA     |

| R/W: R R R R R R/W R/W     |   | 0<br>B | - | - | - | 0<br>B/W | 0<br>B/W | 0<br>B/W |

|        |          | Initial |     |                                                                                                                                |

|--------|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                                                                    |

| 7 to 3 | _        | All 0   | R   | Reserved                                                                                                                       |

|        |          |         |     | These bits are always read as 0. The write value should always be 0.                                                           |

| 2      | TTSE     | 0       | R/W | Timing Select E                                                                                                                |

|        |          |         |     | Specifies the timing for transferring data from TGRF_0<br>to TGRE_0 when they are used together for buffer<br>operation.       |

|        |          |         |     | In channels 3 and 4, bit 2 is reserved. It is always read as 0 and the write value should always be 0.                         |

|        |          |         |     | 0: When compare match E occurs in channel 0                                                                                    |

|        |          |         |     | 1: When TCNT_0 is cleared                                                                                                      |

| 1      | TTSB     | 0       | R/W | Timing Select B                                                                                                                |

|        |          |         |     | Specifies the timing for transferring data from TGRD to TGRB in each channel when they are used together for buffer operation. |

|        |          |         |     | 0: When compare match B occurs in each channel                                                                                 |

|        |          |         |     | 1: When TCNT is cleared in each channel                                                                                        |

| 0      | TTSA     | 0       | R/W | Timing Select A                                                                                                                |

|        |          |         |     | Specifies the timing for transferring data from TGRC to TGRA in each channel when they are used together for buffer operation. |

|        |          |         |     | 0: When compare match A occurs in each channel                                                                                 |

|        |          |         |     | 1: When TCNT is cleared in each channel                                                                                        |

|        |          |         |     |                                                                                                                                |

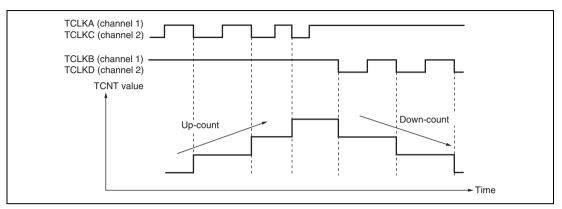

#### (c) Phase counting mode 3

Figure 11.32 shows an example of phase counting mode 3 operation, and table 11.48 summarizes the TCNT up/down-count conditions.

| TCLKA (Channel 1)<br>TCLKC (Channel 2) | TCLKB (Channel 1)<br>TCLKD (Channel 2) | Operation  |

|----------------------------------------|----------------------------------------|------------|

| High level                             | _F                                     | Don't care |

| Low level                              | <u> </u>                               | Don't care |

|                                        | Low level                              | Don't care |

| <u> </u>                               | High level                             | Up-count   |

| High level                             | T_                                     | Down-count |

| Low level                              | _                                      | Don't care |

| _ <b>_</b>                             | High level                             | Don't care |

| T_                                     | Low level                              | Don't care |

|                                        |                                        |            |

[Legend]

F: Rising edge

E: Falling edge

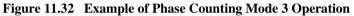

#### Figure 15.3 shows a sample flowchart for initialization.

- [1] Set the clock selection in SCSCR. Be sure to clear bits TIE, RIE, TE, and RE to 0.

- [2] Set the data transfer format in SCSMR.

- [3] Write a value corresponding to the bit rate into SCBRR. (Not necessary if an external clock is used.)

- [4] Sets the general I/O port external pins used. Set as RxD input at receiving and TxD at transmission.

However, no setting for SCK pin is required when CKE[1:0] is 00.

In the case when internal synchronous clock output is set, the SCK pin starts outputting the clock at this stage.

- [5] Set the TE bit or RE bit in SCSCR to 1. Also set the RIE, REIE, and TIE bits. Setting the TE and RE bits enables the TxD and RxD pins to be used.

When transmitting, the SCIF will go to the mark state; when receiving, it will go to the idle state, waiting for a start bit.

Figure 15.3 Sample Flowchart for Initialization

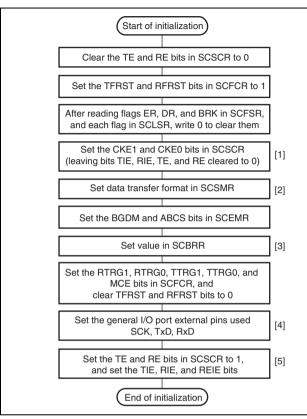

#### 17.3.7 Sequence Status Register (SPSSR)

SPSSR indicates the sequence control status.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                        |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------------------------|

| 7 to 2 | —        | All 0            | R   | Reserved                                                                                           |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                               |

| 1      | SPSS1    | 0                | R   | Sequence Status                                                                                    |

| 0      | SPSS0    | 0                | R   | During sequence control, these bits indicate one of SPCMD0 to SPCMD3 that is currently referenced. |

|        |          |                  |     | 00: SPCMD0                                                                                         |

|        |          |                  |     | 01: SPCMD1                                                                                         |

|        |          |                  |     | 10: SPCMD2                                                                                         |

|        |          |                  |     | 11: SPCMD3                                                                                         |

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                        |

|------|----------|------------------|-----|----------------------------------------------------------------------------------------------------|

| 11   | TDLA3    | 0                | R/W | Transmit Left-Channel Data Assigns 3 to 0                                                          |

| 10   | TDLA2    | 0                | R/W | Specify the position of left-channel data in a transmit                                            |

| 9    | TDLA1    | 0                | R/W | frame as B'0000 (0) to B'1110 (14).                                                                |

| 8    | TDLA0    | 0                | R/W | 1111: Setting prohibited                                                                           |

| _    |          |                  |     | <ul> <li>Transmit data for the left channel is specified in the<br/>SITDL bit in SITDR.</li> </ul> |

| 7    | TDRE     | 0                | R/W | Transmit Right-Channel Data Enable                                                                 |

|      |          |                  |     | 0: Disables right-channel data transmission                                                        |

|      |          |                  |     | 1: Enables right-channel data transmission                                                         |

| 6    | TLREP    | 0                | R/W | Transmit Left-Channel Repeat                                                                       |

|      |          |                  |     | 0: Transmits data specified in the SITDR bit in SITDR as right-channel data                        |

|      |          |                  |     | 1: Repeatedly transmits data specified in the SITDL bit in<br>SITDR as right-channel data          |

|      |          |                  |     | • This bit setting is valid when the TDRE bit is set to 1.                                         |

|      |          |                  |     | <ul> <li>When this bit is set to 1, the SITDR settings are ignored.</li> </ul>                     |

| 5, 4 |          | All 0            | R   | Reserved                                                                                           |

|      |          |                  |     | These bits are always read as 0. The write value should always be 0.                               |

| 3    | TDRA3    | 0                | R/W | Transmit Right-Channel Data Assigns 3 to 0                                                         |

| 2    | TDRA2    | 0                | R/W | Specify the position of right-channel data in a transmit                                           |

| 1    | TDRA1    | 0                | R/W | frame as B'0000 (0) to B'1110 (14).                                                                |

| 0    | TDRA0    | 0                | R/W | 1111: Setting prohibited                                                                           |

|      |          |                  |     | Transmit data for the right channel is specified in the SITDR bit in SITDR.                        |

- 3. Implementation Guide for the CAN Protocol, CAN Specification 2.0 Addendum, CAN In Automation, Erlangen, Germany, 1997

- 4. Road vehicles Controller area network (CAN): Part 1: Data link layer and physical signalling (ISO-11898-1, 2003)

- 5. Road vehicles Controller area network (CAN): Part 4: Time triggered communication (ISO-11898-4, 2004)

#### 21.1.5 Features

- Supports CAN specification 2.0B

- Bit timing compliant with ISO-11898-1

- 32 Mailbox version

- Clock frequency: Up to 36 MHz

- 31 programmable Mailboxes for transmit / receive + 1 receive-only mailbox

- Sleep mode for low power consumption and automatic recovery from sleep mode by detecting CAN bus activity

- Programmable receive filter mask (standard and extended identifier) supported by all Mailboxes

- Programmable CAN data rate up to 1MBit/s

- Transmit message queuing with internal priority sorting mechanism against the problem of priority inversion for real-time applications

- Data buffer access without SW handshake requirement in reception

- Flexible micro-controller interface

- Flexible interrupt structure

- 16-bit free running timer with flexible clock sources and pre-scaler, 3 Timer Compare Match Registers

- 6-bit Basic Cycle Counter for Time Trigger Transmission

- Timer Compare Match Registers with interrupt generation

- Timer counter clear / set capability

- Registers for Time-Trigger: Local\_Time, Cycle\_time, Ref\_Mark, Tx\_Enable Window, Ref\_Trigger\_Offset

- Flexible TimeStamp at SOF for both transmission and reception supported

- Time-Trigger Transmission, Periodic Transmission supported (on top of Event Trigger Transmission)

- Basic Cycle value can be embedded into a CAN frame and transmitted

**Bit 15 to 0**—Remote Request pending flags for mailboxes 31 to 16 respectively.

| Bit[15:0]: RFPR1 | Description                                                                        |

|------------------|------------------------------------------------------------------------------------|

| 0                | [Clearing Condition] Writing '1' (Initial value)                                   |

| 1                | Corresponding Mailbox received Remote Frame                                        |

|                  | [Setting Condition]<br>Completion of remote frame receive in corresponding mailbox |

#### RFPR0

| Bit:           | 15        | 14        | 13        | 12        | 11        | 10 | 9 | 8         | 7       | 6 | 5 | 4 | 3 | 2         | 1         | 0         |

|----------------|-----------|-----------|-----------|-----------|-----------|----|---|-----------|---------|---|---|---|---|-----------|-----------|-----------|

|                |           |           |           |           |           |    |   | RFPR      | 0[15:0] |   |   |   |   |           |           |           |

|                |           |           |           |           |           |    |   |           |         |   |   |   |   |           |           |           |

| Initial value: | 0<br>R/W* | 0<br>B/W* | 0<br>R/W* | 0<br>R/W* | 0<br>R/W* | 0  | 0 | 0<br>R/W* | 0       | 0 | 0 | 0 | 0 | 0<br>R/W* | 0<br>R/W* | 0<br>B/W* |

Note: \* Only when writing a '1' to clear.

**Bit 15 to 0** — Remote Request pending flags for mailboxes 15 to 0 respectively.

| Bit[15:0]: RFPR0 | Description                                                                        |

|------------------|------------------------------------------------------------------------------------|

| 0                | [Clearing Condition] Writing '1' (Initial value)                                   |

| 1                | Corresponding Mailbox received Remote Frame                                        |

|                  | [Setting Condition]<br>Completion of remote frame receive in corresponding mailbox |

#### Mailbox Interrupt Mask Register (MBIMR) (7)

The MBIMR1 and MBIMR0 are 16-bit read/write registers. The MBIMR only prevents the setting of IRR related to the Mailbox activities, that are IRR[1] – Data Frame Received Interrupt, IRR[2] - Remote Frame Receive Interrupt, IRR[8] - Mailbox Empty Interrupt, and IRR[9] - Message OverRun/OverWrite Interrupt. If a mailbox is configured as receive, a mask at the corresponding bit position prevents the generation of a receive interrupt (IRR[1] and IRR[2] and IRR[9]) but does not prevent the setting of the corresponding bit in the RXPR or RFPR or UMSR. Similarly when a mailbox has been configured for transmission, a mask prevents the generation of an Interrupt signal and setting of an Mailbox Empty Interrupt due to successful transmission or abortion of transmission (IRR[8]), however, it does not prevent this module from clearing the corresponding TXPR/TXCR bit + setting the TXACK bit for successful transmission, and it does not prevent this module from clearing the corresponding TXPR/TXCR bit + setting the ABACK bit for abortion of the transmission.

# 21.4.5 Reconfiguration of Mailbox

When re-configuration of Mailboxes is required, the following procedures should be taken.

• Change configuration of transmit box

Two cases are possible.

- Change of ID, RTR, IDE, LAFM, Data, DLC, NMC, ATX, DART This change is possible only when MBC = 3'b000. Confirm that the corresponding TXPR is not set. The configuration (except MBC bit) can be changed at any time.

- Change from transmit to receive configuration (MBC)

Confirm that the corresponding TXPR is not set. The configuration can be changed only in Halt or reset state. Please note that it might take longer for this module to transit to halt state if it is receiving or transmitting a message (as the transition to the halt state is delayed until the end of the reception/transmission), and also this module will not be able to receive/transmit messages during the Halt state.

In case this module is in the Bus Off state the transition to halt state depends on the configuration of the bit 6 of MCR and also bit and 14 of MCR.

• Change configuration (ID, RTR, IDE, LAFM, Data, DLC, NMC, ATX, DART, MBC) of receiver box or Change receiver box to transmitter box

The configuration can be changed only in Halt Mode.

This module will not lose a message if the message is currently on the CAN bus and this module is a receiver. This module will be moving into Halt Mode after completing the current reception. Please note that it might take longer if this module is receiving or transmitting a message (as the transition to the halt state is delayed until the end of the reception/transmission), and also this module will not be able to receive/transmit messages during the Halt Mode.

In case this module is in the Bus Off state the transition to halt mode depends on the configuration of the bit 6 and 14 of MCR.

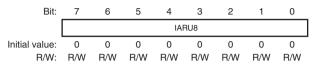

# 22.3.5 IEBus Master Unit Address Register 2 (IEAR2)

IEAR2 sets the upper eight bits of the master unit address. In master communications, this register becomes the master address field value. In slave communications, this register is compared with the received slave address field.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                |

|--------|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 0 | IARU8    | All 0            | R/W | Upper 8 Bits of IEBus Master Unit Address                                                                                                                                                                  |

|        |          |                  |     | Set the upper 8 bits of the master unit address. This register becomes the master address field value. In slave communications, the master unit address is compared with the received slave address field. |

# 22.3.6 IEBus Slave Address Setting Register 1 (IESA1)

IESA1 sets the lower four bits of the communications destination slave unit address.

| Bit:           | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|----------------|-----|-----|-----|-----|---|---|---|---|

|                |     | IS/ | AL4 |     | - | - | - | - |

| Initial value: | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 |

| R/W:           | R/W | R/W | R/W | R/W | R | R | R | R |

|        |          | Initial |     |                                                                                      |

|--------|----------|---------|-----|--------------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                          |

| 7 to 4 | ISAL4    | 0000    | R/W | Lower 4 Bits of IEBus Slave Address                                                  |

|        |          |         |     | These bits set the lower 4 bits of the communication destination slave unit address. |

| 3 to 0 | _        | All 0   | R   | Reserved                                                                             |

|        |          |         |     | These bits are always read as 0. The write value should always be 0.                 |

# 22.3.7 IEBus Slave Address Setting Register 2 (IESA2)

IESA2 sets the upper eight bits of the communications destination slave unit address.

# 22.3.17 IEBus Transmit Interrupt Enable Register (IEIET)

IEIET enables/disables interrupts for sources such as transmit start, transmit normal completion, and transmit error completion in IETSR.

| Bit:           | 7 | 6    | 5    | 4 | 3      | 2            | 1      | 0           |

|----------------|---|------|------|---|--------|--------------|--------|-------------|

|                | - | TXSE | TXFE | - | TXEALE | TXE<br>TTMEE | TXEROE | TXE<br>ACKE |

| Initial value: | 0 | 0    | 0    | 0 | 0      | 0            | 0      | 0           |

| R/W:           | R | R/W  | R/W  | R | R/W    | R/W          | R/W    | R/W         |

|     |          | Initial |     |                                                                   |

|-----|----------|---------|-----|-------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                       |

| 7   | _        | 0       | R   | Reserved                                                          |

|     |          |         |     | This bit is always read as 0. The write value should always be 0. |

| 6   | TXSE     | 0       | R/W | Transmit Start Interrupt Enable                                   |

|     |          |         |     | Enables/disables a transmit start (TXS) interrupt.                |

|     |          |         |     | 0: Disables a transmit start (TXS) interrupt                      |

|     |          |         |     | 1: Enables a transmit start (TXS) interrupt                       |

| 5   | TXFE     | 0       | R/W | Transmit Normal Completion Interrupt Enable                       |

|     |          |         |     | Enables/disables a transmit normal completion (TXF) interrupt.    |

|     |          |         |     | 0: Disables a transmit normal completion (TXF)<br>interrupt       |

|     |          |         |     | 1: Enables a transmit normal completion (TXF) interrupt           |

| 4   |          | 0       | R   | Reserved                                                          |

|     |          |         |     | This bit is always read as 0. The write value should always be 0. |

| 3   | TXEALE   | 0       | R/W | Arbitration Loss Interrupt Enable                                 |

|     |          |         |     | Enables/disables an arbitration loss (TXEAL) interrupt.           |

|     |          |         |     | 0: Disables an arbitration loss (TXEAL) interrupt                 |

|     |          |         |     | 1: Enables an arbitration loss (TXEAL) interrupt                  |

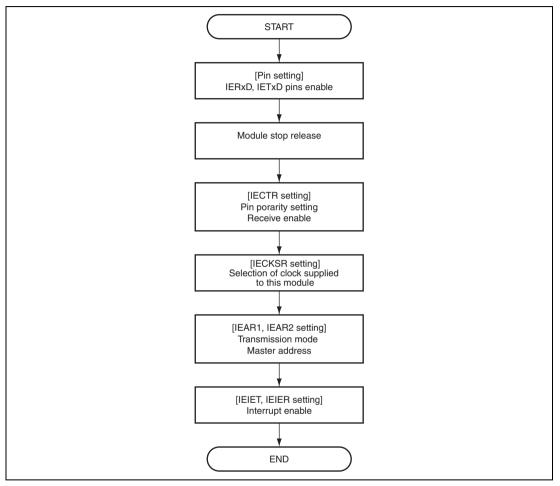

# 22.5 Software Control Flows

#### 22.5.1 Initial Setting

Figure 22.8 shows the flowchart for the initial setting.

Figure 22.8 Flowchart for Initial Setting

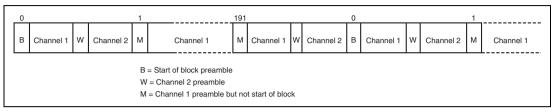

Figure 23.4 shows the block format, which consists of 192 continuous frames. One block begins at the starting frame (preamble B) and ends at the 192nd frame (frame 191), and the preamble is used to identify all subframes. Each block has a total of 384 subframes, which are classified into three categories: subframe 0 indicating the beginning of a new block, subframe 1 (usually the channel 1), and subframe 2 (usually the channel 2). Usually, the music data sent and received by the SPDIF is continuous so that continuous blocks appear.

Figure 23.4 Block Format

Table 23.2 shows the binary values of the Renesas SPDIF preambles. The polarity of these preambles differs depending on the status of the preceding symbol (parity bit).

| <b>Table 23.2</b> | <b>Binary Preamble Values</b> |

|-------------------|-------------------------------|

|-------------------|-------------------------------|

| Preamble | Preceding Symbol's Status = 0 | Preceding Symbol's Status = 1 |

|----------|-------------------------------|-------------------------------|

| В        | 11101000                      | 00010111                      |

| Μ        | 11100010                      | 00011101                      |

| W        | 11100100                      | 00011011                      |

Note: As shown in figure 23.3, the even parity bit at time slot 31 of a subframe determines the type of a preamble for one cycle of transmission. Usually, therefore, any one is selected from the set states that are sent through the Renesas SPDIF. However, IEC60958 requires decoding both types in view of connection with the preamble polarity reversed; the Renesas SPDIF has preambles decoded according to table 23.2.

Channel status information is encoded at the rate of one bit per subframe, making the channel status information per block have a total of 192 bits for each of subframes 1 and 2. For the format of the channel status, refer to the IEC 60958 standard.

| Bit    | Bit Name  | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                            |

|--------|-----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 to 0 | UTST[3:0] | 0000             | R/W | (1) When the host controller function is selected<br>These bits can be set after writing 1 to DRPD. This<br>module outputs waveforms when both DRPD and                                                                                                                |

|        |           |                  |     | UACT are set to 1. This module also performs high-<br>speed termination after the UTST bits are written to.                                                                                                                                                            |

|        |           |                  |     | <ul><li>Procedure for setting the UTST bits</li><li>1. Power-on reset.</li></ul>                                                                                                                                                                                       |

|        |           |                  |     | <ol> <li>Start the clock supply (Set SCKE to 1 after<br/>the crystal oscillation and the PLL for USB<br/>are settled).</li> </ol>                                                                                                                                      |

|        |           |                  |     | <ol><li>Set DCFM and DRPD to 1 (setting HSE to 1<br/>is not required).</li></ol>                                                                                                                                                                                       |

|        |           |                  |     | <ol> <li>Set USBE to 1.</li> <li>Set the UTST bits to the appropriate value</li> </ol>                                                                                                                                                                                 |

|        |           |                  |     | according to the test specifications.                                                                                                                                                                                                                                  |

|        |           |                  |     | 6. Set the UACT bit to 1.                                                                                                                                                                                                                                              |

|        |           |                  |     | Procedure for modifying the UTST bits                                                                                                                                                                                                                                  |

|        |           |                  |     | <ol> <li>(In the state after executing step 6 above) Set<br/>UACT and USBE to 0.</li> </ol>                                                                                                                                                                            |

|        |           |                  |     | 2. Set USBE to 1.                                                                                                                                                                                                                                                      |

|        |           |                  |     | <ol><li>Set the UTST bits to the appropriate value<br/>according to the test specifications.</li></ol>                                                                                                                                                                 |

|        |           |                  |     | 4. Set the UACT bit to 1.                                                                                                                                                                                                                                              |

|        |           |                  |     | When these bits are set to Test_SE0_NAK (1011),<br>this module does not output the SOF packet even<br>when 1 is set to UACT.                                                                                                                                           |

|        |           |                  |     | When these bits are set to Test_Force_Enable (1101), this module outputs the SOF packet when 1 is set to UACT. In this test mode, this module does not perform hardware control consequent to detection of high-speed disconnection (detection of the DTCH interrupt). |

|        |           |                  |     | When setting the UTST bits, the PID bits for all the pipes should be set to NAK.                                                                                                                                                                                       |

|        |           |                  |     | To return to normal USB communication after a test mode has been set and executed, a power-on reset should be applied.                                                                                                                                                 |

This module can select the bus clock or external clock as the source of the panel clock. It also has a frequency divider providing a division ratio from 1/1 to 1/32.

|           | Clock Frequency | Input/Output Clock Frequency (MHz |                      |  |  |

|-----------|-----------------|-----------------------------------|----------------------|--|--|

| DCDR[5:0] | Division Ratio  | 60.000* <sup>2</sup>              | 72.000* <sup>2</sup> |  |  |

| 000001*1  | 1/1             | 60.000                            | 72.000               |  |  |

| 000010    | 1/2             | 30.000                            | 36.000               |  |  |

| 000011    | 1/3             | 20.000                            | 24.000               |  |  |

| 000100    | 1/4             | 15.000                            | 18.000               |  |  |

| 000110    | 1/6             | 10.000                            | 12.000               |  |  |

| 001000    | 1/8             | 7.500                             | 9.000                |  |  |

| 001100    | 1/12            | 5.000                             | 6.000                |  |  |

| 010000    | 1/16            | 3.750                             | 4.500                |  |  |

| 011000    | 1/24            | 2.500                             | 3.000                |  |  |

| 100000    | 1/32            | 1.875                             | 2.250                |  |  |

### Table 28.14 Input/Output Clock Frequency and Division Ratio

Notes: 1. Setting prohibited when the bus clock  $(B\phi)$  is selected for the source of the panel clock.

2. When the bus clock  $(B\phi)$  is selected for the source of the panel clock.

| Bit      | Bit Name    | Initial Value | R/W | Description                                                       |                         |

|----------|-------------|---------------|-----|-------------------------------------------------------------------|-------------------------|

| 14 to 12 | PF11MD[2:0] | 000           | R/W | PF11 Mode                                                         |                         |

|          |             |               |     | Select the function of the                                        | he PF11.                |

|          |             |               |     | 000: PF11                                                         | 100: TIOC3C             |

|          |             |               |     | 001: A25                                                          | 101: SPDIF_IN           |

|          |             |               |     | 010: SSIDATA3                                                     | 110: QMO/QIO0           |

|          |             |               |     | 011: MOSI0                                                        | 111: Setting prohibited |

| 11       |             | 0             | R   | Reserved                                                          |                         |

|          |             |               |     | This bit is always read should always be 0.                       | as 0. The write value   |

| 10 to 8  | PF10MD[2:0] | 000           | R/W | PF10 Mode                                                         |                         |

|          |             |               |     | Select the function of the                                        | he PF10.                |

|          |             |               |     | 000: PF10                                                         | 100: TIOC3B             |

|          |             |               |     | 001: A24                                                          | 101: FCE                |

|          |             |               |     | 010: SSIWS3                                                       | 110: QSSL               |

|          |             |               |     | 011: SSL00                                                        | 111: Setting prohibited |

| 7        |             | 0             | R   | Reserved                                                          |                         |

|          |             |               |     | This bit is always read should always be 0.                       | as 0. The write value   |

| 6 to 4   | PF9MD[2:0]  | 000           | R/W | PF9 Mode                                                          |                         |

|          |             |               |     | Select the function of the                                        | he PF9.                 |

|          |             |               |     | 000: PF9                                                          | 100: TIOC3A             |

|          |             |               |     | 001: A23                                                          | 101: FRB                |

|          |             |               |     | 010: SSISCK3                                                      | 110: QSPCLK             |

|          |             |               |     | 011: RSPCK0                                                       | 111: Setting prohibited |

| 3        |             | 0             | R   | Reserved                                                          |                         |

|          |             |               |     | This bit is always read as 0. The write value should always be 0. |                         |

| 2 to 0   | PF8MD[2:0]  | 000           | R/W | PF8 Mode                                                          |                         |

|          |             |               |     | Select the function of the                                        | he PF8.                 |

|          |             |               |     | 000: PF8                                                          | 100: Setting prohibited |

|          |             |               |     | 001: CE2B                                                         | 101: Setting prohibited |

|          |             |               |     | 010: SSIDATA2                                                     | 110: SD_CD              |

|          |             |               |     | 011: DV_CLK                                                       | 111: Setting prohibited |

SH7266 Group, SH7267 Group User's Manual: Hardware

Publication Date: Rev.3.00 Oct 31, 2016

Published by: Renesas Electronics Corporation