# E. Renesas Electronics America Inc - <u>R5S72661W144FP#V0 Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IEBus, SCI, SIO, SPI, USB                       |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 80                                                                                 |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1.5M x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.15V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 144-LQFP                                                                           |

| Supplier Device Package    | 144-LFQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72661w144fp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (3) Power-On Reset Initiated by Watchdog Timer

When a setting is made for a power-on reset to be generated in watchdog timer mode of the watchdog timer, and WTCNT of the watchdog timer overflows, this LSI enters the power-on reset state.

In this case, WRCSR of the watchdog timer and FRQCR of the clock pulse generator are not initialized by the reset signal generated by the watchdog timer.

If a reset caused by the  $\overline{\text{RES}}$  pin or the user debugging interface reset assert command occurs simultaneously with a reset caused by watchdog timer overflow, the reset caused by the  $\overline{\text{RES}}$  pin or the user debugging interface reset assert command has priority, and the WOVF bit in WRCSR is cleared to 0. When power-on reset exception processing is started by the watchdog timer, the CPU operates in the same way as when a power-on reset was caused by the  $\overline{\text{RES}}$  pin.

# 6.2.4 Manual Reset

## (1) Manual Reset Initiated by Watchdog Timer

When a setting is made for a manual reset to be generated in watchdog timer mode of the watchdog timer, and WTCNT of the watchdog timer overflows, this LSI enters the manual reset state.

When manual reset exception processing is started by the watchdog timer, the CPU operates as follows:

- 1. The initial value (execution start address) of the program counter (PC) is fetched from the exception handling vector table.

- 2. The initial value of the stack pointer (SP) is fetched from the exception handling vector table.

- 3. The vector base register (VBR) is cleared to H'00000000, the interrupt mask level bits (I3 to I0) of the status register (SR) are initialized to H'F (B'1111), and the BO and CS bits are initialized to 0. The BN bit in IBNR of interrupt controller is also initialized to 0.

- 4. The values fetched from the exception handling vector table are set in the PC and SP, and the program begins executing.

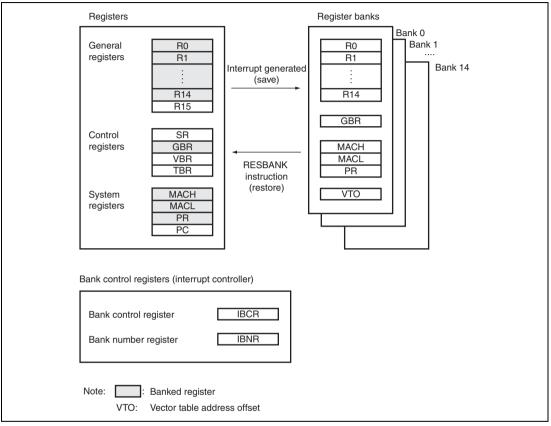

# 7.8 Register Banks

This LSI has fifteen register banks used to perform register saving and restoration required in the interrupt processing at high speed. Figure 7.10 shows the register bank configuration.

Figure 7.10 Overview of Register Bank Configuration

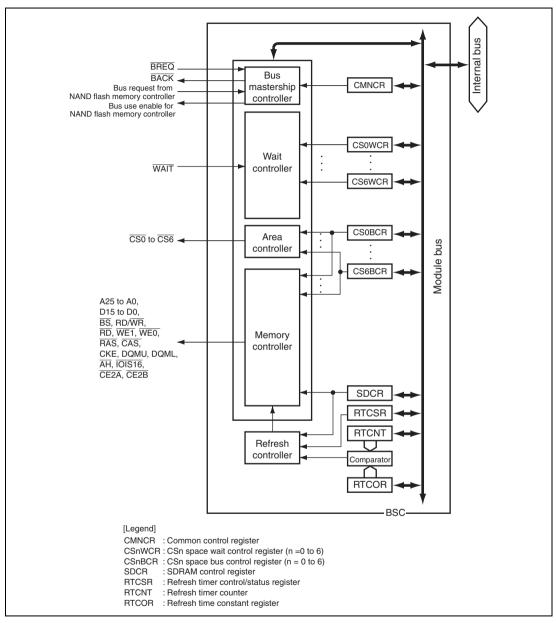

Figure 9.1 shows a block diagram of this module.

Figure 9.1 Block Diagram of Bus State Controller

### (a) Auto-refreshing

Refreshing is performed at intervals determined by the input clock selected by bits CKS2 to CKS0 in RTCSR, and the value set by in RTCOR. The value of bits CKS2 to CKS0 in RTCOR should be set so as to satisfy the refresh interval stipulation for the SDRAM used. First make the settings for RTCOR, RTCNT, and the RMODE and RFSH bits in SDCR, and then make the CKS2 to CKS0 and RRC2 to RRC0 settings. When the clock is selected by bits CKS2 to CKS0, RTCNT starts counting up from the value at that time. The RTCNT value is constantly compared with the RTCOR value, and if the two values are the same, a refresh request is generated and an auto-refresh is performed for the number of times specified by the RRC2 to RRC0. At the same time, RTCNT is cleared to zero and the count-up is restarted.

Figure 9.25 shows the auto-refresh cycle timing. After starting the auto refreshing, PALL command is issued in the Tp cycle to make all the banks to pre-charged state from active state when some bank is being pre-charged. Then REF command is issued in the Trr cycle after inserting idle cycles of which number is specified by the WTRP1 and WTRP0 bits in CS3WCR. A new command is not issued for the duration of the number of cycles specified by the WTRC1 and WTRC0 bits in CS3WCR after the Trr cycle. The WTRC1 and WTRC0 bits must be set so as to satisfy the SDRAM refreshing cycle time stipulation (tRC). An idle cycle is inserted between the Tp cycle and Trr cycle when the setting value of the WTRP1 and WTRP0 bits in CS3WCR is longer than or equal to 1 cycle.

#### (12) Low-Power SDRAM

The low-power SDRAM can be accessed using the same protocol as the normal SDRAM.

The differences between the low-power SDRAM and normal SDRAM are that partial refresh takes place that puts only a part of the SDRAM in the self-refresh state during the self-refresh function, and that power consumption is low during refresh under user conditions such as the operating temperature. The partial refresh is effective in systems in which the data in a work area other than the specific area can be lost without severe repercussions. For details, please refer to the Data Sheet for the low-power SDRAM to be used.

The low-power SDRAM supports the extension mode register in addition to the mode registers as the normal SDRAM. This LSI supports issuing of the extension mode register write command (EMRS).

The EMRS command is issued according to the conditions specified in table below. For example, if data H'0YYYYYY is written to address H'FFFC5XX0 in longword, the commands are issued to the CS3 space in the following sequence: PALL -> REF  $\times$  8 -> MRS -> EMRS. In this case, the MRS and EMRS issue addresses are H'0000XX0 and H'YYYYYY, respectively. If data H'1YYYYYYY is written to address H'FFFC5XX0 in longword, the commands are issued to the CS3 space in the following sequence: PALL -> MRS -> EMRS.

| Command to be<br>Issued             | Access<br>Address | Access Data | Write<br>Access<br>Size | MRS<br>Command<br>Issue Address | EMRS<br>Command<br>Issue Address |

|-------------------------------------|-------------------|-------------|-------------------------|---------------------------------|----------------------------------|

| CS2 MRS                             | H'FFFC4XX0        | H'*****     | 16 bits                 | H'0000XX0                       | _                                |

| CS3 MRS                             | H'FFFC5XX0        | H'*****     | 16 bits                 | H'0000XX0                       | _                                |

| CS2 MRS + EMRS<br>(with refresh)    | H'FFFC4XX0        | H'0YYYYYYY  | 32 bits                 | H'0000XX0                       | ΗΎΥΥΥΥΥ                          |

| CS3 MRS + EMRS<br>(with refresh)    | H'FFFC5XX0        | H'0YYYYYYY  | 32 bits                 | H'0000XX0                       | ΗΎΥΥΥΥΥ                          |

| CS2 MRS + EMRS<br>(without refresh) | H'FFFC4XX0        | Η'1ΥΥΥΥΥΥΥ  | 32 bits                 | H'0000XX0                       | ΗΎΥΥΥΥΥΥ                         |

| CS3 MRS + EMRS<br>(without refresh) | H'FFFC5XX0        | Η'1ΥΥΥΥΥΥΥ  | 32 bits                 | H'0000XX0                       | ΗΎΥΥΥΥΥ                          |

#### Table 9.14 Output Addresses when EMRS Command Is Issued

#### (b) Phase counting mode 2

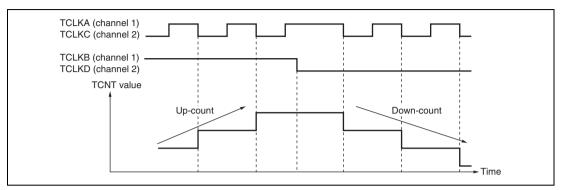

Figure 11.31 shows an example of phase counting mode 2 operation, and table 11.47 summarizes the TCNT up/down-count conditions.

Figure 11.31 Example of Phase Counting Mode 2 Operation

| Table 11.47 | Up/Down-Count Conditions in Phase Counting Mode 2 |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

| TCLKA (Channel 1)<br>TCLKC (Channel 2) | TCLKB (Channel 1)<br>TCLKD (Channel 2) | Operation  |

|----------------------------------------|----------------------------------------|------------|

| High level                             | _F                                     | Don't care |

| Low level                              | T_                                     | Don't care |

| _ <b>「</b>                             | Low level                              | Don't care |

| ₹                                      | High level                             | Up-count   |

| High level                             | T_                                     | Don't care |

| Low level                              |                                        | Don't care |

| _ <b>_</b>                             | High level                             | Don't care |

| T                                      | Low level                              | Down-count |

|                                        |                                        |            |

[Legend]

F: Rising edge

L: Falling edge

#### 15.3.10 FIFO Data Count Set Register (SCFDR)

SCFDR is a 16-bit register which indicates the quantity of data stored in the transmit FIFO data register (SCFTDR) and the receive FIFO data register (SCFRDR).

It indicates the quantity of transmit data in SCFTDR with the upper 8 bits, and the quantity of receive data in SCFRDR with the lower 8 bits. SCFDR can always be read by the CPU.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10     | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2      | 1 | 0 |

|----------------|----|----|----|----|----|--------|---|---|---|---|---|---|---|--------|---|---|

|                | -  | -  | -  |    |    | T[4:0] |   |   | - | - | - |   |   | R[4:0] |   |   |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0 | 0 |

| R/W:           | R  | R  | R  | R  | R  | R      | R | R | R | R | R | R | R | R      | R | R |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                     |

|----------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 13 | _        | All 0            | R   | Reserved                                                                                                                                                        |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                            |

| 12 to 8  | T[4:0]   | 00000            | R   | T4 to T0 bits indicate the quantity of non-transmitted data stored in SCFTDR. H'00 means no transmit data, and H'10 means that SCFTDR is full of transmit data. |

| 7 to 5   |          | All 0            | R   | Reserved                                                                                                                                                        |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                            |

| 4 to 0   | R[4:0]   | 00000            | R   | R4 to R0 bits indicate the quantity of receive data stored<br>in SCFRDR. H'00 means no receive data, and H'10<br>means that SCFRDR full of receive data.        |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                         |

|--------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5      | MST      | 0                | R/W | Master/Slave Select                                                                                                                                                                                                                                                                                                                                 |

| 4      | TRS      | 0                | R/W | Transmit/Receive Select                                                                                                                                                                                                                                                                                                                             |

|        |          |                  |     | In master mode with the I <sup>2</sup> C bus format, when<br>arbitration is lost, MST and TRS are both reset by<br>hardware, causing a transition to slave receive mode.<br>Modification of the TRS bit should be made between<br>transfer frames.                                                                                                  |

|        |          |                  |     | When seven bits after the start condition is issued in<br>slave receive mode match the slave address set to<br>SAR and the 8th bit is set to 1, TRS is automatically<br>set to 1. If an overrun error occurs in master receive<br>mode with the clocked synchronous serial format, MST<br>is cleared and the mode changes to slave receive<br>mode. |

|        |          |                  |     | Operating modes are described below according to MST and TRS combination. When clocked synchronous serial format is selected and MST = 1, clock is output.                                                                                                                                                                                          |

|        |          |                  |     | 00: Slave receive mode                                                                                                                                                                                                                                                                                                                              |

|        |          |                  |     | 01: Slave transmit mode                                                                                                                                                                                                                                                                                                                             |

|        |          |                  |     | 10: Master receive mode                                                                                                                                                                                                                                                                                                                             |

|        |          |                  |     | 11: Master transmit mode                                                                                                                                                                                                                                                                                                                            |

| 3 to 0 | CKS[3:0] | 0000             | R/W | Transfer Clock Select                                                                                                                                                                                                                                                                                                                               |

|        |          |                  |     | These bits should be set according to the necessary transfer rate (table 18.3) in master mode.                                                                                                                                                                                                                                                      |

|          |            | Initial |     |                                                                      |

|----------|------------|---------|-----|----------------------------------------------------------------------|

| Bit      | Bit Name   | Value   | R/W | Description                                                          |

| 23 to 20 | CHNO[3:0]  | All 0   | W   | Channel Number                                                       |

|          |            |         |     | 0000: Don't care                                                     |

|          |            |         |     | 0001: A (left channel)                                               |

|          |            |         |     | 0010: B (right channel)                                              |

|          |            |         |     | 0011: C                                                              |

| 19 to 16 | SRCNO[3:0] | All 0   | W   | Source Number                                                        |

|          |            |         |     | 0000: Don't care                                                     |

|          |            |         |     | 0001: 1                                                              |

|          |            |         |     | 0010: 2                                                              |

|          |            |         |     | 0011:3                                                               |

| 15 to 8  | CATCD[7:0] | All 0   | W   | Category Code (Example)                                              |

|          |            |         |     | 00000000: 2-channel general format                                   |

|          |            |         |     | 00000001: 2-channel compact disc (IEC 908)                           |

|          |            |         |     | 00000010: 2-channel PCM encoder/decoder                              |

|          |            |         |     | 00000011: 2-channel digital audio tape recorder                      |

| 7, 6     | _          | All 0   | W   | Reserved                                                             |

|          |            |         |     | The write value should always be 0.                                  |

| 5 to 1   | CTL[4:0]   | All 0   | W   | Control                                                              |

|          |            |         |     | The control bits are copied from the source (see IEC60958 standard). |

| 0        | _          | 0       | W   | Reserved                                                             |

|          |            |         |     | The write value should always be 0.                                  |

|          |            |         |     |                                                                      |

# 24.3 Register Descriptions

This module has the following registers.

#### Table 24.1 Register Configuration

| Name                                                             | Abbreviation | R/W | Initial<br>Value | Address    | Access<br>Size |

|------------------------------------------------------------------|--------------|-----|------------------|------------|----------------|

| Enable control register                                          | CROMEN       | R/W | H'00             | H'FFFF9000 | 8              |

| Sync code-based synchronization control register                 | CROMSY0      | R/W | H'89             | H'FFFF9001 | 8              |

| Decoding mode control register                                   | CROMCTL0     | R/W | H'82             | H'FFFF9002 | 8              |

| EDC/ECC check control register                                   | CROMCTL1     | R/W | H'D1             | H'FFFF9003 | 8              |

| Automatic decoding stop control register                         | CROMCTL3     | R/W | H'00             | H'FFFF9005 | 8              |

| Decoding option setting control register                         | CROMCTL4     | R/W | H'00             | H'FFFF9006 | 8              |

| HEAD20 to HEAD22 representation<br>control register              | CROMCTL5     | R/W | H'00             | H'FFFF9007 | 8              |

| Sync code status register                                        | CROMST0      | R   | H'00             | H'FFFF9008 | 8              |

| Post-ECC header error status register                            | CROMST1      | R   | H'00             | H'FFFF9009 | 8              |

| Post-ECC subheader error status register                         | CROMST3      | R   | H'00             | H'FFFF900B | 8              |

| Header/subheader validity check status register                  | CROMST4      | R   | H'00             | H'FFFF900C | 8              |

| Mode determination and link sector detection status register     | CROMST5      | R   | H'00             | H'FFFF900D | 8              |

| ECC/EDC error status register                                    | CROMST6      | R   | H'00             | H'FFFF900E | 8              |

| Buffer status register                                           | CBUFST0      | R   | H'00             | H'FFFF9014 | 8              |

| Decoding stoppage source status register                         | CBUFST1      | R   | H'00             | H'FFFF9015 | 8              |

| Buffer overflow status register                                  | CBUFST2      | R   | H'00             | H'FFFF9016 | 8              |

| Pre-ECC correction header:<br>minutes data register              | HEAD00       | R   | H'00             | H'FFFF9018 | 8              |

| Pre-ECC correction header: seconds data register                 | HEAD01       | R   | H'00             | H'FFFF9019 | 8              |

| Pre-ECC correction header:<br>frames (1/75 second) data register | HEAD02       | R   | H'00             | H'FFFF901A | 8              |

| Pre-ECC correction header:<br>mode data register                 | HEAD03       | R   | H'00             | H'FFFF901B | 8              |

#### 26.3.5 Address Register 2 (FLADR2)

FLADR2 is a 32-bit readable/writable register, and is valid when the ADRCNT2 bit in FLCMDCR is set to 1. FLADR2 specifies an address to be output in command access mode.

| Bit:           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22  | 21  | 20  | 19     | 18  | 17  | 16  |

|----------------|----|----|----|----|----|----|----|----|-----|-----|-----|-----|--------|-----|-----|-----|

|                | -  | -  | -  | -  | -  | -  | -  | -  | -   | -   | -   | -   | -      | -   | -   | -   |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0      | 0   | 0   | 0   |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R   | R   | R   | R   | R      | R   | R   | R   |

|                |    |    |    |    |    |    |    |    |     |     |     |     |        |     |     |     |

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7   | 6   | 5   | 4   | 3      | 2   | 1   | 0   |

|                | -  | -  | -  | -  | -  | -  | -  | -  |     |     |     | ADR | 5[7:0] |     |     |     |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0      | 0   | 0   | 0   |

| R/W:           | R  | R  | R  | R  | R  | R  | R  | R  | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

|         |           | Initial |     |                                                                             |

|---------|-----------|---------|-----|-----------------------------------------------------------------------------|

| Bit     | Bit Name  | Value   | R/W | Description                                                                 |

| 31 to 8 | _         | All 0   | R   | Reserved                                                                    |

| _       |           |         |     | These bits are always read as 0. The write value should always be 0.        |

| 7 to 0  | ADR5[7:0] | H'00    | R/W | Fifth Address Data                                                          |

|         |           |         |     | Specify 5th data to be output to flash memory as an address when ADRMD = 1. |

| Bit  | Bit Name      | Initial<br>Value | R/W  | Description                     |

|------|---------------|------------------|------|---------------------------------|

| 9    | PIPE9NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE9 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 8    | PIPE8NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE8 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 7    | PIPE7NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE7 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 6    | PIPE6NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE6 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 5    | PIPE5NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE5 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 4    | PIPE4NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE4 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 3    | PIPE3NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE3 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 2    | PIPE2NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE2 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 1    | PIPE1NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE1 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| 0    | PIPE0NRDY     | 0                | R/W* | NRDY Interrupt Status for PIPE0 |

|      |               |                  |      | 0: Interrupts not generated     |

|      |               |                  |      | 1: Interrupts generated         |

| Nata | * Only Coop h |                  |      | 1: Interrupts generated         |

Note: \* Only 0 can be written.

| Bit     | Bit Name  | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                       |

|---------|-----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 to 3 | _         | All 0            | R   | Reserved                                                                                                                                                                                                                                          |

|         |           |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                              |

| 2 to 0  | IITV[2:0] | 000              | R/W | Interval Error Detection Interval                                                                                                                                                                                                                 |

|         |           |                  |     | Specifies the interval error detection timing for the selected pipe in terms of frames, which is expressed as n-th power of 2 (n is the value to be set).                                                                                         |

|         |           |                  |     | As described later, the detailed functions are<br>different in host controller mode and in function<br>controller mode.                                                                                                                           |

|         |           |                  |     | Modify these bits when the value of CSSTS is 0, the PID bits are set to NAK, and no pipe is specified by the CURPIPE bits.                                                                                                                        |

|         |           |                  |     | Before modifying these bits after modifying the PID<br>bits for the selected pipe from BUF to NAK, check<br>that CSSTS and PBUSY are 0. However, if the PID<br>bits have been modified to NAK by this module,<br>checking PBUSY is not necessary. |

|         |           |                  |     | Before modifying these bits after USB<br>communication has been completed with these bits<br>set to a certain value, set PID to NAK and then set<br>ACLRM to 1 to initialize the interval timer.                                                  |

|         |           |                  |     | The IITV bits are invalid for PIPE3 to PIPE5; set these bits to 000 for these pipes.                                                                                                                                                              |

# (5) Register Access Wait Control

There is a restriction on the cycle time for accessing the registers of this module except for SYSSTS as given below.

Wait-related restriction: The cycle time for successive accesses to the USB 2.0 host/function module must be a duration of at least four USB clock (48 MHz) cycles (83.33 ns). To fulfill the above restriction, a register access wait control is necessary using the BWAIT[3:0] bits in BUSWAIT. The initial value is the maximum value (access cycles = 17 clock cycles). The optimum value should be found and set.

Setting example 1: When successively accessing the registers of this module

Bus clock frequency: 72 MHz

Calculation: (2 cycles (access cycles for the registers of this module) + 1 cycle (interval between successive accesses) + BWAIT)  $\times$  1/72 MHz  $\geq$  83.33 ns

#### BWAIT = 3

Setting example 2: When sending data from the on-chip high-speed RAM to the FIFO port register through DMA transfer

Bus clock frequency: 72 MHz

Calculation: (2 cycles (access cycles for the registers of this module) + 2 cycles (access cycles for the on-chip high-speed RAM) + BWAIT)  $\times$  1/72 MHz  $\geq$  83.33 ns

BWAIT = 2

#### (6) Input Clock Selection

The UCKSEL bit in SYSCFG can be used to select the input clock signal from USB\_X1 or EXTAL for this module. Stop supply of the clock signal to the USB module (SCKE = 0) when the UCKSEL bit is to be modified.

## (2) Port J Control Register 0 (PJCR0)

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10         | 9   | 8   | 7          | 6   | 5   | 4   | 3          | 2   | 1   | 0   |

|----------------|----|----|----|----|----|------------|-----|-----|------------|-----|-----|-----|------------|-----|-----|-----|

|                | -  | -  | -  | -  | -  | PJ2MD[2:0] |     | -   | PJ1MD[2:0] |     | -   | PJ  | PJ0MD[2:0] |     |     |     |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0          | 0   | 0   | 0          | 0   | 0   | 0   | 0          | 0   | 0   | 0   |

| R/W:           | R  | R  | R  | R  | R  | R/W        | R/W | R/W | R          | R/W | R/W | R/W | R          | R/W | R/W | R/W |

| Bit      | Bit Name   | Initial Value | R/W | Description                                                          |                         |  |  |  |

|----------|------------|---------------|-----|----------------------------------------------------------------------|-------------------------|--|--|--|

| 15 to 11 | _          | All 0         | R   | Reserved                                                             |                         |  |  |  |

|          |            |               |     | These bits are always read as 0. The write value should always be 0. |                         |  |  |  |

| 10 to 8  | PJ2MD[2:0] | 000           | R/W | PJ2 Mode                                                             |                         |  |  |  |

|          |            |               |     | Select the function of                                               | the PJ2.                |  |  |  |

|          |            |               |     | 000: PJ2                                                             | 100: SCK0               |  |  |  |

|          |            |               |     | 001: CTx1                                                            | 101: LCD_M_DISP         |  |  |  |

|          |            |               |     | 010: JRx0&CRx1                                                       | 110: Setting prohibited |  |  |  |

|          |            |               |     | 011: CS2                                                             | 111: Setting prohibited |  |  |  |

| 7        |            | 0             | R   | Reserved                                                             |                         |  |  |  |

|          |            |               |     | This bit is always read should always be 0.                          | l as 0. The write value |  |  |  |

| 6 to 4   | PJ1MD[2:0] | 000           | R/W | PJ1 Mode                                                             |                         |  |  |  |

|          |            |               |     | Select the function of                                               | the PJ1.                |  |  |  |

|          |            |               |     | 000: PJ1                                                             | 100: RxD0               |  |  |  |

|          |            |               |     | 001: CRx0                                                            | 101: Setting prohibited |  |  |  |

|          |            |               |     | 010: IERxD                                                           | 110: Setting prohibited |  |  |  |

|          |            |               |     | 011: IRQ0                                                            | 111: Setting prohibited |  |  |  |

| 3        |            | 0             | R   | Reserved                                                             |                         |  |  |  |

|          |            |               |     | This bit is always read should always be 0.                          | l as 0. The write value |  |  |  |

| 2 to 0   | PJ0MD[2:0] | 000           | R/W | PJ0 Mode                                                             |                         |  |  |  |

|          |            |               |     | Select the function of                                               | the PJ0.                |  |  |  |

|          |            |               |     | 000: PJ0                                                             | 100: TxD0               |  |  |  |

|          |            |               |     | 001: CTx0                                                            | 101: A0                 |  |  |  |

|          |            |               |     | 010: IERxD                                                           | 110: Setting prohibited |  |  |  |

|          |            |               |     | 011: CS1                                                             | 111: Setting prohibited |  |  |  |

# 34.4 Operation

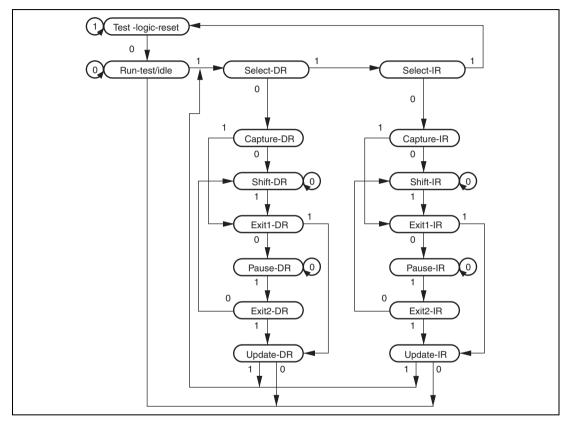

#### 34.4.1 TAP Controller

Figure 34.2 shows the internal states of the TAP controller.

Figure 34.2 TAP Controller State Transitions

Note: The transition condition is the TMS value at the rising edge of TCK. The TDI value is sampled at the rising edge of TCK; shifting occurs at the falling edge of TCK. For details on transition timing of the TDO value, see section 34.4.3, TDO Output Timing. The TDO is at high impedance, except with shift-DR and shift-IR states. During the change to  $\overline{\text{TRST}}$  = 0, there is a transition to test-logic-reset asynchronously with TCK.

|                      | Register     |                |                |                |                |                |                |               |               |

|----------------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|

| Module Name          | Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1 | Bit 24/16/8/0 |

| Direct memory        | RDMATCR_14   | _              | _              | _              | _              | _              | _              | _             | _             |

| access<br>controller |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      | SAR_15       |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      | DAR_15       |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      | DMATCR_15    | _              | _              | _              | _              | _              | _              | _             |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      | CHCR_15      | тс             | _              | RLDSAR         | RLDDAR         | _              | DAF            | SAF           |               |

|                      |              | _              | _              | _              | TEMASK         | HE             | HIE            | _             | _             |

|                      |              | DM[1]          | DM[0]          | SM[1]          | SM[0]          | RS[3]          | RS[2]          | RS[1]         | RS[0]         |

|                      |              | _              | _              | ТВ             | TS[1]          | TS[0]          | IE             | TE            | DE            |

|                      | RSAR_15      |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      | RDAR_15      |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                      |              |                |                |                |                |                |                |               |               |

|                       | Register     |                |                |                |                |                |                |               |               |

|-----------------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|

| Module Name           | Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1 | Bit 24/16/8/0 |

| Multi-function        | TGRA_0       |                |                |                |                |                |                |               |               |

| timer pulse<br>unit 2 |              |                |                |                |                |                |                |               |               |

|                       | TGRB_0       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TGRC_0       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TGRD_0       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TGRE_0       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TGRF_0       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TIER2_0      | TTGE2          | —              | —              | _              | _              | _              | TGIEF         | TGIEE         |

|                       | TSR2_0       | _              | —              | —              | _              | _              | _              | TGFF          | TGFE          |

|                       | TBTM_0       | _              | _              | _              | _              |                | TTSE           | TTSB          | TTSA          |

|                       | TCR_1        | _              | CCLR[1]        | CCLR[0]        | CKEG[1]        | CKEG[0]        | TPSC[2]        | TPSC[1]       | TPSC[0]       |

|                       | TMDR_1       | _              | _              | _              | _              | MD[3]          | MD[2]          | MD[1]         | MD[0]         |

|                       | TIOR_1       | IOB[3]         | IOB[2]         | IOB[1]         | IOB[0]         | IOA[3]         | IOA[2]         | IOA[1]        | IOA[0]        |

|                       | TIER_1       | TTGE           | _              | TCIEU          | TCIEV          |                |                | TGIEB         | TGIEA         |

|                       | TSR_1        | TCFD           | _              | TCFU           | TCFV           |                |                | TGFB          | TGFA          |

|                       | TCNT_1       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TGRA_1       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TGRB_1       |                |                |                |                |                |                |               |               |

|                       |              |                |                |                |                |                |                |               |               |

|                       | TICCR        | _              | _              | _              | _              | I2BE           | I2AE           | I1BE          | I1AE          |

|                       | TCR_2        | _              | CCLR[1]        | CCLR[0]        | CKEG[1]        | CKEG[0]        | TPSC[2]        | TPSC[1]       | TPSC[0]       |

|                       | TMDR_2       | _              | _              | _              | _              | MD[3]          | MD[2]          | MD[1]         | MD[0]         |

|                       | TIOR_2       | IOB[3]         | IOB[2]         | IOB[1]         | IOB[0]         | IOA[3]         | IOA[2]         | IOA[1]        | IOA[0]        |

|                       | TIER_2       | TTGE           | _              | TCIEU          | TCIEV          | _              | _              | TGIEB         | TGIEA         |

(TED = 0 Cycle, TEH = 0 Cycle, No Wait)

| SSLND               |

|---------------------|

| SSLP                |

| STAT 1197           |

| STBCR1 1787         |

| STBCR2 1788         |

| STBCR3 1789         |

| STBCR4 1791         |

| STBCR5 1794         |

| STBCR6 1796         |

| STBCR7 1798         |

| STBCR8              |

| STRMDIN0            |

| STRMDIN2            |

| STRMDOUT01277       |

| SWRSTCR 1801        |

| SYSCFG 1374         |

| SYSCR1              |

| SYSCR2              |

| SYSCR3 1805         |

| SYSCR4 1807         |

| SYSCR5 1808         |

| SYSSTS              |

| TADCOBRA_4          |

| TADCOBRB_4          |

| TADCORA_4           |

| TADCORB 4           |

| 457                 |

| TBTER               |

| TBTM                |

| TCBR                |

| TCDR                |

| TCMR0 to TCMR2 1085 |

| TCNT                |

| TCNTR               |

| TCNTS               |

| TCR                 |

| TDAD                |

| TDDR                |

| TDER                |

| TEC 1060            |

| 120                 |

| TESTMODE 1387 |   |

|---------------|---|

| TGCR          |   |

| TGR 461       |   |

| TICCR         |   |

| TIER          | ) |

| TIOR          | , |

| TITCNT        |   |

| TITCR         | 1 |

| TLCA 1201     |   |

| TLCS 1205     |   |

| TMDR          |   |

| TOCR1         | , |

| TOCR2         |   |

| TOER          | , |

| TOLBR         |   |

| TRCA 1202     | , |

| TRCS 1207     |   |

| TRWER         |   |

| TSR 449, 1081 |   |

| TSTR          |   |

| TSYR 463      |   |

| TTCR0         |   |

| TTTSEL 1087   |   |

| TUI 1204      |   |

| TWCR          |   |

| TXACK01068    |   |

| TXACK11067    |   |

| TXCR0 1067    |   |

| TXCR11066     |   |

| TXPR0 1065    |   |

| TXPR1 1064    |   |

| UFRMNUM1431   |   |

| UMSR01074     |   |

| UMSR11074     |   |

| USBADDR 1432  |   |

| USBINDX1435   |   |

| USBLENG 1436  |   |

| USBREQ1433    |   |

| USBVAL 1434   |   |

| WRCSR         |   |