# E·XFL Renesas Electronics America Inc - <u>R5S72670P144FP#VZ Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IEBus, SCI, SIO, SPI, USB                               |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 104                                                                                |

| Program Memory Size        | ·                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1.5M x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.15V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 176-LQFP                                                                           |

| Supplier Device Package    | 176-LFQFP (24x24)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72670p144fp-vz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 24.3.21            | Pre-ECC Correction Subheader: File Number (Byte 16) Data Register<br>(SHEAD00)  | 56 |

|--------------------|---------------------------------------------------------------------------------|----|

| 24.3.22            | Pre-ECC Correction Subheader: Channel Number (Byte 17) Data Register            |    |

| 24.3.23            | (SHEAD01)                                                                       |    |

| 24.3.24            | (SHEAD02)                                                                       |    |

| 24.3.25            | Pre-ECC Correction Subheader: File Number (Byte 20) Data Register               |    |

| 24.3.26            | (SHEAD04)                                                                       |    |

| 24.3.27            | (SHEAD05)                                                                       |    |

| 24.3.28            | Pre-ECC Correction Subheader: Data Type (Byte 23) Data Register<br>(SHEAD07)    |    |

| 24.3.29            | Post-ECC Correction Header: Minutes Data Register (HEAD20)                      |    |

| 24.3.30            | Post-ECC Correction Header: Seconds Data Register (HEAD21) 120                  |    |

| 24.3.31            | Post-ECC Correction Header: Frames (1/75 Second) Data Register                  |    |

| 24 2 22            | (HEAD22)                                                                        |    |

| 24.3.32<br>24.3.33 | Post-ECC Correction Reader: Mode Data Register (HEAD25)                         | 32 |

| 24.3.33            | (SHEAD20)                                                                       | 62 |

| 24.3.34            | Post-ECC Correction Subheader: Channel Number (Byte 17) Data Register (SHEAD21) | 63 |

| 24.3.35            | Post-ECC Correction Subheader: Sub-Mode (Byte 18) Data Register<br>(SHEAD22)    |    |

| 24.3.36            | Post-ECC Correction Subheader: Data Type (Byte 19) Data Register<br>(SHEAD23)   |    |

| 24.3.37            | Post-ECC Correction Subheader: File Number (Byte 20) Data Register (SHEAD24)    |    |

| 24.3.38            | Post-ECC Correction Subheader: Channel Number (Byte 21) Data Register (SHEAD25) | 65 |

| 24.3.39            | Post-ECC Correction Subheader: Sub-Mode (Byte 22) Data Register<br>(SHEAD26)    | 65 |

| 24.3.40            | Post-ECC Correction Subheader: Data Type (Byte 23) Data Register<br>(SHEAD27)   |    |

| 24.3.41            | Automatic Buffering Setting Control Register 0 (CBUFCTL0)                       |    |

| 24.3.42            | Automatic Buffering Start Sector Setting: Minutes Control Register              | 50 |

|                    | (CBUFCTL1)                                                                      | 58 |

| Peripheral Module                | Setting Value for One<br>Channel ({MID, RID}) | MID      | RID  | Function |

|----------------------------------|-----------------------------------------------|----------|------|----------|

| Compare match timer<br>Channel 1 | H'FF                                          | B'111111 | B'11 |          |

| Renesas quad serial              | H'A1                                          | B'101000 | B'01 | Transmit |

| peripheral interface             | H'A2                                          |          | B'10 | Receive  |

When MID or RID other than the values listed in table 10.3 is set, the operation of this LSI is not guaranteed. The transfer request from DMARS is valid only when the resource select bits (RS3 to RS0) in CHCR0 to CHCR15 have been set to B'1000. Otherwise, even if DMARS has been set, the transfer request source is not accepted.

#### Table 11.20 TIORL\_0 (Channel 0)

|               |               |                                                                                                   |                                                                                                                                                                                                                                                                          | Description                                                                             |  |  |  |

|---------------|---------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| Bit 2<br>IOC2 | Bit 1<br>IOC1 | Bit 0<br>IOC0                                                                                     | TGRC_0<br>Function                                                                                                                                                                                                                                                       | TIOC0C Pin Function                                                                     |  |  |  |

| 0             | 0             | 0                                                                                                 | Output                                                                                                                                                                                                                                                                   | Output retained*1                                                                       |  |  |  |

|               |               | 1                                                                                                 | compare                                                                                                                                                                                                                                                                  | Initial output is 0                                                                     |  |  |  |

|               |               |                                                                                                   | register                                                                                                                                                                                                                                                                 | 0 output at compare match                                                               |  |  |  |

|               | 1             | 0                                                                                                 | _                                                                                                                                                                                                                                                                        | Initial output is 0                                                                     |  |  |  |

|               |               |                                                                                                   |                                                                                                                                                                                                                                                                          | 1 output at compare match                                                               |  |  |  |

|               |               | 1                                                                                                 | _                                                                                                                                                                                                                                                                        | Initial output is 0                                                                     |  |  |  |

|               |               |                                                                                                   |                                                                                                                                                                                                                                                                          | Toggle output at compare match                                                          |  |  |  |

| 1             | 0             | 0                                                                                                 | _                                                                                                                                                                                                                                                                        | Output retained                                                                         |  |  |  |

|               |               | 1                                                                                                 | _                                                                                                                                                                                                                                                                        | Initial output is 1                                                                     |  |  |  |

|               |               |                                                                                                   |                                                                                                                                                                                                                                                                          | 0 output at compare match                                                               |  |  |  |

|               | 1             | 0                                                                                                 | _                                                                                                                                                                                                                                                                        | Initial output is 1                                                                     |  |  |  |

|               |               |                                                                                                   |                                                                                                                                                                                                                                                                          | 1 output at compare match                                                               |  |  |  |

|               |               | 1                                                                                                 | _                                                                                                                                                                                                                                                                        | Initial output is 1                                                                     |  |  |  |

|               |               |                                                                                                   |                                                                                                                                                                                                                                                                          | Toggle output at compare match                                                          |  |  |  |

| 0             | 0             | 0                                                                                                 | • •                                                                                                                                                                                                                                                                      | Input capture at rising edge                                                            |  |  |  |

|               |               | 1                                                                                                 | register*2                                                                                                                                                                                                                                                               | Input capture at falling edge                                                           |  |  |  |

|               | 1             | Х                                                                                                 |                                                                                                                                                                                                                                                                          | Input capture at both edges                                                             |  |  |  |

| 1             | Х             | Х                                                                                                 | Capture input source is channel 1/count                                                                                                                                                                                                                                  |                                                                                         |  |  |  |

|               |               |                                                                                                   |                                                                                                                                                                                                                                                                          | Input capture at TCNT_1 count-up/count-down                                             |  |  |  |

|               | 0<br>0<br>0   | IOC2     IOC1       0     0       1     1       1     0       1     0       0     0       1     1 | $\begin{array}{c ccccc} \mathbf{IOC1} & \mathbf{IOC0} \\ \hline 0 & 0 & 0 \\ \hline 1 & 1 \\ \hline 1 & 0 \\ \hline 1 & 1 \\ \hline 1 & 0 \\ \hline 1 \\ \hline 1 & 0 \\ \hline 1 \\ \hline 1 & 0 \\ \hline 1 \\ \hline 1 \\ 0 \\ \hline 1 \\ \hline 1 \\ X \end{array}$ | IOC2IOC1IOC0Function000Output<br>compare<br>register*21011011001011011011011011110011X1 |  |  |  |

#### [Legend]

X: Don't care

Notes: 1. After power-on reset, 0 is output until TIOR is set.

2. When the BFA bit in TMDR\_0 is set to 1 and TGRC\_0 is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

## Table 11.21 TIOR\_1 (Channel 1)

| <b>Bit 2</b><br><b>IOA2</b><br>0 | Bit 1<br>IOA1 | Bit 0                                     | TGRA_1                                                |                                                                             |  |  |  |  |  |

|----------------------------------|---------------|-------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| 0                                |               | IOA0                                      | Function                                              | TIOC1A Pin Function                                                         |  |  |  |  |  |

|                                  | 0             | 0                                         | Output                                                | Output retained*                                                            |  |  |  |  |  |

|                                  |               | 1                                         | compare Initial output is 0                           |                                                                             |  |  |  |  |  |

|                                  |               |                                           | register                                              | 0 output at compare match                                                   |  |  |  |  |  |

|                                  | 1             | 0                                         | —                                                     | Initial output is 0                                                         |  |  |  |  |  |

|                                  |               |                                           |                                                       | 1 output at compare match                                                   |  |  |  |  |  |

|                                  |               | 1                                         | _                                                     | Initial output is 0                                                         |  |  |  |  |  |

|                                  |               |                                           |                                                       | Toggle output at compare match                                              |  |  |  |  |  |

| 1                                | 0             | 0                                         | _                                                     | Output retained                                                             |  |  |  |  |  |

|                                  |               | 1                                         | —                                                     | Initial output is 1                                                         |  |  |  |  |  |

|                                  |               |                                           |                                                       | 0 output at compare match                                                   |  |  |  |  |  |

|                                  | 1             | 0                                         | _                                                     | Initial output is 1                                                         |  |  |  |  |  |

|                                  |               |                                           |                                                       | 1 output at compare match                                                   |  |  |  |  |  |

|                                  |               | 1                                         | _                                                     | Initial output is 1                                                         |  |  |  |  |  |

|                                  |               |                                           |                                                       | Toggle output at compare match                                              |  |  |  |  |  |

| 0                                | 0             | 0                                         |                                                       | Input capture at rising edge                                                |  |  |  |  |  |

|                                  |               | 1                                         | register                                              | Input capture at falling edge                                               |  |  |  |  |  |

|                                  | 1             | Х                                         | _                                                     | Input capture at both edges                                                 |  |  |  |  |  |

| 1                                | Х             | Х                                         | _                                                     | Input capture at generation of channel 0/TGRA_0 compare match/input capture |  |  |  |  |  |

|                                  | 0             | 1 0<br>1 0<br>1<br>0 0<br><u>1</u><br>1 X | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                       |  |  |  |  |  |

# Description

[Legend]

X: Don't care

Note: \* After power-on reset, 0 is output until TIOR is set.

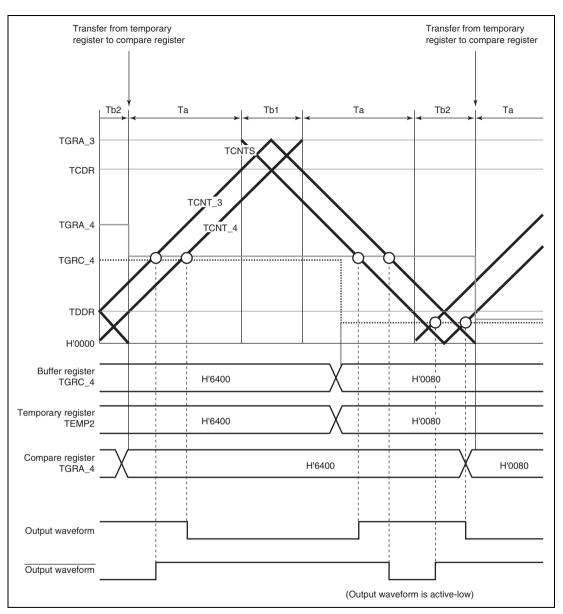

Figure 11.40 Example of Complementary PWM Mode Operation

| Channel | Register Name                    | Abbreviation | R/W                 | Initial<br>Value | Address    | Access<br>Size |

|---------|----------------------------------|--------------|---------------------|------------------|------------|----------------|

| 4       | Serial mode register_4           | SCSMR_4      | R/W                 | H'0000           | H'FFFEA000 | 16             |

|         | Bit rate register_4              | SCBRR_4      | R/W                 | H'FF             | H'FFFEA004 | 8              |

|         | Serial control register_4        | SCSCR_4      | R/W                 | H'0000           | H'FFFEA008 | 16             |

|         | Transmit FIFO data register_4    | SCFTDR_4     | W                   | Undefined        | H'FFFEA00C | 8              |

|         | Serial status register_4         | SCFSR_4      | R/(W)*1             | H'0060           | H'FFFEA010 | 16             |

|         | Receive FIFO data register_4     | SCFRDR_4     | R                   | Undefined        | H'FFFEA014 | 8              |

|         | FIFO control register_4          | SCFCR_4      | R/W                 | H'0000           | H'FFFEA018 | 16             |

|         | FIFO data count register_4       | SCFDR_4      | R                   | H'0000           | H'FFFEA01C | 16             |

|         | Serial port register_4           | SCSPTR_4     | R/W                 | H'0050           | H'FFFEA020 | 16             |

|         | Line status register_4           | SCLSR_4      | R/(W)* <sup>2</sup> | H'0000           | H'FFFEA024 | 16             |

|         | Serial extension mode register_4 | SCEMR_4      | R/W                 | H'0000           | H'FFFEA028 | 16             |

| 5       | Serial mode register_5           | SCSMR_5      | R/W                 | H'0000           | H'FFFEA800 | 16             |

|         | Bit rate register_5              | SCBRR_5      | R/W                 | H'FF             | H'FFFEA804 | 8              |

|         | Serial control register_5        | SCSCR_5      | R/W                 | H'0000           | H'FFFEA808 | 16             |

|         | Transmit FIFO data register_5    | SCFTDR_5     | W                   | Undefined        | H'FFFEA80C | 8              |

|         | Serial status register_5         | SCFSR_5      | R/(W)*1             | H'0060           | H'FFFEA810 | 16             |

|         | Receive FIFO data register_5     | SCFRDR_5     | R                   | Undefined        | H'FFFEA814 | 8              |

|         | FIFO control register_5          | SCFCR_5      | R/W                 | H'0000           | H'FFFEA818 | 16             |

|         | FIFO data count register_5       | SCFDR_5      | R                   | H'0000           | H'FFFEA81C | 16             |

|         | Serial port register_5           | SCSPTR_5     | R/W                 | H'0050           | H'FFFEA820 | 16             |

|         | Line status register_5           | SCLSR_5      | R/(W)*2             | H'0000           | H'FFFEA824 | 16             |

|         | Serial extension mode register_5 | SCEMR_5      | R/W                 | H'0000           | H'FFFEA828 | 16             |

# **18.3** Register Descriptions

Table 18.2 shows the register configuration.

#### Table 18.2 Register Configuration

| Channel | Register Name                                  | Abbreviation | R/W | Initial<br>Value | Address    | Access<br>Size |

|---------|------------------------------------------------|--------------|-----|------------------|------------|----------------|

| 0       | I <sup>2</sup> C bus control register 1        | ICCR1_0      | R/W | H'00             | H'FFFEE000 | 8              |

|         | l <sup>2</sup> C bus control register 2        | ICCR2_0      | R/W | H'7D             | H'FFFEE001 | 8              |

|         | l <sup>2</sup> C bus mode register             | ICMR_0       | R/W | H'38             | H'FFFEE002 | 8              |

|         | l <sup>2</sup> C bus interrupt enable register | ICIER_0      | R/W | H'00             | H'FFFEE003 | 8              |

|         | I <sup>2</sup> C bus status register           | ICSR_0       | R/W | H'00             | H'FFFEE004 | 8              |

|         | Slave address register                         | SAR_0        | R/W | H'00             | H'FFFEE005 | 8              |

|         | I <sup>2</sup> C bus transmit data register    | ICDRT_0      | R/W | H'FF             | H'FFFEE006 | 8              |

|         | I <sup>2</sup> C bus receive data register     | ICDRR_0      | R/W | H'FF             | H'FFFEE007 | 8              |

|         | NF2CYC register                                | NF2CYC_0     | R/W | H'00             | H'FFFEE008 | 8              |

| 1       | I <sup>2</sup> C bus control register 1        | ICCR1_1      | R/W | H'00             | H'FFFEE400 | 8              |

|         | I <sup>2</sup> C bus control register 2        | ICCR2_1      | R/W | H'7D             | H'FFFEE401 | 8              |

|         | I <sup>2</sup> C bus mode register             | ICMR_1       | R/W | H'38             | H'FFFEE402 | 8              |

|         | I <sup>2</sup> C bus interrupt enable register | ICIER_1      | R/W | H'00             | H'FFFEE403 | 8              |

|         | I <sup>2</sup> C bus status register           | ICSR_1       | R/W | H'00             | H'FFFEE404 | 8              |

|         | Slave address register                         | SAR_1        | R/W | H'00             | H'FFFEE405 | 8              |

|         | I <sup>2</sup> C bus transmit data register    | ICDRT_1      | R/W | H'FF             | H'FFFEE406 | 8              |

|         | I <sup>2</sup> C bus receive data register     | ICDRR_1      | R/W | H'FF             | H'FFFEE407 | 8              |

|         | NF2CYC register                                | NF2CYC_1     | R/W | H'00             | H'FFFEE408 | 8              |

| 2       | I <sup>2</sup> C bus control register 1        | ICCR1_2      | R/W | H'00             | H'FFFEE800 | 8              |

|         | I <sup>2</sup> C bus control register 2        | ICCR2_2      | R/W | H'7D             | H'FFFEE801 | 8              |

|         | I <sup>2</sup> C bus mode register             | ICMR_2       | R/W | H'38             | H'FFFEE802 | 8              |

|         | I <sup>2</sup> C bus interrupt enable register | ICIER_2      | R/W | H'00             | H'FFFEE803 | 8              |

|         | I <sup>2</sup> C bus status register           | ICSR_2       | R/W | H'00             | H'FFFEE804 | 8              |

|         | Slave address register                         | SAR_2        | R/W | H'00             | H'FFFEE805 | 8              |

|         | I <sup>2</sup> C bus transmit data register    | ICDRT_2      | R/W | H'FF             | H'FFFEE806 | 8              |

|         | l <sup>2</sup> C bus receive data register     | ICDRR_2      | R/W | H'FF             | H'FFFEE807 | 8              |

|         | NF2CYC register                                | NF2CYC_2     | R/W | H'00             | H'FFFEE808 | 8              |

Page 890 of 2104

#### (1) Message Control Field

**STDID**[10:0]: These bits set the identifier (standard identifier) of data frames and remote frames.

**EXTID**[17:0]: These bits set the identifier (extended identifier) of data frames and remote frames.

**RTR** (Remote Transmission Request bit): Used to distinguish between data frames and remote frames. This bit is overwritten by received CAN Frames depending on Data Frames or Remote Frames.

**Important:** Please note that, when ATX bit is set with the setting MBC = 001(bin), the RTR bit will never be set. When a Remote Frame is received, the CPU can be notified by the corresponding RFPR set or IRR[2] (Remote Frame Receive Interrupt), however, as this module needs to transmit the current message as a Data Frame, the RTR bit remains unchanged.

**Important:** In order to support automatic answer to remote frame when MBC = 001 (bin) is used and ATX = 1 the RTR flag must be programmed to zero to allow data frame to be transmitted.

Note: When a Mailbox is configured to send a remote frame request the DLC used for transmission is the one stored into the Mailbox.

| RTR | Description  |

|-----|--------------|

| 0   | Data frame   |

| 1   | Remote frame |

**IDE** (Identifier Extension bit): Used to distinguish between the standard format and extended format of CAN data frames and remote frames.

| IDE | Description     |

|-----|-----------------|

| 0   | Standard format |

| 1   | Extended format |

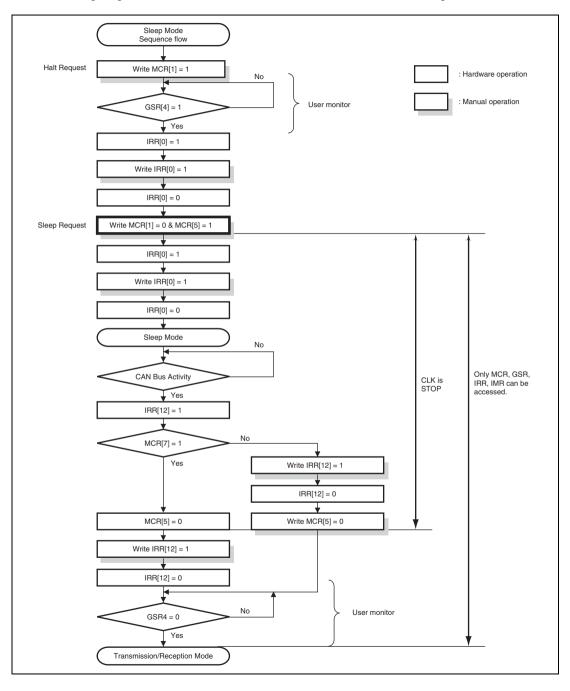

#### The following diagram shows the flow to follow to move this module into sleep mode.

RENESAS

#### (3) Slave Address Field

The slave address field is a field to transmit an address (the slave address) of a unit (the slave unit) to be transmitted. The slave address field is comprised of slave address bits, a parity bit, and an acknowledge bit.

The slave address consists of 12 bits and the MSB is output first. The parity bit is output after the 12-bit slave address is transmitted to avoid receiving the slave address accidentally. The master unit then detects the acknowledgement from the slave unit to confirm that the slave unit exists on the bus. When the acknowledgement is detected, the master unit enters the control field output state. However, the master unit enters the control field output state without detecting the acknowledgement in broadcast communications.

The slave unit returns an acknowledgement when the slave addresses match and the parities of the master and slave addresses are correct. When the parity of either the master or slave address is incorrect, the slave unit decides that the master or slave address was not correctly received and does not return the acknowledgement. In this case, the master unit enters the waiting (monitor) state and communications ends.

In the case of broadcast communications, the slave address is used to identify the type of broadcast communications (group or general) as follows:

- When the slave address is H'FFF: General broadcast communications

- When the slave address is other than H'FFF: Group broadcast communications

- Note: The group number is the upper 4-bit value of the slave address in group broadcast communications.

#### (4) Control Field

The control field is a field for transmitting the type and direction of the following data field. The control field is comprised of control bits, a parity bit, and an acknowledge bit.

The control bits consist of four bits and the MSB is output first.

The parity bit is output following the control bits. When the parity is correct, and the slave unit can implement the function required from the master unit, the slave unit returns an acknowledgement and enters the message length field output state. However, if the slave unit cannot implement the requirements from the master unit even though the parity is correct, or if the parity is not correct, the slave unit does not return an acknowledgement and returns to the waiting (monitor) state.

| Bit   | Bit Name                                                                  | Initial<br>Value | R/W | Description                                                       |  |  |  |  |

|-------|---------------------------------------------------------------------------|------------------|-----|-------------------------------------------------------------------|--|--|--|--|

| 0     | _                                                                         | 1                | R   | Reserved                                                          |  |  |  |  |

|       |                                                                           |                  |     | This bit is always read as 1. The write value should always be 1. |  |  |  |  |

| Note: | e: * The controller is not capable of reading data in sector access mode. |                  |     |                                                                   |  |  |  |  |

# (2) D0FIFOSEL, D1FIFOSEL

| Bit: 15          | 14   | 13    | 12    | 11  | 10     | 9 | 8          | 7 | 6 | 5 | 4 | 3   | 2     | 1       | 0   |

|------------------|------|-------|-------|-----|--------|---|------------|---|---|---|---|-----|-------|---------|-----|

| RCNT             | REW  | DCLRM | DREQE | MBW | /[1:0] | _ | BIG<br>END | _ | _ | — | _ |     | CURPI | PE[3:0] |     |

| Initial value: 0 | 0    | 0     | 0     | 0   | 0      | 0 | 0          | 0 | 0 | 0 | 0 | 0   | 0     | 0       | 0   |

| R/W: R/W         | R/W* | R/W   | R/W   | R/W | R/W    | R | R/W        | R | R | R | R | R/W | R/W   | R/W     | R/W |

| Bit | Bit Name | Initial<br>Value | R/W  | Description                                                                                                                                                                                                                                                                                 |

|-----|----------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | RCNT     | 0                | R/W  | Read Count Mode                                                                                                                                                                                                                                                                             |

|     |          |                  |      | Specifies the read mode for the value in the DTLN bits in DnFIFOCTR.                                                                                                                                                                                                                        |

|     |          |                  |      | <ol> <li>The DTLN bit is cleared when all of the receive<br/>data has been read from the DnFIFO.</li> </ol>                                                                                                                                                                                 |

|     |          |                  |      | (In double buffer mode, the DTLN bit value is<br>cleared when all the data has been read from a<br>single plane.)                                                                                                                                                                           |

|     |          |                  |      | <ol> <li>The DTLN bit is decremented when the receive<br/>data is read from the DnFIFO.</li> </ol>                                                                                                                                                                                          |

|     |          |                  |      | When accessing DnFIFO with the BFRE bit set to 1, set this bit to 0.                                                                                                                                                                                                                        |

| 14  | REW      | 0                | R/W* | Buffer Pointer Rewind                                                                                                                                                                                                                                                                       |

|     |          |                  |      | Specifies whether or not to rewind the buffer pointer.                                                                                                                                                                                                                                      |

|     |          |                  |      | 0: The buffer pointer is not rewound.                                                                                                                                                                                                                                                       |

|     |          |                  |      | 1: The buffer pointer is rewound.                                                                                                                                                                                                                                                           |

|     |          |                  |      | When the selected pipe is in the receiving direction,<br>setting this bit to 1 while the FIFO buffer is being<br>read allows re-reading the FIFO buffer from the first<br>data (in double buffer mode, re-reading the currently-<br>read FIFO buffer plane from the first data is allowed). |

|     |          |                  |      | Do not set REW to 1 simultaneously with modifying the CURPIPE bits. Before setting REW to 1, be sure to check that FRDY is 1.                                                                                                                                                               |

|     |          |                  |      | To re-write to the FIFO buffer again from the first data for the pipe in the transmitting direction, use the BCLR bit.                                                                                                                                                                      |

|        |              | Initial |     |                                                                                                                                                                                                                                                              |

|--------|--------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit Name     | Value   | R/W | Description                                                                                                                                                                                                                                                  |

| 3 to 0 | CURPIPE[3:0] | 0000    | R/W | FIFO Port Access Pipe Specification                                                                                                                                                                                                                          |

|        |              |         |     | Specifies the pipe number for reading or writing data through the D0FIFO/D1FIFO port.                                                                                                                                                                        |

|        |              |         |     | 0000: No pipe specified                                                                                                                                                                                                                                      |

|        |              |         |     | 0001: Pipe 1                                                                                                                                                                                                                                                 |

|        |              |         |     | 0010: Pipe 2                                                                                                                                                                                                                                                 |

|        |              |         |     | 0011: Pipe 3                                                                                                                                                                                                                                                 |

|        |              |         |     | 0100: Pipe 4                                                                                                                                                                                                                                                 |

|        |              |         |     | 0101: Pipe 5                                                                                                                                                                                                                                                 |

|        |              |         |     | 0110: Pipe 6                                                                                                                                                                                                                                                 |

|        |              |         |     | 0111: Pipe 7                                                                                                                                                                                                                                                 |

|        |              |         |     | 1000: Pipe 8                                                                                                                                                                                                                                                 |

|        |              |         |     | 1001: Pipe 9                                                                                                                                                                                                                                                 |

|        |              |         |     | Other than above: Setting prohibited                                                                                                                                                                                                                         |

|        |              |         |     | After writing to these bits, read these bits to check<br>that the written value agrees with the read value<br>before proceeding to the next process.                                                                                                         |

|        |              |         |     | Do not set the same pipe number to the CURPIPE bits in CFIFOSEL, D0FIFOSEL, and D1FIFOSEL.                                                                                                                                                                   |

|        |              |         |     | Even if an attempt is made to modify the setting of<br>these bits during access to the FIFO buffer, the<br>current access setting is retained until the access is<br>completed. Then, the modification becomes effective<br>thus enabling continuous access. |

Note: \* Only 0 can be read and 1 can be written.

#### 27.3.9 FIFO Port Control Registers (CFIFOCTR, D0FIFOCTR, D1FIFOCTR)

CFIFOCTR, D0FIFOCTR and D1FIFOCTR are registers that determine whether or not writing to the buffer memory has been finished, the buffer accessed from the CPU has been cleared, and the FIFO port is accessible. CFIFOCTR, D0FIFOCTR, and D1FIFOCTR are used for the corresponding FIFO ports.

These registers are initialized by a power-on reset.

| Bit           | : 15     | 14                 | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6    | 5      | 4 | 3 | 2 | 1 | 0 |

|---------------|----------|--------------------|------|----|----|----|---|---|---|------|--------|---|---|---|---|---|

|               | BVAL     | BCLR               | FRDY | _  |    |    |   |   |   | DTLN | [11:0] |   |   |   |   |   |

| Initial value | : 0      | 0                  | 0    | 0  | 0  | 0  | 0 | 0 | 0 | 0    | 0      | 0 | 0 | 0 | 0 | 0 |

| R/W           | ': R/W*2 | <sup>2</sup> R/W*1 | R    | R  | R  | R  | R | R | R | R    | R      | R | R | R | R | R |

## (4) Setup of Data to be Transmitted using Isochronous Transfer when the Function Controller Function is Selected

With isochronous data transmission using this module in function controller function, after data has been written to the buffer memory, a data packet can be sent with the next frame in which an SOF packet is detected. This function is called the isochronous transfer transmission data setup function, and it makes it possible to designate the frame from which transmission began.

If a double buffer is used for the buffer memory, transmission will be enabled for only one of the two buffers even after the writing of data to both buffers has been completed, that buffer memory being the one to which the data writing was completed first. For this reason, even if multiple IN tokens are received, the only buffer memory that can be sent is one packet's worth of data.

When an IN token is received, if the buffer memory is in the transmission enabled state, this module transmits the data. If the buffer memory is not in the transmission enabled state, however, a zero-length packet is sent and an underrun error occurs.

Figure 27.20 shows an example of transmission using the isochronous transfer transmission data setup function with this module, when IITV = 0 (every frame) has been set.

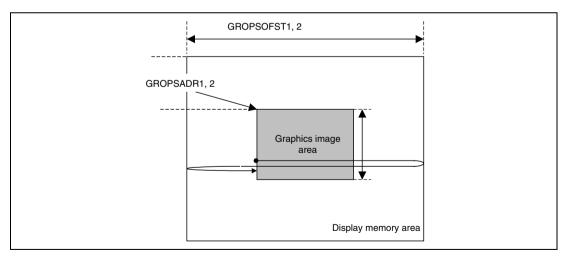

#### 28.7.21 Graphics Image Line Offset Registers (GROPSOFST1 and GROPSOFST2)

| Bit:                   | 31              | 30       | 29       | 28       | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------------------|-----------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|                        | -               | -        | -        |          |          |          |          |          | GROPS    | OFST[28  | :16]     |          |          |          |          |          |

| Initial value:<br>R/W: | 0<br>R          | 0<br>R   | 0<br>R   | 0<br>R/W |

| Bit:                   | 15              | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|                        | GROPSOFST[15:0] |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |

| Initial value:<br>R/W: | 0<br>R/W        | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>B/W |

| Bit      | Bit Name            | Initial Value | R/W | Description                                                                 |

|----------|---------------------|---------------|-----|-----------------------------------------------------------------------------|

| 31 to 29 | _                   | All 0         | R   | Reserved                                                                    |

|          |                     |               |     | These bits are always read as 0. The write value should always be 0.        |

| 28 to 0  | GROPSOFST<br>[28:0] | H'00000000    | R/W | These bits specify the line offset for the graphics image.                  |

|          |                     |               |     | In 16-byte burst transfer: The lower four bits should always be 0000.       |

|          |                     |               |     | In 128-byte burst transfer: The lower seven bits should always be 000_0000. |

Figure 28.21 Graphics Image Memory Area Settings

The start (left side) address of line n is obtained by adding the base address register value (GROPSADR1 or GROPSADR2) and the line offset (GROPSOFST1 or GROPSOFST2)  $\times$  n.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                          |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8      | CL       | 0                | R/W | Internal Work Memory Clear                                                                                                                                                                                           |

| _      |          |                  |     | Writing 1 to this bit clears the input FIFO, output FIFO, input buffer memory, intermediate memory, and accumulator. This bit is always read as 0. Even when SRCEN = 0, writing 1 to this bit clears the processing. |

| 7 to 4 | IFS[3:0] | All 0            | R/W | Input Sampling Rate                                                                                                                                                                                                  |

|        |          |                  |     | Specifies the input sampling rate.                                                                                                                                                                                   |

|        |          |                  |     | 0000: 8.0 kHz                                                                                                                                                                                                        |

|        |          |                  |     | 0001: 11.025 kHz                                                                                                                                                                                                     |

|        |          |                  |     | 0010: 12.0 kHz                                                                                                                                                                                                       |

|        |          |                  |     | 0011: Setting prohibited                                                                                                                                                                                             |

|        |          |                  |     | 0100: 16.0 kHz                                                                                                                                                                                                       |

|        |          |                  |     | 0101: 22.05 kHz                                                                                                                                                                                                      |

|        |          |                  |     | 0110: 24.0 kHz                                                                                                                                                                                                       |

|        |          |                  |     | 0111: Setting prohibited                                                                                                                                                                                             |

|        |          |                  |     | 1000: 32.0 kHz                                                                                                                                                                                                       |

|        |          |                  |     | 1001: 44.1 kHz                                                                                                                                                                                                       |

|        |          |                  |     | 1010: 48.0 kHz                                                                                                                                                                                                       |

|        |          |                  |     | 1011: Setting prohibited                                                                                                                                                                                             |

|        |          |                  |     | 1100: Setting prohibited                                                                                                                                                                                             |

|        |          |                  |     | 1101: Setting prohibited                                                                                                                                                                                             |

|        |          |                  |     | 1110: Setting prohibited                                                                                                                                                                                             |

|        |          |                  |     | 1111: Setting prohibited                                                                                                                                                                                             |

|        |          |                  |     | Note: For channel 1, these bits are reserved and always read as 0. The write value should always be 0.                                                                                                               |

| 3 to 1 | _        | All 0            | R   | Reserved                                                                                                                                                                                                             |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                 |

| Port | Register Name                                                | Abbreviation | R/W | Intial Value | Address    | AccessSize               |

|------|--------------------------------------------------------------|--------------|-----|--------------|------------|--------------------------|

| G    | Port G port register 1                                       | PGPR1        | R   | H'xxxx       | H'FFFE38D8 | 8, 16, 32                |

|      | Port G port register 0                                       | PGPR0        | R   | H'xxxx       | H'FFFE38DA | 8, 16                    |

| Н    | Port H control register 1                                    | PHCR1        | R/W | H'0000       | H'FFFE38EC | 8, 16, 32                |

|      | Port H control register 0                                    | PHCR0        | R/W | H'0000       | H'FFFE38EE | 8, 16                    |

|      | Port H port register 0                                       | PHPR0        | R   | H'xxxx       | H'FFFE38FA | 8, 16                    |

| J    | Port J control register 1                                    | PJCR1        | R/W | H'0000       | H'FFFE390C | 8* <sup>3</sup> , 16, 32 |

|      | Port J control register 0                                    | PJCR0        | R/W | H'0000       | H'FFFE390E | 8, 16                    |

|      | Port J I/O register 0                                        | PJIOR0       | R/W | H'0000       | H'FFFE3912 | 8, 16                    |

|      | Port J data register 0                                       | PJDR0        | R/W | H'0000       | H'FFFE3916 | 8, 16                    |

|      | Port J port register 0                                       | PJPR0        | R   | H'xxxx       | H'FFFE391A | 8, 16                    |

| _    | Serial sound interface<br>noise canceler control<br>register | SNCR         | R/W | H'0000       | H'FFFE393E | 8, 16                    |

Notes: 1. The initial value depends on the boot mode of the LSI.

2. In 16- or 32-bit access, the register can be read but cannot be written to.

3. In 8-bit access, the register can be read but cannot be written to.

When deep standby mode is canceled by interrupts (NMI or realtime clock alarm) or changes on the pins for canceling, the deep standby cancel source flag register (DSFR) can be used to confirm which source has canceled the mode.

Pins retain the state immediately before the transition to deep standby mode. However, in system activation through the external memory, the retention of the states of the external memory control pins is cancelled so that programs can be fetched after cancellation of deep standby mode. Other pins, after cancellation of deep standby mode, continue to retain the pin states until writing 0 to the IOKEEP bit in DSFR after reading 1 from the same bit. In system activation from the on-chip data-retention RAM, after cancellation of deep standby mode, both the external memory control pins and other pins continues to retain the pin states until writing 0 to the IOKEEP bit in DSFR after reading 1 from the same bit. Reconfiguration of peripheral functions is required to return to the previous state of deep standby mode. Peripheral functions include all functions such as the clock pulse generator, interrupt controller, general I/O ports, and peripheral modules. After the reconfiguration, the retention of the pin state can be canceled and the LSI returns to the state prior to the transition to deep standby mode by reading 1 from the IOKEEP bit in DSFR and then writing 0 to it.

#### (4) Notes on Transition to Deep Standby Mode

If multiple canceling sources have been specified and multiple canceling sources are input, multiple cancel source flags will be set.

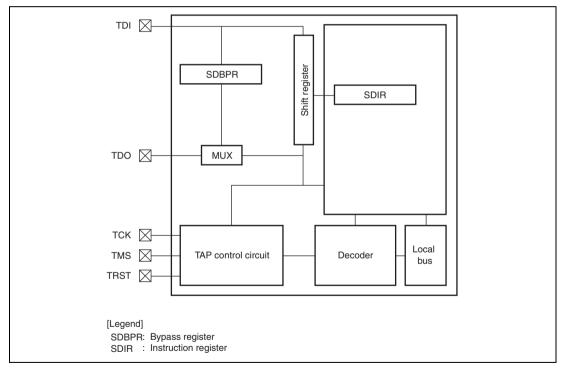

# Section 34 User Debugging Interface

This LSI incorporates a user debugging interface for emulator support.

# 34.1 Features

The user debugging interface has reset and interrupt request functions.

The H-UDI in this LSI is used for emulator connection.

Refer to the emulator manual for the method of connecting the emulator.

Figure 34.1 shows a block diagram.

Figure 34.1 Block Diagram

| Item                                                                      | Page | Revision                                                                                                                                                                                                                                                                                     | (See                                                                                                                                                                                                   | Manual fo                         | r De          | tails)       |                           |       |        |                            |  |

|---------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|--------------|---------------------------|-------|--------|----------------------------|--|

| 1.6 List of Pins<br>Table 1.4 List of<br>Pins                             | 35   | Function 2           Function 2           SH7266         SH7267         Function 2           Pin No.         Symbol         I/O           138         166         WE0/DQML         O           139         167         WE1/DQMU/WE         O           140         168         RAS         O |                                                                                                                                                                                                        |                                   |               |              |                           |       |        |                            |  |

| Figure 1.3 (2)<br>Simplified Circuit<br>Diagram (TTL AND<br>Input Buffer) | 37   | Figure am                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                        | d<br>PAD                          | 1             |              | TTL inp<br>TTL inp        |       |        |                            |  |

| Table 9.19<br>Number of Idle                                              | 343  | Table amended                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                        |                                   |               |              |                           |       |        |                            |  |

| Cycles Inserted<br>between Access<br>Cycles to Different<br>Memory Types  |      | Previous Cycle                                                                                                                                                                                                                                                                               | SRAM                                                                                                                                                                                                   | Burst ROM<br>(Asynchronous)       |               | Byte<br>SRAM | Byte<br>SRAM<br>(BAS = 1) | SDRAM | PCMCIA | Burst ROM<br>(Synchronous) |  |

| Memory Types                                                              |      | SRAM                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                      | 0                                 | 1             | 0            | 0/1*1                     | 0/1*1 | 0      | 0                          |  |

|                                                                           |      | Burst ROM<br>(asynchronou<br>s)                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                      | 0                                 | 1             | 0            | 0/1*1                     | 0/1*1 | 0      | 0                          |  |

|                                                                           |      | MPX-I/O                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                      | 1                                 | 0             | 1            | 1                         | 1     | 1      | 1                          |  |

|                                                                           |      | Byte SRAM<br>(BAS = 0)                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                      | 0                                 | 1             | 0            | 0/1*1                     | 0/1*1 | 0      | 0                          |  |

|                                                                           |      | Byte SRAM<br>(BAS = 1)                                                                                                                                                                                                                                                                       | 0/1*1                                                                                                                                                                                                  | 0/1*1                             | <b>1</b> /2*1 | 0/1*1        | 0                         | 0     | 0/1*1  | 0/1*1                      |  |

| 11.1 Features                                                             | 411  | Description • 25 interru                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                        |                                   |               |              |                           |       |        |                            |  |

| 11.3.23 Timer Cycle<br>Data Register<br>(TCDR)                            | 478  | TCDR is a mode. Set                                                                                                                                                                                                                                                                          | Description amended<br>TCDR is a 16-bit register used only in complementary PWM<br>mode. Set half the PWM carrier sync value (a value of two times<br>TDDR + 3 or greater) as the TCDR register value. |                                   |               |              |                           |       |        |                            |  |

| Figure 11.20<br>Cascaded Operation<br>Setting Procedure                   | 500  |                                                                                                                                                                                                                                                                                              | TPS                                                                                                                                                                                                    | ended<br>SC2 to TPS<br>2 overflov |               |              |                           |       | R to B | '111 to                    |  |