# E·XFL Renesas Electronics America Inc - <u>R5S72671P144FP#VZ Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 144MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IEBus, SCI, SIO, SPI, USB                       |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 104                                                                                |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1.5M x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.15V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 176-LQFP                                                                           |

| Supplier Device Package    | 176-LFQFP (24x24)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s72671p144fp-vz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

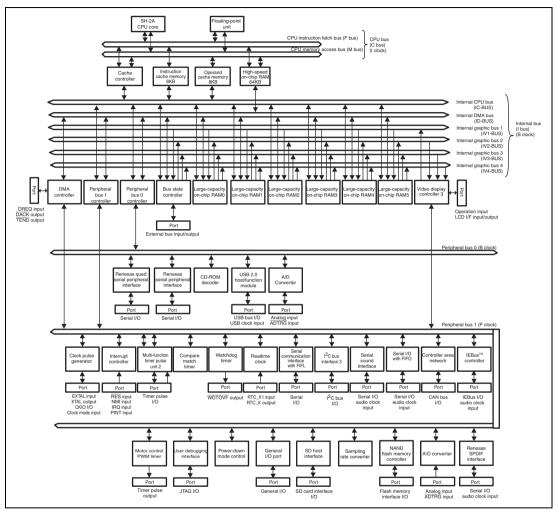

# 1.3 Block Diagram

Figure 1.1 Block Diagram

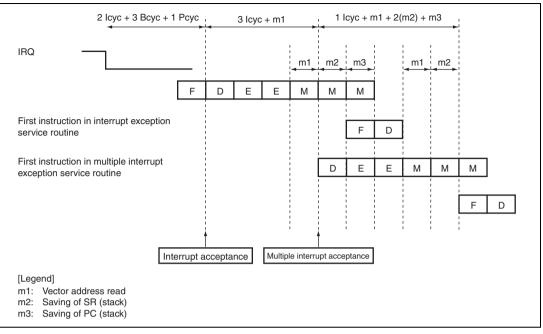

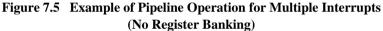

Figure 7.6 Example of Pipeline Operation when IRQ Interrupt is Accepted (Register Banking without Register Bank Overflow)

# 8.4.3 Usage Examples

# (1) Invalidating Specific Entries

Specific cache entries can be invalidated by writing 0 to the entry's V bit in the memory mapping cache access. When the A bit is 1, the tag address specified by the write data is compared to the tag address within the cache selected by the entry address, and data is written to the bits V and U specified by the write data when a match is found. If no match is found, there is no operation. When the V bit of an entry in the address array is set to 0, the entry is written back if the entry's U bit is 1.

An example when a write data is specified in R0 and an address is specified in R1 is shown below.

```

; R0=H'0110 0010; tag address(28-11)=B'0 0001 0001 0000 0000 0, U=0, V=0

; R1=H'F080 0088; operand cache address array access, entry=B'000 1000, A=1

;

MOV.L R0,@R1

```

# (2) Reading the Data of a Specific Entry

The data section of a specific cache entry can be read by the memory mapping cache access. The longword indicated in the data field of the data array in figure 8.4 is read into the register.

An example when an address is specified in R0 and data is read in R1 is shown below.

```

; R0=H'F100 004C; instruction cache data array access, entry=B'000 0100,

; Way=0, longword address=3

;

MOV.L @R0,R1

```

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                       |

|--------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | WM       | 0                | R/W | External Wait Mask Specification                                                                                                                  |

|        |          |                  |     | Specifies whether or not the external wait input is valid. The specification by this bit is valid even when the number of access wait cycle is 0. |

|        |          |                  |     | 0: External wait input is valid                                                                                                                   |

|        |          |                  |     | 1: External wait input is ignored                                                                                                                 |

| 5 to 0 | _        | All 0            | R   | Reserved                                                                                                                                          |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                              |

### • CS4WCR

| Bit:           | 31 | 30 | 29 | 28  | 27   | 26  | 25  | 24   | 23  | 22  | 21  | 20    | 19 | 18 | 17  | 16   |

|----------------|----|----|----|-----|------|-----|-----|------|-----|-----|-----|-------|----|----|-----|------|

|                | -  | -  | -  | -   | -    | -   | -   | -    | -   | -   | BST | [1:0] | -  | -  | BW[ | 1:0] |

| Initial value: | 0  | 0  | 0  | 0   | 0    | 0   | 0   | 0    | 0   | 0   | 0   | 0     | 0  | 0  | 0   | 0    |

| R/W:           | R  | R  | R  | R   | R    | R   | R   | R    | R   | R   | R/W | R/W   | R  | R  | R/W | R/W  |

|                |    |    |    |     |      |     |     |      |     |     |     |       |    |    |     |      |

| Bit:           | 15 | 14 | 13 | 12  | 11   | 10  | 9   | 8    | 7   | 6   | 5   | 4     | 3  | 2  | 1   | 0    |

|                | -  | -  | -  | SW[ | 1:0] |     | W[3 | 3:0] |     | WM  | -   | -     | -  | -  | HW[ | 1:0] |

| Initial value: | 0  | 0  | 0  | 0   | 0    | 1   | 0   | 1    | 0   | 0   | 0   | 0     | 0  | 0  | 0   | 0    |

| R/W:           | R  | R  | R  | R/W | R/W  | R/W | R/W | R/W  | R/W | R/W | R   | R     | R  | R  | R/W | R/W  |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                          |

|----------|----------|------------------|-----|----------------------------------------------------------------------|

| 31 to 22 | —        | All 0            | R   | Reserved                                                             |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0. |

# Table 9.11Relationship between BSZ[1:0], A2/3ROW[1:0], A2/3COL[1:0], and AddressMultiplex Output (3)-2

|                           | Setting                     |                                |           |                                |  |  |

|---------------------------|-----------------------------|--------------------------------|-----------|--------------------------------|--|--|

| BSZ<br>[1:0]              | A2/3<br>ROW<br>[1:0]        | A2/3<br>COL<br>[1:0]           | _         |                                |  |  |

| 10 (16 bits)              | 10 (13 bits)                | 10 (10 bits)                   | -         |                                |  |  |

| Output Pin of<br>This LSI | Row Address<br>Output Cycle | Column Address<br>Output Cycle | SDRAM Pin | Function                       |  |  |

| A17                       | A27                         | A17                            |           | Unused                         |  |  |

| A16                       | A26                         | A16                            | _         |                                |  |  |

| A15                       | A25* <sup>2</sup>           | A25* <sup>2</sup>              | A14 (BA1) | Specifies bank                 |  |  |

| A14                       | A24* <sup>2</sup>           | A24* <sup>2</sup>              | A13 (BA0) |                                |  |  |

| A13                       | A23                         | A13                            | A12       | Address                        |  |  |

| A12                       | A22                         | A12                            | A11       |                                |  |  |

| A11                       | A21                         | L/H* <sup>1</sup>              | A10/AP    | Specifies<br>address/precharge |  |  |

| A10                       | A20                         | A10                            | A9        | Address                        |  |  |

| A9                        | A19                         | A9                             | A8        |                                |  |  |

| A8                        | A18                         | A8                             | A7        |                                |  |  |

| A7                        | A17                         | A7                             | A6        |                                |  |  |

| A6                        | A16                         | A6                             | A5        |                                |  |  |

| A5                        | A15                         | A5                             | A4        |                                |  |  |

| A4                        | A14                         | A4                             | A3        |                                |  |  |

| A3                        | A13                         | A3                             | A2        |                                |  |  |

| A2                        | A12                         | A2                             | A1        |                                |  |  |

| A1                        | A11                         | A1                             | A0        |                                |  |  |

| A0                        | A10                         | A0                             |           | Unused                         |  |  |

| Example of con            | nected memory               |                                |           |                                |  |  |

512-Mbit product (8 Mwords  $\times$  16 bits  $\times$  4 banks, column 10 bits product): 1

Notes: 1. L/H is a bit used in the command specification; it is fixed at low or high according to the access mode.

2. Bank address specification

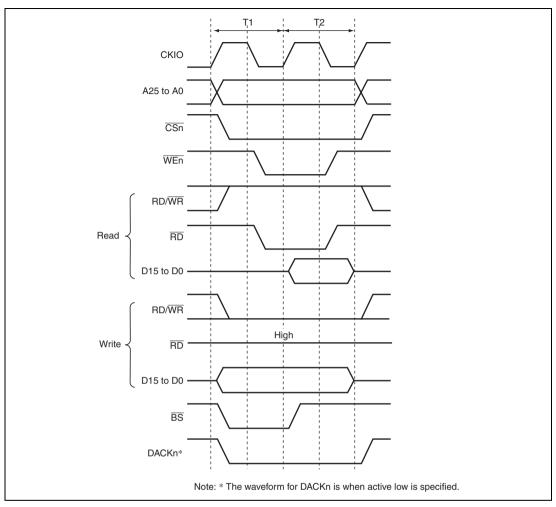

Figure 9.32 Basic Access Timing for SRAM with Byte Selection (BAS = 0)

| Bit    | Bit Name | Initial<br>Value | R/W    | Description                                                                                                                                                                                                                                                 |

|--------|----------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 8   | PR[1:0]  | 00               | R/W    | Priority Mode                                                                                                                                                                                                                                               |

|        |          |                  |        | These bits select the priority level between channels<br>when there are transfer requests for multiple channels<br>simultaneously.                                                                                                                          |

|        |          |                  |        | 00: Fixed mode 1: CH0 > CH1 > CH2 > CH3 > CH4 ><br>CH5 > CH6 > CH7 > CH8 > CH9 > CH10 > CH11<br>> CH12 > CH13 > CH14 > CH15                                                                                                                                 |

|        |          |                  |        | 01: Fixed mode 2: CH0 > CH8 > CH1 > CH9 > CH2 ><br>CH10 > CH3 > CH11 > CH4 > CH12 > CH5 ><br>CH13 > CH6 > CH14 > CH7 > CH15                                                                                                                                 |

|        |          |                  |        | 10: Setting prohibited                                                                                                                                                                                                                                      |

|        |          |                  |        | 11: Setting prohibited                                                                                                                                                                                                                                      |

| 7 to 3 | _        | All 0            | R      | Reserved                                                                                                                                                                                                                                                    |

|        |          |                  |        | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                        |

| 2      | AE       | 0                | R/(W)* | Address Error Flag                                                                                                                                                                                                                                          |

|        |          |                  |        | Indicates whether an address error has occurred by<br>this module. When this bit is set, even if the DE bit in<br>CHCR and the DME bit in DMAOR are set to 1, DMA<br>transfer is not enabled. This bit can only be cleared by<br>writing 0 after reading 1. |

|        |          |                  |        | 0: No address error occurred by this module                                                                                                                                                                                                                 |

|        |          |                  |        | 1: Address error occurred by this module                                                                                                                                                                                                                    |

|        |          |                  |        | [Clearing condition]                                                                                                                                                                                                                                        |

|        |          |                  |        | • Writing 0 after reading AE = 1                                                                                                                                                                                                                            |

### • TSR2\_0

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0       |  |

|----------------|---|---|---|---|---|---|---------|---------|--|

|                | - | - | - | - | - | - | TGFF    | TGFE    |  |

| Initial value: | 1 | 1 | 0 | 0 | 0 | 0 | 0       | 0       |  |

| R/W:           | R | R | R | R | R | R | R/(W)*1 | R/(W)*1 |  |

Note: 1. Writing 0 to this bit after reading it as 1 clears the flag and is the only allowed way.

| Bit    | Bit Name      | Initial<br>Value | R/W                                  | Description                                                                           |

|--------|---------------|------------------|--------------------------------------|---------------------------------------------------------------------------------------|

|        | Dit Name      |                  | -                                    | •                                                                                     |

| 7, 6   | _             | All 1            | R                                    | Reserved<br>These bits are always read as 1. The write value<br>should always be 1.   |

| 5 to 2 | —             | All 0            | R                                    | Reserved                                                                              |

|        |               |                  |                                      | These bits are always read as 0. The write value should always be 0.                  |

| 1      | TGFF          | 0                | <b>R</b> /( <b>W</b> )* <sup>1</sup> | Compare Match Flag F                                                                  |

|        |               |                  |                                      | Status flag that indicates the occurrence of compare match between TCNT_0 and TGRF_0. |

|        |               |                  |                                      | [Clearing condition]                                                                  |

|        |               |                  |                                      | <ul> <li>When 0 is written to TGFF after reading<br/>TGFF = 1*<sup>2</sup></li> </ul> |

|        |               |                  |                                      | [Setting condition]                                                                   |

|        |               |                  |                                      | <ul> <li>When TCNT_0 = TGRF_0 and TGRF_0 is</li> </ul>                                |

|        |               |                  |                                      | functioning as compare register                                                       |

| 0      | TGFE          | 0                | R/(W)*1                              | Compare Match Flag E                                                                  |

|        |               |                  |                                      | Status flag that indicates the occurrence of compare match between TCNT_0 and TGRE_0. |

|        |               |                  |                                      | [Clearing condition]                                                                  |

|        |               |                  |                                      | <ul> <li>When 0 is written to TGFE after reading<br/>TGFE = 1*<sup>2</sup></li> </ul> |

|        |               |                  |                                      | [Setting condition]                                                                   |

|        |               |                  |                                      | <ul> <li>When TCNT_0 = TGRE_0 and TGRE_0 is</li> </ul>                                |

|        |               |                  |                                      | functioning as compare register                                                       |

| Notes: | 1. Writing 01 | to this bit at   | fter reading                         | g it as 1 clears the flag.                                                            |

If the next flag is set before TGFA is cleared to 0 after reading TGFA = 1, TGFA remains 1 even when 0 is written to. In this case, read TGFA = 1 again to clear TGFA to 0.

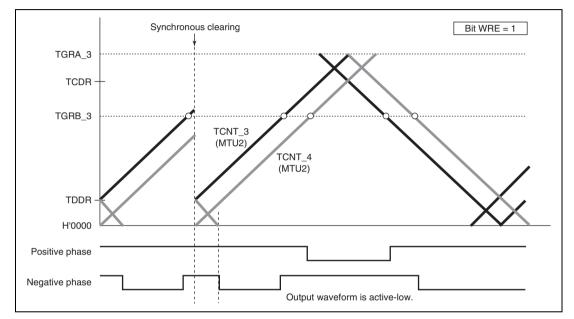

• Examples of Output Waveform Control at Synchronous Counter Clearing in Complementary PWM Mode

Figures 11.58 to 11.61 show examples of output waveform control in which this module operates in complementary PWM mode and synchronous counter clearing is generated while the WRE bit in TWCR is set to 1. In the examples shown in figures 11.58 to 11.61, synchronous counter clearing occurs at timing (3), (6), (8), and (11) shown in figure 11.56, respectively.

Figure 11.58 Example of Synchronous Clearing in Dead Time during Up-Counting (Timing (3) in Figure 11.56; Bit WRE of TWCR is 1)

### 14.3.8 Year Counter (RYRCNT)

RYRCNT is used for setting/counting in the BCD-coded year section. The count operation is performed by a carry for each year of the month counter.

The assignable range is from 0000 through 9999 (practically in BCD), otherwise operation errors occur. Carry out write processing after stopping the count operation through the setting of the START bit in RCR2.

| Blt           | : 15        | 14        | 13        | 12          | 11        | 10        | 9           | 8         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|---------------|-------------|-----------|-----------|-------------|-----------|-----------|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|               |             | 1000      | years     |             |           | 100       | years       |           |           | 10 y      | ears      |           |           | 1 y       | vear      |           |

| Initial value | Undefined U | Undefined | Undefined | Undefined l | Jndefined | Undefined | d Undefined | Undefined |

| R/W           | : R/W       | R/W       | R/W       | R/W         | R/W       | R/W       | R/W         | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       |

|               |             |           |           |             |           |           |             |           |           |           |           |           |           |           |           |           |

|               |             |           | Initi     | ial         |           |           |             |           |           |           |           |           |           |           |           |           |

| Bit           | Bit Na      | ame       | Val       | ue          | R/        | W         | Desc        | riptio    | n         |           |           |           |           |           |           |           |

| 15 to 12      | 1000        | years     | Unc       | lefined     | IR/       | W         | Count       | ting T    | housa     | and's l   | Positi    | on of     | Years     | ;         |           |           |

| 11 to 8       | 100 y       | ears      | Unc       | lefined     | IR/       | W         | Count       | ting H    | undre     | d's P     | ositio    | n of Y    | ears      |           |           |           |

| 7 to 4        | 10 yea      | ars       | Unc       | lefinec     | IR/       | W         | Count       | ting T    | en's F    | ositio    | n of \    | /ears     |           |           |           |           |

| 3 to 0        | 1 yea       | r         | Unc       | lefined     | IR/       | W         | Count       | ting O    | ne's F    | Positio   | on of `   | Years     |           |           |           |           |

| Bit | Bit Name | Initial<br>Value | R/W    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|----------|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | BRK      | 0                | R/(W)* | <ul> <li>Break Detection</li> <li>Indicates that a break signal has been detected in receive data.</li> <li>0: No break signal received</li> <li>[Clearing conditions]</li> <li>BRK is cleared to 0 when the chip is a power-on reset</li> <li>BRK is cleared to 0 when software reads BRK after it has been set to 1, then writes 0 to BRK</li> <li>1: Break signal received*<sup>1</sup></li> </ul>                                                                                                                                                                                                                                                                  |

|     |          |                  |        | <ul> <li>[Setting condition]</li> <li>BRK is set to 1 when data including a framing<br/>error is received, and a framing error occurs with<br/>space 0 in the subsequent receive data</li> <li>Note: 1. When a break is detected, transfer of the<br/>receive data (H'00) to SCFRDR stops<br/>after detection. When the break ends and<br/>the receive signal becomes mark 1, the<br/>transfer of receive data resumes.</li> </ul>                                                                                                                                                                                                                                     |

| 3   | FER      | 0                | R      | <ul> <li>Framing Error Indication</li> <li>Indicates a framing error in the data read from the next receive FIFO data register (SCFRDR) in asynchronous mode.</li> <li>0: No receive framing error occurred in the next data read from SCFRDR</li> <li>[Clearing conditions]</li> <li>FER is cleared to 0 when the chip undergoes a power-on reset</li> <li>FER is cleared to 0 when no framing error is present in the next data read from SCFRDR</li> <li>1: A receive framing error occurred in the next data read from SCFRDR.</li> <li>[Setting condition]</li> <li>FER is set to 1 when a framing error is present in the next data read from SCFRDR.</li> </ul> |

# 17.4 Operation

In this section, the serial transfer period means a period from the beginning of driving valid data to the fetching of the final valid data, and the QSSL negation period means the idle period.

### 17.4.1 Overview of Operations

This module is capable of serial transfers in single-/dual-/quad-SPI modes. Table 17.4 gives the features of single-/dual-/quad-SPI modes.

|                                        | Single-SPI                         | Dual-SPI      | Quad-SPI      |

|----------------------------------------|------------------------------------|---------------|---------------|

| Number of data lines                   | One input line and one output line | Two IO lines  | Four IO lines |

| Data line direction                    | Single-directional                 | Bidirectional | Bidirectional |

| Simultaneous<br>transmission/reception | Supported                          | Not supported | Not supported |

### Table 17.4Features of Each SPI Mode

# 18.2 Input/Output Pins

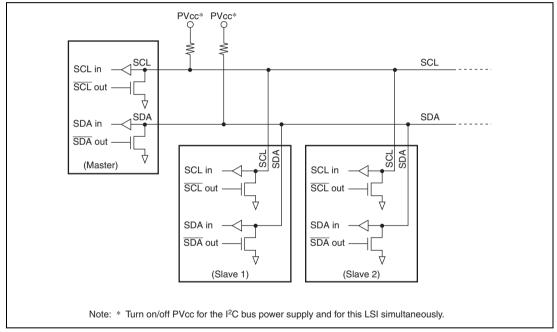

Table 18.1 shows the pin configuration.

## Table 18.1 Pin Configuration

| Pin Name     | Symbol       | I/O | Function                                   |

|--------------|--------------|-----|--------------------------------------------|

| Serial clock | SCL0 to SCL2 | I/O | I <sup>2</sup> C serial clock input/output |

| Serial data  | SDA0 to SDA2 | I/O | l <sup>2</sup> C serial data input/output  |

Figure 18.2 shows an example of I/O pin connections to external circuits.

Figure 18.2 External Circuit Connections of I/O Pins

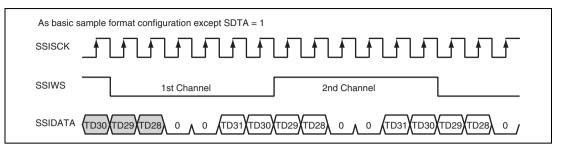

• Transmitting and Receiving in the Order of Padding Bits and Serial Data; with Delay

Figure 19.14 Transmitting and Receiving in the Order of Padding Bits and Serial Data; with Delay

• Transmitting and Receiving in the Order of Padding Bits and Serial Data; without Delay

| As basic sample format configuration except SDTA = 1 and DEL = 1            |             |             |  |  |  |

|-----------------------------------------------------------------------------|-------------|-------------|--|--|--|

| SSISCK                                                                      |             |             |  |  |  |

| SSIWS                                                                       | 1st Channel | 2nd Channel |  |  |  |

| SSIDATA (TD29/TD28) 0 0 (TD31/TD30/TD29/TD28) 0 0 (TD31/TD30/TD29/TD28) 0 0 |             |             |  |  |  |

Figure 19.15 Transmitting and Receiving in the Order of Padding Bits and Serial Data; without Delay

• Transmitting and Receiving in the Order of Serial Data and Padding Bits; without Delay

| ·     | configuration except DEL = 1 |             |           |

|-------|------------------------------|-------------|-----------|

| SSIWS | 1st Channel                  | 2nd Channel | 1         |

|       |                              |             | TD31 TD30 |

Figure 19.16 Transmitting and Receiving in the Order of Serial Data and Padding Bits; without Delay

### 21.3.2 Mailbox Structure

Mailboxes play a role as message buffers to transmit/receive CAN frames. Each Mailbox is comprised of 3 identical storage fields that are 1): Message Control, 2): Local Acceptance Filter Mask, 3): Message Data. In addition some Mailboxes contain the following extra Fields: 4): Time Stamp, 5): Time Trigger configuration and 6): Time Trigger Control. The following table shows the address map for the control, LAFM, data, timestamp, Transmission Trigger Time and Time Trigger Control addresses for each mailbox.

|                        | Address   |           |           |           |               |                 |            |

|------------------------|-----------|-----------|-----------|-----------|---------------|-----------------|------------|

|                        | Control0  | LAFM      | Data      | Control1  | Time<br>Stamp | Trigger<br>Time | TT control |

| Mailbox                | 4 bytes   | 4 bytes   | 8 bytes   | 2 bytes   | 2 bytes       | 2 bytes         | 2 bytes    |

| 0<br>(Receive<br>Only) | 100 – 103 | 104– 107  | 108 – 10F | 110 – 111 | 112 – 113     | No              | No         |

| 1                      | 120 – 123 | 124 – 127 | 128 – 12F | 130 – 131 | 132 – 133     | No              | No         |

| 2                      | 140 – 143 | 144 – 147 | 148 – 14F | 150 – 151 | 152 – 153     | No              | No         |

| 3                      | 160 – 163 | 164 – 167 | 168 – 16F | 170 – 171 | 172 – 173     | No              | No         |

| 4                      | 180 – 183 | 184 – 187 | 188 – 18F | 190 – 191 | 192 – 193     | No              | No         |

| 5                      | 1A0 – 1A3 | 1A4 – 1A7 | 1A8 – 1AF | 1B0 – 1B1 | 1B2 – 1B3     | No              | No         |

| 6                      | 1C0 – 1C3 | 1C4 – 1C7 | 1C8 – 1CF | 1D0 – 1D1 | 1D2 – 1D3     | No              | No         |

| 7                      | 1E0 – 1E3 | 1E4 – 1E7 | 1E8 – 1EF | 1F0 – 1F1 | 1F2 – 1F3     | No              | No         |

| 8                      | 200 – 203 | 204 – 207 | 208 – 20F | 210 – 211 | 212 – 213     | No              | No         |

| 9                      | 220 – 223 | 224 – 227 | 228 – 22F | 230 – 231 | 232 – 233     | No              | No         |

| 10                     | 240 - 243 | 244 – 247 | 248 – 24F | 250 – 251 | 252 – 253     | No              | No         |

| 11                     | 260 - 263 | 264 – 267 | 268 – 26F | 270 – 271 | 272 – 273     | No              | No         |

| 12                     | 280 - 283 | 284 – 287 | 288 – 28F | 290 – 291 | 292 – 293     | No              | No         |

| 13                     | 2A0 – 2A3 | 2A4 – 2A7 | 2A8 – 2AF | 2B0 – 2B1 | 2B2 – 2B3     | No              | No         |

| 14                     | 2C0 - 2C3 | 2C4 – 2C7 | 2C8 – 2CF | 2D0 – 2D1 | 2D2 – 2D3     | No              | No         |

| 15                     | 2E0 – 2E3 | 2E4 – 2E7 | 2E8 – 2EF | 2F0 – 2F1 | 2F2 – 2F3     | No              | No         |

| 16                     | 300 - 303 | 304 - 307 | 308 – 30F | 310 – 311 | No            | No              | No         |

| 17                     | 320 - 323 | 324 – 327 | 328 – 32F | 330 - 331 | No            | No              | No         |

| 18                     | 340 - 343 | 344 – 347 | 348 – 34F | 350 – 351 | No            | No              | No         |

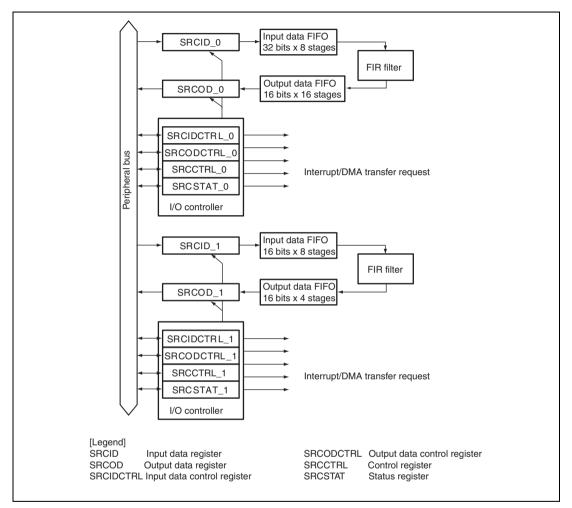

Figure 29.1 shows a block diagram.

Figure 29.1 Block Diagram

# 33.3 Operation

### 33.3.1 Sleep Mode

### (1) Transition to Sleep Mode

Executing the SLEEP instruction when the STBY bit in STBCR1 is 0 causes a transition from the program execution state to sleep mode. Although the CPU halts immediately after executing the SLEEP instruction, the contents of its internal registers remain unchanged. The on-chip peripheral modules continue to run in sleep mode. The clock output from the CKIO pin is continued.

### (2) Canceling Sleep Mode

Sleep mode is canceled by an interrupt (NMI, IRQ, and on-chip peripheral module), a DMA address error, or a reset (manual reset or power-on reset).

• Canceling by an interrupt

When an NMI, IRQ, or on-chip peripheral module interrupt occurs, sleep mode is canceled and interrupt exception handling is executed. When the priority level of the generated interrupt is equal to or lower than the interrupt mask level that is set in the status register (SR) of the CPU, or the interrupt by the on-chip peripheral module is disabled on the module side, the interrupt request is not accepted and sleep mode is not canceled.

- Canceling by a DMA address error When a DMA address error occurs, sleep mode is canceled and DMA address error exception handling is executed.

- Canceling by a reset

Sleep mode is canceled by a power-on reset or a manual reset.

| Module Name                | Register Name                                                      | Abbreviation      | Number<br>of Bits | Address    | Access<br>Size |

|----------------------------|--------------------------------------------------------------------|-------------------|-------------------|------------|----------------|

| Video display controller 3 | Timing control register for vertical sync signal for graphic image | GRA_<br>VSYNC_TIM | 32                | H'FFFF3910 | 8, 16, 32      |

|                            | AC modulation signal toggle line count                             | AC_LINE_NUM       | 32                | H'FFFF3914 | 8, 16, 32      |

|                            | DE area size register                                              | DE_SIZE           | 32                | H'FFFF3920 | 8, 16, 32      |

|                            | DE area start position register                                    | DE_START          | 32                | H'FFFF3924 | 8, 16, 32      |

| Sampling rate              | Input data register_0                                              | SRCID_0           | 32                | H'FFFE7000 | 16, 32         |

| converter                  | Output data register_0                                             | SRCOD_0           | 32                | H'FFFE7004 | 16, 32         |

|                            | Input data control register_0                                      | SRCIDCTRL_0       | 16                | H'FFFE7008 | 16             |

|                            | Output data control register_0                                     | SRCODCTRL_0       | 16                | H'FFFE700A | 16             |

|                            | Control register_0                                                 | SRCCTRL_0         | 16                | H'FFFE700C | 16             |

|                            | Status register_0                                                  | SRCSTAT_0         | 16                | H'FFFE700E | 16             |

|                            | Input data register_1                                              | SRCID_1           | 16                | H'FFFE7800 | 16, 32         |

|                            | Output data register_1                                             | SRCOD_1           | 32                | H'FFFE7804 | 16, 32         |

|                            | Input data control register_1                                      | SRCIDCTRL_1       | 16                | H'FFFE7808 | 16             |

|                            | Output data control register_1                                     | SRCODCTRL_1       | 16                | H'FFFE780A | 16             |

|                            | Control register_1                                                 | SRCCTRL_1         | 16                | H'FFFE780C | 16             |

|                            | Status register_1                                                  | SRCSTAT_1         | 16                | H'FFFE780E | 16             |

| General                    | Port A I/O register 1                                              | PAIOR1            | 16                | H'FFFE3810 | 8, 16, 32*     |

| purpose I/O<br>ports       | Port A I/O register 0                                              | PAIOR0            | 16                | H'FFFE3812 | 8, 16*         |

| pons                       | Port A data register 1                                             | PADR1             | 16                | H'FFFE3814 | 8, 16, 32*     |

|                            | Port A data register 0                                             | PADR0             | 16                | H'FFFE3816 | 8, 16*         |

|                            | Port A port register 0                                             | PAPR0             | 16                | H'FFFE381A | 8, 16          |

|                            | Port B control register 5                                          | PBCR5             | 16                | H'FFFE3824 | 8, 16, 32      |

|                            | Port B control register 4                                          | PBCR4             | 16                | H'FFFE3826 | 8, 16          |

|                            | Port B control register 3                                          | PBCR3             | 16                | H'FFFE3828 | 8, 16, 32      |

|                            | Port B control register 2                                          | PBCR2             | 16                | H'FFFE382A | 8, 16          |

|                            | Port B control register 1                                          | PBCR1             | 16                | H'FFFE382C | 8, 16, 32      |

|                            | Port B control register 0                                          | PBCR0             | 16                | H'FFFE382E | 8, 16          |

|                            | Port B I/O register 1                                              | PBIOR1            | 16                | H'FFFE3830 | 8, 16, 32      |

|                            | Port B I/O register 0                                              | PBIOR0            | 16                | H'FFFE3832 | 8, 16          |

|                            | Port B data register 1                                             | PBDR1             | 16                | H'FFFE3834 | 8, 16, 32      |

# Section 37 Electrical Characteristics

# 37.1 Absolute Maximum Ratings

## Table 37.1 Absolute Maximum Ratings

| Item                                                    |                                       | Symbol              | Value                                    | Unit |

|---------------------------------------------------------|---------------------------------------|---------------------|------------------------------------------|------|

| Power supply                                            | voltage (I/O)                         | PV <sub>cc</sub>    | –0.3 to 4.6                              | V    |

| Power supply                                            | voltage (Internal)                    | V <sub>cc</sub>     | –0.3 to 1.7                              | V    |

| PLL power sup                                           | pply voltage                          | PLLV <sub>cc</sub>  | –0.3 to 1.7                              | V    |

| Analog power                                            | supply voltage                        | AV <sub>cc</sub>    | –0.3 to 4.6                              | V    |

| Analog referen                                          | ce voltage                            | AV <sub>ref</sub>   | –0.3 to $\mathrm{AV}_{\mathrm{cc}}$ +0.3 | V    |

| USB transceive                                          | er analog power supply voltage (I/O)  | $USBAPV_{cc}$       | –0.3 to 4.6                              | V    |

| USB transceive                                          | er digital power supply voltage (I/O) | $USBDPV_{cc}$       | –0.3 to 4.6                              | V    |

| USB transceiver analog power supply voltage (internal)  |                                       | USBAV <sub>cc</sub> | –0.3 to 1.7                              | V    |

| USB transceiver digital power supply voltage (internal) |                                       | $USBDV_{cc}$        | –0.3 to 1.7                              | V    |

| Power supply for USB 480 MHz (internal)                 |                                       | USBUV <sub>cc</sub> | –0.3 to 1.7                              | V    |

| Input voltage                                           | Analog input pin                      | V <sub>AN</sub>     | –0.3 to AV $_{\rm cc}$ +0.3              | V    |

|                                                         | VBUS                                  | V <sub>in</sub>     | –0.3 to 5.5                              | V    |

|                                                         | Other input pins                      | V <sub>in</sub>     | –0.3 to $PV_{cc}$ +0.3                   | V    |

| Operating<br>temperature                                | Regular specifications                | T <sub>opr</sub>    | -20 to +85                               | °C   |

|                                                         | Wide-range specifications             | -                   | -40 to +85                               | _    |

| Storage temperature                                     |                                       | T <sub>stg</sub>    | -55 to +125                              | °C   |

Caution: Permanent damage to the LSI may result if absolute maximum ratings are exceeded.

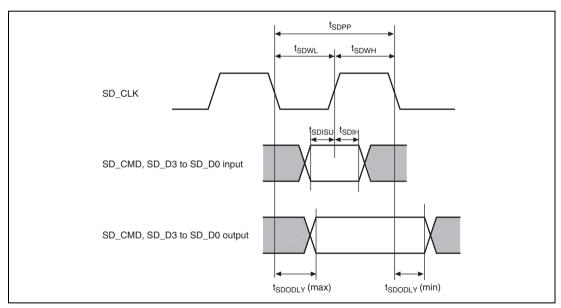

## 37.4.17 SD Host Interface Timing

### Table 37.23 SD Host Interface Timing

| Item                                                          | Symbol         | Min.                         | Max. | Unit | Figure |

|---------------------------------------------------------------|----------------|------------------------------|------|------|--------|

| SD_CLK clock cycle                                            | tsdpp          | $2 \times t_{\text{pcyc}}$   | _    | ns   | Figure |

| SD_CLK clock high width                                       | <b>t</b> sdwh  | $0.4 	imes t_{\text{SDPP}}$  | _    | ns   | 37.76  |

| SD_CLK clock low width                                        | tsdwl          | $0.4 \times t_{\text{SDPP}}$ | _    | ns   | -      |

| SD_CMD, SD_D3 to SD_D0 output data delay (data transfer mode) | tsdodly        | —                            | 14   | ns   | -      |

| SD_CMD, SD_D3 to SD_D0 input data setup                       | <b>t</b> sdisu | 5                            | _    | ns   | -      |

| SD_CMD, SD_D3 to SD_D0 input data hold                        | <b>t</b> sdih  | 5                            |      | ns   | -      |

Note:  $t_{pcvc}$  indicates peripheral clock (P $\phi$ ) cycle.

Figure 37.76 SD Card Interface