Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                              |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                      |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                             |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 160KB (160K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 12K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 10x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | PG-VQFN-48-54                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe161fl20f80vaafxuma1 |

## **Table of Contents**

# **Table of Contents**

|                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Configuration and Definition     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Functional Description               | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Central Processing Unit (CPU)        | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Memory Protection Unit (MPU)         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Memory Checker Module (MCHK)         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| On-Chip Debug Support (OCDS)         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Capture/Compare Unit (CC2)           | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Capture/Compare Units CCU6x          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Real Time Clock                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Instruction Set Summary              | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Electrical Parameters                | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| General Parameters                   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operating Conditions                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC Parameters                        | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DC Parameters for Upper Voltage Area | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DC Parameters for Lower Voltage Area | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Analog/Digital Converter Parameters  | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AC Parameters                        | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                      | Summary of Features  Device Types Definition of Feature Variants  General Device Information Pin Configuration and Definition Identification Registers  Functional Description  Memory Subsystem and Organization Central Processing Unit (CPU) Memory Protection Unit (MPU) Memory Checker Module (MCHK) Interrupt System On-Chip Debug Support (OCDS) Capture/Compare Unit (CC2) Capture/Compare Units CCU6x General Purpose Timer (GPT12E) Unit Real Time Clock A/D Converters Universal Serial Interface Channel Modules (USIC) MultiCAN Module System Timer Window Watchdog Timer Clock Generation Parallel Ports Power Management Instruction Set Summary  Electrical Parameters General Parameters General Parameters Operating Conditions Voltage Range definitions Parameter Interpretation DC Parameters DC Parameters for Upper Voltage Area DC Parameters for Lower Voltage Area Power Consumption Analog/Digital Converter Parameters System Parameters Flash Memory Parameters AC Parameters AC Parameters AC Parameters |

## **Summary of Features**

- On-Chip Peripheral Modules

- Synchronizable 12-bit A/D Converter with up to 10 channels, conversion time below 1 μs, optional data preprocessing (data reduction, range check), broken wire detection

- 16-channel general purpose capture/compare unit (CC2)

- Two capture/compare units for flexible PWM signal generation (CCU6x)

- Multi-functional general purpose timer unit with 5 timers

- Up to 4 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI/QSPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 32 message objects (Full CAN/Basic CAN) on 2 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Single power supply from 3.0 V to 5.5 V

- · Power reduction and wake-up modes with flexible power management

- Programmable window watchdog timer and oscillator watchdog

- Up to 33 general purpose I/O lines

- · On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via Device Access Port (DAP), Single-Pin DAP (SPD) or JTAG interface

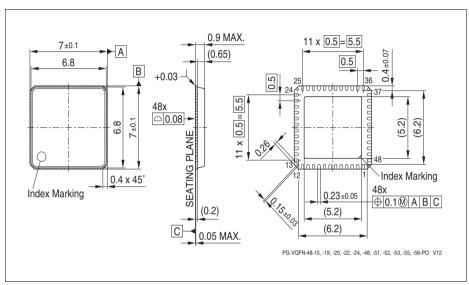

- 48-pin Green VQFN package, 0.5 mm (10.7 mil) pitch

### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the function set of the corresponding product type

- the temperature range<sup>1)</sup>:

- SAF-...: -40°C to 85°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XE161xL please contact your sales representative or local distributor.

Data Sheet 4 V1.2, 2012-07

<sup>1)</sup> Not all derivatives are offered in all temperature ranges.

**Summary of Features**

#### 1.2 Definition of Feature Variants

The XE161xL types are offered with several Flash memory sizes. **Table 3** and **Table 4** describe the location of the available Flash memory.

Table 3 Continuous Flash Memory Ranges

| Total Flash Size | 1st Range <sup>1)</sup> | 2nd Range            | 3rd Range            |

|------------------|-------------------------|----------------------|----------------------|

| 160 Kbytes       | C0'0000 <sub>H</sub>    | C1'0000 <sub>H</sub> | C4'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>    | C2'0FFF <sub>H</sub> | C4'7FFF <sub>H</sub> |

| 96 Kbytes        | C0'0000 <sub>H</sub>    | C1'0000 <sub>H</sub> | C4'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>    | C1'0FFF <sub>H</sub> | C4'7FFF <sub>H</sub> |

<sup>1)</sup> The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

Table 4 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 0 <sup>1)</sup> | Flash 1 |  |

|------------------|-----------------------|---------|--|

| 160              | 128                   | 32      |  |

| 96               | 64                    | 32      |  |

<sup>1)</sup> The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XE161xL types are offered with different interface options. **Table 5** lists the available channels for each option.

Table 5 Interface Channel Association

| Total Number      | Available Channels / Message Objects                 |

|-------------------|------------------------------------------------------|

| 10 ADC0 channels  | CH0, CH2, CH3, CH4, CH8, CH9, CH16, CH17, CH19, CH20 |

| 2 CAN nodes       | CAN0, CAN1<br>32 message objects                     |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1                               |

### **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 13  | P5.4              | I      | In/B | Bit 4 of Port 5, General Purpose Input         |

|     | ADC0_CH4          | I      | In/B | Analog Input Channel 4 for ADC0                |

|     | CCU63_T12<br>HRB  | I      | In/B | External Run Control Input for T12 of CCU63    |

|     | T3EUDA            | I      | In/B | GPT12E Timer T3 External Up/Down Control Input |

|     | TMS_A             | I      | In/B | JTAG Test Mode Selection Input                 |

| 14  | P5.8              | I      | In/B | Bit 8 of Port 5, General Purpose Input         |

|     | ADC0_CH8          | I      | In/B | Analog Input Channel 8 for ADC0                |

|     | CCU6x_T12H<br>RC  | I      | In/B | External Run Control Input for T12 of CCU60/3  |

|     | CCU6x_T13H<br>RC  | I      | In/B | External Run Control Input for T13 of CCU60/3  |

| 15  | P5.9              | I      | In/B | Bit 9 of Port 5, General Purpose Input         |

|     | ADC0_CH9          | I      | In/B | Analog Input Channel 9 for ADC0                |

|     | CC2_T7IN          | I      | In/B | CAPCOM2 Timer T7 Count Input                   |

| 16  | P2.0              | O0 / I | DA/B | Bit 0 of Port 2, General Purpose Input/Output  |

|     | CCU63_CC6         | O2     | DA/B | CCU63 Channel 0 Output                         |

|     | RxDC0C            | I      | DA/B | CAN Node 0 Receive Data Input                  |

|     | CCU63_CC6<br>0INB | I      | DA/B | CCU63 Channel 0 Input                          |

|     | ADC0_CH19         | I      | DA/B | Analog Input Channel 19 for ADC0               |

|     | T5INB             | I      | DA/B | GPT12E Timer T5 Count/Gate Input               |

### **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                        |

|-----|-------------------|--------|------|-------------------------------------------------|

| 40  | P10.9             | O0 / I | St/B | Bit 9 of Port 10, General Purpose Input/Output  |

|     | U0C0_SELO<br>4    | O1     | St/B | USIC0 Channel 0 Select/Control 4 Output         |

|     | U0C1_MCLK<br>OUT  | O2     | St/B | USIC0 Channel 1 Master Clock Output             |

|     | TxDC1             | О3     | St/B | CAN Node 1 Transmit Data Output                 |

|     | CCU60_CCP<br>OS2A | I      | St/B | CCU60 Position Input 2                          |

|     | TCK_B             | I      | St/B | DAP0/JTAG Clock Input                           |

|     | T3INB             | I      | St/B | GPT12E Timer T3 Count/Gate Input                |

| 44  | P10.10            | O0 / I | St/B | Bit 10 of Port 10, General Purpose Input/Output |

|     | U0C0_SELO<br>0    | O1     | St/B | USIC0 Channel 0 Select/Control 0 Output         |

|     | CCU60_COU<br>T63  | O2     | St/B | CCU60 Channel 3 Output                          |

|     | U1C0_DOUT         | О3     | St/B | USIC1 Channel 0 Shift Data Output               |

|     | U0C0_DX2C         | I      | St/B | USIC0 Channel 0 Shift Control Input             |

|     | TDI_B             | I      | St/B | JTAG Test Data Input                            |

|     | U0C1_DX1A         | I      | St/B | USIC0 Channel 1 Shift Clock Input               |

| 45  | P10.12            | O0 / I | St/B | Bit 12 of Port 10, General Purpose Input/Output |

|     | U1C0_DOUT         | 01     | St/B | USIC1 Channel 0 Shift Data Output               |

|     | U0C0_DOUT         | O2     | St/B | USIC0 Channel 0 Shift Data Output               |

|     | CCU63_COU<br>T62  | О3     | St/B | CCU63 Channel 2 Output                          |

|     | TDO_A             | ОН     | St/B | DAP1/JTAG Test Data Output                      |

|     | SPD_0             | I/OH   | St/B | SPD Input/Output                                |

|     | C0                | I      | St/B | Configuration Pin 0                             |

|     | U0C0_DX0D         | I      | St/B | USIC0 Channel 0 Shift Data Input                |

|     | U1C0_DX0C         | I      | St/B | USIC1 Channel 0 Shift Data Input                |

|     | U1C0_DX1E         | I      | St/B | USIC1 Channel 0 Shift Clock Input               |

| 46  | XTAL2             | 0      | Sp/M | Crystal Oscillator Amplifier Output             |

**Functional Description**

## 3.7 Capture/Compare Unit (CC2)

The CAPCOM unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, external count inputs allow event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

Table 9 Compare Modes

| <b>Compare Modes</b> | Function                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------|

| Mode 0               | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1               | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

## **Functional Description**

When clocked by  $f_{\rm SYS}$  = 80 MHz, time intervals between 12.5 ns and 13.4 s can be monitored.

When clocked by  $f_{\rm WU}$  = 500 kHz, time intervals between 2.0  $\mu$ s and 2147.5 s can be monitored.

The default Watchdog Timer interval after power-up is 0.13 s (@  $f_{WII}$  = 500 kHz).

#### 3.16 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{\rm SYS}$  for the XE161xL from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on the EXTCLK pin.

**Functional Description**

## 3.19 Instruction Set Summary

Table 11 lists the instructions of the XE161xL.

The addressing modes that can be used with a specific instruction, the function of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

Table 11 Instruction Set Summary

| Mnemonic      | Description                                                                                       |     |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4 |  |  |  |  |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4 |  |  |  |  |

| SUB(B)        | Subtract word (byte) operands                                                                     | 2/4 |  |  |  |  |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4 |  |  |  |  |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- × 16-bit)                                       |     |  |  |  |  |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2   |  |  |  |  |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2   |  |  |  |  |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2   |  |  |  |  |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2   |  |  |  |  |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4 |  |  |  |  |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4 |  |  |  |  |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4 |  |  |  |  |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2   |  |  |  |  |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4   |  |  |  |  |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4   |  |  |  |  |

| ВСМР          | Compare direct bit to direct bit                                                                  | 4   |  |  |  |  |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4   |  |  |  |  |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4 |  |  |  |  |

| CMPD1/2       | PD1/2 Compare word data to GPR and decrement GPR by 1/2                                           |     |  |  |  |  |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 |     |  |  |  |  |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2   |  |  |  |  |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2   |  |  |  |  |

**Electrical Parameters**

## 4.1.1 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XE161xL. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

Table 13 Operating Conditions

| Parameter                                                        | Symbol                        | Values |                           |                           | Unit | Note /                                              |

|------------------------------------------------------------------|-------------------------------|--------|---------------------------|---------------------------|------|-----------------------------------------------------|

|                                                                  |                               | Min.   | Тур.                      | Max.                      |      | Test Condition                                      |

| Voltage Regulator Buffer Capacitance for DMP_M                   | $C_{ m EVRM} \ { m SR}$       | 1.0    | -                         | 4.7                       | μF   | 1)2)                                                |

| External Load<br>Capacitance                                     | C <sub>L</sub> SR             | -      | 20 <sup>3)</sup>          | -                         | pF   | pin out<br>driver= default                          |

| System frequency                                                 | $f_{\rm SYS}{\rm SR}$         | -      | _                         | 80                        | MHz  | 5)                                                  |

| Overload current for analog inputs <sup>6)</sup>                 | I <sub>OVA</sub> SR           | -2     | -                         | 5                         | mA   | not subject to production test                      |

| Overload current for digital inputs <sup>6)</sup>                | $I_{\mathrm{OVD}}\mathrm{SR}$ | -5     | -                         | 5                         | mA   | not subject to production test                      |

| Overload current coupling factor for analog inputs <sup>7)</sup> | K <sub>OVA</sub><br>CC        | -      | 2.5 x<br>10 <sup>-4</sup> | 1.5 x<br>10 <sup>-3</sup> | -    | $I_{\rm OV}$ < 0 mA; not subject to production test |

|                                                                  |                               | _      | 1.0 x<br>10 <sup>-6</sup> | 1.0 x<br>10 <sup>-4</sup> | -    | $I_{\rm OV}$ > 0 mA; not subject to production test |

Table 22 ADC Parameters for Lower Voltage Range (cont'd)

| Parameter                                    | Symbol              | Values |      |      | Unit | Note /         |

|----------------------------------------------|---------------------|--------|------|------|------|----------------|

|                                              |                     | Min.   | Тур. | Max. |      | Test Condition |

| Wakeup time from analog powerdown, fast mode | t <sub>WAF</sub> CC | _      | -    | 8.5  | μS   |                |

| Wakeup time from analog powerdown, slow mode | t <sub>WAS</sub> CC | _      | _    | 15.0 | μS   |                |

- 1) These parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) typical values can be used for calculation.

- 2) The sum of DNL/INL/GAIN/OFF errors does not exceed the related TUE total unadjusted error.

- 3) If a reduced analog reference voltage between 1V and  $V_{\rm DDPB}$  / 2 is used, then there are additional decrease in the ADC speed and accuracy.

- 4) If the analog reference voltage range is below V<sub>DDPB</sub> but still in the defined range of V<sub>DDPB</sub> / 2 and V<sub>DDPB</sub> is used, then the ADC converter errors increase. If the reference voltage is reduced by the factor k (k<1), TUE, DNL, INL, Gain and Offset errors increase also by the factor 1/k.</p>

- 5) If the analog reference voltage is  $> V_{DDPR}$ , then the ADC converter errors increase.

- 6) TUE is based on 12-bit conversion.

- 7) TUE is tested at V<sub>AREF</sub> = V<sub>DDPB</sub> = 3.3 V, V<sub>AGND</sub> = 0 V. It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see I<sub>OV</sub> specification) does not exceed 10 mA, and if V<sub>AREF</sub> and V<sub>AGND</sub> remain stable during the measurement time.

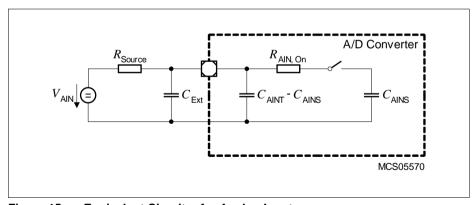

Figure 15 Equivalent Circuitry for Analog Inputs

Sample time and conversion time of the XE161xL's A/D converters are programmable. The timing above can be calculated using **Table 23**.

The limit values for  $f_{\rm ADCI}$  must not be exceeded when selecting the prescaler value.

#### **Electrical Parameters**

Table 23 A/D Converter Computation Table

| GLOBCTR.5-0<br>(DIVA) | A/D Converter Analog Clock $f_{\mathrm{ADCI}}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup> |

|-----------------------|------------------------------------------------|---------------------|---------------------------|

| 000000 <sub>B</sub>   | $f_{	exttt{SYS}}$                              | 00 <sub>H</sub>     | $t_{ADCI} \times 2$       |

| 000001 <sub>B</sub>   | $f_{\rm SYS}$ / 2                              | 01 <sub>H</sub>     | $t_{ADCI} \times 3$       |

| 000010 <sub>B</sub>   | $f_{SYS}$ / 3                                  | 02 <sub>H</sub>     | $t_{ADCI} \times 4$       |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                       | :                   | $t_{ADCI} \times (STC+2)$ |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                          | FE <sub>H</sub>     | $t_{ADCI} \times 256$     |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                          | FF <sub>H</sub>     | $t_{ADCI} \times 257$     |

<sup>1)</sup> The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

## **Converter Timing Example A:**

Assumptions:  $f_{SYS} = 80 \text{ MHz}$  (i.e.  $t_{SYS} = 12.5 \text{ ns}$ ), DIVA =  $03_H$ , STC =  $00_H$

Analog clock  $f_{ADCI} = f_{SYS} / 4 = 20 \text{ MHz}$ , i.e.  $t_{ADCI} = 50 \text{ ns}$

Sample time  $t_S = t_{ADCI} \times 2 = 100 \text{ ns}$

Conversion 12-bit:

$t_{\text{C12}} = 16 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 16 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.825 \text{ }\mu\text{s}$

Conversion 10-bit:

$t_{\text{C10}} = 12 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 12 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.625 \text{ }\mu\text{s}$

Conversion 8-bit:

$t_{\text{C8}} = 10 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 10 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.525 \text{ }\mu\text{s}$

# Converter Timing Example B:

Assumptions:  $f_{SYS} = 66 \text{ MHz}$  (i.e.  $t_{SYS} = 15.2 \text{ ns}$ ), DIVA =  $03_H$ , STC =  $00_H$

Analog clock  $f_{ADCI} = f_{SYS} / 4 = 16.5 \text{ MHz}$ , i.e.  $t_{ADCI} = 60.6 \text{ ns}$

Sample time  $t_S = t_{ADCI} \times 2 = 121.2 \text{ ns}$

Conversion 12-bit:

$t_{\text{C12}} = 16 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 16 \times 60.6 \text{ ns} + 2 \times 15.2 \text{ ns} = 1.0 \text{ }\mu\text{s}$

Conversion 10-bit:

$t_{\text{C10}} = 12 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 12 \times 60.6 \text{ ns} + 2 \times 15.2 \text{ ns} = 0.758 \text{ }\mu\text{s}$

**Electrical Parameters**

## 4.5 System Parameters

The following parameters specify several aspects which are important when integrating the XE161xL into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

Table 24 Various System Parameters

| Parameter                                                             | Symbol              | Values                               |          |                                      | Unit | Note /                                     |

|-----------------------------------------------------------------------|---------------------|--------------------------------------|----------|--------------------------------------|------|--------------------------------------------|

|                                                                       |                     | Min.                                 | Тур.     | Max.                                 |      | Test Condition                             |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | $\Delta f_{INT}$ CC | -1                                   | -        | 1                                    | %    | $\Delta T_{\rm J} = \le 10^{\circ}{\rm C}$ |

| Internal clock source frequency                                       | $f_{INT}CC$         | 4.8                                  | 5.0      | 5.2                                  | MHz  |                                            |

| Wakeup clock source                                                   | $f_{WU}CC$          | 400                                  | _        | 700                                  | kHz  | FREQSEL= 00                                |

| frequency <sup>2)</sup>                                               |                     | 210                                  | _        | 390                                  | kHz  | FREQSEL= 01                                |

|                                                                       |                     | 140                                  | _        | 260                                  | kHz  | FREQSEL= 10                                |

|                                                                       |                     | 110                                  | _        | 200                                  | kHz  | FREQSEL= 11                                |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC | 1.4                                  | 1.9      | 2.4                                  | ms   | $f_{\rm WU}$ = 500 kHz                     |

| Startup time from stopover mode with code execution from PSRAM        | t <sub>SSO</sub> CC | 11 / f <sub>WU</sub> <sup>3)</sup>   | _        | 12 /<br>$f_{\rm WU}^{3)}$            | μS   |                                            |

| Core voltage (PVC) supervision level                                  | $V_{PVC}CC$         | V <sub>LV</sub> - 0.03               | $V_{LV}$ | V <sub>LV</sub> + 0.07 <sup>4)</sup> | V    | 5)                                         |

| Supply watchdog (SWD) supervision level                               | $V_{SWD}$ CC        | V <sub>LV</sub> - 0.10 <sup>6)</sup> | $V_{LV}$ | V <sub>LV</sub> + 0.15               | V    | voltage_range=<br>lower 5)                 |

|                                                                       |                     | V <sub>LV</sub> - 0.15               | $V_{LV}$ | V <sub>LV</sub> + 0.15               | V    | voltage_range=<br>upper 5)                 |

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

<sup>2)</sup> This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization.

<sup>3)</sup>  $f_{WU}$  in MHz.

## 4.7.2 Definition of Internal Timing

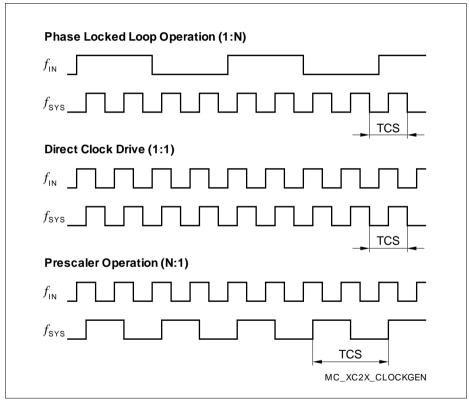

The internal operation of the XE161xL is controlled by the internal system clock  $f_{\rm SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XE161xL.

Figure 18 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 18** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

Table 30 Standard Pad Parameters for Upper Voltage Range (cont'd)

| Parameter                       | Symbol             | Values |      |                                 | Unit | Note /                                                                                                        |    |                                                                                                               |

|---------------------------------|--------------------|--------|------|---------------------------------|------|---------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------|

|                                 |                    | Min.   | Тур. | Max.                            |      | Test Condition                                                                                                |    |                                                                                                               |

| Rise and Fall times (10% - 90%) | t <sub>RF</sub> CC | _      | _    | 38 +<br>0.6 x<br>C <sub>L</sub> | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Medium                      |    |                                                                                                               |

|                                 |                    | _      | _    | 1 +<br>0.45 x<br>C <sub>L</sub> | ns   | $C_L \ge 20 \text{ pF};$<br>$C_L \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Soft |    |                                                                                                               |

|                                 |                    |        |      | _                               | _    | 16 +<br>0.45 x<br>$C_{L}$                                                                                     | ns | $C_L \ge 20 \text{ pF};$<br>$C_L \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Slow |

|                                 |                    |        |      |                                 |      |                                                                                                               |    | _                                                                                                             |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 25 mA.

Table 31 Standard Pad Parameters for Lower Voltage Range

| Parameter                                                    | Symbol               |      | Values |      | Unit | Note /<br>Test Condition |

|--------------------------------------------------------------|----------------------|------|--------|------|------|--------------------------|

|                                                              |                      | Min. | Тур.   | Max. |      |                          |

| Maximum output driver current (absolute value) <sup>1)</sup> | I <sub>Omax</sub> CC | _    | -      | 1.8  | mA   | Driver_Strength = Medium |

|                                                              |                      | _    | -      | 3.0  | mA   | Driver_Strength = Strong |

|                                                              |                      | _    | -      | 0.3  | mA   | Driver_Strength = Weak   |

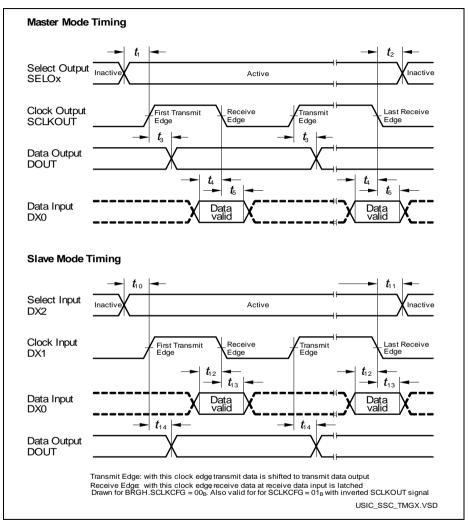

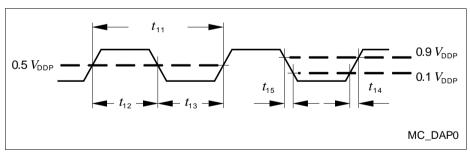

Figure 21 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.

**Table 37** is valid under the following conditions:  $C_1 = 20 \text{ pF}$ ; voltage\_range= lower

Table 37 DAP Interface Timing for Lower Voltage Range

| Parameter                                      | Symbol             | Values            |      |      | Unit | Note /              |