Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 80MHz                                                                     |

| Connectivity               | EBI/EMI, FPGA, IrDA, SPI, UART/USART, USB                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                        |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | ROM                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 160K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                              |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 225-LFBGA                                                                 |

| Supplier Device Package    | 225-LFBGA (13x13)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91cap7e-na-zj |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 9.3 Reset Controller

- Based on two Power-on-Reset cells

- one on VDDBU and one on VDDCORE

- Status of the last reset

- Either general reset (VDDBU rising), wake-up reset (VDDCORE rising), software reset, user reset or watchdog reset

- Controls the internal resets and the NRST pin output

- Allows shaping a reset signal for the external devices

# 9.4 Shut Down Controller

- Shut-Down and Wake-Up logic

- Software programmable assertion of the SHDN open-drain pin

- De-assertion Programmable on a WKUP pin level change or on alarm

# 9.5 Clock Generator

- Embeds the Low Power, fast start-up 32kHz RC Oscillator

- Provides the default Slow Clock SLCK to the system

- The SLCK is required for AT91CAP7E to start-up because it is the default clock for the ARM7TDMI at power-up.

- Embeds the Low Power 32768Hz Slow Clock Oscillator

- Requires an external 32768Hz crystal

- Optional Slow Clock SLCK source when a real-time timebase is required

- Embeds the Main Oscillator

- Requires an external crystal. For systems using the USB features, 12MHz is recommended.

- Oscillator bypass feature

- Supports 8 to 16MHz crystals. Recommend 12 MHz crystal if using the USB features of AT91CAP7E.

- Generates input reference clock for the two PLLs.

- Embeds PLLA primarily for generating processor and master clocks. For full-speed operation on the ARM7TDMI processor, this PLL should be programmed to generate a 160 MHz clock that must then be divided in half to generate the 80 MHz PCK and related clocks.

- PLLA outputs an 80 to 240MHz clock

- Requires an external RC filter network

- PLLA has a 1MHz minimum input frequency

- Integrates an input divider to increase output accuracy

- Embeds PLLB primarily for generating a 96 MHz clock that is divided down to generate the USB related clocks.

- PLLB uses an internal low-pass filter (LPF) and can output a 50 to 100 MHz clock

- PLLB and its internal low-pass filter (LPF) are tuned especially for generating a 96 MHz clock with a 12 MHz input frequency

- 12 MHz minimum input frequency

# • URSTS: User Reset Status

0 = No high-to-low edge on NRST happened since the last read of RSTC\_SR.

1 = At least one high-to-low transition of NRST has been detected since the last read of RSTC\_SR.

# • RSTTYP: Reset Type

Reports the cause of the last processor reset. Reading this RSTC\_SR does not reset this field.

|   | RSTTYP |   | Reset Type     | Comments                                 |

|---|--------|---|----------------|------------------------------------------|

| 0 | 0      | 0 | General Reset  | Both VDDCORE and VDDBU rising            |

| 0 | 0      | 1 | Wake Up Reset  | VDDCORE rising                           |

| 0 | 1      | 0 | Watchdog Reset | Watchdog fault occurred                  |

| 0 | 1      | 1 | Software Reset | Processor reset required by the software |

| 1 | 0      | 0 | User Reset     | NRST pin detected low                    |

# • NRSTL: NRST Pin Level

Registers the NRST Pin Level at Master Clock (MCK).

# • SRCMP: Software Reset Command in Progress

0 = No software command is being performed by the reset controller. The reset controller is ready for a software command.

1 = A software reset command is being performed by the reset controller. The reset controller is busy.

# 14.4.3 Reset Controller Mode Register

| Register Name: | RSTC_MR |

|----------------|---------|

|----------------|---------|

| Access Type: | Read/W | /rite |         |       |    |    |        |

|--------------|--------|-------|---------|-------|----|----|--------|

| 31           | 30     | 29    | 28      | 27    | 26 | 25 | 24     |

|              |        |       | KI      | EY    |    |    |        |

| 23           | 22     | 21    | 20      | 19    | 18 | 17 | 16     |

| -            | _      | -     | -       | _     | _  | _  |        |

| 15           | 14     | 13    | 12      | 11    | 10 | 9  | 8      |

| -            | —      | -     | -       | ERSTL |    |    |        |

| 7            | 6      | 5     | 4       | 3     | 2  | 1  | 0      |

| -            | —      |       | URSTIEN | —     | —  | —  | URSTEN |

# • URSTEN: User Reset Enable

0 = The detection of a low level on the pin NRST does not generate a User Reset.

1 = The detection of a low level on the pin NRST triggers a User Reset.

# • URSTIEN: User Reset Interrupt Enable

0 = USRTS bit in RSTC\_SR at 1 has no effect on rstc\_irq.

1 = USRTS bit in RSTC\_SR at 1 asserts rstc\_irq if URSTEN = 0.

• ERSTL: External Reset Length

# AT91CAP7E

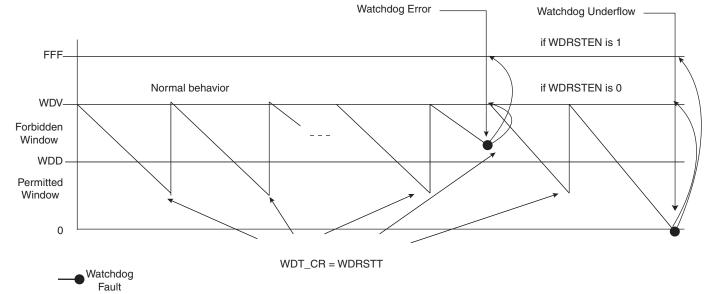

# Figure 17-2. Watchdog Behavior

# 17.4 User Interface

# 17.4.1 Register Mapping

# Table 17-1.Watchdog Timer Registers

| Offset | Register         | Name   |                 | Reset Value |

|--------|------------------|--------|-----------------|-------------|

| 0x00   | Control Register | WDT_CR | Write-only      | -           |

| 0x04   | Mode Register    | WDT_MR | Read/Write Once | 0x3FFF_2FFF |

| 0x08   | Status Register  | WDT_SR | Read-only       | 0x0000_0000 |

# 17.4.2 Watchdog Timer Control Register

| Register Name | gister Name: WDT_CR |    |      |         |    |    |        |

|---------------|---------------------|----|------|---------|----|----|--------|

| Access Type:  |                     |    | Writ | te-only |    |    |        |

| 31            | 30                  | 29 | 28   | 27      | 26 | 25 | 24     |

|               |                     |    | К    | EY      |    |    |        |

| 23            | 22                  | 21 | 20   | 19      | 18 | 17 | 16     |

| -             | -                   | -  | -    | -       | -  | -  | -      |

| 15            | 14                  | 13 | 12   | 11      | 10 | 9  | 8      |

| -             | _                   | -  | -    | -       | -  | -  | -      |

| 7             | 6                   | 5  | 4    | 3       | 2  | 1  | 0      |

| -             | -                   | -  | -    | -       | -  | -  | WDRSTT |

# • WDRSTT: Watchdog Restart

0: No effect.

1: Restarts the Watchdog.

# • KEY: Password

Should be written at value 0xA5. Writing any other value in this field aborts the write operation.

# 17.4.3 Watchdog Timer Mode Register

| Register Nam | e:      | WDT_I           | MR       |     |    |    |    |  |

|--------------|---------|-----------------|----------|-----|----|----|----|--|

| Access Type: |         | Read/Write Once |          |     |    |    |    |  |

| 31           | 30      | 29              | 28       | 27  | 26 | 25 | 24 |  |

|              |         | WDIDLEHLT       | WDDBGHLT |     | W  | DD |    |  |

| 23           | 22      | 21              | 20       | 19  | 18 | 17 | 16 |  |

|              |         |                 | WE       | D   |    |    |    |  |

| 15           | 14      | 13              | 12       | 11  | 10 | 9  | 8  |  |

| WDDIS        | WDRPROC | WDRSTEN         | WDFIEN   | WDV |    |    |    |  |

| 7            | 6       | 5               | 4        | 3   | 2  | 1  | 0  |  |

|              |         |                 | W        | V   |    |    |    |  |

# • WDV: Watchdog Counter Value

Defines the value loaded in the 12-bit Watchdog Counter.

# • WDFIEN: Watchdog Fault Interrupt Enable

- 0: A Watchdog fault (underflow or error) has no effect on interrupt.

- 1: A Watchdog fault (underflow or error) asserts interrupt.

# • WDRSTEN: Watchdog Reset Enable

- 0: A Watchdog fault (underflow or error) has no effect on the resets.

- 1: A Watchdog fault (underflow or error) triggers a Watchdog reset.

# • WDRPROC: Watchdog Reset Processor

- 0: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates all resets.

- 1: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates the processor reset.

# • WDD: Watchdog Delta Value

Defines the permitted range for reloading the Watchdog Timer.

If the Watchdog Timer value is less than or equal to WDD, writing WDT\_CR with WDRSTT = 1 restarts the timer.

If the Watchdog Timer value is greater than WDD, writing WDT\_CR with WDRSTT = 1 causes a Watchdog error.

### • WDDBGHLT: Watchdog Debug Halt

- 0: The Watchdog runs when the processor is in debug state.

- 1: The Watchdog stops when the processor is in debug state.

# • WDIDLEHLT: Watchdog Idle Halt

- 0: The Watchdog runs when the system is in idle mode.

- 1: The Watchdog stops when the system is in idle state.

- WDDIS: Watchdog Disable

# 94 AT91CAP7E

The connection of some signals through the MUX logic is not direct and depends on the Memory Controller in use at the moment.

Table 20-2 on page 118 details the connections between the two Memory Controllers and the EBI pins.

| EBI Pins        | SDRAMC I/O Lines | SMC I/O Lines |

|-----------------|------------------|---------------|

| NWR1/NBS1/CFIOR | NBS1             | NWR1/NUB      |

| A0/NBS0         | Not Supported    | SMC_A0/NLB    |

| A1/NBS2/NWR2    | Not Supported    | SMC_A1        |

| A[11:2]         | SDRAMC_A[9:0]    | SMC_A[11:2]   |

| SDA10           | SDRAMC_A10       | Not Supported |

| A12             | Not Supported    | SMC_A12       |

| A[14:13]        | SDRAMC_A[12:11]  | SMC_A[14:13]  |

| A[25:15]        | Not Supported    | SMC_A[25:15]  |

| D[31:16]        | D[31:16]         | D[31:16]      |

| D[15:0]         | D[15:0]          | D[15:0]       |

Table 20-2. EBI Pins and Memory Controllers I/O Lines Connections

# 20.4 Application Example

# 20.4.1 Hardware Interface

Table 20-3 and Table 20-4 detail the connections to be applied between the EBI pins and the external devices for each Memory Controller.

| Table 20-3. | EBI Pins and External Static Devices Connections |

|-------------|--------------------------------------------------|

|-------------|--------------------------------------------------|

|              |                        | Pins of the Interfaced Device  |                         |                                |                                 |                         |  |  |  |  |  |  |

|--------------|------------------------|--------------------------------|-------------------------|--------------------------------|---------------------------------|-------------------------|--|--|--|--|--|--|

| Pins         | 8-bit Static<br>Device | 2 x 8-bit<br>Static<br>Devices | 16-bit Static<br>Device | 4 x 8-bit<br>Static<br>Devices | 2 x 16-bit<br>Static<br>Devices | 32-bit Static<br>Device |  |  |  |  |  |  |

| Controller   |                        | SMC                            |                         |                                |                                 |                         |  |  |  |  |  |  |

| D0 - D7      | D0 - D7                | D0 - D7                        | D0 - D7                 | D0 - D7                        | D0 - D7                         | D0 - D7                 |  |  |  |  |  |  |

| D8 - D15     | -                      | D8 - D15                       | D8 - D15                | D8 - D15                       | D8 - 15                         | D8 - 15                 |  |  |  |  |  |  |

| D16 - D23    | -                      | _                              | -                       | D16 - D23                      | D16 - D23                       | D16 - D23               |  |  |  |  |  |  |

| D24 - D31    | -                      | _                              | _                       | D24 - D31                      | D24 - D31                       | D24 - D31               |  |  |  |  |  |  |

| A0/NBS0      | AO                     | -                              | NLB                     | _                              | NLB <sup>(3)</sup>              | BE0 <sup>(5)</sup>      |  |  |  |  |  |  |

| A1/NWR2/NBS2 | A1                     | A0                             | AO                      | WE <sup>(2)</sup>              | NLB <sup>(4)</sup>              | BE2 <sup>(5)</sup>      |  |  |  |  |  |  |

| A2 - A25     | A[2:25]                | A[1:24]                        | A[1:24]                 | A[0:23]                        | A[0:23]                         | A[0:23]                 |  |  |  |  |  |  |

| NCS0         | CS                     | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |  |  |  |

| NCS1/SDCS    | CS                     | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |  |  |  |

| NCS2         | CS                     | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |  |  |  |

| NCS3/NANDCS  | CS                     | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |  |  |  |

| NCS4/CFCS0   | CS                     | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |  |  |  |

# 118 AT91CAP7E

AT91CAP7E

# 21.14.1 SMC Setup Register Register Name:

SMC\_SETUP[0..7]

Read/Write

Access Type:

29 28 27 24 31 30 26 25 NCS RD SETUP \_ 23 22 21 20 19 18 16 17 NRD\_SETUP \_ \_ 15 14 13 12 11 10 9 8 NCS\_WR\_SETUP \_ \_ 5 4 7 6 3 2 1 0 NWE\_SETUP \_

# • NWE\_SETUP: NWE Setup Length

The NWE signal setup length is defined as:

NWE setup length = (128\* NWE\_SETUP[5] + NWE\_SETUP[4:0]) clock cycles

# • NCS\_WR\_SETUP: NCS Setup Length in WRITE Access

In write access, the NCS signal setup length is defined as:

NCS setup length = (128\* NCS\_WR\_SETUP[5] + NCS\_WR\_SETUP[4:0]) clock cycles

# • NRD\_SETUP: NRD Setup Length

The NRD signal setup length is defined in clock cycles as:

NRD setup length = (128\* NRD\_SETUP[5] + NRD\_SETUP[4:0]) clock cycles

# • NCS\_RD\_SETUP: NCS Setup Length in READ Access

In read access, the NCS signal setup length is defined as:

NCS setup length = (128\* NCS\_RD\_SETUP[5] + NCS\_RD\_SETUP[4:0]) clock cycles

# 23. Peripheral DMA Controller (PDC)

# 23.1 Description

The Peripheral DMA Controller (PDC) transfers data between on-chip serial peripherals and the on- and/or off-chip memories. The link between the PDC and a serial peripheral is operated by the AHB to ABP bridge.

The PDC contains 22 channels. The full-duplex peripherals feature 19 mono directional channels used in pairs (transmit only or receive only) except the ADC Controller uses only one RX channel. The half-duplex peripherals feature 3 bi-directional channels.

The user interface of each PDC channel is integrated into the user interface of the peripheral it serves. The user interface of mono directional channels (receive only or transmit only), contains two 32-bit memory pointers and two 16-bit counters, one set (pointer, counter) for current transfer and one set (pointer, counter) for next transfer. The bi-directional channel user interface contains four 32-bit memory pointers and four 16-bit counters. Each set (pointer, counter) is used by current transmit, next transmit, current receive and next receive.

Using the PDC removes processor overhead by reducing its intervention during the transfer. This significantly reduces the number of clock cycles required for a data transfer, which improves microcontroller performance.

To launch a transfer, the peripheral triggers its associated PDC channels by using transmit and receive signals. When the programmed data is transferred, an end of transfer interrupt is generated by the peripheral itself.

# 24.2.10.3PMC System Clock Status RegisterRegister Name:PMC\_SCSR

| · <b>J</b>   |     |           |    |      |      |      |      |

|--------------|-----|-----------|----|------|------|------|------|

| Access Type: |     | Read-only |    |      |      |      |      |

| 31           | 30  | 29        | 28 | 27   | 26   | 25   | 24   |

| _            | _   | _         | _  | _    | _    | -    | -    |

| 23           | 22  | 21        | 20 | 19   | 18   | 17   | 16   |

| _            | _   | _         | _  | _    | _    | -    | _    |

| 15           | 14  | 13        | 12 | 11   | 10   | 9    | 8    |

| _            | _   | —         | _  | PCK3 | PCK2 | PCK1 | PCK0 |

| 7            | 6   | 5         | 4  | 3    | 2    | 1    | 0    |

| UDP          | UHP | _         | _  | _    | _    | -    | PCK  |

# PCK: Processor Clock Status

0 = The Processor clock is disabled.

1 = The Processor clock is enabled.

# • UHP: USB Host Port Clock Status

0 = The 12 and 48 MHz clock (UHPCK) of the USB Host Port is disabled.

1 = The 12 and 48 MHz clock (UHPCK) of the USB Host Port is enabled.

# • UDP: USB Device Port Clock Status

0 = The 48 MHz clock (UDPCK) of the USB Device Port is disabled.

1 = The 48 MHz clock (UDPCK) of the USB Device Port is enabled.

# • PCKx: Programmable Clock x Output Status

0 = The corresponding Programmable Clock output is disabled.

1 = The corresponding Programmable Clock output is enabled.

# 24.2.10.10 PMC Clock Generator PLL B Register Register Name: CKGR PLLBR

| negister num | 0.   |            |           |     |    |      |    |  |

|--------------|------|------------|-----------|-----|----|------|----|--|

| Access Type: |      | Read/Write |           |     |    |      |    |  |

| 31           | 30   | 29         | 28        | 27  | 26 | 25   | 24 |  |

| _            | -    | USE        | BDIV      | -   |    | MULB |    |  |

| 23           | 22   | 21         | 20        | 19  | 18 | 17   | 16 |  |

|              |      |            | MU        | JLB |    |      |    |  |

| 15           | 14   | 13         | 12        | 11  | 10 | 9    | 8  |  |

| OL           | JTB  |            | PLLBCOUNT |     |    |      |    |  |

| 7            | 6    | 5          | 4         | 3   | 2  | 1    | 0  |  |

|              | DIVB |            |           |     |    |      |    |  |

Possible limitations on PLL B input frequencies and multiplier factors should be checked before using the PMC.

# • DIVB: Divider B

| DIVB    | Divider Selected                                      |

|---------|-------------------------------------------------------|

| 0       | Divider output is 0                                   |

| 1       | Divider is bypassed                                   |

| 2 - 255 | Divider output is the selected clock divided by DIVB. |

# PLLBCOUNT: PLL B Counter

Specifies the number of slow clock cycles before the LOCKB bit is set in PMC\_SR after CKGR\_PLLBR is written.

### • OUTB: PLLB Clock Frequency Range

To optimize clock performance, this field must be programmed as specified in "PLL Characteristics" in the Electrical Characteristics section of the product datasheet.

### • MULB: PLL B Multiplier

0 = The PLL B is deactivated.

1 up to 2047 = The PLL B Clock frequency is the PLL B input frequency multiplied by MULB + 1.

### • USBDIV: Divider for USB Clock

| USBDIV                                    |   | Divider for USB Clock(s)                           |  |

|-------------------------------------------|---|----------------------------------------------------|--|

| 0 0 Divider output is PLL B clock output. |   | Divider output is PLL B clock output.              |  |

| 0                                         | 1 | Divider output is PLL B clock output divided by 2. |  |

| 1                                         | 0 | Divider output is PLL B clock output divided by 4. |  |

| 1                                         | 1 | Reserved.                                          |  |

| 24.2.10.15 P<br>Register Name | -  | <i>iister</i><br>PMC_SR |    |         |         |         |         |

|-------------------------------|----|-------------------------|----|---------|---------|---------|---------|

| Access Type:                  |    | Read-only               |    |         |         |         |         |

| 31                            | 30 | 29                      | 28 | 27      | 26      | 25      | 24      |

| -                             | —  | —                       | _  | _       | —       | -       | —       |

| 23                            | 22 | 21                      | 20 | 19      | 18      | 17      | 16      |

| -                             | —  | —                       | -  | -       | -       | -       | —       |

| 15                            | 14 | 13                      | 12 | 11      | 10      | 9       | 8       |

| -                             | -  | -                       | -  | PCKRDY3 | PCKRDY2 | PCKRDY1 | PCKRDY0 |

| 7                             | 6  | 5                       | 4  | 3       | 2       | 1       | 0       |

| OSC_SEL                       | -  | -                       | -  | MCKRDY  | LOCKB   | LOCKA   | MOSCS   |

# • MOSCS: MOSCS Flag Status

0 = Main oscillator is not stabilized.

1 = Main oscillator is stabilized.

# LOCKA: PLL A Lock Status

- 0 = PLL A is not locked

- 1 = PLL A is locked.

#### LOCKB: PLL B Lock Status

- 0 = PLL B is not locked.

- 1 = PLL B is locked.

# MCKRDY: Master Clock Status

- 0 = Master Clock is not ready.

- 1 = Master Clock is ready.

### OSC\_SEL: Slow Clock Oscillator Selection

- 0 = Internal slow clock RC oscillator.

- 1 = External slow clock 32 kHz oscillator.

### PCKRDYx: Programmable Clock Ready Status

0 = Programmable Clock x is not ready.

1 = Programmable Clock x is ready.

| 26.6.3 | Debug Unit Interrupt Ena | able Register |  |

|--------|--------------------------|---------------|--|

| Name:  |                          | DBGU_IER      |  |

| Access | Type:                    | Write-only    |  |

|   | access type. |        | VVIIIC- | onny   |        |    |         |       |

|---|--------------|--------|---------|--------|--------|----|---------|-------|

| _ | 31           | 30     | 29      | 28     | 27     | 26 | 25      | 24    |

|   | COMMRX       | COMMTX | —       | _      | -      | -  | -       | _     |

| _ | 23           | 22     | 21      | 20     | 19     | 18 | 17      | 16    |

|   | _            | -      | —       | _      | -      | -  | -       | _     |

| _ | 15           | 14     | 13      | 12     | . 11   | 10 | 9       | 8     |

|   | -            | -      | -       | RXBUFF | TXBUFE | -  | TXEMPTY | -     |

|   | 7            | 6      | 5       | 4      | 3      | 2  | 1       | 0     |

|   | PARE         | FRAME  | OVRE    | ENDTX  | ENDRX  | _  | TXRDY   | RXRDY |

|   |              |        |         |        |        |    |         |       |

- RXRDY: Enable RXRDY Interrupt

- TXRDY: Enable TXRDY Interrupt

- ENDRX: Enable End of Receive Transfer Interrupt

- ENDTX: Enable End of Transmit Interrupt

- OVRE: Enable Overrun Error Interrupt

- FRAME: Enable Framing Error Interrupt

- PARE: Enable Parity Error Interrupt

- TXEMPTY: Enable TXEMPTY Interrupt

- TXBUFE: Enable Buffer Empty Interrupt

- RXBUFF: Enable Buffer Full Interrupt

- COMMTX: Enable COMMTX (from ARM) Interrupt

- COMMRX: Enable COMMRX (from ARM) Interrupt

- 0 = No effect.

1 = Enables the corresponding interrupt.

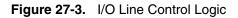

# 27.4 Functional Description

The PIO Controller features up to 32 fully-programmable I/O lines. Most of the control logic associated to each I/O is represented in Figure 27-3. In this description each signal shown represents but one of up to 32 possible indexes.

- Four output signals on I/O lines 4 to 7 (to drive LEDs for example), driven high and low, no pull-up resistor

- Four input signals on I/O lines 8 to 11 (to read push-button states for example), with pull-up resistors, glitch filters and input change interrupts

- Four input signals on I/O line 12 to 15 to read an external device status (polled, thus no input change interrupt), no pull-up resistor, no glitch filter

- I/O lines 16 to 19 assigned to peripheral A functions with pull-up resistor

- I/O lines 20 to 23 assigned to peripheral B functions, no pull-up resistor

- I/O line 24 to 27 assigned to peripheral A with Input Change Interrupt and pull-up resistor

| Register | Value to be Written |

|----------|---------------------|

| PIO_PER  | 0x0000 FFFF         |

| PIO_PDR  | 0x0FFF 0000         |

| PIO_OER  | 0x0000 00FF         |

| PIO_ODR  | 0x0FFF FF00         |

| PIO_IFER | 0x0000 0F00         |

| PIO_IFDR | 0x0FFF F0FF         |

| PIO_SODR | 0x0000 0000         |

| PIO_CODR | 0x0FFF FFFF         |

| PIO_IER  | 0x0F00 0F00         |

| PIO_IDR  | 0x00FF F0FF         |

| PIO_MDER | 0x0000 000F         |

| PIO_MDDR | 0x0FFF FFF0         |

| PIO_PUDR | 0x00F0 00F0         |

| PIO_PUER | 0x0F0F FF0F         |

| PIO_ASR  | 0x0F0F 0000         |

| PIO_BSR  | 0x00F0 0000         |

| PIO_OWER | 0x0000 000F         |

| PIO_OWDR | 0x0FFF FFF0         |

Table 27-1.

Programming Example

# 27.6 User Interface

Each I/O line controlled by the PIO Controller is associated with a bit in each of the PIO Controller User Interface registers. Each register is 32 bits wide. If a parallel I/O line is not defined, writing to the corresponding bits has no effect. Undefined bits read zero. If the I/O line is not mul-

# 28.7.1 SPI Control Register

| Name:        |    | SPI_C   | K    |    |    |        |          |

|--------------|----|---------|------|----|----|--------|----------|

| Access Type: |    | Write-c | only |    |    |        |          |

| 31           | 30 | 29      | 28   | 27 | 26 | 25     | 24       |

| _            | _  | _       | _    | _  | _  | -      | LASTXFER |

| 23           | 22 | 21      | 20   | 19 | 18 | 17     | 16       |

| _            | -  | -       | -    | -  | _  | -      | -        |

| 15           | 14 | 13      | 12   | 11 | 10 | 9      | 8        |

| _            | _  | -       | —    | —  | -  | —      | -        |

| 7            | 6  | 5       | 4    | 3  | 2  | 1      | 0        |

| SWRST        | _  | _       | _    | _  | _  | SPIDIS | SPIEN    |

# • SPIEN: SPI Enable

0 = No effect.

1 = Enables the SPI to transfer and receive data.

# • SPIDIS: SPI Disable

0 = No effect.

1 = Disables the SPI.

As soon as SPIDIS is set, SPI finishes its tranfer.

All pins are set in input mode and no data is received or transmitted.

If a transfer is in progress, the transfer is finished before the SPI is disabled.

If both SPIEN and SPIDIS are equal to one when the control register is written, the SPI is disabled.

## • SWRST: SPI Software Reset

0 = No effect.

1 = Reset the SPI. A software-triggered hardware reset of the SPI interface is performed.

The SPI is in slave mode after software reset.

PDC channels are not affected by software reset.

# • LASTXFER: Last Transfer

0 = No effect.

1 = The current NPCS will be deasserted after the character written in TD has been transferred. When CSAAT is set, this allows to close the communication with the current serial peripheral by raising the corresponding NPCS line as soon as TD transfer has completed.

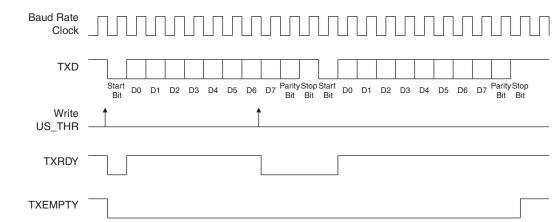

### Figure 29-6. Character Transmit

Example: 8-bit, Parity Enabled One Stop

The characters are sent by writing in the Transmit Holding Register (US\_THR). The transmitter reports two status bits in the Channel Status Register (US\_CSR): TXRDY (Transmitter Ready), which indicates that US\_THR is empty and TXEMPTY, which indicates that all the characters written in US\_THR have been processed. When the current character processing is completed, the last character written in US\_THR is transferred into the Shift Register of the transmitter and US\_THR becomes empty, thus TXRDY raises.

Both TXRDY and TXEMPTY bits are low since the transmitter is disabled. Writing a character in US\_THR while TXRDY is active has no effect and the written character is lost.

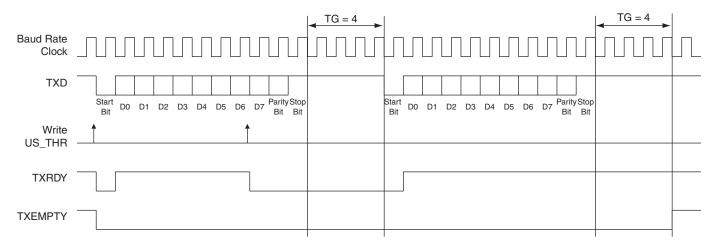

# Figure 29-7. Transmitter Status

29.6.3.2 Manchester Encoder

When the Manchester encoder is in use, characters transmitted through the USART are encoded based on biphase Manchester II format. To enable this mode, set the MAN field in the US\_MR register to 1. Depending on polarity configuration, a logic level (zero or one), is transmitted as a coded signal one-to-zero or zero-to-one. Thus, a transition always occurs at the midpoint of each bit time. It consumes more bandwidth than the original NRZ signal (2x) but the receiver has more error control since the expected input must show a change at the center of a bit cell. An example of Manchester encoded sequence is: the byte 0xB1 or 10110001 encodes to 10 01 10 10 01 01 10, assuming the default polarity of the encoder. Figure 29-8 illustrates this coding scheme.

# Figure 29-23. Timeguard Operations

Table 29-7 indicates the maximum length of a timeguard period that the transmitter can handle in relation to the function of the Baud Rate.

| Baud Rate | Bit time | Timeguard |

|-----------|----------|-----------|

| Bit/sec   | μs       | ms        |

| 1 200     | 833      | 212.50    |

| 9 600     | 104      | 26.56     |

| 14400     | 69.4     | 17.71     |

| 19200     | 52.1     | 13.28     |

| 28800     | 34.7     | 8.85      |

| 33400     | 29.9     | 7.63      |

| 56000     | 17.9     | 4.55      |

| 57600     | 17.4     | 4.43      |

| 115200    | 8.7      | 2.21      |

Table 29-7. Maximum Timeguard Length Depending on Baud Rate

### 29.6.3.11 Receiver Time-out

The Receiver Time-out provides support in handling variable-length frames. This feature detects an idle condition on the RXD line. When a time-out is detected, the bit TIMEOUT in the Channel Status Register (US\_CSR) rises and can generate an interrupt, thus indicating to the driver an end of frame.

The time-out delay period (during which the receiver waits for a new character) is programmed in the TO field of the Receiver Time-out Register (US\_RTOR). If the TO field is programmed at 0, the Receiver Time-out is disabled and no time-out is detected. The TIMEOUT bit in US\_CSR remains at 0. Otherwise, the receiver loads a 16-bit counter with the value programmed in TO. This counter is decremented at each bit period and reloaded each time a new character is received. If the counter reaches 0, the TIMEOUT bit in the Status Register rises. Then, the user can either:

• Stop the counter clock until a new character is received. This is performed by writing the Control Register (US\_CR) with the STTTO (Start Time-out) bit at 1. In this case, the idle state

- RXBUFF: Buffer Full Interrupt Disable

- NACK: Non Acknowledge Interrupt Disable

- RIIC: Ring Indicator Input Change Disable

- DSRIC: Data Set Ready Input Change Disable

- DCDIC: Data Carrier Detect Input Change Interrupt Disable

- CTSIC: Clear to Send Input Change Interrupt Disable

- MANE: Manchester Error Interrupt Disable

0: No effect.

1: Disables the corresponding interrupt.

# 29.7.5 USART Interrupt Mask Register

Name: US\_IMR

| Access Type: |       | Read-c | only   |        |           |         |         |

|--------------|-------|--------|--------|--------|-----------|---------|---------|

| 31           | 30    | 29     | 28     | 27     | 26        | 25      | 24      |

| _            | _     | —      | _      | _      | _         | _       | _       |

| 23           | 22    | 21     | 20     | 19     | 18        | 17      | 16      |

| -            | —     | -      | MANE   | CTSIC  | DCDIC     | DSRIC   | RIIC    |

| 15           | 14    | 13     | 12     | 11     | 10        | 9       | 8       |

| -            | —     | NACK   | RXBUFF | TXBUFE | ITERATION | TXEMPTY | TIMEOUT |

| 7            | 6     | 5      | 4      | 3      | 2         | 1       | 0       |

| PARE         | FRAME | OVRE   | ENDTX  | ENDRX  | RXBRK     | TXRDY   | RXRDY   |

- RXRDY: RXRDY Interrupt Mask

- TXRDY: TXRDY Interrupt Mask

- RXBRK: Receiver Break Interrupt Mask

- ENDRX: End of Receive Transfer Interrupt Mask

- ENDTX: End of Transmit Interrupt Mask

- OVRE: Overrun Error Interrupt Mask

- FRAME: Framing Error Interrupt Mask

- PARE: Parity Error Interrupt Mask

- TIMEOUT: Time-out Interrupt Mask

386 AT91CAP7E

- TXEMPTY: TXEMPTY Interrupt Mask

- ITERATION: Iteration Interrupt Mask

- TXBUFE: Buffer Empty Interrupt Mask

- RXBUFF: Buffer Full Interrupt Mask

- NACK: Non Acknowledge Interrupt Mask

- RIIC: Ring Indicator Input Change Mask

- DSRIC: Data Set Ready Input Change Mask

- DCDIC: Data Carrier Detect Input Change Interrupt Mask

- CTSIC: Clear to Send Input Change Interrupt Mask

**USART Channel Status Register**

# MANE: Manchester Error Interrupt Mask

- 0: The corresponding interrupt is disabled.

- 1: The corresponding interrupt is enabled.

29.7.6

| Name:        |       | US_CS  | SR     |        |           |         |         |

|--------------|-------|--------|--------|--------|-----------|---------|---------|

| Access Type: |       | Read-o | only   |        |           |         |         |

| 31           | 30    | 29     | 28     | 27     | 26        | 25      | 24      |

| -            | -     | -      | -      | -      | -         | -       | MANERR  |

| 23           | 22    | 21     | 20     | 19     | 18        | 17      | 16      |

| CTS          | DCD   | DSR    | RI     | CTSIC  | DCDIC     | DSRIC   | RIIC    |

| 15           | 14    | 13     | 12     | 11     | 10        | 9       | 8       |

| -            | -     | NACK   | RXBUFF | TXBUFE | ITERATION | TXEMPTY | TIMEOUT |

|              |       | _      |        | _      |           |         |         |

| 7            | 6     | 5      | 4      | 3      | 2         | 1       | 0       |

| PARE         | FRAME | OVRE   | ENDTX  | ENDRX  | RXBRK     | TXRDY   | RXRDY   |

### • RXRDY: Receiver Ready

0: No complete character has been received since the last read of US\_RHR or the receiver is disabled. If characters were being received when the receiver was disabled, RXRDY changes to 1 when the receiver is enabled.

1: At least one complete character has been received and US\_RHR has not yet been read.

# • TXRDY: Transmitter Ready

0: A character is in the US\_THR waiting to be transferred to the Transmit Shift Register, or an STTBRK command has been requested, or the transmitter is disabled. As soon as the transmitter is enabled, TXRDY becomes 1.

1: There is no character in the US\_THR.