Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | LINbus, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1574-e-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 3-3: PIC16(L)F1574 MEMORY MAP, BANKS 0-7

|      | BANK0                         | ``   | ,<br>BANK1                    |      | BANK2                         |      | BANK3                         |       | BANK4                         |      | BANK5                         |              | BANK6                                      |      | BANK7                         |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|-------|-------------------------------|------|-------------------------------|--------------|--------------------------------------------|------|-------------------------------|

| 000h | Core Registers<br>(Table 3-2) | 080h | Core Registers<br>(Table 3-2) | 100h | Core Registers<br>(Table 3-2) | 180h | Core Registers<br>(Table 3-2) | 200h  | Core Registers<br>(Table 3-2) | 280h | Core Registers<br>(Table 3-2) | 300h         | Core Registers<br>(Table 3-2)              | 380h | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh  |                               | 28Bh |                               | 30Bh         |                                            | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch  | WPUA                          | 28Ch | ODCONA                        | 30Ch         | SLRCONA                                    | 38Ch | INLVLA                        |

| 00Dh | —                             | 08Dh | —                             | 10Dh | _                             | 18Dh | —                             | 20Dh  | —                             | 28Dh | —                             | 30Dh         | —                                          | 38Dh | _                             |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh  | WPUC                          | 28Eh | ODCONC                        | 30Eh         | SLRCONC                                    | 38Eh | INLVLC                        |

| 00Fh |                               | 08Fh | _                             | 10Fh | —                             | 18Fh | —                             | 20Fh  |                               | 28Fh |                               | 30Fh         |                                            | 38Fh |                               |

| 010h | —                             | 090h | —                             | 110h | —                             | 190h | —                             | 210h  | _                             | 290h | _                             | 310h         | _                                          | 390h | _                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | CM1CON0                       | 191h | PMADRL                        | 211h  | _                             | 291h | _                             | 311h         | _                                          | 391h | IOCAP                         |

| 012h | PIR2                          | 092h | PIE2                          | 112h | CM1CON1                       | 192h | PMADRH                        | 212h  | _                             | 292h | _                             | 312h         | _                                          | 392h | IOCAN                         |

| 013h | PIR3                          | 093h | PIE3                          | 113h | CM2CON0                       | 193h | PMDATL                        | 213h  |                               | 293h |                               | 313h         |                                            | 393h | IOCAF                         |

| 014h |                               | 094h | _                             | 114h | CM2CON1                       | 194h | PMDATH                        | 214h  |                               | 294h |                               | 314h         |                                            | 394h |                               |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | CMOUT                         | 195h | PMCON1                        | 215h  | _                             | 295h | _                             | 315h         | _                                          | 395h | _                             |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h  | —                             | 296h | —                             | 316h         | —                                          | 396h |                               |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(1)</sup>        | 217h  | _                             | 297h | _                             | 317h         | _                                          | 397h | IOCCP                         |

| 018h | T1CON                         | 098h | OSCTUNE                       | 118h | DACCON0                       | 198h | —                             | 218h  | —                             | 298h | —                             | 318h         | —                                          | 398h | IOCCN                         |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h | DACCON1                       | 199h | RCREG                         | 219h  | —                             | 299h | —                             | 319h         | —                                          | 399h | IOCCF                         |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | —                             | 19Ah | TXREG                         | 21Ah  | _                             | 29Ah | _                             | 31Ah         | _                                          | 39Ah |                               |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh | —                             | 19Bh | SPBRGL                        | 21Bh  |                               | 29Bh |                               | 31Bh         |                                            | 39Bh |                               |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                        | 21Ch  | —                             | 29Ch | —                             | 31Ch         | —                                          | 39Ch | —                             |

| 01Dh | _                             | 09Dh | ADCON0                        | 11Dh | —                             | 19Dh | RCSTA                         | 21Dh  | —                             | 29Dh | —                             | 31Dh         | —                                          | 39Dh | —                             |

| 01Eh | _                             | 09Eh | ADCON1                        | 11Eh | —                             | 19Eh | TXSTA                         | 21Eh  | _                             | 29Eh | _                             | 31Eh         | _                                          | 39Eh | _                             |

| 01Fh | —                             | 09Fh | ADCON2                        | 11Fh | —                             | 19Fh | BAUDCON                       | 21Fh  | —                             | 29Fh | —                             | 31Fh         | —                                          | 39Fh | _                             |

| 020h | General<br>Purpose            | 0A0h | General<br>Purpose            | 120h | General<br>Purpose            | 1A0h | General<br>Purpose            | 220h  | General<br>Purpose            | 2A0h | General<br>Purpose            | 320h<br>32Fh | General<br>Purpose<br>Register<br>16 Bytes | 3A0h | Unimplemented                 |

| 005  | Register<br>80 Bytes          | 0551 | Register<br>80 Bytes          | 105  | Register<br>80 Bytes          |      | Register<br>80 Bytes          | 0.051 | Register<br>80 Bytes          | 0    | Register<br>80 Bytes          | 330h         | Unimplemented<br>Read as '0'               | 055h | Read as '0'                   |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh  |                               | 2EFh |                               | 36Fh         |                                            | 3EFh |                               |

| 070h | Common RAM                    | 0F0h | Accesses<br>70h – 7Fh         | 170h | Accesses<br>70h – 7Fh         | 1F0h | Accesses<br>70h – 7Fh         | 270h  | Accesses<br>70h – 7Fh         | 2F0h | Accesses<br>70h – 7Fh         | 370h         | Accesses<br>70h – 7Fh                      | 3F0h | Accesses<br>70h – 7Fh         |

| 07Fh |                               | 0FFh |                               | 17Fh |                               | 1FFh |                               | 27Fh  |                               | 2FFh |                               | 37Fh         |                                            | 3FFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16LF1574.

PIC16(L)F1574/5/8/9

## 3.3.6 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-14 can be addressed from any Bank.

| Addr            | Name   | Bit 7            | Bit 6                                                                                        | Bit 5         | Bit 4        | Bit 3        | Bit 0         | Value on<br>POR, BOR | Value on all other Resets |           |           |  |

|-----------------|--------|------------------|----------------------------------------------------------------------------------------------|---------------|--------------|--------------|---------------|----------------------|---------------------------|-----------|-----------|--|

| Bank            | 0-31   |                  |                                                                                              |               |              |              |               |                      |                           |           |           |  |

| x00h or<br>x80h | INDF0  |                  | this location<br>ical register)                                                              |               | xxxx xxxx    | uuuu uuuu    |               |                      |                           |           |           |  |

| x01h or<br>x81h | INDF1  |                  | this location<br>ical register)                                                              |               | nts of FSR1H | /FSR1L to ad | ddress data i | memory               |                           | XXXX XXXX | uuuu uuuu |  |

| x02h or<br>x82h | PCL    | Program C        | ounter (PC) I                                                                                | Least Signifi | cant Byte    |              |               |                      |                           | 0000 0000 | 0000 0000 |  |

| x03h or<br>x83h | STATUS | _                |                                                                                              |               | TO           | PD           | Z             | DC                   | С                         | 1 1000    | q quuu    |  |

| x04h or<br>x84h | FSR0L  | Indirect Da      | ta Memory A                                                                                  | ddress 0 Lo   | w Pointer    |              |               |                      |                           | 0000 0000 | uuuu uuuu |  |

| x05h or<br>x85h | FSR0H  | Indirect Da      | ta Memory A                                                                                  | ddress 0 Hig  | gh Pointer   |              |               |                      |                           | 0000 0000 | 0000 0000 |  |

| x06h or<br>x86h | FSR1L  | Indirect Da      | ta Memory A                                                                                  | ddress 1 Lo   | w Pointer    |              |               |                      |                           | 0000 0000 | uuuu uuuu |  |

| x07h or<br>x87h | FSR1H  | Indirect Da      | ta Memory A                                                                                  | ddress 1 Hig  | gh Pointer   |              |               |                      |                           | 0000 0000 | 0000 0000 |  |

| x08h or<br>x88h | BSR    | _                | -                                                                                            | _             |              |              | BSR<4:0>      |                      |                           | 0 0000    | 0 0000    |  |

| x09h or<br>x89h | WREG   | Working Register |                                                                                              |               |              |              |               |                      |                           |           | uuuu uuuu |  |

| x0Ahor<br>x8Ah  | PCLATH | _                | Write Buffer for the upper 7 bits of the Program Counter         -000 0000         -000 0000 |               |              |              |               |                      |                           |           |           |  |

| x0Bhor<br>x8Bh  | INTCON | GIE              | PEIE                                                                                         | TMR0IE        | INTE         | IOCIE        | TMR0IF        | INTF                 | IOCIF                     | 0000 0000 | 0000 0000 |  |

#### TABLE 3-14: CORE FUNCTION REGISTERS SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16(L)F157x Memory Programming Specification*" (DS40001766).

### 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

| U-0             | U-0               | R/W-0/0           | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-----------------|-------------------|-------------------|-----------------|------------------|------------------|----------------|--------------|

|                 | _                 |                   |                 | TUN              | <5:0>            |                |              |

| bit 7           |                   |                   |                 |                  |                  |                | bit 0        |

|                 |                   |                   |                 |                  |                  |                |              |

| Legend:         |                   |                   |                 |                  |                  |                |              |

| R = Readab      | le bit            | W = Writable      | bit             | U = Unimpler     | nented bit, read | d as '0'       |              |

| u = Bit is und  | changed           | x = Bit is unkr   | nown            | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is se | et                | '0' = Bit is clea | ared            |                  |                  |                |              |

|                 |                   |                   |                 |                  |                  |                |              |

| bit 7-6         | Unimpleme         | nted: Read as '   | 0'              |                  |                  |                |              |

| bit 5-0         | TUN<5:0>:         | Frequency Tunir   | ng bits         |                  |                  |                |              |

|                 | 100000 = N        | Ainimum frequer   | псу             |                  |                  |                |              |

|                 | •                 |                   |                 |                  |                  |                |              |

|                 | •                 |                   |                 |                  |                  |                |              |

|                 | 111111 =          |                   |                 |                  |                  |                |              |

|                 | 000000 = <b>C</b> | Oscillator module | e is running at | the factory-cali | brated frequen   | cy.            |              |

|                 | 000001 =          |                   |                 |                  |                  |                |              |

|                 | •                 |                   |                 |                  |                  |                |              |

|                 | •                 |                   |                 |                  |                  |                |              |

|                 | 011110 =          |                   |                 |                  |                  |                |              |

|                 | 011111 = 🛚        | Maximum freque    | ncy             |                  |                  |                |              |

### REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER

|                       | D 0/0                 | D 0/0                 | D 0/0                  | 11.0           |                   | 11.0             |             |

|-----------------------|-----------------------|-----------------------|------------------------|----------------|-------------------|------------------|-------------|

| R-0/0                 | R-0/0                 | R-0/0                 | R-0/0                  | U-0            | U-0               | U-0              | U-0         |

| PWM4IF <sup>(1)</sup> | PWM3IF <sup>(1)</sup> | PWM2IF <sup>(1)</sup> | PWM1IF <sup>(1)</sup>  | —              | —                 | —                | _           |

| bit 7                 |                       |                       |                        |                |                   |                  | bit 0       |

|                       |                       |                       |                        |                |                   |                  |             |

| Legend:               |                       |                       |                        |                |                   |                  |             |

| R = Readable          | bit                   | W = Writable          | bit                    | U = Unimpler   | mented bit, read  | as '0'           |             |

| u = Bit is unch       | nanged                | x = Bit is unkr       | nown                   | -n/n = Value   | at POR and BOI    | R/Value at all o | ther Resets |

| '1' = Bit is set      |                       | '0' = Bit is cle      | ared                   |                |                   |                  |             |

|                       |                       |                       |                        |                |                   |                  |             |

| bit 7                 | PWM4IF: PW            | /M4 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt i       | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 6                 | PWM3IF: PW            | /M3 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt         | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 5                 | PWM2IF: PW            | /M2 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt         |                       |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 4                 | PWM1IF: PW            | /M1 Interrupt F       | lag bit <sup>(1)</sup> |                |                   |                  |             |

|                       | 1 = Interrupt         | is pending            |                        |                |                   |                  |             |

|                       | 0 = Interrupt         | is not pending        |                        |                |                   |                  |             |

| bit 3-0               | Unimplemen            | nted: Read as '       | 0'                     |                |                   |                  |             |

| Note 1. Th            | oso hits aro roa      | d only Thoy m         | ust be cleared         | l by addragain | a the Flee regist | ora inaida tha n | aadula      |

## REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

- Note 1: These bits are read-only. They must be cleared by addressing the Flag registers inside the module.

- 2: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## PIC16(L)F1574/5/8/9

| TABLE 9-3: | SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER |

|------------|-----------------------------------------------------|

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4             | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |  |

|--------|--------|--------|-------|-------------------|-------|-------|-------|-------|---------------------|--|

| OSCCON | SPLLEN |        | IRCF  | <3:0>             |       | —     | SCS   | <1:0> | 69                  |  |

| PCON   | STKOVF | STKUNF | —     | RWDT              | RMCLR | RI    | POR   | BOR   | 79                  |  |

| STATUS | —      | _      | _     | TO                | PD    | Z     | DC    | С     | 23                  |  |

| WDTCON | _      | _      |       | WDTPS<4:0> SWDTEN |       |       |       |       |                     |  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 | _       | —       |          | —        | CLKOUTEN | BORE     | N<1:0>  | —       | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   |          | FOSC    | <1:0>   | 56                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

| Devinhevel                  | xxxPPS    | Default Pir     | n Selection     | Reset Value (xxxPPS<4:0>) |                 |  |  |

|-----------------------------|-----------|-----------------|-----------------|---------------------------|-----------------|--|--|

| Peripheral                  | Register  | PIC16(L)F1578/9 | PIC16(L)F1574/5 | PIC16(L)F1578/9           | PIC16(L)F1574/5 |  |  |

| Interrupt-on-change         | INTPPS    | RA2             | RA2             | 00010                     | 00010           |  |  |

| Timer Oclock                | TOCKIPPS  | RA2             | RA2             | 00010                     | 00010           |  |  |

| Timer 1clock                | T1CKIPPS  | RA5             | RA5             | 00101                     | 00101           |  |  |

| Timer 1 gate                | T1GPPS    | RA4             | RA4             | 00100                     | 00100           |  |  |

| CWG1                        | CWG1INPPS | RA2             | RA2             | 00010                     | 00010           |  |  |

| EUSART RX                   | RXPPS     | RB5             | RC5             | 01101                     | 10101           |  |  |

| EUSART CK                   | CKPPS     | RB7             | RC4             | 01111                     | 10100           |  |  |

| ADC Auto-Conversion Trigger | ADCACTPPS | RC4             | RC4             | 10100                     | 10100           |  |  |

TABLE 12-1:PPS INPUT REGISTER RESET VALUES

**Example:** ADCACTPPS = 0x14 selects RC4 as the ADC Auto-Conversion Trigger input.

|             | Output Circal           | F     | PIC16(L)F1578 | /9    | PIC16(L | )F1574/5 |

|-------------|-------------------------|-------|---------------|-------|---------|----------|

| RxyPPS<3:0> | Output Signal           | PORTA | PORTB         | PORTC | PORTA   | PORTC    |

| 1111        | Reserved                | —     | —             | _     | —       | —        |

| 1110        | Reserved                | _     | —             |       | —       | _        |

| 1101        | Reserved                | —     | —             | —     | —       | —        |

| 1100        | Reserved                | —     | —             |       | —       | —        |

| 1011        | Reserved                | _     | —             |       | —       | _        |

| 1010        | DT <sup>(1)</sup>       | •     | •             | •     | •       | •        |

| 1001        | TX/CK <sup>(1)</sup>    | •     | •             | •     | •       | •        |

| 1000        | CWG1OUTB <sup>(1)</sup> | •     | •             | •     | •       | •        |

| 0111        | CWG1OUTA <sup>(1)</sup> | •     | •             | •     | •       | •        |

| 0110        | PWM4_out                | •     | •             | •     | •       | •        |

| 0101        | PWM3_out                | •     | •             | •     | •       | •        |

| 0100        | PWM2_out                | •     | •             | •     | •       | •        |

| 0011        | PWM1_out                | •     | •             | •     | •       | •        |

| 0010        | sync_C2OUT              | •     | •             | •     | •       | •        |

| 0001        | sync_C1OUT              | •     | •             | •     | •       | •        |

| 0000        | LATxy                   | •     | •             | ٠     | •       | •        |

## TABLE 12-2: AVAILABLE PORTS FOR OUTPUT BY PERIPHERAL<sup>(2)</sup>

Note 1: TRIS control is overridden by the peripheral as required.

2: Unsupported peripherals will output a '0'.

#### 16.4 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 16-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 16-5. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 16-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of  $10k\Omega 5.0V VDD$  TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient<math>= TAMP + TC + TCOFF  $= 2\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]$ The value for TC can be approximated with the following equations:  $VAPPLIED\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = VCHOLD$  ;[1] VCHOLD charged to within 1/2 lsb  $VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VCHOLD$  ;[2] VCHOLD charge response to VAPPLIED  $VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VCHOLD$  ;[2] VCHOLD charge response to VAPPLIED  $VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VAPPLIED\left(1 - \frac{1}{(2^{n+1}) - 1}\right)$  ;combining [1] and [2] Note: Where n = number of bits of the ADC. Solving for TC:  $TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$

$$= -12.5pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$$

= 1.715µs

Therefore:

$$TACQ = 2\mu s + 1.715\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.96\mu s

Note 1: The reference voltage (VRPOS) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

### 19.2 Register Definitions: Option Register

## REGISTER 19-1: OPTION\_REG: OPTION REGISTER

|                  |                                                               | -                                                                                                                                                                           |                                                          |                |                  |                  |              |

|------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------|------------------|------------------|--------------|

| R/W-1/1          | R/W-1/1                                                       | R/W-1/1                                                                                                                                                                     | R/W-1/1                                                  | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

| WPUEN            | INTEDG                                                        | TMR0CS                                                                                                                                                                      | TMR0SE                                                   | PSA            |                  | PS<2:0>          |              |

| bit 7            |                                                               |                                                                                                                                                                             |                                                          |                |                  |                  | bit 0        |

|                  |                                                               |                                                                                                                                                                             |                                                          |                |                  |                  |              |

| Legend:          |                                                               |                                                                                                                                                                             |                                                          |                |                  |                  |              |

| R = Readable     | bit                                                           | W = Writable                                                                                                                                                                | bit                                                      | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is uncha | anged                                                         | x = Bit is unkr                                                                                                                                                             | nown                                                     | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |                                                               | '0' = Bit is cle                                                                                                                                                            | ared                                                     |                |                  |                  |              |

| bit 7<br>bit 6   | 1 = All weak<br>0 = Weak pul<br>INTEDG: Inte<br>1 = Interrupt | ak Pull-Up Ena<br>pull-ups are dis<br>Il-ups are enabl<br>errupt Edge Sel<br>on rising edge<br>on falling edge                                                              | abled (except<br>ed by individu<br>ect bit<br>of INT pin |                |                  |                  |              |

| bit 5            | <b>TMR0CS:</b> Tir<br>1 = Transitior                          | ner0 Clock Sou<br>on T0CKI pin<br>nstruction cycle                                                                                                                          | Irce Select bit                                          | l)             |                  |                  |              |

| bit 4            | TMR0SE: Tir<br>1 = Incremen                                   | ner0 Source Ec<br>it on high-to-lov<br>it on low-to-high                                                                                                                    | lge Select bit<br>v transition on                        | T0CKI pin      |                  |                  |              |

| bit 3            | <b>PSA:</b> Presca<br>1 = Prescaler                           | ler Assignment<br>is not assigne<br>is assigned to                                                                                                                          | bit<br>d to the Timer                                    | 0 module       |                  |                  |              |

| bit 2-0          |                                                               | escaler Rate Se                                                                                                                                                             |                                                          |                |                  |                  |              |

|                  | Bit                                                           | Value Timer0                                                                                                                                                                | Rate                                                     |                |                  |                  |              |

|                  | )<br>(<br>(<br>1<br>1<br>1<br>1<br>1<br>1<br>1                | 000         1:2           001         1:4           010         1:8           011         1:1           100         1:3           101         1:6           110         1:1 | 6<br>2<br>4<br>28                                        |                |                  |                  |              |

| TABLE 19-1:      | SUMMAR                                                        | Y OF REGIST                                                                                                                                                                 |                                                          | CIATED WIT     | H TIMER0         |                  |              |

| Name       | Bit 7       | Bit 6          | Bit 5        | Bit 4   | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|-------------|----------------|--------------|---------|-------|--------|---------|--------|---------------------|

| ADCON2     |             | TRIGSI         | EL<3:0>      |         | -     |        |         | —      | 160                 |

| INTCON     | GIE         | PEIE           | TMR0IE       | INTE    | IOCIE | TMR0IF | INTF    | IOCIF  | 86                  |

| OPTION_REG | WPUEN       | INTEDG         | TMR0CS       | TMR0SE  | PSA   |        | PS<2:0> |        | 178                 |

| TMR0       | Holding Reg | gister for the | 8-bit Timer0 | ) Count |       |        | 176*    |        |                     |

| TRISA      |             | _              | TRISA5       | TRISA4  | _(1)  | TRISA2 | TRISA1  | TRISA0 | 120                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

## 20.8 Register Definitions: Timer1 Control

### REGISTER 20-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u                                                                                                   | R/W-0/u                    | R/W-0/u                                                                  | R/W-0/u        | U-0                                | R/W-0/u     | U-0 | R/W-0/u |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|----------------|------------------------------------|-------------|-----|---------|--|--|

| TMR1CS<1:0>                                                                                               |                            | T1CKPS<1:0>                                                              |                | _                                  | T1SYNC      | _   | TMR10N  |  |  |

| bit 7                                                                                                     |                            |                                                                          |                |                                    |             |     | bit 0   |  |  |

|                                                                                                           |                            |                                                                          |                |                                    |             |     |         |  |  |

| Legend:                                                                                                   |                            |                                                                          |                |                                    |             |     |         |  |  |

| R = Readable bit                                                                                          |                            | W = Writable bit                                                         |                | U = Unimplemented bit, read as '0' |             |     |         |  |  |

| u = Bit is unchanged                                                                                      |                            | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                |                                    |             |     |         |  |  |

| '1' = Bit is set                                                                                          |                            | '0' = Bit is clea                                                        | ared           |                                    |             |     |         |  |  |

|                                                                                                           |                            |                                                                          |                |                                    |             |     |         |  |  |

| bit 7-6                                                                                                   | TMR1CS<1                   | :0>: Timer1 Cloc                                                         | k Source Sele  | ect bits                           |             |     |         |  |  |

|                                                                                                           |                            | clock source is                                                          |                |                                    |             |     |         |  |  |

|                                                                                                           |                            | clock source is                                                          | 1 (            | 0 0                                | e)          |     |         |  |  |

| 01 = Timer1 clock source is system clock (Fosc)<br>00 = Timer1 clock source is instruction clock (Fosc/4) |                            |                                                                          |                |                                    |             |     |         |  |  |

| bit 5-4                                                                                                   |                            | :0>: Timer1 Inpu                                                         |                | . ,                                |             |     |         |  |  |

|                                                                                                           | 11 = 1:8 Pre               | •                                                                        |                |                                    |             |     |         |  |  |

|                                                                                                           | 10 = 1:4 Pre               |                                                                          |                |                                    |             |     |         |  |  |

|                                                                                                           | 01 <b>= 1:2 Pre</b>        | escale value                                                             |                |                                    |             |     |         |  |  |

|                                                                                                           | 00 = 1:1 Pre               | escale value                                                             |                |                                    |             |     |         |  |  |

| bit 3                                                                                                     | Unimpleme                  | nted: Read as '                                                          | כי             |                                    |             |     |         |  |  |

| bit 2 <b>T1SYNC</b> : Timer1 Synchronization Control bit                                                  |                            |                                                                          |                |                                    |             |     |         |  |  |

| 1 = Do not synchronize asynchronous clock input                                                           |                            |                                                                          |                |                                    |             |     |         |  |  |

|                                                                                                           | 0 = Synchro                | onize asynchron                                                          | ous clock inpu | t with system c                    | lock (Fosc) |     |         |  |  |

| bit 1                                                                                                     | Unimplemented: Read as '0' |                                                                          |                |                                    |             |     |         |  |  |

| bit 0                                                                                                     | TMR1ON: T                  | ïmer1 On bit                                                             |                |                                    |             |     |         |  |  |

|                                                                                                           | 1 = Enables                |                                                                          |                |                                    |             |     |         |  |  |

|                                                                                                           | 0 = Stops T                | imer1 and clears                                                         | Timer1 date t  | flin-flon                          |             |     |         |  |  |

| Name    | Bit 7                         | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|-------|--------|-------|-------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL | —      | SCKP  | BRG16 | —      | WUE    | ABDEN  | 204                 |

| INTCON  | GIE                           | PEIE  | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 86                  |

| PIE1    | TMR1GIE                       | ADIE  | RCIE   | TXIE  | —     | _      | TMR2IE | TMR1IE | 87                  |

| PIR1    | TMR1GIF                       | ADIF  | RCIF   | TXIF  | —     | —      | TMR2IF | TMR1IF | 90                  |

| RCSTA   | SPEN                          | RX9   | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 203*                |

| SPBRGL  | BRG<7:0>                      |       |        |       |       |        |        | 205*   |                     |

| SPBRGH  | BRG<15:8>                     |       |        |       |       |        | 205*   |        |                     |

| TXREG   | EUSART Transmit Data Register |       |        |       |       |        |        | 194    |                     |

| TXSTA   | CSRC                          | TX9   | TXEN   | SYNC  | SENDB | BRGH   | TRMT   | TX9D   | 202                 |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous transmission.

\* Page provides register information.

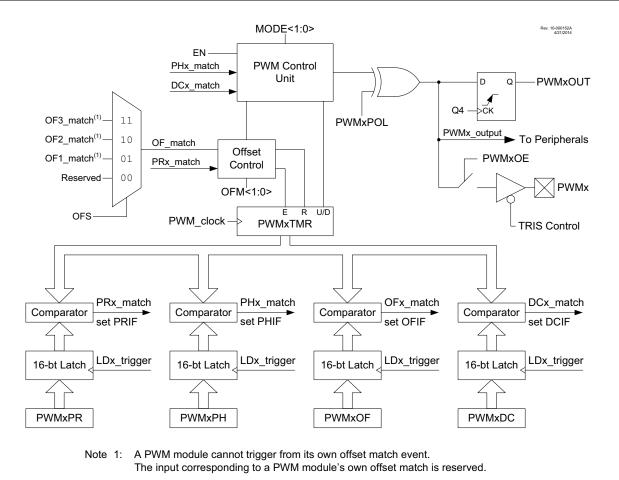

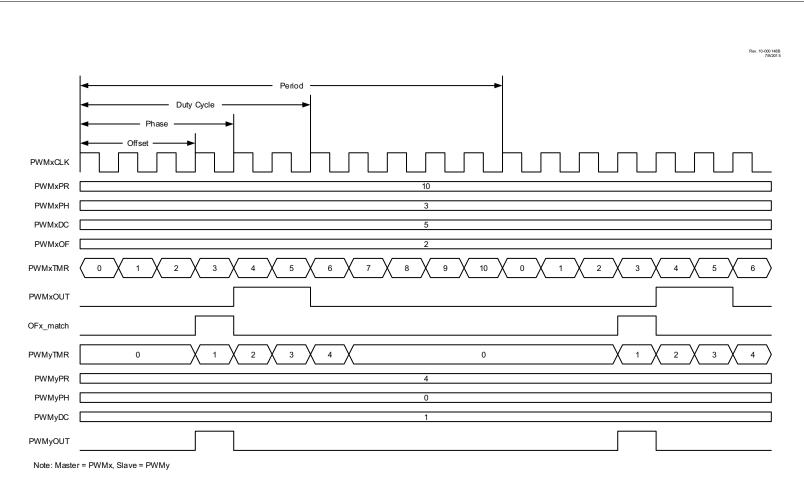

## 23.0 16-BIT PULSE-WIDTH MODULATION (PWM) MODULE

The Pulse-Width Modulation (PWM) module generates a pulse width modulated signal determined by the phase, duty cycle, period, and offset event counts that are contained in the following registers:

- PWMxPH register

- PWMxDC register

- PWMxPR register

- PWMxOF register

Figure 23-1 shows a simplified block diagram of the PWM operation.

Each PWM module has four modes of operation:

- Standard

- · Set On Match

- Toggle On Match

- · Center-Aligned

For a more detailed description of each PWM mode, refer to **Section 23.2** "**PWM Modes**".

Each PWM module has four offset modes:

- Independent Run

- · Slave Run with Synchronous Start

- · One-Shot Slave with Synchronous Start

- Continuous Run Slave with Synchronous Start and Timer Reset

Using the offset modes, each PWM module can offset its waveform relative to any other PWM module in the same device. For a more detailed description of the offset modes refer to **Section 23.3 "Offset Modes"**.

Every PWM module has a configurable reload operation to ensure all event count buffers change at the end of a period thereby avoiding signal glitches. Figure 23-2 shows a simplified block diagram of the reload operation. For a more detailed description of the reload operation, refer to Section **Section 23.4 "Reload Operation"**.

### FIGURE 23-1: 16-BIT PWM BLOCK DIAGRAM

### FIGURE 23-10: ONE-SHOT SLAVE RUN MODE WITH SYNC START TIMING DIAGRAM

PIC16(L)F1574/5/8/9

© 2016 Microchip Technology Inc

PIC16(L)F1574/5/8/9

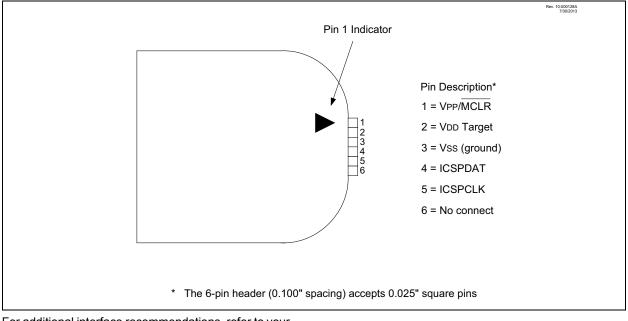

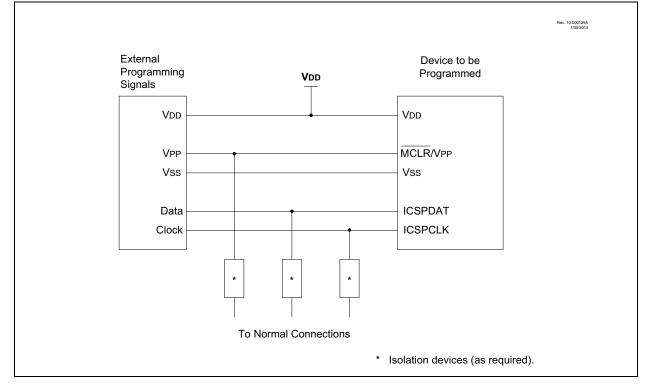

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 25-3 for more information.

## FIGURE 26-1: GENERAL FORMAT FOR INSTRUCTIONS

| 13                                                                                                                                                              | 8 7                                                                      | 6              |                 | 0  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|-----------------|----|

| OPCODE                                                                                                                                                          | d                                                                        |                | f (FILE #)      |    |

| d = 0 for de<br>d = 1 for de<br>f = 7-bit file                                                                                                                  | stination f                                                              |                |                 |    |

| Bit-oriented file                                                                                                                                               | register o<br>10 9                                                       | peratio<br>7 6 |                 | 0  |

| OPCODE                                                                                                                                                          |                                                                          | IT #)          | f (FILE #)      | -  |

| b = 3-bit bit<br>f = 7-bit file                                                                                                                                 |                                                                          | dress          |                 |    |

| Literal and conti                                                                                                                                               | rol operati                                                              | ons            |                 |    |

| General                                                                                                                                                         |                                                                          |                |                 |    |

| 13                                                                                                                                                              | 8                                                                        | 7              |                 | 0  |

| OPCODE                                                                                                                                                          |                                                                          |                | k (literal)     |    |

| k = 8-bit imr                                                                                                                                                   | nediate va                                                               | lue            |                 |    |

| CALL and GOTO ir                                                                                                                                                | nstructions                                                              | only           |                 |    |

| <u>13 11</u>                                                                                                                                                    |                                                                          | ,              |                 | 0  |

| OPCODE                                                                                                                                                          |                                                                          | k (lit         | eral)           |    |

| k = 11-bit im                                                                                                                                                   | imediate va                                                              | alue           |                 |    |

|                                                                                                                                                                 | only                                                                     |                |                 |    |

| MOVLP instruction<br>13                                                                                                                                         | Only                                                                     | 76             |                 | 0  |

| OPCODE                                                                                                                                                          |                                                                          |                | k (literal)     |    |

| k = 7-bit imr                                                                                                                                                   | nediate va                                                               | lue            |                 |    |

|                                                                                                                                                                 |                                                                          |                |                 |    |

| MOVLB instruction                                                                                                                                               | only                                                                     | F              | 4               | 0  |

| 13<br>OPCODE                                                                                                                                                    |                                                                          | 5              | 4<br>k (literal | 0  |

| k = 5-bit imr                                                                                                                                                   |                                                                          | مىا            | (               | ,  |

| K – 5-bit IIII                                                                                                                                                  |                                                                          | lue            |                 |    |

|                                                                                                                                                                 |                                                                          |                |                 |    |

| BRA instruction or                                                                                                                                              |                                                                          | Q              |                 | 0  |

| BRA instruction or<br>13<br>OPCODE                                                                                                                              | 9                                                                        | 8              | k (literal)     | 0  |

| 13<br>OPCODE                                                                                                                                                    | 9                                                                        | -              | k (literal)     | 0  |

| 13                                                                                                                                                              | 9                                                                        | -              | k (literal)     | 0  |

| 13<br>OPCODE<br>k = 9-bit imi                                                                                                                                   | 9<br>mediate va                                                          | lue            |                 | 0  |

| 13<br>OPCODE<br>k = 9-bit imi<br>FSR Offset instru<br>13                                                                                                        | 9<br>mediate va<br>uctions<br>7                                          | lue<br>6 5     |                 | 0  |

| 13<br>OPCODE<br>k = 9-bit imi<br>FSR Offset instru<br>13<br>OPCODE                                                                                              | 9<br>mediate va<br>ictions<br>7                                          | lue            |                 | 0  |

| 13<br>OPCODE<br>k = 9-bit imi<br>FSR Offset instru<br>13                                                                                                        | 9<br>mediate va<br>ictions<br>7<br>riate FSR                             | lue<br>65<br>n |                 | 0  |

| 13<br>OPCODE<br>k = 9-bit imi<br>FSR Offset instru<br>13<br>OPCODE<br>n = appropr                                                                               | 9<br>mediate va<br>ictions<br>7<br>riate FSR<br>mediate va               | lue<br>65<br>n |                 | 0  |

| 13<br>OPCODE<br>k = 9-bit imi<br>FSR Offset instru<br>13<br>OPCODE<br>n = appropri<br>k = 6-bit imi                                                             | 9<br>mediate va<br>ictions<br>7<br>riate FSR<br>mediate va               | lue<br>65<br>n | k (literal      | 0) |

| 13<br>OPCODE<br>k = 9-bit imi<br>FSR Offset instru<br>13<br>OPCODE<br>n = appropri<br>k = 6-bit imi<br>FSR Increment in<br>13                                   | 9<br>mediate va<br>ictions<br>7<br>riate FSR<br>mediate va<br>structions | lue<br>65<br>n | k (literal      | 0) |

| 13<br>OPCODE<br>k = 9-bit imit<br>FSR Offset instru<br>13<br>OPCODE<br>n = approprise<br>k = 6-bit imit<br>FSR Increment init<br>13<br>OPCODE<br>n = approprise | 9<br>mediate va<br>ictions<br>7<br>riate FSR<br>mediate va<br>structions | lue<br>65<br>n | k (literal      | 0) |

| PIC16LF1574/5/8/9<br>PIC16F1574/5/8/9 |                           | Standard Operating Conditions (unless otherwise stated) |      |      |       |            |                                                                            |  |

|---------------------------------------|---------------------------|---------------------------------------------------------|------|------|-------|------------|----------------------------------------------------------------------------|--|

|                                       |                           |                                                         |      |      |       |            |                                                                            |  |

| Param.<br>No.                         | Device<br>Characteristics | Min.                                                    | Тур† | Max. | Units | Conditions |                                                                            |  |

|                                       |                           |                                                         |      |      |       | VDD        | Note                                                                       |  |

| D018A*                                |                           | —                                                       | 2.3  | 2.8  | mA    | 3.0        | Fosc = 32 MHz,<br>HFINTOSC (Note 3)                                        |  |

| D018A*                                |                           | —                                                       | 2.5  | 2.9  | mA    | 3.0        | Fosc = 32 MHz,                                                             |  |

|                                       |                           | —                                                       | 2.6  | 3.0  | mA    | 5.0        | HFINTOSC (Note 3)                                                          |  |

| D019A                                 |                           | —                                                       | 2.0  | 2.2  | mA    | 3.0        | Fosc = 32 MHz,<br>External Clock (ECH),<br>High-Power mode <b>(Note 3)</b> |  |

| D019A                                 |                           | —                                                       | 2.1  | 2.3  | mA    | 3.0        | Fosc = 32 MHz,                                                             |  |

|                                       |                           | —                                                       | 2.2  | 2.7  | mA    | 5.0        | External Clock (ECH),<br>High-Power mode <b>(Note 3)</b>                   |  |

| D019B                                 |                           | —                                                       | 2.6  | 16   | μA    | 1.8        | Fosc = 32 kHz,                                                             |  |

|                                       |                           | —                                                       | 5.0  | 22   | μA    | 3.0        | External Clock (ECL),<br>Low-Power mode                                    |  |

| D019B                                 |                           |                                                         | 14   | 23   | μA    | 2.3        | Fosc = 32 kHz,                                                             |  |

|                                       |                           |                                                         | 18   | 29   | μA    | 3.0        | External Clock (ECL),<br>Low-Power mode                                    |  |

|                                       |                           | _                                                       | 20   | 30   | μA    | 5.0        |                                                                            |  |

| D019C                                 |                           |                                                         | 21   | 29   | μA    | 1.8        | Fosc = 500  kHz,                                                           |  |

|                                       |                           | _                                                       | 35   | 44   | μA    | 3.0        | External Clock (ECL),<br>Low-Power mode                                    |  |

| D019C                                 |                           | _                                                       | 34   | 46   | μA    | 2.3        | Fosc = 500 kHz,                                                            |  |

|                                       |                           | _                                                       | 43   | 59   | μA    | 3.0        | External Clock (ECL),<br>Low-Power mode                                    |  |

|                                       |                           | _                                                       | 49   | 61   | μA    | 5.0        |                                                                            |  |

#### SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED) **TABLE 27-2**:

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: CLKIN = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: PLL required for 32 MHz operation.

# PIC16(L)F1574/5/8/9

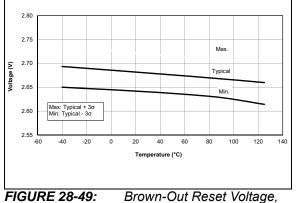

BORV = 0.

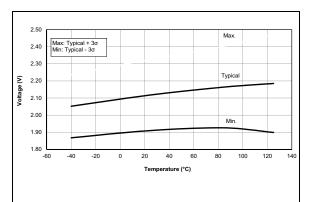

FIGURE 28-50: Low-Power Brown-Out Reset Voltage, LPBOR = 0.

Max.

Typical

Temperature (°C)

Min.

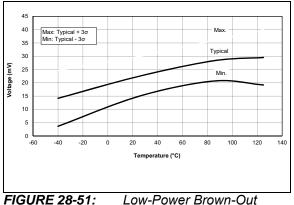

Reset Hysteresis, LPBOR = 0.

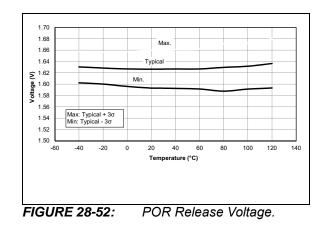

FIGURE 28-53: POR Rearm Voltage, PIC16F1574/5/8/9 Only.

-40

-20 0 20 40 60 80

1.54 1.52

1.50

1.48 **S**<sup>1.46</sup> 1.44 1.42

1.40

1.38

1.36

1.34

-60

5.0 5.5 6.0